ARM协处理器指令.

- 格式:doc

- 大小:30.00 KB

- 文档页数:10

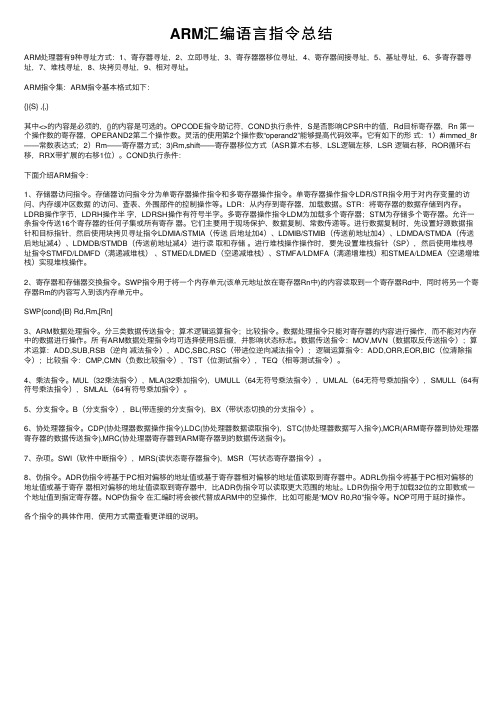

ARM汇编语⾔指令总结ARM处理器有9种寻址⽅式:1、寄存器寻址,2、⽴即寻址,3、寄存器器移位寻址,4、寄存器间接寻址,5、基址寻址,6、多寄存器寻址,7、堆栈寻址,8、块拷贝寻址,9、相对寻址。

ARM指令集:ARM指令基本格式如下:{}{S} ,{,}其中<>的内容是必须的,{}的内容是可选的。

OPCODE指令助记符,COND执⾏条件,S是否影响CPSR中的值,Rd⽬标寄存器,Rn 第⼀个操作数的寄存器,OPERAND2第⼆个操作数。

灵活的使⽤第2个操作数“operand2”能够提⾼代码效率。

它有如下的形式:1)#immed_8r ——常数表达式;2)Rm——寄存器⽅式;3)Rm,shift——寄存器移位⽅式(ASR算术右移,LSL逻辑左移,LSR 逻辑右移,ROR循环右移,RRX带扩展的右移1位)。

COND执⾏条件:下⾯介绍ARM指令:1、存储器访问指令。

存储器访问指令分为单寄存器操作指令和多寄存器操作指令。

单寄存器操作指令LDR/STR指令⽤于对内存变量的访问、内存缓冲区数据的访问、查表、外围部件的控制操作等。

LDR:从内存到寄存器,加载数据。

STR:将寄存器的数据存储到内存。

LDRB操作字节,LDRH操作半字,LDRSH操作有符号半字。

多寄存器操作指令LDM为加载多个寄存器;STM为存储多个寄存器。

允许⼀条指令传送16个寄存器的任何⼦集或所有寄存器。

它们主要⽤于现场保护、数据复制、常数传递等。

进⾏数据复制时,先设置好源数据指针和⽬标指针,然后使⽤块拷贝寻址指令LDMIA/STMIA(传送后地址加4)、LDMIB/STMIB(传送前地址加4)、LDMDA/STMDA(传送后地址减4)、LDMDB/STMDB(传送前地址减4)进⾏读取和存储。

进⾏堆栈操作操作时,要先设置堆栈指针(SP),然后使⽤堆栈寻址指令STMFD/LDMFD(满递减堆栈)、STMED/LDMED(空递减堆栈)、STMFA/LDMFA(满递增堆栈)和STMEA/LDMEA(空递增堆栈)实现堆栈操作。

ARM指令的分类和主要指令。

分支指令、Load/Store指令、数据处理指令、程序状态寄存器指令、异常中断指令、协处理器

ARM有两种方法可以实现程序分支转移。

跳转指令:ARM跳转指令有以下4种:① B 分支指令②BL 带链接分支指令③BX 分支并可选地交换指令集④BLX 带链接分支并可选择地交换指令集。

长跳转指令:直接向PC寄存器(R15)中写入目标地址。

可以实现4GB地址空间中的任意跳转

Load/Store指令:单寄存器传输指令,多寄存器传输指令,交换指令

ARM数据处理指令大致分为以下6种类型:数据传送指令,算术运算指令,逻辑运算指令,比较指令,测试指令,乘法指令.

程序状态寄存器指令:读状态寄存器指令MRS,写状态寄存器指令MSR,指令举例,开中断与关中断

异常中断指令:复位(Reset),软件中断(software interrupt SWI),指令预取中止(Prefech Abort),数据访问中止(Data Abort),外部中断请求(IRQ),快速中断请求(FIQ)

ARM协处理器指令: ARM支持协处理器操作。

协处理器控制通过协处理器命令实现。

另外:

ARM伪指令: ARM伪指令不是ARM指令集中的指令,只是为了编程方便编译器定义了伪指令。

可以像其它ARM指令一样使用伪指令,但在编译时这些指令将被等效的ARM指令代替。

ARM伪指令有4条,分别为ADR伪指令、ADRL伪指令、LDR伪指令和NOP伪指令。

协处理器CP15使用介绍一、访问CP15寄存器的指令访问CP15寄存器指令的编码格式及语法说明如下:说明:<opcode_1>:协处理器行为操作码,对于CP15来说,<opcode_1>永远为0b000,否则结果未知。

<rd>:不能是r15/pc,否则,结果未知。

<crn>:作为目标寄存器的协处理器寄存器,编号为C0~C15。

<crm>:附加的目标寄存器或源操作数寄存器,如果不需要设置附加信息,将crm设置为c0,否则结果未知。

<opcode_2>:提供附加信息比如寄存器的版本号或者访问类型,用于区分同一个编号的不同物理寄存器,可以省略<opcode_2>或者将其设置为0,否则结果未知。

指令说明语法格式mcr 将ARM处理器的寄存器中的数据写到CP15中的寄存器中mcr{<cond>} p15, <opcode_1>, <rd>, <crn>, <crm>, {<opcode_2>}mrc 将CP15中的寄存器中的数据读到ARM处理器的寄存器中mcr{<cond>} p15, <opcode_1>, <rd>, <crn>, <crm>, {<opcode_2>}二、CP15寄存器介绍CP15的寄存器列表如下所示。

1.CP15的寄存器C0CP15中寄存器C0对应两个标识符寄存器,由访问CP15中的寄存器指令中的<opcode_2>指定要访问哪个具体物理寄存器,<opcode_2>与两个标识符寄存器的对应关系如下所示:1)主标识符寄存器访问主标识符寄存器的指令格式如下所示:mrc p15, 0, r0, c0, c0, 0 ;将主标识符寄存器C0,0的值读到r0中ARM不同版本体系处理器中主标识符寄存器的编码格式说明如下。

ARM RRX指令是一种协处理器指令,用于完成对通用寄存器中的内容进行带扩展的循环右移的操作。

该指令的格式为:通用寄存器,RRX操作数。

RRX指令可完成对通用寄存器中的内容进行带扩展的循环右移的操作,按操作数所指定的数量向右循环移位,左端用进位标志位C 来填充。

其中,操作数可以是通用寄存器,也可以是立即数(0~31)。

例如,MOV R0,R1,RRX#2;将R1中的内容进行带扩展的循环右移两位后传送到R0中。

此外,ARM微处理器还支持多达16个协处理器,用于各种协处理操作。

在程序执行的过程中,每个协处理器只执行针对自身的协处理指令,忽略ARM处理器和其他协处理器的指令。

在讲指令之前,先简单地介绍一下Cortex-M3 中支持的算术与逻辑标志。

本书在后面还会展开论述。

它们是:APSR 中的5 个标志位4.2.1 分类指令表表4.2 16位数据操作指令表4.3 16位转移指令IT If-Then表4.4 16位存储器数据传送指令16 数据传送指令没有任何新内容,因为它们是Thumb 指令,在v4T 时就已经定格了——译注表4.5 其它16位指令表4.6 32位数据操作指令UXTH 半字被无符号扩展到32 位(高16 位清0——译注)表4.7 32位存储器数据传送指令表4.8 32位转移指令表4.9 其它32位指令4.2.2 未支持的指令有若干条Thumb 指令没有得到Cortex-M3 的支持,下表列出了未被支持的指令,以及不支持的原因。

表4.10 因为不再是传统的架构,导致有些指令已失去意义未支持的指令以前的功能BLX #im 在使用立即数做操作数时,BLX 总是要切入ARM 状态。

因为Cortex-M3 只在Thumb 态下运行,故以此指令为代表的,凡是试图切入ARM 态的操作,都将引发一个用法fault。

SETEND由ARMv6 引入的,在运行时改变处理器端设置的指令(大端或小端)。

因为Cortex-M3 不支持动态端的功能,所以此指令也将引发faultCM3 也不支持有少量在ARMv7-M 中列出的指令。

比如,ARMv7M 支持Thumb2 的协处理器指令,但是CM3 却不能挂协处理器。

表4.11 列出了这些与协处理器相关的指令。

如果试图执行它们,则将引发用法fault(NVIC 中的NOCP (No CoProcessor)标志置位)。

表4.11 不支持的协处理器相关指令未支持的指令以前的功能MCR 把通用寄存器的值传送到协处理器的寄存器中MCR2把通用寄存器的值传送到协处理器的寄存器中MCRR 把通用寄存器的值传送到协处理器的寄存器中,一次操作两个MRC把协处理器寄存器的值传送到通用寄存器中MRC2 把协处理器寄存器的值传送到通用寄存器中MRRC把协处理器寄存器的值传送到通用寄存器中,一次操作两个LDC 把某个连续地址空间中的一串数值传送至协处理器中STC从协处理器中传送一串数值到地址连续的一段地址空间中还有一个是改变处理器状态指令(CPS),它的一些用法也不再支持。

指令格式:指令{条件}{S} {目的Regi ster},{OP1},{OP2} "{ }"中的内容可选。

即,可以不带条件只有目的寄存器,或只有目的寄存器和操作数1,也可以同时包含所有选项。

“S”决定指令的操作是否影响C PSR中条件标志位的值,当没有S时指令不更新C P SR中条件标志位的值助记符英文全称示例、功能跳转指令BBranch跳转指令B Label;程序无条件跳转到标号L a bel处执行BLBranch with Link带返回的跳转指令BL Label;当程序无条件跳转到标号L abel处执行时,同时将当前的P C值保存到R14中BLXBranch with Link and exchan ge带返回和状态切换的跳转指令BLX Label;从ARM指令集跳转到指令中所指定的目标地址,并将处理器的工作状态有A RM状态切换到Th umb状态,该指令同时将PC的当前内容保存到寄存器R14中BXBranch and exchan ge带状态切换的跳转指令BX Label;跳转到指令中所指定的目标地址,目标地址处的指令既可以是ARM指令,也可以是Th umb指令数据处理MOVMove数据传送MOV R1,R0,LSL#3;将寄存器R0的值左移3位后传送到R1MVNMove NOT数据非传送MVN R0,#0 ;将立即数0取反传送到寄存器R0中,完成后R0=-1CMPCompare比较指令CMP R1,R0;将寄存器R1的值与寄存器R0的值相减,并根据结果设置CPSR的标志位CMNCompare negati ve负数比较指令CMN R1,R0 ;将寄存器R1的值与寄存器R0的值相加,并根据结果设置CPSR的标志位TSTTest位测试指令TST R1,#0xffe;将寄存器R1的值与立即数0xff e按位与,并根据结果设置CPSR的标志位TEQTest equivalence相等测试指令TEQ R1,R2;将寄存器R1的值与寄存器R2的值按位异或,并根据结果设置CPSR的标志位ADDAdd加法运算指令ADD R0,R2,R3,LSL#1; R0 = R2 + (R3 << 1)ADCAdd with carry带进位加法ADCS R2,R6,R10; R2 = R6+R10+!C,且更新CPS R的进位标志位SUBSubtract减法运算指令SUB R0,R1,#256; R0 = R1 – 256SBCSubtract with carry带进位减法指令SUBS R0,R1,R2 ; R0 = R1 - R2 - !C,并根据结果设置CPSR的进位标志位RSBReverse subtra ct逆向减法指令RSB R0,R1,R2 ; R0 = R2 – R1RSCReverse subtra ct with carry带进位逆向减法指令RSC R0,R1,R2; R0 = R2 – R1 - !CANDAnd逻辑与操作指令AND R0,R0,#3;该指令保持R0的0、1位,其余位清零。

ARM指令集详解ARM可以用两套指令集:ARM指令集和Thumb指令集。

本文介绍ARM指令集。

在介绍ARM指令集之前,先介绍指令的格式。

1 指令格式(1)基本格式<opcode>{<cond>}{S} <Rd>,<Rn>{,<opcode2>}其中,<>内的项是必须的,{}内的项是可选的,如<opcode>是指令助记符,是必须的,而{<cond>}为指令执行条件,是可选的,如果不写则使用默认条件AL(无条件执行)。

opcode 指令助记符,如LDR,STR 等cond 执行条件,如EQ,NE 等S 是否影响CPSR 寄存器的值,书写时影响CPSR,否则不影响Rd 目标寄存器Rn 第一个操作数的寄存器operand2 第二个操作数指令格式举例如下:LDR R0,[R1] ;读取R1 地址上的存储器单元内容,执行条件ALBEQ DATAEVEN ;跳转指令,执行条件EQ,即相等跳转到DATAEVENADDS R1,R1,#1 ;加法指令,R1+1=R1 影响CPSR 寄存器,带有SSUBNES R1,R1,#0xD;条件执行减法运算(NE),R1-0xD=>R1,影响CPSR 寄存器,带有S(2)第2个操作数在ARM 指令中,灵活的使用第2个操作数能提高代码效率,第2个操作数的形式如下:#immed_8r常数表达式,该常数必须对应8 位位图,即常数是由一个8 位的常数循环移位偶数位得到。

合法常量0x3FC、0、0xF0000000、200、0xF0000001等都是合法常量。

非法常量0x1FE、511、0xFFFF、0x1010、0xF0000010等都是非法常量。

常数表达式应用举例如下:MOV R0,#1 ;R0=1AND R1,R2,#0x0F ;R2 与0x0F,结果保存在R1LDR R0,[R1],#-4 ;读取R1 地址上的存储器单元内容,且R1=R1-4Rm寄存器方式,在寄存器方式下操作数即为寄存器的数值。

ARM指令集ARM指令的基本格式ARM指令的基本格式为:<Opcode> {<Cond>} {S} <Rd>, <Rn> { , <Opcode2> }其中,<>内的项是必需的,{}内的项是可选的。

1)Opcode项Opcode是指令助记符,即操作码,说明指令需要执⾏的操作,在指令中是必需的。

2)Cond项(command)Cond项表明了指令的执⾏的条件,每⼀条ARM指令都可以在规定的条件下执⾏,每条ARM指令包含4位的条件码,位于指令的最⾼4位[31:28]。

条件码共有16种,每种条件码⽤2个字符表⽰,这两个字符可以添加⾄指令助记符的后⾯,与指令同时使⽤。

当指令的执⾏条件满⾜时,指令才被执⾏,否则指令被忽略。

如果在指令后不写条件码,则使⽤默认条件AL(⽆条件执⾏)。

指令的条件码条件码助记符后缀标志含义0000 EQ Z置位相等equal0001 NE Z清零不相等not equal0010 CS C置位⽆符号数⼤于或等于Carry Set0011 CC C清零⽆符号数⼩于0100 MI N置位负数minus0101 PL N清零正数或零plus0110 VS V置位溢出0111 VC V清零没有溢出1000 HI C置位Z清零⽆符号数⼤于high1001 LS Z置位C清零⽆符号数⼩于或等于less1010 GE N等于V 带符号数⼤于或等于1011 LT N不等于V 带符号数⼩于least1100 GT Z清零且(N等于V)带符号数⼤于great1101 LE Z清零或(N不等于V)带符号数⼩于或等于1110 AL 忽略⽆条件执⾏all1111条件码应⽤举例:例:⽐较两个值⼤⼩,并进⾏相应加1处理,C语⾔代码为:if ( a > b ) a++;else b++;对应的ARM指令如下(其中R0中保存a 的值,R1中保存b的值):CMP R0, R1 ; R0与R1⽐较,做R0-R1的操作ADDHI R0, R0, #1 ;若R0 > R1, 则R0 = R0 + 1ADDLS R1, R1, #1 ; 若R0 <= R1, 则R1 = R1 + 1CMP⽐较指令,⽤于把⼀个寄存器的内容和另⼀个寄存器的内容或⼀个⽴即数进⾏⽐较,同时更新CPSR中条件标志位的值。

ARM协处理器指令ARM 微处理器可支持多达 16 个协处理器,用于各种协处理操作,在程序执行的过程中,每个协处理器只执行针对自身的协处理指令,忽略 ARM 处理器和其他协处理器的指令。

ARM 的协处理器指令主要用于 ARM 处理器初始化 ARM 协处理器的数据处理操作,以及在ARM 处理器的寄存器和协处理器的寄存器之间传送数据,和在ARM 协处理器的寄存器和存储器之间传送数据。

ARM 协处理器指令包括以下 5 条:— CDP 协处理器数操作指令— LDC 协处理器数据加载指令— STC 协处理器数据存储指令— MCR ARM 处理器寄存器到协处理器寄存器的数据传送指令— MRC 协处理器寄存器到ARM 处理器寄存器的数据传送指令1、CDP 指令CDP 指令的格式为:CDP{条件} 协处理器编码,协处理器操作码1,目的寄存器,源寄存器1,源寄存器2,协处理器操作码2。

CDP 指令用于ARM 处理器通知ARM 协处理器执行特定的操作,若协处理器不能成功完成特定的操作,则产生未定义指令异常。

其中协处理器操作码1 和协处理器操作码2 为协处理器将要执行的操作,目的寄存器和源寄存器均为协处理器的寄存器,指令不涉及ARM 处理器的寄存器和存储器。

指令示例:CDP P3 , 2 , C12 , C10 , C3 , 4 ;该指令完成协处理器 P3 的初始化2、LDC 指令LDC 指令的格式为:LDC{条件}{L} 协处理器编码,目的寄存器,[源寄存器]LDC 指令用于将源寄存器所指向的存储器中的字数据传送到目的寄存器中,若协处理器不能成功完成传送操作,则产生未定义指令异常。

其中,{L}选项表示指令为长读取操作,如用于双精度数据的传输。

指令示例:LDC P3 , C4 , [R0] ;将 ARM 处理器的寄存器 R0 所指向的存储器中的字数据传送到协处理器 P3 的寄存器 C4 中。

3、STC 指令STC 指令的格式为:STC{条件}{L} 协处理器编码,源寄存器,[目的寄存器]STC 指令用于将源寄存器中的字数据传送到目的寄存器所指向的存储器中,若协处理器不能成功完成传送操作,则产生未定义指令异常。

其中,{L}选项表示指令为长读取操作,如用于双精度数据的传输。

指令示例:STC P3 , C4 , [R0] ;将协处理器 P3 的寄存器 C4 中的字数据传送到 ARM 处理器的寄存器R0 所指向的存储器中。

4、MCR 指令MCR 指令的格式为:MCR{条件}协处理器编码,协处理器操作码1,源寄存器,目的寄存器1,目的寄存器2,协处理器操作码2。

MCR 指令用于将ARM 处理器寄存器中的数据传送到协处理器寄存器中,若协处理器不能成功完成操作,则产生未定义指令异常。

其中协处理器操作码1 和协处理器操作码2 为协处理器将要执行的操作,源寄存器为ARM 处理器的寄存器,目的寄存器1 和目的寄存器2 均为协处理器的寄存器。

指令示例:MCR P3,3,R0,C4,C5,6;该指令将 ARM 处理器寄存器 R0 中的数据传送到协处理器 P3 的寄存器 C4 和 C5 中。

5、MRC 指令MRC 指令的格式为:MRC{条件}协处理器编码,协处理器操作码1,目的寄存器,源寄存器1,源寄存器2,协处理器操作码2。

MRC 指令用于将协处理器寄存器中的数据传送到ARM 处理器寄存器中,若协处理器不能成功完成操作,则产生未定义指令异常。

其中协处理器操作码1 和协处理器操作码2 为协处理器将要执行的操作,目的寄存器为ARM 处理器的寄存器,源寄存器1 和源寄存器2 均为协处理器的寄存器。

指令示例:MRC P3,3,R0,C4,C5,6;该指令将协处理器 P3 的寄存器中的数据传送到 ARM 处理器寄存器中. The ARM920T 有两个具体协处理器CP14调试通信通道协处理器调试通信通道协处理器DCC(the Debug Communications Channel提供了两个32bits寄存器用于传送数据,还提供了6bits通信数据控制寄存器控制寄存器中的两个位提供目标和主机调试器之间的同步握手。

通信数据控制寄存器以下指令在 Rd 中返回控制寄存器的值:MRC p14, 0, Rd, c0, c0此控制寄存器中的两个位提供目标和主机调试器之间的同步握手:位 1(W 位)从目标的角度表示通信数据写入寄存器是否空闲:W = 0 目标应用程序可以写入新数据。

W = 1 主机调试器可以从写入寄存器中扫描出新数据。

位 0(R 位)从目标的角度表示通信数据读取寄存器中是否有新数据:R = 1 有新数据,目标应用程序可以读取。

R = 0 主机调试器可以将新数据扫描到读取寄存器中。

注意调试器不能利用协处理器 14 直接访问调试通信通道,因为这对调试器无意义。

但调试器可使用扫描链读写DCC 寄存器。

DCC 数据和控制寄存器可映射到 EmbeddedICE 逻辑单元中的地址。

若要查看 EmbeddedICE 逻辑寄存器,请参阅您的调试器和调试目标的相关文档。

通信数据读取寄存器用于接收来自调试器的数据的 32 位宽寄存器。

以下指令在 Rd 中返回读取寄存器的值:MRC p14, 0, Rd, c1, c0通信数据写入寄存器用于向调试器发送数据的 32 位宽寄存器。

以下指令将 Rn 中的值写到写入寄存器中:MCR p14, 0, Rn, c1, c0注意有关访问 ARM10 和 ARM11 内核 DCC 寄存器的信息,请参阅相应的技术参考手册。

ARM9 之后的各处理器中,所用指令、状态位位置以及对状态位的解释都有所不同。

目标到调试器的通信这是运行于 ARM 内核上的应用程序与运行于主机上的调试器之间的通信事件顺序:1. 目标应用程序检查 DCC 写入寄存器是否空闲可用。

为此,目标应用程序使用 MRC 指令读取调试通信通道控制寄存器,以检查 W 位是否已清除。

2. 如果 W 位已清除,则通信数据写入寄存器已清空,应用程序对协处理器 14 使用 MCR 指令将字写入通信数据写入寄存器。

写入寄存器操作会自动设置W 位。

如果 W 位已设置,则表明调试器尚未清空通信数据写入寄存器。

此时,如果应用程序需要发送另一个字,它必须轮询 W 位,直到它已清除。

3. 调试器通过扫描链 2 轮询通信数据控制寄存器。

如果调试器发现 W 位已设置,则它可以读 DCC 数据寄存器,以读取应用程序发送的信息。

读取数据的进程会自动清除通信数据控制寄存器中的 W 位。

以下代码显示了这一过程AREA OutChannel, CODE, READONLYENTRYMOV r1,#3 ; Number of words to sendADR r2, outdata ; Address of data to sendpolloutMRC p14,0,r0,c0,c0 ; Read control registerTST r0, #2BNE pollout ; if W set, register still fullwriteLDR r3,[r2],#4 ; Read word from outdata; into r3 and update the pointerMCR p14,0,r3,c1,c0 ; Write word from r3SUBS r1,r1,#1 ; Update counterBNE pollout ; Loop if more words to be writtenMOV r0, #0x18 ; Angel_SWIreason_ReportExceptionLDR r1, =0x20026 ; ADP_Stopped_ApplicationExitSVC 0x123456 ; ARM semihosting (formerly SWIoutdataDCB "Hello there!"END调试器到目标的通信这是运行于主机上的调试器向运行于内核上的应用程序传输消息的事件顺序:1. 调试器轮询通信数据控制寄存器的 R 位。

如果 R 位已清除,则通信数据读取寄存器已清空,可将数据写入此寄存器,以供目标应用程序读取。

2. 调试器通过扫描链 2 将数据扫描到通信数据读取寄存器中。

此操作会自动设置通信数据控制寄存器中的 R 位。

3. 目标应用程序轮询通信数据控制寄存器中的 R 位。

如果该位已经设置,则通信数据读取寄存器中已经有数据,应用程序可使用 MRC 指令从协处理器14 读取该数据。

同时,读取指令还会清除 R 位。

以下显示的目标应用程序代码演示了这一过程AREA InChannel, CODE, READONLYENTRYMOV r1,#3 ; Number of words to readLDR r2, =indata ; Address to store data readpollinMRC p14,0,r0,c0,c0 ; Read control registerTST r0, #1BEQ pollin ; If R bit clear then loopreadMRC p14,0,r3,c1,c0 ; read word into r3STR r3,[r2],#4 ; Store to memory and; update pointerSUBS r1,r1,#1 ; Update counterBNE pollin ; Loop if more words to readMOV r0, #0x18 ; Angel_SWIreason_ReportExceptionLDR r1, =0x20026 ; ADP_Stopped_ApplicationExitSVC 0x123456 ; ARM semihosting (formerly SWIAREA Storage, DATA, READWRITEindataDCB "Duffmessage#"ENDCP15系统控制协处理器CP15 —系统控制协处理器(the system control coprocessor)他通过协处理器指令MCR和MRC提供具体的寄存器来配置和控制caches、MMU、保护系统、配置时钟模式(在bootloader时钟初始化用到)CP15的寄存器只能被MRC和MCR(Move to Coprocessor from ARM Register )指令访问MCR{cond} p15, , , , ,MRC{cond} p15, , , , ,其中L位用来区分MCR(L=1和MRC(L=0操作. CP15包括15个具体的寄存器如下-R0:ID号寄存器-R0:缓存类型寄存器-R1:控制寄存器-R2:转换表基址寄存器(Translation Table Base --TTB)-R3:域访问控制寄存器(Domain access control )-R4:保留-R5:异常状态寄存器(fault status -FSR)-R6:异常地址寄存器(fault address -FAR)-R7:缓存操作寄存器-R8:TLB操作寄存器-R9:缓存锁定寄存器-R10:TLB 锁定寄存器-R11-12&14:保留-R13:处理器ID-R15:测试配置寄存器 2-24要注意有2个R0,根据MCR操作数的不同传送不同的值,这也一个只读寄存器-R0:ID号寄存器这是一个只读寄存器,返回一个32位的设备ID号,具体功能参考ARM各个系列型号的的CP15 Register 0说明.MRC p15, 0, , c0, c0, {0, 3-7} ;returns ID以下为ID Code详细描叙(ARM926EJ-S; ARM920T Part Number为0x920,Architecture (ARMv4T 为0x2具体可参照ARM各型号.-R0:缓存类型寄存器(CACHE TYPE REGISTER),包含了caches的信息。