3. Memory Addressing

- 格式:ppt

- 大小:474.50 KB

- 文档页数:30

Course Design for Computer Organization and Design4th EditionIntroductionThe course design for Computer Organization and Design (COD) 4th edition is designed to provide students with an understanding of the fundamental principles of computer organization and design. The course is divided into three mn units: the first unit covers the basic principles of digital logic and circuit design, the second unit covers the architecture and organization of computer systems, and the third unit covers advanced topics such as parallel processing and memory hierarchies.Course ObjectivesUpon completion of the course, students will be able to: - Understand the basic principles of digital logic and circuit design, including boolean algebra, gates, and flip-flops - Understand the architecture and organization of basic computer systems, including the CPU, memory, and I/O devices - Design and implement basic digital circuits using logic gates and flip-flops - Understand the purpose and function of assembly language and machine language, including instruction sets, memory addressing modes, and CPU operations - Understand the basic principles of pipelining and parallel processing, including pipelined CPU design and parallel processing architectures - Understand the principles of memory hierarchies and caching, including the function and organization of cache memoryCourse Outline•Unit 1: Digital Logic and Circuit Design–Introduction to digital logic–Boolean algebra and logic gates–Flip-flops and sequential circuits–Design of basic digital circuits•Unit 2: Computer System Organization and Architecture–Introduction to computer system organization–CPU organization and instruction sets–Memory organization and addressing modes–Input/output (I/O) devices and interfaces–Assembly language programming and machine language •Unit 3: Advanced Topics in Computer Organization and Design –Pipelining and parallel processing–Cache memory and memory hierarchies–Advanced CPU design and architectures–High-performance computer systemsCourse Delivery and AssessmentThe course will be delivered through a combination of lectures, tutorials, and laboratory work. There will be a mid-term exam and afinal exam as well as regular assessments throughout the course. The lab work will be designed to provide hands-on experience with digitalcircuit design, CPU design, and assembly language programming.ConclusionThe design of the COD 4th edition course is intended to provide a strong foundation in the principles of computer organization and design. By the end of the course, students will have gned the skills necessary to design and implement basic digital circuits and understand the architecture and organization of computer systems. With the rapid changes and developments in computer hardware, it is essential for students to have a solid understanding of the fundamental principles underlying computer systems.。

1. a. b.2.3.4. 1. 2. 1. 2. Homework 12Programming in binary machine language1. Register manipulationCopy a value from register R2 into register R3 usingOnly one ADD instructionOnly one AND instructionClear value of register R5 using only one instructionUsing only one instruction, increment value in register R6 by 1.Using only one instruction, decrement value in register R5 by 2.2. Memory addressingUsing only one instruction, read value from memory located 20 memory locations away from the address stored in PC.Using only one instruction, generate and store in R5 address of a memory location 20 memory locations away from the current PC. Thendemonstrate how the address stored in R5 can be used to access memory at that address.3. Patt & Patel 6.4Systematically decompose the problem 6.4 from Patt & Patel textbook to the level of LC-3 instructions, then write LC-3 instructions to implement your solution. You may change the contents of R0, R1, and R2. Turn in your flow chart and LC-3 instructions in binary. For credit, each instruction must be annotated with a comment in RTL or assembly.4. 2nAssuming that R4 contains a positive value less than 15, put the value 2 into R3. You may change the contents of R3 and R4. Systematically R4decompose the problem to the level of LC-3 instructions, then write LC-3 instructions to implement your solution. Turn in your flow chart and LC-3 instructions in binary. For credit, each instruction must be annotated with a comment in RTL or assembly.5. Sum of sequenceAssuming that R5 contains a strictly positive number, compute the sum of integers from 1 to R5 and store the result in R2. You may change the contents of R2 and R5. Systematically decompose the problem to the level of LC-3 instructions, then write LC-3 instructions to implement your solution. Turn in your flow chart and LC-3 instructions in binary. For credit, each instruction must be annotated with a comment in RTL or assembly.6. Patt & Patel 6.16Solve problem 6.16 from Patt & Patel. Stop your execution trace when the PC reaches x3003, and do not fill in row x3003 of the table in your solution.7. Printing a lineTwo students are trying to print a line of periods bounded by asterisks to the console. The line is supposed to have N – 2 periods, where N 2. Forexample, when N = 8, they want to print, “” to the console (without quotes). Each student came up with a systematic decomposition that appears very *......*different from the other student's solution. Look at the two approaches, as represented by the flow charts below.Explain which approach is the better of the two and why you believe it to be better.Imagine that one must replace each box labeled “print ‘*’” with a complex algorithm requiring almost 1,000 LC-3 instructions toimplement. Repeat your comparison between the two approaches after the replacement described, again explaining why you believe your choiceto be the better one.Homework 12 is due on Wednesday, May 6, at the start of the lecture. Remember to include your (e.g.Discussions section ED1) andfollow the complete submission guidelines.Homework Please ask all questions about this assignment during the office hours, or post them on .piazza For your programs: write the instruction address, the binary LC-3 instruction, and the corresponding or assembly in the following format:RTL 0001 001 010 1 00100 ; R1 R2 + 40001 001 010 1 00100 ; ADD R1, R2, #4Note how .bits are arranged in groups that correspond to instruction-specific operands If you are not sure about the RTL format of a certain instruction, you can refer to Appendix A of your Patt & Patel text or read sections 5.5 and6.1. Try to make your program as simple and intuitive as you can.。

addressing 翻译"Addressing"的中文翻译是“寻址”或“地址”。

在不同的语境下,该词可以有不同的含义和用法。

1. 在计算机领域中,"addressing"指的是计算机系统中对数据或指令的访问和定位。

例如:“The addressing mode determines how a memory address is calculated.”(寻址模式决定了如何计算内存地址。

)2. 在邮件或信函中,"addressing"是指写明收件人的地址和称呼。

例如:“Please make sure you put the correct addressing on the envelope before mailing it.”(请确保在信封上正确填写收件人的地址。

)3. 在社交场合中,"addressing"指的是对他人的称呼和对话方式。

例如:“When addressing someone older or in a position of authority, it is respectful to use their proper title and last name.”(当与年长者或权威人士交谈时,使用他们的正确头衔和姓氏是表示尊重的方式。

)4. "addressing"也可以表示解决或处理问题。

例如:“The government is actively addressing the issue of climate change.”(政府正在积极解决气候变化问题。

)总结一些常用的用法和中英文对照例句:- "Addressing mode" 寻址模式- "Addressing an envelope" 填写信封地址- "Proper addressing" 正确的称呼方式- "Addressing a problem" 解决问题希望以上内容能够满足您的需求。

address 记忆方法

记忆地址(Memory Address)通常是指计算机内存中的位置,每个存储单元都有一个唯一的地址。

在计算机科学中,有一些方法可以帮助记忆和理解地址的概念:

1. 类比:将计算机内存想象成一排邮箱或者邮寄信件的邮箱。

每个邮箱都有一个唯一的地址,就像内存中的每个存储单元有一个唯一的地址。

通过地址,我们可以找到特定的邮箱或存储单元。

2. 使用十六进制:内存地址通常以十六进制表示。

十六进制使用数字 0-9 和字母 A-F 表示 16 进制数字,比起十进制更加紧凑。

例如,地址 0x00400000 表示一个内存地址,前缀 "0x" 表示这是一个十六进制数。

3. 分层结构:将内存看作是一种分层结构,从低地址到高地址。

低地址通常是存储在计算机中的数据、代码等的起始位置,高地址则是结束位置。

这类似于书的页码,其中页码 1 是书的开头,而页码 n 是书的结尾。

4. 实际场景:将内存地址与现实世界中的物理地址或位置联系起来。

例如,内存地址可以被视为计算机内存的街道和房屋号码,每个房屋都有一个唯一的地址。

5. 图形表示:使用图表或图形来表示内存地址的布局。

将内存划分为不同的区域,例如堆、栈、代码段等,可以帮助理解每个区域的作用和范围。

1/ 2

6. 与变量关联:将内存地址与变量关联起来。

变量在内存中存储,并有一个地址。

理解变量如何存储在内存中以及如何通过地址访问这些变量可以帮助记忆地址的概念。

记忆地址的方法因人而异,选择适合自己的方法可以更容易理解和记忆计算机内存中的地址。

2/ 2。

x641. Introduction to x64 Architecturex64, also known as x86-64 or AMD64, is a 64-bit extension of the x86 instruction set architecture. It was developed by AMD and later adopted by Intel. The x64 architecture offers several advantages over its 32-bit predecessor, including increased memory addressing capabilities, improved floating-point performance, and support for more general-purpose registers.2. Memory Addressing in x64In x64 architecture, the memory addressing space is expanded from 32 bits to 48 bits, allowing for a theoretical maximum of 256 TB of addressable memory. This increase in memory space is particularly beneficial for applications that require large amounts of memory, such as scientific simulations, database management systems, and virtualization.3. Registers in x64One of the key differences between x64 and x86 is the increased number of general-purpose registers. While x86 architecture has only 8 general-purpose registers, x64 architecture provides 16 general-purpose registers, including 8 integer registers (RAX, RBX, RCX, RDX, RSI, RDI, RBP, RSP) and 8 additional registers (R8, R9, R10, R11, R12, R13, R14, R15).4. Instruction Set ExtensionsThe x64 architecture introduced several new instruction set extensions, including SSE (Streaming SIMD Extensions), SSE2, SSE3, SSSE3, SSE4, AVX (Advanced Vector Extensions), AVX2, and AVX-512. These extensions provide support for parallel processing, floating-point operations, and other performance-enhancing features. Software developers can take advantage of these extensions to optimize their applications for the x64 architecture.5. Software CompatibilityOne important consideration when migrating from x86 to x64 is software compatibility. Most 32-bit applications can still run on a 64-bit operating system using a compatibility layer called WoW64 (Windows-on-Windows 64). However, some applications may require updates or modifications to work properly in a 64-bit environment. It is recommended to test and validate applications before deploying them on a x64 system.6. Performance BenefitsThe x64 architecture offers several performance benefits over its 32-bit predecessor. The increased memory addressing space allows applications to access more memory, resulting in improved performance for memory-intensive tasks. The additional general-purpose registers provide more storage for data manipulation, reducing the need for memory access. Furthermore, the instruction set extensions enable more efficient parallel processing and floating-point operations, resulting in faster execution of many applications.7. ConclusionThe x64 architecture provides significant enhancements over the previous x86 architecture. With its increased memory addressing capabilities, improved floating-point performance, and expanded set of general-purpose registers, x64 can handle more demanding applications and deliver better overall performance. Software developers should consider optimizing their applications for the x64 architecture to take full advantage of its benefits.。

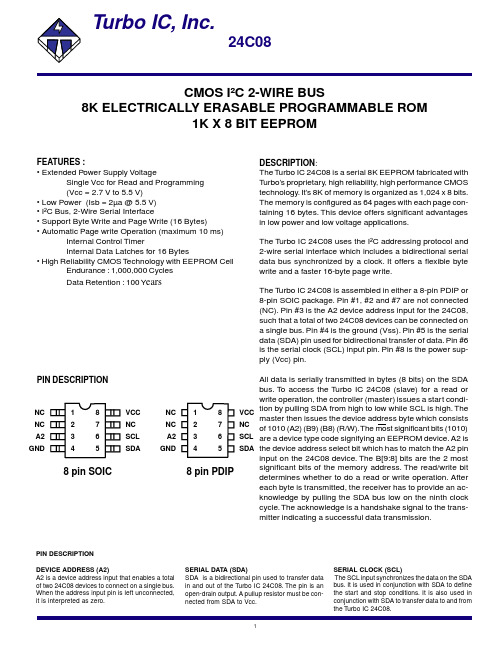

Chapter 5 Computer OrganizationKnowledge point:5.1. three subsystems that make up a computer5.2. functionality of each subsystem5.3. memory addressing and calculating the number of bytes5.4. addressing system for input/output devices.5.5. the systems used to connect different components together.Multiple-choice Questions39. The ___ is a computer subsystem that performs operations on data.( Knowledge point 5.1)a. CPUb. memoryc. I/O hardwared. none of the above40. ____ is a stand-alone storage location that holds data temporarily. ( Knowledge point 5.1)a. An ALUb. A registerc. A control unitd. A tape drive41. ____ is a unit that can add two inputs. ( Knowledge point 5.2)a. An ALUb. A registerc. A control unitd. A tape drive42. A register in a CPU can hold ____.( Knowledge point 5.2)a. datab. instructionsc. program counter valuesd.all of the above43. A control unit with five wires can define up to ____ operations. ( Knowledge point 5.2)a. 5b. 10c. 16d. 3244. A word is ____ bits. ( Knowledge point 5.3)a. 8b. 16c. 32d. any of the above45. If the memory address space is 16 MB and the word size is 8 bits, then ____ bits are needed to access each word. ( Knowledge point 5.3)a. 8b. 16c. 24d.3246. The data in ____ are erased if the computer is powered down. ( Knowledge point5.5.3)a. RAMb. ROMc. a tape drived. a CD-ROM47. ____ is a memory type with capacitors that need to be refreshed periodically. ( Knowledge point 5.3)a. SRAMb. DRAMc. ROMd. all of the above48. ____ is a memory type with traditional flip-flop gates to hold data. ( Knowledge point 5.3)a. SRAMb. DRAMc. ROMd. all of the above49. There are ____ bytes in 16 terabytes. ( Knowledge point 5.3)a.b.c.d.50. ____ can be programmed and erased using electronic impulses but can remain ina computer during erasure. ( Knowledge point 5.3)a. ROMb. PROMc. EPROMd. EEPROM51. ____ is a type of memory in which the user, not the manufacturer, storesprograms that cannot be overwritten. ( Knowledge point 5.3)a. ROMc. EPROMd. EEPROM52. CPU registers should have ____ speed memory. ( Knowledge point 5.3)a. highb. mediumc. lowd. any of the above53. Main memory in a computer usually consists of large amounts of ____ speedmemory. ( Knowledge point 5.3)a. highb. mediumc. lowd. any of the above54. The ____ memory contains a copy of a portion of main memory. ( Knowledge point 5.3)a. CPUb. cachec. maind. ROM55. The ____ is nonstorage I/O device. ( Knowledge point 5.4)a. keywordb. monitorc. printerd. all of the above56.A ____ is an optical storage device. ( Knowledge point 5.4)a. CD-ROMb. CD-Rc. CD-RMd. all of the above57. The ____ is a storage device in which the manufacturer writes information to the disc. ( Knowledge point 5.4)a. CD-ROMb. CD-Rc. CD-RMd. all of the above58. The ____ is a storage device in which the user can writes information only onceto the disc. ( Knowledge point 5.4)a. CD-ROMb. CD-Rc. CD-RMd. all of the above59. The ____ is a storage device that can undergo multiple writings and erasings. ( Knowledge point 5.4)b. CD-Rc. CD-RMd. all of the above60. The smallest storage area on a magnetic disk that can be accessed at one time isa ____.( Knowledge point 5.4)a. trackb. sectorc. framed. head61. For a magnetic disk, the ____ time is the time it takes for the read/write head tomove to the desired track where the data are stored. ( Knowledge point 5.4)a. rotationb. seekc. transferd. location62. Polycarbonate resin is used in ____ . ( Knowledge point 5.4)a. CD-ROMsb. CD-Rsc. CD-RWsd. all of the above63. In a ____, a high-power laser beam simulates pits in an alloy of silver, indium,antimony, and tellurium. ( Knowledge point 5.4)a. CD-ROMb. CD-Rc. CD-RMd. all of the above64. In a ____, a high-power laser beam simulates pits in the dye layer. ( Knowledge point 5.4)a. CD-ROMb. CD-Rc. CD-RMd. all of the above65. Which optical storage device has the highest capacity ? ( Knowledge point 5.4)a. CD-ROMb. CD-Rc. CD-RMd. DVD66. In a DVD, a ____ beam reads the disk. ( Knowledge point 5.4)a. high-power laserb. infraredc. red laserd. blue laser67. A ____ bus connects the CPU and memory. ( Knowledge point 5.5)a. datab. addressc. controld. all of the above68. If the word size is 2 bytes, a data bus with ____ wires is needed. ( Knowledge point 5.5)a. 2b. 4c. 8d. 1669. If the memory has words, the address bus needs to have ____ wires. ( Knowledge point 5.5)a. 8b. 16c. 32d. 6470. A control bus with eight wires can define ____ operations. ( Knowledge point 5.5)a. 8b. 16c. 256d. 51271. The ____ controller features a parallel interface and daisy-chained connection forI/O devices. ( Knowledge point 5.5)a. SCSIb. Fire Wirec. USBd. IDE72. The ____ controller is a serial device that connects slow devices such as thekeyboard and mouse to the computer. ( Knowledge point 5.5)a. SCSIb. Fire Wirec. USBd. IDE73. The ____ controller is a high-speed serial interface that transfers data in packets. ( Knowledge point 5.5)a. SCSIb. Fire Wirec. USBd. IDE74. The three steps in the running of a program on a computer are performed ____in this specific order. ( Knowledge point 5.5)a. fetch, execute, and decodeb. fetch, execute, and fetchc. fetch, decode, and executed. decode, fetch, and execute75. In the ____ method to synchronize the operation of the CPU with the I/Odevice ,the I/O device informs the CPU when it is ready for data transfer.( Knowledge point 5.5)a. programmed I/Ob. interrupt-driven I/Oc. DMAd. isolated I/O76. In the ____ method to synchronize the operation of the CPU with the I/O device,the CPU is idle until the I/O operation is finished. ( Knowledge point 5.5)a. programmed I/Ob. interrupt-driven I/Oc. DMAd. isolated I/O77. In the ____ method to synchronize the operation of the CPU with the I/O device,a large block of data can be passed from an I/O device to memory directly.( Knowledge point 5.5)a. programmed I/Ob. interrupt-driven I/Oc. DMAd. isolated I/OReview questions:1. What are the three subsystems that make up a computer?(Knowledge point 5.1) Answer: the CPU, main memory, and the input/output (I/O) subsystem.2. What are the parts of a CPU? (Knowledge point 5.1)Answer: The CPU performs operations on data and has a ALU, a control unit, and a set of registers.3. What‘s the function of the ALU? (Knowledge point 5.2)Answer: The ALU performs arithmetic and logical operations.Exercises:78. A computer has 64MB of memory. Each word is 4 bytes. How many bits are needed to address each single word in memory? (Knowledge point 5.3)Solution:The memory address space is 64 MB, that is 2 raised to the power 26. The size of each word in bytes is 2 raised to the power 2. So we need 24(subtract 2 from 26) bits to address each single word in memory.79. How many bytes of memory are needed to store a full screen of data if the screen is made of 24 lines with 80 characters in each line? The system uses ASCII code, witheach ASCII character store as a byte. (Knowledge point 5.3)Solution:The quantity of bytes in a full screen is 1920 (24*80) while the system uses ASCII code with each ASCII character store as a byte. So we need 1920 bytes of memory to store the full screen of data.80. An imaginary computer has four data registers(R0 to R3), 1024 words in memory, and 16 different instructions(add, subtract, etc.). What is the minimum size of an instruction in bits if a typical instruction uses the following format: add 565 R2. (Knowledge point 5.5)Solution:The number of data registers in this computer is 4, that is 2 raised to the power 2. The number of words in this computer is 1024, that is 2 raised to the power 10. The number of instructions in this computer is 16, that is 2 raised to the power 4. So the minimum size of an instruction in bits is 16 (2+10+4) bits.81. If the computer in Exercise 80 uses the same size of word for data and instructions. What is the size of each data register? (Knowledge point 5.5) Solution:The size of an instruction in bits is 16. Data size is the same with that of an instruction. So 16 is the size of each data register.82. What is the size of the instruction register of the computer in Exercise 80? (Knowledge point 5.5)Solution:The size of an instruction in bits is 16. So the size of the instruction register of the computer is also 16.83. What is the size of the program counter of the computer in Exercise 80? (Knowledge point 5.5)Solution:The number of words in this computer is 1024, that is 2 raised to the power 10. So the size of the program counter of the computer is 10.84. What is the size of the data bus in Exercise 80? (Knowledge point 5.5) Solution:Data size of this computer in bits is 16. So the size of the data bus is 16.85. What is the size of the address bus in Exercise 80? (Knowledge point 5.5) Solution:The number of words in this computer is 1024, that is 2 raised to the power 10. So the the size of the address bus is 10.86. What is the minimum size of the control bus in Exercise 80? (Knowledge point5.5)Solution:There are 2 control actions(read and write to memory) at most. So the minimum size of the control bus is 1.87. A computer uses isolated I/O addressing. Memory has 1024 words. If each controller has 16 registers, how many controllers can be accessed by this computer? (Knowledge point 5.4)Solution:Memory has 1024 words. So the address space is 1024. Each controller has 16 registers. Then we get 64 (divide 16 by 1024)controllers which can be accessed by this computer.88. A computer uses memory-mapped I/O addressing. The address bus uses 10 lines. If memory is made of 1000 words, how many four-register controllers can be accessed by this computer? (Knowledge point 5.4)Solution:The address bus uses 10 lines. So, the address space is 1024(2 raised to the power 10). The memory is made of 1000 words and each controller has four registers. Then we get (1024-1000)/4 = 6 four-register controllers which can be accessed by this computer.。

1. The production of control signal in Control Unit doesn’t depend on __________.A. clock signalB. operation code in instructionC. read / write signalD. flags given by having executed instruction2. The simplest instruction execution may include ______cycle(s).A. 4B. 3C. 2D. 13. _________ found the fact on the number of transistors on a single chip doubled per year.A. Bill GatesB. Gordon MooreC. William StallingsD. John vonNeumann4. Pipeline pursues(追求)______in a stage.A. some instruction’s overlapB. an instruction’s different cycle’s overlapC. some instruction’s different stages overlapD.some processes(进程) overlap5. The main functions of ALU are ______.A. logic operationsB. both A & CC. arithmetic operationsD. only addition6. In an instruction, source or result operands can not in ______.A. main memoryB. CPU registerC. external storageD. I/O7. Some type of instruction limit the pipeline’s performance , the wors t one is ____ .A. I/O instructionsB. conditional branch instructionC. Arithmetic instructionD. data transfer instructions8. The IMMEDIATE ADDRESSING means___.A. operand includes in instructionB. address of operand’s a ddress included in instructionC. operand been unnecessaryD. operand’s address included in instruction9. The address is known as a type of data, because it is represented by ______.A. a number of floating pointB. a signed integerC. an unsigned integerD. a number of decimal10.If two’s complement 1000 0111 and 0111 1000 are added, the sum in decimal representation is ______.A. –1 .B. –127C. +255D. overflow11. The aim of the interrupt cycle is to ________.A. get an operandB. branch to ISRC. return from ISRD. fetch an instruction12. In RAID, __________ is most important.A. to enlarge capacity of available data in disk systemB. to enable the recovery of data lost due to a disk failureC. to find and correct the read/write errorsD. to improve I/O request rate of system13. The 8-bit twos complement 1010 1101 is changed to a 16-bit _____________.A. 0000 0000 0101 0011B. 1111 1111 1010 1101C. 0000 0000 1010 1101D. 10000000 0010 110114. RAID level(s)_________make use of an independent access technique.A. 3B. 4C. 2D. all15. The disadvantage of Indirect ADDRESSING is ___________ .A. more memory referenceB. large value rangeC. less memory referenceD. limit value range16. After an instruction is fetched, the address of the operand may be in ______ register.A.MARB. SPC. MBRD. PC17. DMA means ______.A.CPU Directly Manages Address busB.“Direct Memory Addressing” modeC.Another Magnetic DisksD.I/O Directly Accesses Memory data18. On address mapping of cache, any block of main memory must be mapped to fixed line of cache, it is ___________ .A.Associative Mapping B。