基于fpga的点阵显示控制器的设计 (1)

- 格式:doc

- 大小:262.50 KB

- 文档页数:19

基于FPGA控制实现点阵列显示的设计

赵可萍;王炜

【期刊名称】《现代电子技术》

【年(卷),期】2006(29)6

【摘要】点阵列显示控制技术在工业控制、家电产品和广告设计中应用广泛.讨论了利用FPGA控制实现多路点阵列显示的技术,对以FPGA芯片为核心,扩展并行I/O接口,实现多路点阵列显示的硬件电路进行了分析,介绍了其设计思想、层次结构,在Max+PlusⅡ平台下,利用编程和图形文件结合的方法实现了软件设计,经波形仿真验证后,进行了硬件电路的实现.实践证明,该系统工作正常,显示的字型准确、稳定.

【总页数】2页(P110-111)

【作者】赵可萍;王炜

【作者单位】天津工业大学,信息与通信工程学院,天津,300160;天津工业大学,信息与通信工程学院,天津,300160

【正文语种】中文

【中图分类】TP273

【相关文献】

1.基于FPGA的液晶显示控制器的设计与实现 [J], 盛象飞

2.基于 FPGA 的 LED 显示屏控制系统的设计与实现 [J], 郑争兵;赵峰

3.基于FPGA的通用液晶显示控制器的设计和实现 [J], 王鸣浩;吴小霞

4.基于FPGA的VGA图像显示及控制系统的设计与实现 [J], 李营;吕兆承;陈帅;权循忠

5.基于FPGA的LCD动态显示控制系统设计与实现 [J], 李璐;余英

因版权原因,仅展示原文概要,查看原文内容请购买。

点阵显示LED点阵就是由发光二极管组成的矩阵,我们下面介绍的8*8点阵,即是8行*8列LED构成。

下面是共阳8*8点阵的内部结构图:从图中可以看出在横向上,每行LED的阳极连在一块,并引出一个引脚到外面;在竖向上,每列的LED阴极连在一块,并引出一个引脚到外面。

所以,要让某行某列的LED亮,就要使该行引出的引脚接高电平,该列引出的引脚接低电平。

好了,我们现在说一下驱动方法。

由于每行(每列)LED的一个极被连在一块,所以这个驱动方法只能是动态扫描法。

从本质上来讲同数码管的动态扫描方法是类似的。

结合VHDL程序,我们来解说一下如何让点阵产生隔列的亮竖柱(第一列亮,第二列灭,第三列亮,第四列灭,依次类推)。

首先我们定义两个数组:line:out std_logic_vector(7 downto 0)--点阵列;row:out std_logic_vector(7 downto 0)--点阵行。

line(0)对应于第一列的引脚输入,其它成员对应关系依次类推,row(0)对应于第一行的引脚输入,其它成员对应关系依次类推。

时刻1:首先我们置line 为0XFE,即第一列的引脚置低电平0,其余列的引脚置高电平1,这样,只有第一列上的LED可根据row的值来点亮或者熄灭,其余列上的LED不管row值是什么,都是灭的。

与此同时,把row置为0xFF,即全部为高电平1,这样结合“只有第一列上的LED可根据row的值来点亮或者熄灭,其余列上的LED不管row值是什么,都是灭的”的状态,只有第一列上的LED全亮。

第一个竖柱点亮了。

紧接着,时刻2:置line为0xFF,即所有列上的led都是灭的,不管row上的值是什么值。

第二个竖柱是灭的。

然后,时刻3:置line为0XFB,即只有第三列的引脚是高电平,其余列的引脚都是低电平,这样,只有第三列上的LED可根据row值来点亮或者熄灭,其余列上的LED不管row值是什么,都是灭的。

基于fpga的点阵显示控制器的设计介绍随着电子信息技术的发展,数字化技术已经在我们的生活中扮演了越来越重要的角色。

在数字化技术的发展过程中,点阵显示控制器(Dot Matrix Display Controller)显得尤为重要。

点阵显示控制器是在数字微处理器的控制下,实现多晶体管、LED等光电子件按照一定规律组成的字符与图形的集成,其应用范围极广。

本文将介绍基于FPGA的点阵显示控制器的设计。

基本原理点阵显示器的基本工作原理是通过控制数字微处理器输出的数据位和控制口信号的电平来控制各个列和行上的LED或LCD点按照一定的规律显示。

点阵显示器的显示控制方法有两种:静态显示控制和动态显示控制。

静态显示控制指的是显示内容在特定的时间段内固定不变,而动态显示控制则是指显示内容在不断变化。

在点阵显示控制器的设计中,静态显示控制是一般应用较为广泛的方式。

FPGA是一种基于可编程逻辑门阵列的数字逻辑器件,它具有高度的可编程性、高速度、高可靠性等优点。

在点阵显示控制器的设计中,使用FPGA可以有效提高点阵控制器的运行速度和可靠性。

基于FPGA的点阵显示控制器的设计方法主要包括以下几个步骤:1. 确定显示器的列数和行数点阵显示器的列数和行数决定了显示器的分辨率。

在设计时,需要根据实际需求确定显示器的列数和行数。

一般来说,显示器的列数和行数越多,显示的内容就越清晰,但是对控制器的要求也就越高。

2. 确定点阵控制器的工作频率点阵显示控制器的工作频率决定了控制器的运行速度。

在设计时,需要根据实际需求确定点阵控制器的工作频率,以确保控制器的运行速度能够满足设计要求。

3. 设计点阵控制器的逻辑电路在确定点阵控制器的工作频率和分辨率后,需要设计点阵控制器的逻辑电路。

这里主要包括点阵控制器的时序控制、数据存储和输出控制等。

在完成点阵控制器的逻辑电路设计后,需要进行硬件电路的实现。

在硬件电路的实现过程中,需要将逻辑电路转化为硬件电路,并进行相应的布线和连接。

东华理工大学长江学院毕业论文题目:基于FPGA点阵显示屏设计(软件)Title: Design of Dot Matrix Screen based on FPGA二零一贰年六月摘要本设计是一16×16点阵LED电子显示屏的设计。

整机以EP2C5T144C8N为主控芯片,介绍了以它为控制系统的LED点阵电子显示屏的动态设计和开发过程。

通过该芯片控制一个行驱动器74HC154和两个列驱动器74HC595来驱动显示屏显示。

该电子显示屏可以显示各种文字或单色图像,采用4块8 x 8点阵LED显示模块来组成16x16点阵显示模式。

显示采用动态显示,使得图形或文字能够实现静止、移入移出等多种显示方式。

文中详细介绍了LED点阵显示的硬件设计思路、硬件电路各个部分的功能及原理、相应软件的程序设计,以及使用说明等。

控制系统程序采用FPGA编辑,通过编程控制各显示点对应LED阳极和阴极端的电平,就可以有效的控制各显示点的亮灭。

所显示字符的点阵数据可以自行编写(即直接点阵画图),也可从标准字库中提取。

LED显示以其组构方式灵活、显示稳定、功耗低、寿命长、技术成熟、成本低廉等特点在车站、证券所、运动场馆、交通干道及各种室内/外显示场合的信息发布,公益宣传,环境参数实时,重大活动倒计时等等得到广泛的应用。

设计结果证明,该系统性能稳定,结构合理,具有横向扩展拼接功能。

关键词: LED FPGH 硬件描述语言ABSTRACTThe design is a 16 × 16 dot matrix LED display design. The machine to EP2C5T144C8N as the main chip, LED dot-matrix electronic display for the control system it dynamic design and development process. Through the chip to control a line drive 74HC154 and two drive 74HC595 to drive the display shows. The electronic screen can display text or monochrome images, four 8 x 8 dot matrix LED display module to form a 16x16 dot matrix display mode. Displays the dynamic display, graphics or text to achieve stationary, moved out of the other display.LED dot matrix display hardware design ideas, features and principles of the various parts of the hardware circuit, the corresponding software programming, and instructions for use, etc. in detail.Control system using FPGA Editor, by programming the control point corresponds to the LED anode and cathode level, can effectively control the display point bright off. Shows the character of the lattice data can write your own (ie, direct dot drawing) can also be extracted from the standard font.LED display with its group structure is flexible, showing a stable, low power consumption, long life, mature technology, low cost and other characteristics of the station, securities, sports venues, major trunk roads and a variety of indoor / outdoor occasions, information dissemination, public promotion, environmental parameters in real time, the major activities of the countdown has been widely used.The design results show that the system is stable performance, reasonable structure, with horizontal expansion splicing. Keywords: LED FPGH hardware description language目录第一章绪论 (1)1.1FPGA的发展历史和发展方向 (1)1.2FPGA的应用 (3)1.3LED的定义和特点 (4)1.4LED简介 (5)1.5LED显示屏的分类 (7)第二章系统整体设计方案 (8)2.1需要实现的功能 (8)2.2显示模式方案论证 (8)2.3显示数据传输方案论证 (9)第三章硬件设计 (10)3.1FPGA最小系统 (10)3.2FPGA硬件系统的设计技巧 (13)3.4列驱动电路 (14)3.5行驱动电路 (17)3.6点阵LED电子显示屏电路 (18)第四章系统程序的设计 (20)4.1系统主程序 (20)第五章调试及仿真 (21)5.1系统开发工具介绍 (21)5.2调试与仿真 (21)5.3编译 (23)5.4时序仿真 (24)结论 (26)致谢 (27)参考文献 (28)附录一 (29)第一章绪论随着FPGA的不断发展,应用于生活当中屡见不鲜。

基于FPGA 的8*8点阵显示器学院名称:电 信 学 院专 业: 电气工程及其自动化专业班 级: 08电气2姓 名: 韩 韬同组姓名: 董 立 峰学 号:指导教师姓名: 宋伟 黄成2010 年 12 月JIANGSU TEACHERS UNIVERSITY OF TECHNOLOGY 数字电路课程设计报告一课题要求(1)技术要求①掌握较复杂逻辑的设计,调试。

②掌握用VHDL语言设计数字逻辑电路。

③掌握quartusII6.0软件的使用方法。

④了解8*8列共阴点阵显示器的工作原理和功能。

⑤掌握常用驱动电路的原理及使用方法。

⑥掌握EP2C5T144C8芯片的使用。

(2)功能要求本设计为基于FPGA的8*8点阵显示器,运用VHDL语言编写软件,并通过硬件来实现显示汉字,及滚动,屏显等功能。

主要功能:静态显示一个完整的汉字能一屏一屏动态显示多个汉字能滚动动态显示多个汉字能通过开关控制点阵显示方式(3)本人工作在此次课程设计中我主要负责软件的编写与仿真。

以及软件的下载。

二设计方案1 原理图要实现8*8点阵显示器显示动态汉字的功能,主要实现两方面的设计:硬件部分和软件部分。

2 硬件部分硬件部分主要包括:驱动电路,点阵显示器,端口降压电路。

本次使用的点阵显示器为列共阴型点阵显示器。

及当行为高电平,列为低电平是对应的发光二极管反光。

硬件部分的主要功能是将软件中输出的行列信号在点阵中显示出来。

3 软件部分软件部分通过调用汉字库的方式来实现汉字的显示。

通过逐列扫描的方法来实现完整的汉字显示。

编辑输入综合适配编程下载硬件测试功能仿真时序仿真FPGA设计流程编辑输入:首先根据课程设计与硬件要求在quartus中编写软件。

功能仿真与时仿真:利用EDA工具软件对EDA设计进行模拟,验证设计和排除错误。

锁定端口:结合硬件要求锁定各个端口。

编程下载:把生成的编程文件通过编程器载入目标器件,以便进行硬件验证和调试,进而完成设计。

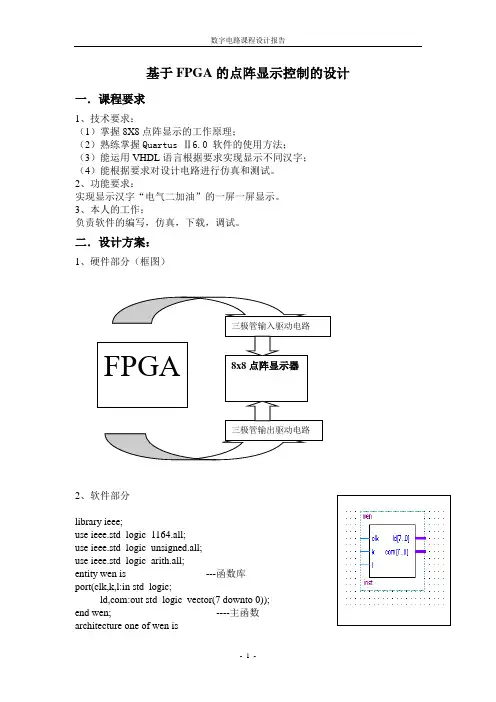

基于FPGA 的点阵显示控制的设计一.课程要求1、技术要求:(1)掌握8X8点阵显示的工作原理;(2)熟练掌握Quartus Ⅱ6.0 软件的使用方法;(3)能运用VHDL 语言根据要求实现显示不同汉字;(4)能根据要求对设计电路进行仿真和测试。

2、功能要求:实现显示汉字“电气二加油”的一屏一屏显示。

3、本人的工作:负责软件的编写,仿真,下载,调试。

二.设计方案:1、硬件部分(框图)2、软件部分library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity wen is ---函数库port(clk,k,l:in std_logic;ld,com:out std_logic_vector(7 downto 0));end wen; ----主函数architecture one of wen issignal st:std_logic_vector(7 downto 0);signal osc,osd:std_logic;signal d_ff:std_logic_vector(29 downto 0);signaldata,d0,d1,d2,d3,d4,d5,d6,d7,d8,d9,d10,d11,d12,d13,d14,d15:std_logic_vector(7 downto 0);signal lie0:std_logic_vector(6 downto 0); ---定义变量begincom<=data;ld<=st;d0<="00000000"when lie0(6 downto 0)="0000000"else"00000100"when lie0(6 downto 0)="0000001"else"00100000"when lie0(6 downto 0)="0000010"else"01000100"when lie0(6 downto 0)="0000011"else"10001010"when lie0(6 downto 0)="0000100"else"11111111"when lie0(6 downto 0)="0000101"else"11111011"when lie0(6 downto 0)="0000110"else"11011111"when lie0(6 downto 0)="0000111"else"10111011"when lie0(6 downto 0)="0001000"else"01110101"when lie0(6 downto 0)="0001001"else"00000000";d1<="00111110"when lie0(6 downto 0)="0000000"else"00010010"when lie0(6 downto 0)="0000001"else"00100000"when lie0(6 downto 0)="0000010"else"00111110"when lie0(6 downto 0)="0000011"else"01010100"when lie0(6 downto 0)="0000100"else"11000001"when lie0(6 downto 0)="0000101"else"11101101"when lie0(6 downto 0)="0000110"else"11011111"when lie0(6 downto 0)="0000111"else"11000001"when lie0(6 downto 0)="0001000"else"10101011"when lie0(6 downto 0)="0001001"else"00000000";d2<="00101010"when lie0(6 downto 0)="0000000"else"00010101"when lie0(6 downto 0)="0000001"else"00100100"when lie0(6 downto 0)="0000010"else"10000100"when lie0(6 downto 0)="0000011"else"00000000"when lie0(6 downto 0)="0000100"else"11010101"when lie0(6 downto 0)="0000101"else"11101010"when lie0(6 downto 0)="0000110"else"11011011"when lie0(6 downto 0)="0000111"else"01111011"when lie0(6 downto 0)="0001000"else"00000000";d3<="11111111"when lie0(6 downto 0)="0000000"else "00010101"when lie0(6 downto 0)="0000001"else "00100100"when lie0(6 downto 0)="0000010"else "01111100"when lie0(6 downto 0)="0000011"else "11111100"when lie0(6 downto 0)="0000100"else "00000000"when lie0(6 downto 0)="0000101"else "11101010"when lie0(6 downto 0)="0000110"else "11011011"when lie0(6 downto 0)="0000111"else "10000011"when lie0(6 downto 0)="0001000"else "00000011"when lie0(6 downto 0)="0001001"else "00000000";d4<="10101010"when lie0(6 downto 0)="0000000"else "00010101"when lie0(6 downto 0)="0000001"else "00100100"when lie0(6 downto 0)="0000010"else "00000000"when lie0(6 downto 0)="0000011"else "10010100"when lie0(6 downto 0)="0000100"else "01010101"when lie0(6 downto 0)="0000101"else "11101010"when lie0(6 downto 0)="0000110"else "11011011"when lie0(6 downto 0)="0000111"else "11111111"when lie0(6 downto 0)="0001000"else "01101011"when lie0(6 downto 0)="0001001"else "00000000";d5<="10111110"when lie0(6 downto 0)="0000000"else "01110101"when lie0(6 downto 0)="0000001"else "00100100"when lie0(6 downto 0)="0000010"else "01111100"when lie0(6 downto 0)="0000011"else "11111111"when lie0(6 downto 0)="0000100"else "01000001"when lie0(6 downto 0)="0000101"else "10001010"when lie0(6 downto 0)="0000110"else "11011011"when lie0(6 downto 0)="0000111"else "10000011"when lie0(6 downto 0)="0001000"else "00000000"when lie0(6 downto 0)="0001001"else "00000000";d6<="11000000"when lie0(6 downto 0)="0000000"else "10000000"when lie0(6 downto 0)="0000001"else "00100000"when lie0(6 downto 0)="0000010"else "01000100"when lie0(6 downto 0)="0000011"else "10010100"when lie0(6 downto 0)="0000100"else"01111111"when lie0(6 downto 0)="0000110"else"11011111"when lie0(6 downto 0)="0000111"else"10111011"when lie0(6 downto 0)="0001000"else"01101011"when lie0(6 downto 0)="0001001"else"00000000";d7<="00000000"when lie0(6 downto 0)="0000000"else"11000000"when lie0(6 downto 0)="0000001"else"00100000"when lie0(6 downto 0)="0000010"else"01111100"when lie0(6 downto 0)="0000011"else"11111100"when lie0(6 downto 0)="0000100"else"11111111"when lie0(6 downto 0)="0000101"else"00111111"when lie0(6 downto 0)="0000110"else"11011111"when lie0(6 downto 0)="0000111"else"10000011"when lie0(6 downto 0)="0001000"else"00000011"when lie0(6 downto 0)="0001001"else"00000000"; ---字库电气二加油d8<="00000000"when lie0="00000000"else"00111110"when lie0="00000001"else"00101010"when lie0="00000010"else"11111111"when lie0="00000011"else"10101010"when lie0="00000100"else"10111110"when lie0="00000101"else"11000000"when lie0="00000110"else"00000000"when lie0="00000111"else"00000000"when lie0="00001000"else"00000000"when lie0="00001001"else"00000000";d9<="00111110"when lie0="00000000"else"00101010"when lie0="00000001"else"11111111"when lie0="00000010"else"10101010"when lie0="00000011"else"10111110"when lie0="00000100"else"11000000"when lie0="00000101"else"00000000"when lie0="00000110"else"00000000"when lie0="00000111"else"00000000"when lie0="00001000"else"00000000"when lie0="00001001"else"00000000";d10<="00101010"when lie0="00000000"else"10101010"when lie0="00000010"else "10111110"when lie0="00000011"else "11000000"when lie0="00000100"else "00000000"when lie0="00000101"else "00000000"when lie0="00000110"else "00000000"when lie0="00000111"else "00000000"when lie0="00001000"else "00111110"when lie0="00001001"else "00000000";d11<="11111111"when lie0="00000000"else "10101010"when lie0="00000001"else "10111110"when lie0="00000010"else "11000000"when lie0="00000011"else "00000000"when lie0="00000100"else "00000000"when lie0="00000101"else "00000000"when lie0="00000110"else "00000000"when lie0="00000111"else "00111110"when lie0="00001000"else "00101010"when lie0="00001001"else "00000000";d12<="10101010"when lie0="00000000"else "10111110"when lie0="00000001"else "11000000"when lie0="00000010"else "00000000"when lie0="00000011"else "00000000"when lie0="00000100"else "00000000"when lie0="00000101"else "00000000"when lie0="00000110"else "00111110"when lie0="00000111"else "00101010"when lie0="00001000"else "11111111"when lie0="00001001"else "00000000";d13<="10111110"when lie0="00000000"else "11000000"when lie0="00000001"else "00000000"when lie0="00000010"else "00000000"when lie0="00000011"else "00000000"when lie0="00000100"else "00000000"when lie0="00000101"else "00111110"when lie0="00000110"else "00101010"when lie0="00000111"else "11111111"when lie0="00001000"else"00000000";d14<="11000000"when lie0="00000000"else "00000000"when lie0="00000001"else "00000000"when lie0="00000010"else "00000000"when lie0="00000011"else "00000000"when lie0="00000100"else "00111110"when lie0="00000101"else "00101010"when lie0="00000110"else "11111111"when lie0="00000111"else "10101010"when lie0="00001000"else "10111110"when lie0="00001001"else"00000000";d15<="00000000"when lie0="00000000"else "00000000"when lie0="00000001"else "00000000"when lie0="00000010"else "00000000"when lie0="00000011"else "00111110"when lie0="00000100"else "00101010"when lie0="00000101"else "11111111"when lie0="00000110"else "10101010"when lie0="00000111"else "10111110"when lie0="00001000"else "11000000"when lie0="00001001"else"00000000"; ---字库循环电first:process-----分频beginwait until clk='1';if d_ff(29 downto 0)>=2e8 thend_ff(29 downto 0)<="000000000000000000000000000000"; elsed_ff(29 downto 0)<=d_ff+1;end if;osc<=not d_ff(10);if l='0' thenosd<=not d_ff(26);else osd<= not d_ff(24);---程序分频取第26位24 位end if;end process first;second:process(osc)----扫描部分beginif(osc='1' and osc'event)thencase k iswhen '1'=> ---一屏一屏显示电气二加油if st(7 downto 0)="00000000"or st(7 downto 0)="01111111" then st(7 downto 0)<="11111110";data<=d0;elsif st(7 downto 0)="11111110"thenst(7 downto 0)<="11111101";data<=d1;elsif st(7 downto 0)="11111101" thenst(7 downto 0)<="11111011";data<=d2;elsif st(7 downto 0)="11111011" thenst(7 downto 0)<="11110111";data<=d3;elsif st(7 downto 0)="11110111" thenst(7 downto 0)<="11101111";data<=d4;elsif st(7 downto 0)="11101111" thenst(7 downto 0)<="11011111";data<=d5;elsif st(7 downto 0)="11011111" thenst(7 downto 0)<="10111111";data<=d6;elsif st(7 downto 0)="10111111" thenst(7 downto 0)<="01111111";data<=d7;end if; ---逐列扫描when '0'=> ---滚动显示电if st(7 downto 0)="00000000"or st(7 downto 0)="01111111" then st(7 downto 0)<="11111110";data<=d8;elsif st(7 downto 0)="11111110"thenst(7 downto 0)<="11111101";data<=d9;elsif st(7 downto 0)="11111101" thenst(7 downto 0)<="11111011";data<=d10;elsif st(7 downto 0)="11111011" thenst(7 downto 0)<="11110111";data<=d11;elsif st(7 downto 0)="11110111" thenst(7 downto 0)<="11101111";data<=d12;elsif st(7 downto 0)="11101111" thenst(7 downto 0)<="11011111";data<=d13;elsif st(7 downto 0)="11011111" thenst(7 downto 0)<="10111111";data<=d14;elsif st(7 downto 0)="10111111" thenst(7 downto 0)<="01111111";data<=d15;end if;end case;end if;end process second;third:process(osd)---循环beginif(osd='1' and osd'event)thenif lie0(6 downto 0)="0001001"thenlie0(6 downto 0)<="0000000";else lie0(6 downto 0)<=lie0+1;end if;end if;end process third;end one;三.软件设计的过程1.初始的设计:构思是按照列共阳行共阴设计“电气二”三个字一频一频显示。

基于fpga的led点阵系统控制器的设计与实现FPGA LED点阵系统控制器的设计与实现一、LED点阵系统概述1.1 简介LED点阵系统由FPGA控制器和LED屏组成,LED屏是一种分布式多媒体显示系统,由多个由特定数量LED组成的子系统,这些子系统具有固定的行和列数。

FPGA控制器是控制LED屏显示内容的核心,它通过向LED屏发送显示数据和控制指令来控制LED屏显示内容。

1.2 功能LED点阵系统具有优异的显示特色,能够在小空间内节省大量的时间和成本,对于分布式多媒体系统来说,具有高可靠性和高性价比的特点。

其优势可以体现在以下几个方面:二、FPGA LED点阵系统控制器的设计和实现2.1 FPGA控制器硬件FPGA控制器连接LED屏,负责传输和控制信号,包括两个部分:数据接口和总线接口。

数据接口负责向LED屏发送数据,而总线接口则负责向LED屏发送控制指令,另外,FPGA控制器还需要一个集成电路(IC)作为IO数据收发接口。

2.2 FPGA控制器软件FPGA控制器需要安装一个FPGA电路板,然后编写一个用于控制和加载LED 显示内容的软件,FPGA软件负责控制和加载数据,FPGA电路板则负责传输数据和控制指令。

2.3 LED屏硬件LED屏由多个特定数量的LED组成,这些LED之间形成一个行、列的矩阵结构,每个LED都由一个像素点来控制。

此外,LED屏还安装有一个IC,该IC用于控制LED点阵显示,并负责接收FPGA控制器传输过来的数据和控制指令。

综上所述,FPGA LED点阵系统控制器的设计与实现主要包括:FPGA控制器硬件设计、FPGA控制器软件设计以及LED屏硬件设计,确保系统可靠性和实用性,有效地利用LED点阵系统技术,实现视觉效果的优化。

基于FPGA的点阵LED显示屏控制器的设计屏幕在现代信息化的社会里应用越来越广泛,而它的灵魂是其内部的控制器。

传统的LED控制器绝大部分是基于设计的,这种控制器在控制单色或双色点阵是足够的,但是用法它来控制多彩色的LED屏和高辨别率的LED屏,是十分困难的。

为解决这一问题,本文提出了一种基于的LED点阵屏的控制器设计。

1 国内讨论现状如今,FPGA技术正处于高速进展时期,芯片的集成度越来越高,处理速度也越来越快,但成本却越来越低。

低端的FPGA正在逐渐的取代传统的数字元件,而高端的FPGA也在不断在与ASIC争夺市场份额。

随着科技的长进和创造工艺的不同改进,FPGA的集成度将不断提高,芯片的成本将不断降低,FPGA的应用前景将日趋明亮。

传统的LED屏控制器的设计通常是基于单片机的,单片机作为其主控制器,控制协调LED屏的囫囵显示系统的显示,这种控制器在控制单色或双色点阵是绰绰有余的,但因为工作频率的缘由,若是用法基于单片机的控制器来驱动高辨别率的LED屏或者是高灰度级的LED屏等,在这些对数据的处理速度要求很高场合下,单片机的处理速度是远远无法满足其要求。

若是用法FPGA设计LED屏控制器则可以很好的解决上面的问题。

如今最快的单片机的处理速度最快也就300MHZ左右,而FPGA的处理速度最快这可以达到上GHZ,所以在上面那些对数据处理速度要求很高的场合下,FPGA能很轻松的胜任。

此外,FPGA设计的控制器除了解决传统单片机在处理速度上的不足外,在传输上方面,它还可以通过网络来举行长距离数据传输,最远的传输距离可达100米;在控制显示方面,它可实现灰度级的显示。

这使的该控制器在LED屏市场上有很大的优势以及有用性。

2 系统设计第1页共3页。

目录序言 (2)第1章课题要求 (2)1.1 技术要求 (2)1.1.1 EDA技术 (2)1.1.2 VHDL语言 (3)1.1.3 层次化设计 (3)1.2功能要求 (3)1.3本人任务 (3)第2章方案设计及原理框图 (3)第3章单元模块设计仿真结果及分析 (5)第4章顶层模块设计仿真结果及分析 (13)第5章硬件电路设计与安装图 (14)第6章硬件电路安装与调试 (15)第7章调试结果 (16)第8章收获与体会 (17)参考文献 (18)序言随着计算机技术和电子技术的飞速发展和广泛应用,电器设备的输出设备也变得复杂多样。

诸如CRT显示、LCD显示、多位LED显示及发光二极管显示等应运而生。

在这些显示当中,LED及发光二极管显示电路较为简单,成本也较低,在功能单一的仪器仪表与机电设备中应用较广。

但当设备显示的点或位较多时,就需要采用一定的驱动电路与相应的驱动方式。

EDA技术就是依赖功能强大的计算机,在EDA工具软件平台上,对以硬件描述语言VHDL为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、化简、分割、综合、布局布线以及逻辑优化和仿真测试,直至实现既定的电子线路系统功能。

EDA技术为现代电子理论和设计的表达与实现提供了可能性。

随着电子设计自动化(EDA)技术的进展,基于可编程FPGA器件进行系统芯片集成的新设计方法,也正在快速地取代基于PCB板的传统设计方式。

第一章课题要求1.1技术要求1.1.1 EDA技术20世纪90年代,国际上电子和计算机技术较先进的国家,一直在积极探索新的电子电路设计方法,并在设计方法、工具等方面进行了彻底的变革,取得了巨大成功。

在电子技术设计领域,可编程逻辑器件(如CPLD、FPGA)的应用,已得到广泛的普及,这些器件为数字系统的设计带来了极大的灵活性。

这些器件可以通过软件编程而对其硬件结构和工作方式进行重构,从而使得硬件的设计可以如同软件设计那样方便快捷。

绪论1.1 研究意义作为大型平板显示设备的一种,LED显示屏以其使用寿命长、维护费用低、功耗低等特点在显示领域占有重要的位置。

特别在近年,带有红、绿、蓝三基色以及灰度显示效果的全彩LED显示屏,以其丰富多彩的显示效果而倍受业界关注,成为LED显示屏市场近年增长幅度比较大的产品。

寿命、单位面积亮度、三基色的偏差程度、点距、对比度、灰度等级(包括灰度级数和线性度)、扫描频率等指标性能是衡量或横向比较大型显示设备好坏的标准。

而这些指标性能的优劣,很大程度上决定于扫描控制器的性能。

因此对大屏幕全彩LED显示扫描控制方法的研究有着重要的意义。

随着显示屏尺寸的扩大、亮度要求的增加,数据传输和控制的时间也会增加,如果仍然采用单片机作为控制器,将会影响显示效果,严重时可能无法正常工作,然而,这时若采用可编程逻辑器件作为控制器,则可解决这一难题。

一方面,随着微电子技术的发展和生产工艺的提高,器件的性能大有很大的提高,出现了高性能的现场可编程逻辑器件(FPGA),FPGA具有处理速度高、可靠性高、高容量和集成度高等特点,在大屏幕显示系统设计中使用FPGA可以满足现在的LED大屏幕系统对于处理视频数据的高速要求,同时改善电路的性能,缩小系统的体积。

设计中使用硬件描述语言进行电路设计,可以随时根据设计需要进行修改,而不必对硬件进行修改,它使系统的设计和调试非常方便,大大的缩短了产品的开发周期,降低了开发成本,也方便以后的系统升级。

1.2 研究现状LED照明发展非常迅速,年增长率超过60%,随着LED发光效率的不断提升,封装技术不断改进,驱动陆能和寿命的增加,LED照明技术在未来5年内会逐渐进入千家万户。

在世界各国环保议题日渐重视的趋势下,LED照明产业将扮演极重要的角色,其主要应用在于室内、室外照明以及街灯等高功率产品。

据悉,2009年全球照明市场约1219亿美元,LED仅占0.5%,显见其未来潜力之可观。

其中,以亚太地区的市场规模为最大、约占全球33.7%之比例,居次为北美的30.1%和欧洲之27.4%。

对基于FPGA的图形点阵液晶显示系统设计与实现探讨发布时间:2022-05-23T02:17:18.610Z 来源:《科学与技术》2022年2月3期作者:黄丽芬[导读] FPGA为现场可编程门阵列,能够利用较高质量的资源配置能力黄丽芬南宁富联富桂精密工业有限公司、530033摘要:FPGA为现场可编程门阵列,能够利用较高质量的资源配置能力,对硬件进行数字化控制,满足系统质量的需求。

目前该技术已经被广泛应用于电子产品生产中。

液晶显示器是近几年来数字化产品中非常常见的一种显示器种类,能够提升系统运行的稳定性。

因此,若能够将现场可编程门阵列与液晶显示器进行融合,便可以提升系统的整体性能,为系统的运行奠定良好的基础。

鉴于此情况,本文将围绕基于FPGA的图形点阵液晶显示系统设计进行研究,分析液晶显示器的相关性能以及FPGA的软件设计,以此为我国相关行业的发展提供借鉴。

关键词:图形点阵;液晶显示系统;整体结构引言:由于液晶显示器具有高效控制、能耗较低的应用优势,因此在移动通信、卫星定位等领域中被广泛应用,而FPGA则能够利用自身的集成化优势,进一步强化系统的运用。

因此,针对FPGA的图形点阵液晶显示系统设计进行分析与研究,对于技术发展与产品开发来讲尤为重要。

一、液晶显示系统硬件方案(一)整体结构设计为了能够尽可能地降低结构设计的难度,在进行液晶显示系统规划时,技术人员使用了型号为T6963C的图形显示模块,能够有效地帮助管理人员进行初始化设置,而外部处理器则选择CYCLONE系列的组件,可以高质量的进行信息交互。

(二)LED与EPGA的硬件接口电路设计T6963系列组件在模块的分辨率方面可以满足系统设计的需求,能够达到240*128的分辨率。

此外由于EPGA可以更加简便的对系统进行控制,因此在系统设计的过程中,技术人员还需要加大对IO控制信号的应用,以此增强信号传递的质量。

同时,在设计的过程中,工作人员将FPGA的管脚信号进行了更大范围的应用,将其与TS25643A型号的背光灯进行了连接。

基于FPGA的大屏幕LED点阵显示系统设计摘要:本文用FPGA 设计LED 显示屏接收控制系统,着重研究系统硬件设计方案,进一步解决了LED 大屏幕数据的灰度控制、外扩存储器的性能要求及实现方式。

用QuartusII 软件开发各个模块, QuartusII 软件提供的人性化的界面操作,很多模块都可以在系统内直接实现, 方便实用。

LED 屏早在60 年代就已出现,但直到90 年代中期,才出现了全彩屏,该技术近年的价格已有了很大的降幅,分辨率也有了很大的改善。

对于视频来说,LED 屏的低分辨率表现性能良好。

平常看到LED 屏的分辨率与电脑显示器的分辨率是差不多的。

LED 彩色显示大屏是室外显示大屏中用的最多的,是公认的室外大型显示屏中最值得发展的产业,LED 屏以其高亮度、长使用寿命更胜一筹。

与LCD 相比,LED 屏播放视频时的响应速度更快,亮度更高。

与电子发射显示器相比,LED 制造更简单。

与OLED 相比,LED 技术更成熟。

总之,LED 显示以其得天独厚的优势占据了高分辨率视频显示市场。

本文设计的基于FPGA 的大屏幕LED 点阵显示系统处理数据更快、存储量更大。

一、接收卡控制系统的总体方案设计如图 1 所示,视频数据通过DVI 接口传给FPGA1,进行分辨率的切换和显示区域的选择以及信号的反伽码矫正,通过网络传输给接收卡的FPGA2,通过FPGA2 进行数据的缓存,灰度控制以及行扫描和列驱动功能。

接收卡接收的是DVI 传给FPGA1,经FPGA1 处理后的数据。

在FPGA2 内部还要进行数据处理,处理要达到的目标:(1)数据能在LED 屏幕上分区显示;(2)256 灰度级屏幕大小:256*800。

(一)灰度实现方案的选择。

基于FPGA的8*8点阵显示器的设计摘要:主要研究基于VHDL语言的8*8点阵显示汉字。

首先对单个模块进行设计仿真调试,然后对整体模块的设计,通过编程、调试、仿真实现汉字的行扫描,其硬件系统下载正确的实现也获得了与软件仿真相吻合的结果。

关键字:扫描分频点阵显示一.课题要求1.技术要求(1)EDA技术:EDA(Electronic Design Automation)技术就是依赖功能强大的计算机,在EDA工具软件平台上,对以硬件描述语言HDL(Hardware Description Language)为系统描述手段完成的设计文件,自动的完成逻辑编译、化简、分割、综合、布局布线以及逻辑优化和仿真测试,直至实现既定的电子线路系统功能。

(2)VHDL语言:VHDL(Very--High--Speed Integrated Circuit Hardware Description Language主要用于描述数字系统的结构,行为,功能和接口,除了含有许多硬件特征得语句外,VHDL的语言形式和描述风格与句法是十分类似于一般的计算机高级语言。

(3)层次化设计:EDA设计一般采用自顶向下、由粗到细、逐步求精的方法。

设计最顶层是指系统的整体要求,最下层是指具体的逻辑电路实现。

自定向下是将数字系统的整体逐步分解为各个子系统和模块,若子系统规模较大则进一步分解为更小的子系统和模块,层层分解,直至整个系统中各子模块关系合理、便于实现为止。

2.功能要求本次综合型数字电路课程设计组要完成点阵显示控制器的三种功能,分别是按键控制静态显示下一个字、汉字滚动和逐列显示(即先显示两边的各一列然后向外依次显示直至显示整个汉字,之后先显示中间的两行然后向外显示直至显示整个汉字),本次课程设计的所采用的软件是QuartersІІ6.0,硬件是EP2C5T144C8,通过对于8*8点阵显示相应的汉字,分别通过行和列控制显示。

二.设计方案本次课程设计采用的是的行共阳列共阴的8*8点阵,因此不可能在同一时刻显示出整个汉字,为了显示出整个汉字,首先制作一个基本矩阵,然后按照时间的顺序进行逐行扫描,首先行给'"00000001",同时列给相应的码值,第一行的的发光二极管就会有相应的亮,然后行给"00000010",同时列给相应的码值,第二行的的发光二极管就会有相应的亮,用并行操作方式,如此周而复始的重复下去,根据人眼的视觉残留特性,使之形成整个汉字的显示。

本次试验采用行扫描。

图一.硬件总体框图三.单元模块设计仿真结果及分析1.选择输出模式library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity control isport(en:in std_logic;key:in std_logic_vector(1 downto 0);Q0,Q1,Q2:in std_logic_vector(7 downto 0);Y:out std_logic_vector(7 downto 0));end;architecture ex1 of control isbeginprocess(en,key)beginif en='0' then y<="11111111";elsecase key iswhen"00"=>y<=Q0;when"01"=>y<=Q1;when"10"=>y<=q2;when others=>y<="11111111";end case;end if;end process;end ex1;利用对输入按键的码值来控制显示:EN Key1 Key0 Y0 X X "11111111"1 0 0 Q01 0 1 Q11 1 0 Q21 1 1 "11111111"仿真波形:通过仿真波形可以知道只有在EN=‘0’和开关都为高电平的情况下无显示,即输出都为高电平,其余情况下都会输出对应的码值。

2.滚动显示滚动部分是将50MHZ时钟分为两个不同的频率,一个较快的时钟用来控制扫描的速度显示相应的汉字,一次从上向下逐行扫描,用一个较慢的时钟,当来了一个脉冲hang依次加1,就会有不同的码值输送给列,就会有汉字向上移一行。

由于是行扫描在一定的时间里,即高频扫描每种输出的码值,使视觉上就可以实现向上滚动显示汉字的效果。

library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity gundong isport(clk:in std_logic;com:out std_logic_vector(7 downto 0);red:out std_logic_vector(7 downto 0));end;architecture ex2 of gundong issignal st1:std_logic_vector(7 downto 0);signal osc,osd:std_logic;signal d_ff:std_logic_vector(25 downto 0);signal data,d0,d1,d2,d3,d4,d5,d6,d7:std_logic_vector(7 downto 0);signal hang:std_logic_vector(6 downto 0);begincom<=st1; red<=data;d0<="11000001"when hang="0000000"else--周字第1行 "11010101"when hang="0000001"else"11000001"when hang="0000010"else"11000001"when hang="0000011"else"11000001"when hang="0000100"else"11000001"when hang="0000101"else"10111001"when hang="0000110"else"01111101"when hang="0000111"else"11111111"when hang="0001000"else"11101011"when hang="0001001" else"11001110"when hang="0001010"else"10010001"when hang="0001011"else"00000011"when hang="0001100"else"10001011"when hang="0001101"else"01011011"when hang="0001110"else"11010101"when hang="0001111"else"11001110"when hang="0010000"else"11111111"when hang="0010001"else"11111111";d1<="11010101"when hang="0000000"else"11000001"when hang="0000001"else"11000001"when hang="0000010"else"11000001"when hang="0000011"else"11000001"when hang="0000100"else"10111001"when hang="0000101"else"01111101"when hang="0000110"else"11111111"when hang="0000111"else"11101011"when hang="0001000"else"11001110"when hang="0001001"else"10010001"when hang="0001010"else"00000011"when hang="0001011"else"10001011"when hang="0001100"else"01011011"when hang="0001101"else"11010101"when hang="0001110"else"11001110"when hang="0001111"else"11000001"when hang="0010001"else--周字第1行 "11111111";d2<= "11000001"when hang="0000000"else"11000001"when hang="0000001"else"11000001"when hang="0000010"else"11000001"when hang="0000011"else"10111001"when hang="0000100"else"01111101"when hang="0000101"else"11111111"when hang="0000110"else"11101011"when hang="0000111"else"11001110"when hang="0001000"else"10010001"when hang="0001001"else"00000011"when hang="0001010"else"10001011"when hang="0001011"else"01011011"when hang="0001100"else"11010101"when hang="0001101"else"11001110"when hang="0001110"else"11111111"when hang="0001111"else "11000001"when hang="0010000"else--周字第1行 "11010101"when hang="0010001"else"11111111";d3<="11000001"when hang="0000000"else"11000001"when hang="0000001"else"11000001"when hang="0000010"else"10111001"when hang="0000011"else"01111101"when hang="0000100"else"11111111"when hang="0000101"else"11101011"when hang="0000110"else"11001110"when hang="0000111"else"10010001"when hang="0001000"else"00000011"when hang="0001001"else"10001011"when hang="0001010"else"01011011"when hang="0001011"else"11010101"when hang="0001100"else"11001110"when hang="0001101"else"11111111"when hang="0001110"else "11000001"when hang="0001111"else--周字第1行"11000001"when hang="0010001"else"11111111";d4<="11000001"when hang="0000000"else"11000001"when hang="0000001"else"10111001"when hang="0000010"else"01111101"when hang="0000011"else"11111111"when hang="0000100"else"11101011"when hang="0000101"else"11001110"when hang="0000110"else"10010001"when hang="0000111"else"00000011"when hang="0001000"else"10001011"when hang="0001001"else"01011011"when hang="0001010"else"11010101"when hang="0001011"else"11001110"when hang="0001100"else"11111111"when hang="0001101"else"11000001"when hang="0001110"else--周字第1行 "11010101"when hang="0001111"else"11000001"when hang="0010000"else"11000001"when hang="0010001"else"11111111";d5<= "11000001"when hang="0000000"else"10111001"when hang="0000001"else"01111101"when hang="0000010"else"11111111"when hang="0000011"else"11101011"when hang="0000100"else"11001110"when hang="0000101"else"10010001"when hang="0000110"else"00000011"when hang="0000111"else"10001011"when hang="0001000"else"01011011"when hang="0001001"else"11010101"when hang="0001010"else"11001110"when hang="0001011"else"11111111"when hang="0001100"else"11000001"when hang="0001101"else--周字第1行 "11010101"when hang="0001110"else"11000001"when hang="0001111"else"11000001"when hang="0010001"else"11111111";d6<="10111001"when hang="0000000"else"01111101"when hang="0000001"else"11111111"when hang="0000010"else"11101011"when hang="0000011"else"11001110"when hang="0000100"else"10010001"when hang="0000101"else"00000011"when hang="0000110"else"10001011"when hang="0000111"else"01011011"when hang="0001000"else"11010101"when hang="0001001"else"11001110"when hang="0001010"else"11111111"when hang="0001011"else"11000001"when hang="0001100"else--周字第1行 "11010101"when hang="0001101"else"11000001"when hang="0001110"else"11000001"when hang="0001111"else"11000001"when hang="0010000"else"11000001"when hang="0010001"else"11111111";d7<= "01111101"when hang="0000000"else"11111111"when hang="0000001"else"11101011"when hang="0000010"else"11001110"when hang="0000011"else"10010001"when hang="0000100"else"00000011"when hang="0000101"else"10001011"when hang="0000110"else"01011011"when hang="0000111"else"11010101"when hang="0001000"else"11001110"when hang="0001001"else"11111111"when hang="0001010"else"11000001"when hang="0001011"else--周字第1行 "11010101"when hang="0001100"else"11000001"when hang="0001101"else"11000001"when hang="0001110"else"11000001"when hang="0001111"else"10111001"when hang="0010001"else"11111111";first:process(clk)beginif clk'event and clk='1'thenif d_ff>=2e8 then d_ff<=(others=>'0');else d_ff<=d_ff+1;end if;end if;osc<=not d_ff(8);osd<=not d_ff(24);end process first;second:process(osc)beginif osc'event and osc='1' thenif st1="00000000" or st1="10000000" thenst1<="00000001";data<=d0;elsif st1="00000001"thenst1<="00000010";data<=d1;elsif st1="00000010" thenst1<="00000100";data<=d2;elsif st1="00000100" thenst1<="00001000";data<=d3;elsif st1="00001000"thenst1<="00010000";data<=d4;elsif st1="00010000"thenst1<="00100000"; data<=d5;elsif st1="00100000" thenst1<="01000000";data<=d6;elsif st1="01000000" thenst1<="10000000";data<=d7;end if;end if;end process;third:process(osd)beginif osd'event and osd='1'thenif hang="0010001" thenhang<=(others=>'0');else hang<=hang+1;end if;end if;end process third;end ex2;仿真波形:由仿真波形可以知道在时钟的控制下会有相应的码值送出,由此可以知道所写程序是正确的。