EMC Considerations on PCB Design for a High-Power Converter Control System

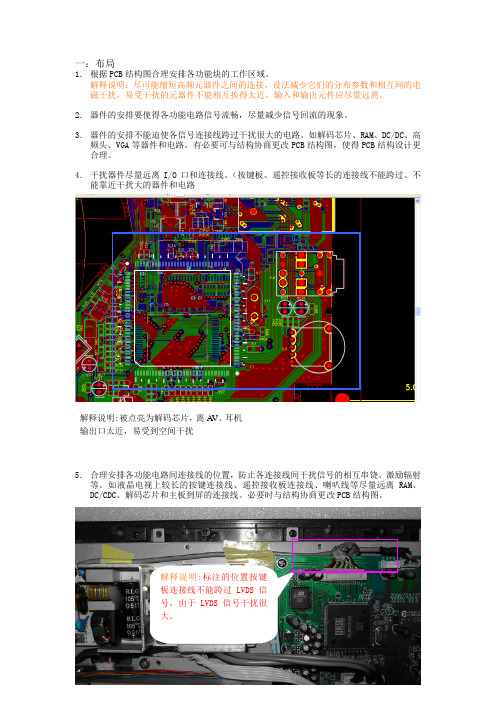

- 格式:pdf

- 大小:3.05 MB

- 文档页数:4

PCB设计中的电磁兼容性改善电磁兼容性(Electromagnetic Compatibility,简称EMC)是指在电子设备中,各种互相干扰的电磁能量不超过规定的范围,以确保设备在电磁环境中的正常工作。

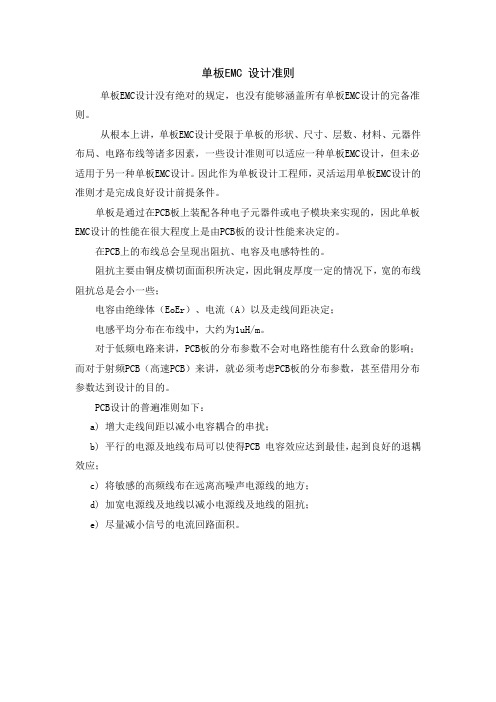

在PCB设计中,保障电磁兼容性是至关重要的。

本文将就PCB设计中的电磁兼容性进行探讨,并介绍一些改善电磁兼容性的方法。

一、电磁兼容性的重要性在现代电子设备中,各种电子产品如手机、电视、计算机等,数量繁多。

这些设备在工作过程中产生的电磁辐射会相互干扰,引起电子设备的不正常工作甚至故障。

而电磁辐射也会对周围环境和人体健康产生潜在的风险。

因此,电磁兼容性的保证显得尤为重要。

二、PCB设计中的电磁兼容性难点在PCB设计中,保障电磁兼容性是一项复杂的任务。

其中,主要存在以下几个难点。

1. 线路布局与走线规划:线路布局和走线规划是保障电磁兼容性的基础。

线路过长、过密会导致信号互相干扰;线路交叉或平行布局会引起信号耦合,进而产生互相干扰的可能。

2. 地线设计:地线在PCB中起到非常重要的作用。

正确的地线设计能够降低信号回路的阻抗,减少信号辐射和敏感性。

然而,过长的地线会导致共模电流和电压的增加,从而影响电磁兼容性。

3. 电源和信号线的隔离:电源和信号线之间的隔离非常关键。

如果电源线和信号线没有充分的隔离,电磁干扰就会传导到其他线路,导致设备工作异常。

4. 元件布局:元件布局不当会直接影响整个系统的电磁兼容性。

例如,元件之间距离过近或排列不当会导致串扰和不希望的辐射。

三、改善PCB设计中的电磁兼容性方法为了提高电磁兼容性,以下是一些常用的改善方法。

1. 良好的线路布局和走线规划:合理规划线路和走线路径,减少线路长度和密度,可以降低信号之间互相干扰的可能。

2. 地线设计:在PCB设计中,正确的地线设计可以有效地降低信号辐射和敏感性。

采用分离式地面平面或多层地面平面,可以起到屏蔽电磁干扰的作用。

3. 电源和信号线的隔离:在PCB设计中,应该尽量将电源线和信号线分开布局,并通过地面平面等方式加强隔离,减少电磁干扰。

单板EMC 设计准则

单板EMC设计没有绝对的规定,也没有能够涵盖所有单板EMC设计的完备准则。

从根本上讲,单板EMC设计受限于单板的形状、尺寸、层数、材料、元器件布局、电路布线等诸多因素,一些设计准则可以适应一种单板EMC设计,但未必适用于另一种单板EMC设计。

因此作为单板设计工程师,灵活运用单板EMC设计的准则才是完成良好设计前提条件。

单板是通过在PCB板上装配各种电子元器件或电子模块来实现的,因此单板EMC设计的性能在很大程度上是由PCB板的设计性能来决定的。

在PCB上的布线总会呈现出阻抗、电容及电感特性的。

阻抗主要由铜皮横切面面积所决定,因此铜皮厚度一定的情况下,宽的布线阻抗总是会小一些;

电容由绝缘体(EoEr)、电流(A)以及走线间距决定;

电感平均分布在布线中,大约为1uH/m。

对于低频电路来讲,PCB板的分布参数不会对电路性能有什么致命的影响;而对于射频PCB(高速PCB)来讲,就必须考虑PCB板的分布参数,甚至借用分布参数达到设计的目的。

PCB设计的普遍准则如下:

a) 增大走线间距以减小电容耦合的串扰;

b) 平行的电源及地线布局可以使得PCB 电容效应达到最佳,起到良好的退耦效应;

c) 将敏感的高频线布在远离高噪声电源线的地方;

d) 加宽电源线及地线以减小电源线及地线的阻抗;

e) 尽量减小信号的电流回路面积。

PCBEMC设计标准1. 引言电子产品的设计和制造中,电磁兼容性〔Electromagnetic Compatibility, EMC〕是一个至关重要的考虑因素。

为了保证产品在遇到电磁干扰时的良好表现,必须遵循一定的设计标准。

本文档旨在为PCB〔Printed Circuit Board〕的EMC设计提供详细指南和建议。

2. 设计布局2.1 别离敏感和噪声局部将PCB分为敏感电路局部和噪声电路局部,并合理布局两者之间的间距。

敏感局部应远离噪声产生器,而噪声局部应尽可能靠近电源和地线等有源器件。

2.2 信号地线和电源地线别离为了防止共模干扰,应将信号地线和电源地线别离,并通过独立的连接方式连接到整个电路板。

同时,应确保地线的大小足够宽,以降低电阻和电感。

2.3 阻止信号循环当信号线和地线形成回路时,可能会导致电磁干扰的增加。

在设计过程中,应注意防止信号线和地线之间形成闭环。

2.4 引入绕线在布局中,根据需要引入绕线,以减少过长的信号线和地线。

3. 网络连接3.1 电源线在设计过程中,应注意电源线的布局。

电源线宜短而粗,尽量减小电阻和电感对电磁干扰的影响。

3.2 地线和信号线在PCB布线时,应确保地线和信号线能够平行走向。

相邻的高速信号线和地线应尽可能靠近。

3.3 电源和信号线的层间穿越在层间穿越时,应减小穿越的区域,防止电源和信号线之间形成环状穿越。

4. 高速设计4.1 控制信号的走线在高速信号走线时,应防止普通信号跨越高速信号线。

同时,应保证高速信号线尽量保持匹配和平行走向。

4.2 信号之间的间距在高速信号布局中,应确保相邻信号之间的间距足够,并且防止平行走向。

间距的增加可以减小信号之间的串扰。

4.3 地线和反向信号线的布局在高速信号布局中,应在信号线的两侧引入地线和反向信号线,以控制信号的传输和降低辐射噪声。

5. 硬件设计5.1 硬件敷铜和接地应在PCB上适当敷铜,以提供良好的接地和屏蔽。

同时,适当增加接地点,降低接地电阻和接地电感。

A PCB design approach for best EMCTim Jarvis BSc CEng MIEE MIEEE Radio & EMC Specialist22/06/2004A PCB design approach for best EMCIntroductionnTim JarvisBSc CEng MIEE MIEEEnRF /Analogue Engineern Since graduating in 1983nOffshore and Naval Sonar nDSP /Embeddedn Detour 1987 to 1997nTelecommunications industrynRF & EMC since 1991nFounded RadioCAD in 2000 following redundancy.nPresentation HistorynApproval 1999ConferencenBest practice in circuit board designnIEE New Issues in Design April 2004nPractical Power Planes for EMCnAutomotive EMC 2004nPractical Power Planes for EMC.A PCB design approach for best EMC22/06/2004 Pre-PCB Questionsn What is our EMC target?n Emissionsn Immunityn ESD, etc.n Market accessn Product safetyn Other directivesn Conflicting standardsA PCB design approach for best EMC22/06/2004 Pre-PCB Questions(continued)n What are our product constraints?n Anticipated volumesn High volume = spent time engineering for lowestcost = minimum PCB layers (2-layers)n Low volume = minimise engineering time = morePCB layers, plenty of component options.n Component technologiesn Fast semiconductors (faster than we need?)n Cheap passives (spend £s to save pence?)A PCB design approach for best EMC22/06/2004 Pre-PCB Questions(continued)n Segregation at the schematic level n What are our system blocks?n Which blocks are noisy?n Which blocks are sensitive?n What about ports and connectors?n Import /export EMI /ESDn Interact with shield /enclosure boundaryn Buy or build EMI filters?22/06/2004A PCB design approach for best EMCPCB Step 1 -PlacementPSTN socketHandset SocketSensitive circuitry well away from cables and noisy digital circuitry.Insensitive Circuitry, in this case without a ground plane.nRULE1 -Never use the auto-placer and always segregate sub-systemsIn this real-world example the noisy digital circuitrywas placed on another PCB.system /sub-system boundariesThink about leak aroundthe sub-systemboundary on your schematic?22/06/2004A PCB design approach for best EMCSimple DIY Filters(continued)Always look at attenuation-v-frequency curves for components. Never rely on component values alone. n Symmetrical FiltersA PCB design approach for best EMC22/06/2004 PCB Step 2 Assign Layersn Ground Plane?n Yes always, big and uncutn(only cut if you really know what you re doing) n Power Planes, do we need them?n It depends who you talk ton1 look at the theoryn2 look at the practice22/06/2004A PCB design approach for best EMC Standard multi-layer construction 1 mm and 0.8mm cores are common.= 0.13 and 0.23 mm prepreg6-layer exampleSignal layers have fairly constant ZSignals couple to the ground and not the power planesPower planes have lowest Z and greatest CAvoid this stack orderF=1/2t t rThis gap is wider than you think!A PCB design approach for best EMC22/06/2004 Power plane sizeSmall is best(<= 75 mm for 1 GHz)A PCB design approach for best EMC22/06/2004 Power plane shapeNon-trapezoidal irregular shapes are best(but not much better)A PCB design approach for best EMC22/06/2004 Power Plane SeparationClose is best(<=2 requires specialist techniques)A PCB design approach for best EMC22/06/2004 Interaction with decoupling capsMore caps the better(but they have little effect above l/2A PCB design approach for best EMC22/06/2004 Interaction with decoupling caps(continued)plane separation is better than 99 * 10nF Capswith a 0.8mm separation @ freq>l/4A PCB design approach for best EMC22/06/2004 What value of decoupling cap?Plain old 100nF caps are usually best(lots and lots of them)A PCB design approach for best EMC22/06/2004 Why we might want power planesCurrent spreading in a power planereduces noise coupling between power pins22/06/2004A PCB design approach for best EMCPower Plane Test JIGHas 5 evenly spaced emitters all connected to one 10 MHz oscillatorvia filtered traces. Has provision for additional decoupling caps.Ground plane and routingon 300x200x1mm THPFR4 PCB. Eachdecoupling capacitor hasa 0.8mm via hole forstitching through to aremovable power plane.22/06/2004A PCB design approach for best EMCHorizontalVertical300x200mm power plane @ 1.6mm, 10x100nF capsA PCB design approach for best EMC22/06/2004300x200mm power plane @ 0.2mm, 10x100nF capsHorizontalVerticalA PCB design approach for best EMC22/06/2004300x200mm power plane @ 50m m, 35x100nF capsHorizontalVerticalA PCB design approach for best EMC22/06/2004No power plane, 10x100nF caps!HorizontalVerticalA PCB design approach for best EMC22/06/2004 No power plane5 leads,j0.4mm, close to ground plane22/06/2004A PCB design approach for best EMC Comparison of Vcc Noisen 50m m power planen35 caps nVcc noise ~12mV RMS n No power plane n 10 capsn Vcc noise ~20mV RMSA PCB design approach for best EMC22/06/2004 Smaller regional power planesn Segment board into smaller regionsn Each has a regional power plane <75mm (1GHz) n Each is interconnected via ferrites or inductorsn Each region has its own local decoupling capsA PCB design approach for best EMC22/06/2004 Example: 5 regional planesn Each region is connected via BLM18RK221SN1n Each region has 4x100nF local decouplersn A further 16x100nF caps decouple the remaining planeA PCB design approach for best EMC22/06/200475x75mm regional power planes @ 1.6mm, 4x100nF caps eachHorizontalVerticalA PCB design approach for best EMC22/06/2004 An interesting questionn Why is no power plane almost as good as a sophisticated buried capacitance power plane?n Possible answer = impedancen Regional Vcc impedance ~1Wn Narrow line feeds impedance >>1Wn gap power plane impedance <<1Wn Hence large power mismatch in both cases!A PCB design approach for best EMC22/06/2004A Power-plane design algorithm2 Layer PCBs & ground planesthis manual technique takes skill and time!Slots <l /20Cuts mustn t run into each otherEdge traces must be clean/insensitiveA PCB design approach for best EMC22/06/2004 Routing Tipsn Be prepared to move components during the routing process.n Minimise vias and layer changes with critical signal tracks.n Do use circuitous (inductive) power routes n Form supply chains:n Clean chainn Dirty chainn De-couple Vcc pins with good (small or X2Y), closely placed capacitors and small power planes (if using power planes).A PCB design approach for best EMC(in brief)THE ENDQuestion from the floorTim Jarvis BSc CEng MIEE MIEEE Radio & EMC Specialist。

多层PCB板设计的电磁兼容(EMC)考量3 - W法则:当两条印制线间距较小时,两条线之间会发生电磁串扰,这会使有关电路功能失常,为避开这种干扰,应保持任何线条间距不小于3倍印制线条宽度,即不小于3W (W为印制线条宽度)。

印制线条宽度取决于线条阻抗的要求,太宽会影响布线密度,太窄会影响传输到终端的信号完整性和强度。

时钟电路、差分对、I/O端口的布线都是3 - W原则的基本应用对象。

3 - W原则只是表示了串扰能量衰减70%的电磁通量线边界,若要求更高,如保证串扰能量衰减98%的电磁通量边界线就必需采纳10W间隔。

2. 3 地线的布置首先,要建立分布参数的概念,高于一定频率时,任何金属导线都要看成是由、电感构成的器件。

所以接地引线具有一定阻抗并且构成电气回路,不管是单点接地还是多点接地,都必需构成低阻抗回路进入真正的地或机架。

25mm 长的典型印制线大约会表现15~ 20nH电感,加上分布电容的存在,就会在接地板和设备机架之间构成谐振电路。

第二,接地电流流经接地线时,会产生传输线效应和天线效应。

当线条长度为1 /4波长时,表现出很高的阻抗,接地线事实上是开路的,接地线反而成为向外辐射的天线。

最后,接地板上弥漫高频电流和骚扰形成的涡流,因此,在接地点之间构成许多回路,这些回路的直径(或接地点间距)应小于最高频率波长的1 /20. 挑选恰当的器件是设计胜利的重要因素,特殊是在挑选规律器件时,尽量挑选升高时光比5ns长的,决不要选比电路要求时序快的规律器件。

2. 4 电源线的布置对于多层板,采纳电源层- 地层结构供电,这种结构的特性阻抗比轨线对小得多,可以做到小于1Ω。

这种结构具有一定的电容,不必在每个集成芯片旁加高频去耦电容。

即使层电容容量不够,需要外加去耦电容时,也不要加在集成芯片旁边,可加在印制板的任何地方。

集第1页共2页。

PCB EMC设计规范目录第一部分布局1 层的设置1.1 合理的层数1.1.1 Vcc、GND的层数1.1.2 信号层数1.2 单板的性能指标与成本要求1.3 电源层、地层、信号层的相对位置1.3.1 Vcc、GND 平面的阻抗以及电源、地之间的EMC环境问题1.3.2 Vcc、GND 作为参考平面,两者的作用与区别1.3.3 电源层、地层、信号层的相对位置2 模块划分及特殊器件的布局2.1 模块划分2.1 .1 按功能划分2 .1.2 按频率划分2.1.3 按信号类型分2.1.4 综合布局2.2 特殊器件的布局2.2.1 电源部分2.2.2 时钟部分2.2.3 电感线圈2.2.4 总线驱动部分2.2.5 滤波器件3 滤波3.1 概述3.2 滤波器件3.2.1 电阻3.2.2 电感3.2.3 电容3.2.4 铁氧体磁珠3.2.5 共模电感3.3 滤波电路3.3.1 滤波电路的形式3.3.2 滤波电路的布局与布线3.4 电容在PCB的EMC设计中的应用3.4.1 滤波电容的种类3.4.2 电容自谐振问题3.4.3 ESR对并联电容幅频特性的影响3.4.4 ESL对并联电容幅频特性的影响3.4.5 电容器的选择3.4.6 去耦电容与旁路电容的设计建议3.4.7 储能电容的设计4 地的分割与汇接4.1接地的含义4.2接地的目的4.3基本的接地方式单点接地多点接地浮地以上各种方式组成的混合接地方式4.4关于接地方式的一般选取原则背板接地方式单板接地方式第二部分布线1传输线模型及反射、串扰1.1概述:1.2传输线模型1.3传输线的种类微带线〔microstrip带状线〔Stripline1.3.3嵌入式微带线1.4传输线的反射1.5串扰2优选布线层2.1表层与内层走线的比较2.1.1 微带线〔Microstrip2.1.3 微带线与带状线的比较2.2 布线层的优先级别3 阻抗控制3.1 特征阻抗的物理意义3.1.1 输入阻抗:3.1.2 特征阻抗3.1.3 偶模阻抗、奇模阻抗、差分阻抗3.2 生产工艺对对阻抗控制的影响3.3 差分阻抗控制3.3.1 当介质厚度为5mil时的差分阻抗随差分线间距的变化趋势3.3.2 当介质厚度为13 mil时的差分阻抗随差分线间距的变化趋势3.3.3 当介质厚度为25 mil时的差分阻抗随差分线间距的变化趋势3.4 屏蔽地线对阻抗的影响3.4.1 地线与信号线之间的间距对信号线阻抗的影响3.4.2 屏蔽地线线宽对阻抗的影响3.5 阻抗控制案例4 特殊信号的处理5 过孔5.1 过孔模型5.1.1 过孔的数学模型5.1.2 对过孔模型的影响因素5.2 过孔对信号传导与辐射发射影响5.2.1 过孔对阻抗控制的影响5.2.2 过孔数量对信号质量的影响6 跨分割区及开槽的处理6.1 开槽的产生6.1.1 对电源/地平面分割造成的开槽6.2 开槽对PCB板EMC性能的影响6.2.1 高速信号与低速信号的面电流分布6.2.2 分地"的概念6.2.3 信号跨越电源平面或地平面上的开槽的问题6.3 对开槽的处理6.3.1 需要严格的阻抗控制的高速信号线,其轨线严禁跨分割走线6.3.2 当PCB板上存在不相容电路时,应该进行分地的处理6.3.3 当跨开槽走线不可避免时,应该进行桥接6.3.4 接插件〔对外不应放置在地层隔逢上6.3.5 高密度接插件的处理6.3.6 跨"静地"分割的处理7 信号质量与EMC 7.1 EMC简介7.2 信号质量简介7.3 EMC与信号质量的相同点7.4 EMC与信号质量的不同点7.5 EMC与信号质量关系小结第三部分背板的EMC设计1 背板槽位的排列1.1 单板信号的互连要求1.2 单板板位结构1.2.1 板位结构影响;1.2.2 板间互连电平、驱动器件的选择2 背板的EMC设计2.1 接插件的信号排布与EMC设计2.1.1 接插件的选型2.1.2 接插件模型与针信号排布2.2 阻抗匹配2.3 电源、地分配2.3.1 电源分割及热插拔对电源的影响2.3.2 地分割与各种地的连接2.3.3屏蔽层第四部分射频PCB的EMC设计1 板材1.1 普通板材1.2 射频专用板材2 隔离与屏蔽2.1 隔离2.2 器件布局2.3 敏感电路和强辐射电路2.4 屏蔽材料和方法2.5 屏蔽腔的尺寸3 滤波3.1 电源和控制线的滤波3.2 频率合成器数据线、时钟线、使能线的滤波4 接地4.1 接地分类4.2 大面积接地4.3 分组就近接地4.4 射频器件接地4.4 接地时应注意的问题4.5 接地平面的分布5 布线5.1 阻抗控制5.2 转角5.3 微带线布线5.4 微带线耦合器5.5 微带线功分器5.6 微带线基本元件5.7 带状线布线5.8 射频信号走线两边包地铜皮6 其它设计考虑第一部分布局1 层的设置在PCB的EMC设计考虑中,首先涉及的便是层的设置;单板的层数由电源、地的层数和信号层数组成;电源层、地层、信号层的相对位置以及电源、地平面的分割对单板的EMC指标至关重要。