TimeQuest 使用步骤

- 格式:docx

- 大小:1.06 MB

- 文档页数:13

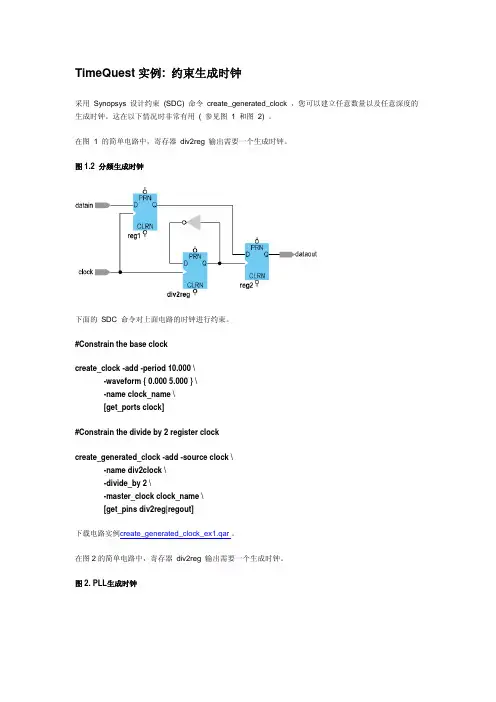

TimeQuest实例: 约束生成时钟采用 Synopsys 设计约束 (SDC) 命令 create_generated_clock ,您可以建立任意数量以及任意深度的生成时钟。

这在以下情况时非常有用 ( 参见图 1 和图 2) 。

在图 1 的简单电路中,寄存器 div2reg 输出需要一个生成时钟。

图1.2 分频生成时钟下面的 SDC 命令对上面电路的时钟进行约束。

#Constrain the base clockcreate_clock -add -period 10.000 \-waveform { 0.000 5.000 } \-name clock_name \[get_ports clock]#Constrain the divide by 2 register clockcreate_generated_clock -add -source clock \-name div2clock \-divide_by 2 \-master_clock clock_name \[get_pins div2reg|regout]下载电路实例create_generated_clock_ex1.qar 。

在图2的简单电路中,寄存器 div2reg 输出需要一个生成时钟。

图2. PLL生成时钟下面的 SDC 命令对上面电路的时钟进行约束。

#Constrain the base clockcreate_clock -add -period 10.000 \-waveform { 0.000 5.000 } \-name clock_name \[get_ports clock]#Constrain the output clock clockcreate_generated_clock -add -source PLL_inst|INCLK[0] \ -name PLL_inst|CLK[1] \-multiply_by 2 \-master_clock clock_name \[get_pins PLL_inst|CLK[1]]下载电路实例create_generated_clock_pll.qar。

时间获取函数timegetsystemtime是Windows API中的一个函数,它用于获取当前系统的时间。

这个函数返回的时间是以毫秒为单位的整数值,表示自系统启动以来经过的毫秒数。

在本文中,我将深入探讨timegetsystemtime的用法,主要包括其功能、调用方法以及相关注意事项。

1. timegetsystemtime的功能timegetsystemtime函数是一个非常有用的时间获取函数,它可以帮助我们获取系统的当前时间。

由于返回的是以毫秒为单位的时间值,因此可以用于各种时间相关的应用和计算,比如定时操作、时间间隔计算等。

2. timegetsystemtime的调用方法要使用timegetsystemtime函数,首先需要包含Windows.h头文件,然后就可以直接调用这个函数。

它的原型定义如下:```cvoid timegetsystemtime(LPSYSTEMTIME lpSystemTime)```在调用这个函数时,需要传入一个SYSTEMTIME结构体指针,用于存储获取到的系统时间信息。

这个结构体包括年、月、日、时、分、秒、毫秒等成员,可以详细描述一个时间点的信息。

调用示例:SYSTEMTIME st;timegetsystemtime(&st);```通过这种调用方法,就可以获取到当前系统的时间,并存储在st结构体中。

3. 注意事项在使用timegetsystemtime函数时,需要注意一些问题。

由于返回的时间是一个以毫秒为单位的整数值,因此可能会导致溢出问题。

在长时间运行的系统中,这个值可能会变得非常大,导致溢出。

在使用这个时间值时,需要进行适当的范围判断和处理。

timegetsystemtime返回的时间值是从系统启动开始计算的,因此无法直接表示一个具体的日历时间。

如果需要获取当前的日历时间,可以结合其他函数来进行转换和处理。

4. 个人观点和理解我个人认为,timegetsystemtime函数是一个非常方便实用的系统时间获取函数。

一、为什么一定要搞定为什么一定要搞定时序分析在ASIC设计中的重要性毋须多说(我也不甚了解)。

在FPGA设计中,很少进行细致全面的时序约束和分析,Fmax是最常见也往往是一个设计唯一的约束。

这一方面是由FPGA的特殊结构决定的,另一方面也是由于缺乏好用的工具造成的。

好的时序约束可以指导布局布线工具进行权衡,获得最优的器件性能,使设计代码最大可能的反映设计者的设计意图。

花些功夫在静态时序分析上既可以保证设计质量,也可以促使设计者再认识自己的代码。

这后一点,对于我们这些逻辑设计初学者来说,尤为重要。

从门级(在Altera的FPGA 器件中是LE级)再认识自己的代码,可以更深入地体会语言的特点,也可以更深入地理解综合工具对语言的处理,对于设计能力的提高帮助很大。

TimeQuest是Altera在6.0版的软件中加入的具备ASIC设计风格的静态时序分析(STA)工具。

通过初步试用和观看网络教程,我感觉TimeQuest确实比Timng Analyzer 功能强大一些,而且使用界面比较友好,易于进行深入的时序约束和结果分析。

TimeQuest采用Synopsys Design Constraints(SDC)文件格式作为时序约束输入,不同于Timing Analyzer采用的Quartus Settings File(QSF)约束文件。

这正是TimeQuest 的优点:采用行业通用的约束语言而不是专有语言,有利于设计约束从FPGA向ASIC设计流程迁移;有利于创建更细致深入的约束条件。

二、时序分析基本概念时序分析基本概念以下内容译自Quartus II Version 10.0 Handbook, Volume 3:Verification的SectionII 7.3:Timing Analysis Overview部分。

TimeQuest需要读入布局布线后的网表才能进行时序分析。

读入的网表是由以下一系列的基本单元构成的:1. Cells:Altera器件中的基本结构单元(例如,查找表、寄存器、IO单元、PLL、存储器块等)。

![Quartus II 11[1].0安装教程](https://uimg.taocdn.com/418b861255270722192ef791.webp)

创造平台——Quartus II 11.0 安装指南一、Altera Quartus II 11.0套件介绍所谓巧妇难为无米之炊,再强的软硬件功底,再多的思维创造力,没有软件的平台,也只是徒劳。

因此,一切创造的平台——Quartus II 软件安装,由零开启的世界,便从此开始。

自从Bingo 2009年开始接触FPGA,Quartus II 版本的软件从n年前的5.1版本到今天的最新发布的11.0,都使用过;当然对于软件核心构架而言,万变不离其宗。

虽然多多少少有点bug,但这10多个版本发展到了现在,能看到Altera一直在努力,致力于更完美的用户界面,更快的综合速度的软件开发。

虽然很多老的工程师不介意积极更新软件,但一次一次的视觉冲击,版本的更新,承受不住古老,使用11.0从某种意义上讲,还是有很大的好处的。

本书中以Quartus II 11.0 软件的安装为例,作为安装指南。

此外,关于Quartus II 10.0 以前版本,安装都大同小异,Bingo曾经写过“Quartus II 9.1的安装指南.pdf”,下载地址为/lib/detail.aspx?id=86239,或者在线浏览网页:/detail/9878.html/crazybingo/archive/2010/05/14/1735341.html如有需要,请自行下载。

对于Quartus II 11.0 ,最基本的套件包含以下三个不部分:(1)Quartus II 11.0 for windows软件(2)Quartus II 11.0 Devices for windows 硬件库(3)Altera-Modelsim for windows第三方仿真器二、Quartus II 11.0 套件下载1.Quartus II 11.0套件下载Quartus II 11.0 与之前的软件有些不同,有以下几个不同的地方:(1)Quartus II 9.1之前的软件自带仿真组件,而之后软件不再包含此组件,因此必须要仿真安装Modelsim。

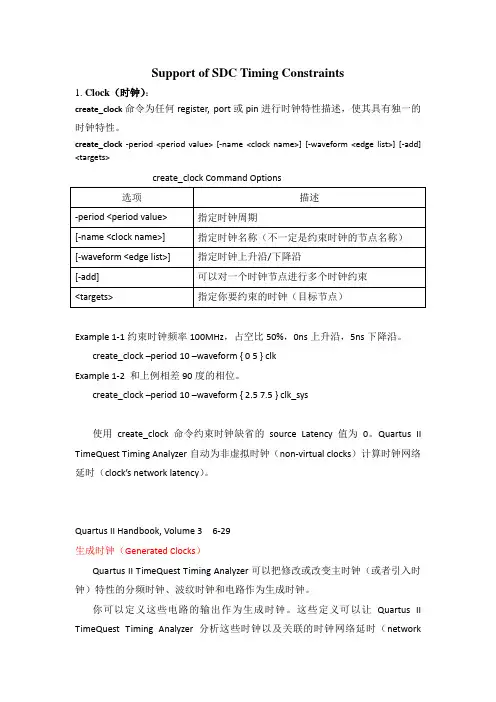

Support of SDC Timing Constraints1. Clock(时钟):create_clock命令为任何register, port或pin进行时钟特性描述,使其具有独一的时钟特性。

create_clock-period <period value> [-name <clock name>] [-waveform <edge list>] [-add] <targets>create_clock Command OptionsExample 1-1约束时钟频率100MHz,占空比50%,0ns上升沿,5ns下降沿。

create_clock –period 10 –waveform { 0 5 } clkExample 1-2 和上例相差90度的相位。

create_clock –period 10 –waveform { 2.5 7.5 } clk_sys使用create_clock命令约束时钟缺省的source Latency值为0。

Quartus IITimeQuest Timing Analyzer自动为非虚拟时钟(non-virtual clocks)计算时钟网络延时(clock’s network latency)。

Quartus II Handbook, Volume 3 6-29生成时钟(Generated Clocks)Quartus II TimeQuest Timing Analyzer可以把修改或改变主时钟(或者引入时钟)特性的分频时钟、波纹时钟和电路作为生成时钟。

你可以定义这些电路的输出作为生成时钟。

这些定义可以让Quartus II TimeQuest Timing Analyzer分析这些时钟以及关联的时钟网络延时(networklatency)。

使用create_generated_clock命令定义生成时钟。

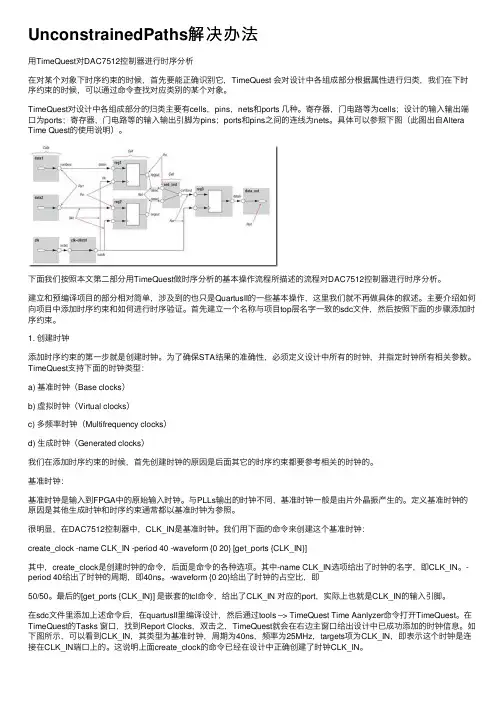

UnconstrainedPaths解决办法⽤TimeQuest对DAC7512控制器进⾏时序分析在对某个对象下时序约束的时候,⾸先要能正确识别它,TimeQuest 会对设计中各组成部分根据属性进⾏归类,我们在下时序约束的时候,可以通过命令查找对应类别的某个对象。

TimeQuest对设计中各组成部分的归类主要有cells,pins,nets和ports ⼏种。

寄存器,门电路等为cells;设计的输⼊输出端⼝为ports;寄存器,门电路等的输⼊输出引脚为pins;ports和pins之间的连线为nets。

具体可以参照下图(此图出⾃Altera Time Quest的使⽤说明)。

下⾯我们按照本⽂第⼆部分⽤TimeQuest做时序分析的基本操作流程所描述的流程对DAC7512控制器进⾏时序分析。

建⽴和预编译项⽬的部分相对简单,涉及到的也只是QuartusII的⼀些基本操作,这⾥我们就不再做具体的叙述。

主要介绍如何向项⽬中添加时序约束和如何进⾏时序验证。

⾸先建⽴⼀个名称与项⽬top层名字⼀致的sdc⽂件,然后按照下⾯的步骤添加时序约束。

1. 创建时钟添加时序约束的第⼀步就是创建时钟。

为了确保STA结果的准确性,必须定义设计中所有的时钟,并指定时钟所有相关参数。

TimeQuest⽀持下⾯的时钟类型:a) 基准时钟(Base clocks)b) 虚拟时钟(Virtual clocks)c) 多频率时钟(Multifrequency clocks)d) ⽣成时钟(Generated clocks)我们在添加时序约束的时候,⾸先创建时钟的原因是后⾯其它的时序约束都要参考相关的时钟的。

基准时钟:基准时钟是输⼊到FPGA中的原始输⼊时钟。

与PLLs输出的时钟不同,基准时钟⼀般是由⽚外晶振产⽣的。

定义基准时钟的原因是其他⽣成时钟和时序约束通常都以基准时钟为参照。

很明显,在DAC7512控制器中,CLK_IN是基准时钟。

TimeQuest快速入门简介本教程介绍用TimeQuest Analyzer进行时序约束和静态时序分析的必要步骤。

所用示例文件在\qdesigns\fir_filter文件夹下。

TimeQuest约束步骤下面的步骤描述了用TimeQuest对设计进行时序约束的步骤,每一步操作包含GUI和Command-line的操作方法。

第1步:在QuartusII中打开&建立工程启动QuartusII软件,在\qdesigns\fir_filter文件夹下打开工程compile_fir_filter.qpf。

第2步:设置TimeQuest Analyzer默认状态下,QuartusII使用Classic Timing Analyzer作为默认的时序分析工具。

需要在QuatusII中进行如下设置将TimeQuest Analyzer设为当前工程的时序分析器。

在【Assignment】菜单下单击【Settings】,在【Category】列表中展开【Timing Analysis Processing】,选择【Use TimeQuest Analyzer during compilation】,然后点击【OK】即可。

第3步:进行初始的编译在将时序约束应用到设计之前,需要为TimeQuest创建初始的数据。

初始数据是通过post-map结果产生的。

步骤如下:在【Processing】菜单栏下,选择【Start】/【Start Analysis&Synthesis】。

通过运行【Analysis&Synthesis】产生post-map数据。

还可以用post-fit网表来产生初始数据。

但是创建post-map数据所用时间更少,而且post-map数据对本设计示例工程来说已经够用。

第4步:启动TimeQuest Analyzer为了创建并验证时序约束,需要启动TimeQuest Analyzer。

timequest静态时序分析学习笔记之命令约束第⼆章约束命令Timequest共包括13条约束命令(从timequest⼯具constrants下拉菜单可选的约束命令,实际不⽌这么多),分别是: Creat clock Creat generated clock Set clock lantency Set clock uncertainty Set clock groups Remove clocks Set input delay Set output delay Set false path Set multicycle path Set muximum delay Set minimum delay Set muximum skew各个约束命令说明2.1 Create_clock 两个作⽤:(page73) 1,约束从外部进⼊FPGA的时钟。

2,创建虚拟时钟,虚拟时钟是指外部IC芯⽚⽤到的时钟,它们不是FPGA内部的时钟域。

Create_clock不能⽤于约束FPGA内部的时钟。

(page74)在约束命令都是添加在SDC⽂件⾥⾯,所以们得先创建⼀个SDC⽂件,通过timequest的cronstraints下拉菜单的generated SDC file选项可以⽣成。

⽽我添加每⼀条命令都是通过quartus 的Edit下拉菜单insert constraint选项添加的。

我们选择通过quartus 的Edit下拉菜单insert constraint选项添加Create_clock约束命令,弹出如图11的会话框,Clock name 指你想约束的时钟名称,任意起,不过最好根据⾃⼰设计的模块起,便于分析阅读,不然时钟多了,⾃⼰都不知道哪个时钟是哪个模块的。

Period 约束时钟的周期 Rising 指时钟上升沿的开始时间 Falling 指时钟下降沿的开始时间图11 Targets 指你想约束的哪个FPGA 管脚。

用Quartus II Timequest Timing Analyzer进行时序分析:实例讲解(一)(2012-06-21 10:25:54)▼标签:杂谈一,概述用Altera的话来讲,timequest timing analyzer是一个功能强大的,ASIC-style的时序分析工具。

采用工业标准--SDC(synopsys design contraints)--的约束、分析和报告方法来验证你的设计是否满足时序设计的要求。

在用户的角度,从我使用TimeQuest的经验看,它与IC 设计中经常用到的比如prime time,time craft等STA软件是比较类似的。

用过prime time或time craft的朋友是非常容易上手的。

在这一系列的文章里,我将会拿一个DAC7512控制器的verilog设计作为例子,详细讲解如何使用TimeQuest进行时序设计和分析。

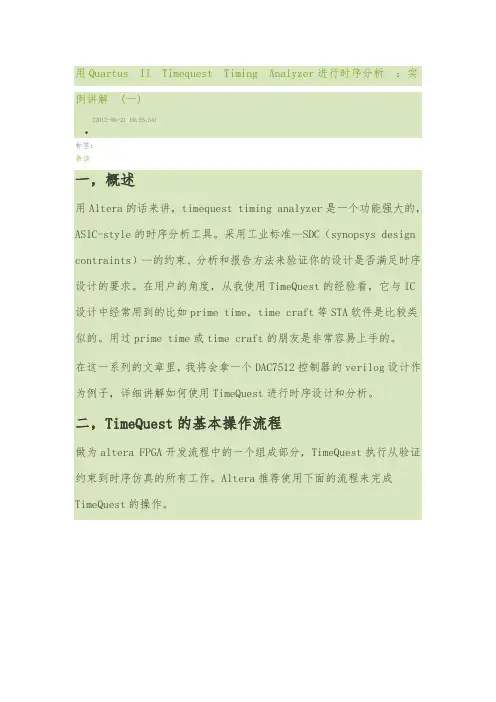

二,TimeQuest的基本操作流程做为altera FPGA开发流程中的一个组成部分,TimeQuest执行从验证约束到时序仿真的所有工作。

Altera推荐使用下面的流程来完成TimeQuest的操作。

1. 建立项目并加入相关设计文件不管做什么事情,都需要有一个目标或者说对象。

我们用TimeQuest做时序分析,当然也需要一个对象,这个对象实际上就是我们的设计。

所以首先是要建立一个Quartus II的项目,并把所有需要的设计文件都加入到项目中去。

需要注意的一点是,这里的设计文件,不仅仅包含逻辑设计相关的文件,也包含已经存在的时序约束文件,当然,需要以synopsys Design Constraints(.sdc)的格式存在的。

2. 对项目进行预编译(initial compilation)项目建立以后,如果从来没有对项目进行过编译的话,就需要对项目进行预编译。

这里的预编译是对应于全编译(full compilation)来讲的,我们可以理解为预编译是对项目进行部分的编译,而全编译是对项目进行完整的编译。

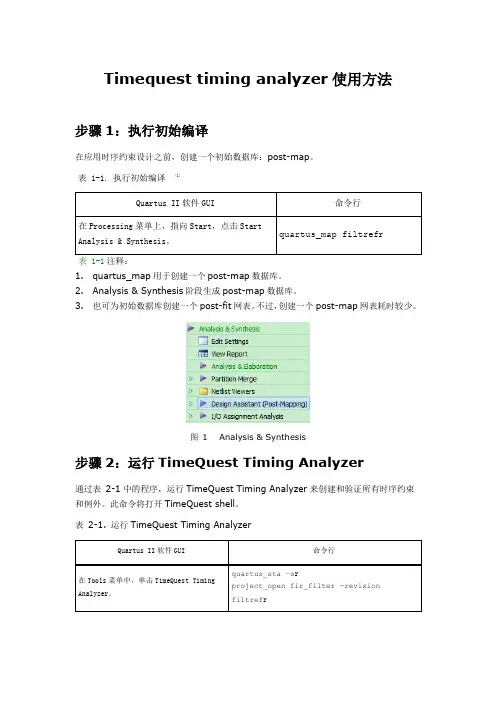

Timequest timing analyzer使用方法步骤1:执行初始编译在应用时序约束设计之前,创建一个初始数据库:post-map。

表 1-1. 执行初始编译(1)3.也可为初始数据库创建一个post-fit网表。

不过,创建一个post-map网表耗时较少。

图1 Analysis & Synthesis当您直接从Quartus II软件中运行TimeQuest Timing Analyzer时,当前工程将会自动打开。

如果使用GUI,那么当出现下面的消息时,请选择No:"No SDC files were found in the Quartus Settings File and filtref.sdc doesn't exist. Would you like to generate an SDC file from the Quartus Settings File?"图2TimeQuest Timing Analyzer步骤3:创建一个Post-map时序网表在指定时序要求之前,请创建一个时序网表。

表3-1. 创建一个Post-Map时序网表注意:不要在Tasks面板中使用Create Timing Netlist命令来创建一个post-map时序网表。

默认情况下,Create Timing Netlist创建一个post-fit数据库。

图3 Create Timing Netlist图4 Input netlist图5waiting图7Create clock图8设置参数图9指定时钟图10 Create clock设置完毕图11Drive PLL clocks图12Update Timing Netlist步骤6:保存到SDC文件在为设计指定时钟约束并更新时序网表后,您可以通过表6-1中的程序来选择创建SDC 文件。

通过TimeQuest Timing Analyzer GUI或者在控制台(console)中指定的约束不会自动保存。

qdatetimeedit 用法QDateTimeEdit 是Qt 框架提供的一个用于编辑日期和时间的小部件控件。

它在图形用户界面(GUI)应用程序中非常有用,可以让用户选择特定的日期和时间。

本文将介绍QDateTimeEdit 控件的用法,并提供一步一步的回答,以帮助读者深入了解和使用QDateTimeEdit 控件。

一、QDateTimeEdit 控件的基本介绍QDateTimeEdit 是Qt 中的一个小部件(QWidget)类,继承自QAbstractSpinBox 类。

它允许用户通过鼠标或键盘来选择日期和时间。

QDateTimeEdit 提供了一个编辑框和一个下拉框,下拉框中显示一个日历来帮助用户选择日期。

二、安装Qt要使用QDateTimeEdit 控件,首先需要安装Qt 开发环境。

Qt 提供了多个版本供选择,你可以根据自己的需求选择合适的版本进行安装。

安装完毕后,打开Qt 的开发环境,我们可以开始使用QDateTimeEdit 控件了。

三、创建QDateTimeEdit 控件下面是创建QDateTimeEdit 控件的基本步骤:1. 在Qt 的开发环境中,打开你想要添加QDateTimeEdit 控件的界面文件(例如.ui 文件)。

2. 在界面编辑器中找到控件工具箱(Widget Box)。

3. 在控件工具箱中找到QDateTimeEdit 控件,将其拖拽到界面中的适当位置。

四、设置QDateTimeEdit 的属性通过设置QDateTimeEdit 的属性,可以控制其外观和行为。

常用的属性包括格式(displayFormat)、最小日期(minimumDate)、最大日期(maximumDate)等。

以下是一些常用的设置方法:1. 设置日期和时间格式:QDateTimeEdit *dateTimeEdit = new QDateTimeEdit();dateTimeEdit->setDisplayFormat("dd.MM.yyyy hh:mm:ss");2. 设置最小日期和时间:QDateTimeEdit *dateTimeEdit = new QDateTimeEdit();dateTimeEdit->setMinimumDateTime(QDateTime::currentDateTim e().addDays(-30));3. 设置最大日期和时间:QDateTimeEdit *dateTimeEdit = new QDateTimeEdit();dateTimeEdit->setMaximumDateTime(QDateTime::currentDateTim e().addDays(30));五、获取QDateTimeEdit 的值要获取QDateTimeEdit 控件的日期和时间值,可以使用QDateTimeEdit 的date() 和time() 方法。

1.在quartus中对设计进行时序分析2.1TimeQuest 工具Quartus® II TimeQuest Timing Analyzer是一个功能强大的ASIC型时序分析工具,能够以工业标准方法论来约束,分析和报告用户设计中所有逻辑的时序性能。

这个工具是一个严格的静态工具,使用时不需要搭建硬件环境及进行调试。

本节将介绍如何使用Quartus II TimeQuest Timing Analyzer工具的图形化功能来约束,分析及报告设计中的时序结果。

使用这个工具,我们要指定初始时序信息,包括时钟,时序例外以及信号传输中的到达和要求的时间。

我们通过后缀名为sdc(Synopsys Design Constraints)的文件来指定时序要求,然后The Quartus II Fitter将优化逻辑布局等来满足我们的时序要求。

在时序分析过程中,Quartus II TimeQuest Timing Analyzer分析设计中的每一条时序路径,计算每条路径的延迟,检查是否存在时序违例,并且报告时序结果。

一旦发现时序违例,可以精确定位到违例路径的时序细节,然后用户约束它以纠正违例。

如果时序分析没有报告违例,那么恭喜你,在这个器件中的逻辑行为将与你的设计意图一致。

使用TimeQuest分析设计时序的一般步骤为:图使用TimeQuest分析设计时序的一般步骤第一次编译时我们需要得到没有设置约束的时序结果,有助于我们给设计添加约束。

第二次编译的时序需要把包含指定时序要求的文件(后缀为sdc 的文件)添加到工程文件中执行编译,这样工具就能够按照我们的时序要求来进行映射了。

2.2timequest快速入门示例下面我们按照altera公司所给的timequest快速入门教程示例来讲解该时序分析工具的大致用法。

使用的工具是目前使用最广泛的quartusII9.1版本提供的TimeQuest工具。

首先我们打开quartus工具的例程。

Quartus 12的TimeQuest Timing Analyzer1.在Quartus II软件打开和设置设计安装路径下\qdesigns\fir_fliter文件。

在Processing 菜单上,指向Start,点击Start Analysis &Synthesis。

2.运行TimeQuest Timing Analyzer在Tools 菜单中,单击TimeQuest Timing Analyzer,如图。

3.创建一个Post-Map时序网表1. 在Netlist 菜单上,点击Create Timing Netlist。

出现Create Timing Netlist 对话框。

2. 在Input netlist 中,选择Post-Map。

3. 点击OK。

注意:您不能在Tasks面板中使用Create Timing Netlist命令来创建一个post-map 时序网表。

默认情况下,Create Timing Netlist 需要一个post-fit 数据库。

Input netlist选"Post-map",按OK,即会建立Timing Netlist完成。

(看到"Create Timing Netlist"項,打綠色勾勾) (看到"Create Timing Netlist"项,打绿色勾勾)5.指定时序要求必须在fir_filter 设计中定义两个时钟。

每个时钟的属性列表请参考。

1. 在Constraints 菜单中,点击Create Clock。

出现CreateClock 对话框。

2. 在表2-2 中对50 MHz 时钟指定参数。

对100 MHz 时钟重复这些步骤。

执行到第三步时会出现下图所示对话框,进行相应设置。

6.更新时序网表在Tasks 面板中,双击Update Timing Netlist 命令。

7保存Synopsys Design Constraints (SDC)文件。

Section 1: Getting StartedCore Timing在编译工程以后,调用Timequest。

如果SDC文件没有创建,那么可以到File->New 选项创建一个新的SDC文件。

Constraining the Core with Four Commands每个 .sdc文件都应当以下面四个命令作为开头:∙- create_clock∙-derive_pll_clocks∙-derive_clock_uncertainty∙-set_clock_group前三个命令是重要的。

命令的细节描述可以通过-long_help帮助显示出来:∙create_clock -long_help∙derive_pll_clocks -long_help∙derive_clock_uncertainty -long_help∙set_clock_groups -long_helpcreate_clock当我们创建一个新的SDC文件,首先要做的就是约束输入FPGA端口的时钟信号,通过使用create_clock命令。

基本的格式如下: create_clock -name sys_clk -period 8.0 [get_portsfpga_clk]注意:1.上面的命令创建了一个周期为8ns的系统时钟sys_clk,并将该时钟连接到我们FPGA的时钟输入端口fpga_clk;2.Tcl和SDC是case-sensitive的,所以请确认fpga_clk 和我们设计的时钟参数相符合;3.该时钟在0ns时刻产生一个上升沿,具有50%的占空比,因而其下降沿在4ns处。

如果我们想产生不同占空比,或者添加一个时钟偏移offset,可以使用-waveform选项。

但很少需要这么做。

4.我们经常会去创建一个与端口port同名的时钟信号,这种做法是不合法的。

下面的例子:create_clock -name fpga_clk -period 8.0 [get_ports fpga_clk]现在有两个单元都有name叫做fpga_clk,一个是端口,一个我们定义的时钟。

FPGA时序约束—TimeQuest基础分类:FPGA相关2012-02-19 11:20 830人阅读评论(0) 收藏举报时序约束的目的是:规范设计的时序行为,表达设计者所期望满足的时序条件,指导综合和布局布线阶段的优化算法等,作用:提高系统设计的fmax、得到正确的时序分析报告一、 TimeQuest分析流程二、 TimeQuest分析步骤1. 在工程编译之前,先要选择时序分析工具,这里选择TimeQuest工具:Setting/Timing Analysis Setting/Use TimeQuest Timing Analyzer during compilation选项2. 加入SDC文件,可以先运行TimeQuest编写SDC文件或者先建立一个空的SDC文件(按照个人习惯),也可以加入TCL文件,这里和SDC文件是等价的,当然用TCL工具会更加方便。

3. 开始编译QuartusII的整个工程4. 启动TimeQuest工具此图为TimeQuest的开始界面,1) Generate timing netlist:右键Start产生时序网表2) Read in SDC File :读取在之前加入SDC文件,便于在SDC文件中在继续加入其他的约束3) 打开SDC文件就可以加入自己要加的约束了4) 在Constraints里有一些加入约束的工具,可以一步一步的加入当然,这里有个先后时序,有的人经验比较丰富的,先建立SDC文件,然后再Timequest 中看分析结果,或进一步优化约束,作为入门可以在TimeQuest中加入约束,然后再编译再查看分析结果。

5)查看分析结果在Report是中查看Setup Hold等分析结果根据报告分析时序违规路径,具体的SDC文件编写和时序分析在后面的博文中会陆续讲到。

101 Innovation Drive San Jose, CA 95134 TimeQuest Timing AnalyzerQuick Start TutorialSoftware Version:9.1Document Version: 1.1Document Date:© December 2009UG-TMQSTANZR-1.1Copyright © 2009 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending ap-plications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.UG-TMQSTANZR-1.1© December 2009Altera CorporationTimeQuest Timing Analyzer Quick Start TutorialContentsChapter 1.About this Tutorial Chapter 2.Quick Start TutorialSystem Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1Procedures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1Step 1: Open and Setup Your Design in the Quartus II Software . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1Step 2: Setup the TimeQuest Timing Analyzer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1Step 3: Perform Initial Compilation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–2Step 4: Launch the TimeQuest Timing Analyzer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–2Step 5: Create a Post-Map Timing Netlist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–3Step 6: Specify Timing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–3Step 7: Update the Timing Netlist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–4Step 8: Save the Synopsys Design Constraints (SDC) File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–4Step 9: Generate Timing Reports for the Initial Timing Netlist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–5Step 10: Save Constraints to an SDC File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–7Step 11. Perform Timing-Driven Compilation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–8Step 12. Verify Timing in the TimeQuest Timing Analyzer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–8Conclusion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–12Chapter 3.Script ExamplesCommands and Tcl Scripts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–1Additional InformationRevision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . About–1How to Contact Altera . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . About–1Typographic Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . About–1ivTimeQuest Timing Analyzer Quick Start Tutorial© December 2009Altera Corporation1.About this Tutorialthe TimeQuest Timing Analyzer. For this tutorial, use the fir_filter design that shipswith the Quartus® II software. Figure1–1 shows the fir_filter design schematic. Figure1–1.fir_filter Design Schematic© December 2009 Altera Corporation TimeQuest Timing Analyzer Quick Start Tutorial1–2Chapter 1:About this Tutorial TimeQuest Timing Analyzer Quick Start Tutorial© December 2009Altera Corporation© December 2009 Altera CorporationTimeQuest Timing Analyzer Quick Start Tutorial2.Quick Start TutorialSystem RequirementsFor this tutorial, use Stratix, Cyclone, MAX II, or newer device families (you can also use MAX 3000 and MAX 7000 device families) with the Quartus ® II software beginning with version 6.0. APEX, FLEX, and Mercury device families are not supported.ProceduresUse the following steps to constrain and analyze a design with the TimeQuest Timing Analyzer. Each step includes the GUI procedure and the command-line equivalent.Step 1: Open and Setup Your Design in the Quartus II SoftwareIn the Quartus II software, browse to and open the fir_filter located in the <qdesign folder >/fir_filter/ folder. Use the GUI or the command-line equivalent procedures in Table 2–1.Step 2: Setup the TimeQuest Timing AnalyzerBy default, the Quartus II software uses the Classic Timing Analyzer as the timing analysis tool for designs targeting the Cyclone device family. Specify the TimeQuest Timing Analyzer as the timing analysis tool in the Quartus II software to use in the compilation flow for the fir_filter project.1This step is not required for all projects. The newer FPGA families default to the TimeQuest Timing Analyzer.Specify the TimeQuest Timing Analyzer as the timing analysis tool in the Quartus II software with the procedures in Table 2–2.Table 2–1.Opening and Setting Up Your DesignProcedures Table2–2.Specifying the TimeQuest Timing Analyzer as DefaultStep 3: Perform Initial CompilationBefore applying timing constraints to the design, create an initial database with theprocedures in Table2–3. The initial database is generated from the post-map results ofthe design.Table2–3.Performing Initial Compilation (Note1)Note to Table2–3:(1)The quartus_map is used to create a post-map database.The Analysis & Synthesis step generates a post-map database.1You can also create a post-fit netlist for the initial database. However, creating a post-map is less time consuming and is sufficient for this tutorial example.Step 4: Launch the TimeQuest Timing AnalyzerLaunch the TimeQuest Timing Analyzer to create and verify all timing constraints andexceptions with the procedures in Table2–4. This command opens the TimeQuestshell.Table2–unching the TimeQuest Timing Analyzer1When you launch the TimeQuest Timing Analyzer directly from the Quartus IIsoftware, the current project is automatically opened.If you use the GUI, select No when the following message appears:"No SDC files were found in the Quartus Settings File and filtref.sdc doesn't exist.Would you like to generate an SDC file from the Quartus Settings File?"TimeQuest Timing Analyzer Quick Start Tutorial© December 2009 Altera CorporationProceduresStep 5: Create a Post-Map Timing NetlistBefore specifying the timing requirements, create a timing netlist. You can create atiming netlist from a post-map or post-fit database. In this step, create a timing netlistfrom the post-map database you created in “Step 3: Perform Initial Compilation” withthe procedures in Table2–5.Table2–5.Creating a Post-Map Timing Netlist1You cannot use the Create Timing Netlist command in the Tasks pane to create a post-map timing netlist. By default, the Create Timing Netlist requires a post-fitdatabase.Step 6: Specify Timing RequirementsYou must define two clocks in the fir_filter design. Refer to Table2–6 for a list ofproperties for each clock.Table2–6.Clocks in fir_filter DesignCreate the clocks in the fir_filter design and assign the proper clock ports with theprocedures in Table2–7.f For more information about constraints supported by the TimeQuest TimingAnalyzer, refer to the TimeQuest Timing Analyzer chapter in volume 3 of the Quartus IIHandbook.Table2–7.Creating Clocks and Assigning Clock Ports1By default, the create_clock command assumes a 50/50 duty cycle if the-waveform option is not used.© December 2009 Altera Corporation TimeQuest Timing Analyzer Quick Start TutorialProceduresf For more information about creating clocks of different duty cycles, refer to theTimeQuest Timing Analyzer chapter in volume 3 of the Quartus II Handbook.After you complete the procedure shown in Table2–7, the clock definition iscomplete.Step 7: Update the Timing NetlistAfter you create timing constraints or exceptions, update the timing netlist to applyall timing requirements to the timing netlist (the new clk and clkx2 clockconstraints) with the procedures in Table2–8.1You must update the timing netlist whenever new timing constraints are applied. Table2–8.Updating the Timing NetlistStep 8: Save the Synopsys Design Constraints (SDC) FileYou have the option of creating an SDC file after specifying the clock constraints forthe design and updating the timing netlist with the procedures in Table2–9.Constraints that have been specified with the TimeQuest Timing Analyzer GUI or inthe console are not automatically saved.1If you inadvertently overwrite any of your constraints later in the design flow, use this initial SDC file to restore all of your constraints.The initial SDC file can act as the “golden” SDC file that contains the originalconstraints and exceptions for the design.Table2–9.Saving the SDC FileThe new filtref.sdc file contains the constraints and false path exceptions for the twoclocks that you defined in “Step 6: Specify Timing Requirements”.The Write SDC File command can overwrite any existing SDC file. When this occurs,the new SDC file does not maintain order or comments. Therefore, Alterarecommends saving a golden SDC file separately that you can manually edit with atext editor. This allows you to enter comments and organize the file to your ownspecifications.TimeQuest Timing Analyzer Quick Start Tutorial© December 2009 Altera CorporationProceduresStep 9: Generate Timing Reports for the Initial Timing NetlistAfter specifying timing constraints and updating the timing netlist, generate timingreports, which verify that all clocks are properly defined and applied to the correctnodes, for the two clocks you defined with the procedures in Table2–10. TheTimeQuest Timing Analyzer provides easy to use report generation commands thatallow you to verify all timing requirements in the design.Table2–10.Report SDC CommandFigure2–1 shows the Create Clock report that you generate when you click ReportSDC in the Tasks pane.Figure2–1.Generating the SDC Assignments ReportSDC Assignments reports all timing constraints and exceptions specified in thedesign. Two reports are generated: one for the clocks and one for the clock groups.Generate a report that summarizes all clocks in the design with the procedures inTable2–11.Table2–11.Generating the Report Clocks ReportFigure2–2 shows the Clocks Summary report.Figure2–2. Clocks Summary ReportUse the Report Clock Transfers command to generate a report to verify that allclock-to-clock transfers are valid with the procedures in Table2–12. This reportcontains all clock-to-clock transfers in the design.© December 2009 Altera Corporation TimeQuest Timing Analyzer Quick Start TutorialProcedures Table2–12.Generating the Report Clock TransfersFigure2–3 shows the Clock Transfers report.Figure2–3. Clock Transfers ReportThe Clock Transfers report indicates that a clock-to-clock transfer exists between theclk source and the clkx2 destination. There are 16 instances where clk clocks thesource node and where clkx2 clocks the destination node.In the fir_filter design, you do not have to analyze clock transfers from clk to clkx2because they are false paths. Declare the paths from clk to clkx2 as false paths withthe procedures in Table2–13. When you complete this procedure, the TimeQuestTiming Analyzer indicates that the Clock Transfers report is outdated.Table2–13.Declaring False Paths1Alternatively, use the set_clock_groups command to declare the paths between the two clock domains as false paths. For example, set_clock_groups-asynchronous -group [get_clocks clk] -group [get_clocks clkx2].This command declares all paths from clk to clkx2 and from clkx2 to clk as falsepaths. This method is preferred.Because you have added a new timing constraint, update the timing netlist with theprocedure in Table2–14.Table2–14.Updating the Timing NetlistTimeQuest Timing Analyzer Quick Start Tutorial© December 2009 Altera CorporationProceduresAfter you enter the set_false_path in the GUI, all generated report panels arelabeled “Out of Date,” indicating that the report panels do not contain results thatreflects the current state of constraints or exceptions in the TimeQuest TimingAnalyzer. To update the report panels, you must regenerate all of the reports.At the command-line, re-enter the commands. In the GUI, right-click on anyout-of-date report in the report panel list and select Regenerate or Regenerate all.After you update the timing netlist, verify that the clock-to-clock transfer has beendeclared false with the procedures in Table2–15.Table2–15.Verifying Using the Report SDC CommandFigure2–4 shows the new SDC Assignments report.Figure2–4.SDC Assignments ReportThe report shown in Figure2–4 indicates that the clock constraints and the false pathsare correct.Use the Report Clocks and Report Clock Transfers commands to verify that the twoclocks have been removed from analysis. Figure2–5 shows the Clock Transfers report.Figure2–5. Clock Transfers Reportf The RR Paths column contains the comment “false path” to indicate that you havedeclared the clock domains as false paths.Step 10: Save Constraints to an SDC FileAfter you specify all clock constraints and false paths for the design, save the timingconstraints and exceptions to an SDC file with the procedures in Table2–16.© December 2009 Altera Corporation TimeQuest Timing Analyzer Quick Start TutorialProcedures Table2–16.Saving Constraints to an SDC File1This procedure overwrites the previously created filtref.sdc file. If you overwrite an SDC with the Write SDC File command, your custom formatting and comments areremoved in the new SDC file.The filtref.sdc file contains the two clock constraints and the false path exceptions.Step 11. Perform Timing-Driven CompilationAfter saving the constraints to the SDC file, run a full compilation on the design tooptimize fitting to meet the constraints. However, before you start a full compilation,add the SDC to your project with the procedures in Table2–17.Table2–17.Adding the SDC File to Your ProjectAfter you add the SDC to your project, run a full compilation on the design with theprocedures in Table2–18.Table2–18.Running a Full CompilationAfter compilation is complete, the TimeQuest Timing Analyzer generates a summaryreport of the clock setup and clock hold checks performed in the Compilation Report.Step 12. Verify Timing in the TimeQuest Timing AnalyzerTo obtain detailed timing analysis data on specific paths, view timing analysis resultsin the TimeQuest Timing Analyzer.1After a full place-and-route is performed, launch the TimeQuest Timing Analyzer as described in “Step 4: Launch the TimeQuest Timing Analyzer”.Generate a post-fit timing netlist, read the SDC file, and update the timing netlist togenerate reports about the latest compilation with the procedures in Table2–19. TimeQuest Timing Analyzer Quick Start Tutorial© December 2009 Altera CorporationProceduresTable2–19.Generating Reports About the Latest Compilation1When you double-click one of the reporting commands, the Create Timing Netlist, Read SDC, and Update Timing Netlist commands are sequentially executed in theTasks pane, automatically setting up the timing netlist.The clock setup check ensures that each register-to-register transfer does not violatethe timing constraints you specified in the SDC. V erify that no violations haveoccurred by generating a clock setup summary check for all clocks in the design withthe procedures in Table2–20.Table2–20.Generating a Clock Setup Summary CheckFigure2–6 shows the Summary (Setup) report.Figure2–6.Summary (Setup) Report1The clkx2 clock does not appear in the Summary (Setup) report because all clock paths between clk and clkx2 have been declared as false paths. In addition, thefir_filter design does not contain any register-to-register paths where a destinationregister path is clocked by clkx2.The Slack column in the Summary (Setup) report indicates that clk fails to meet theconstraint by 11.588 ns. The End Point TNS column is the total of all total negativeslack (TNS) for the specified clock domain. Use this value to gauge the amount offailing paths in the specified clock domain.1For the fir_filter design, the Slack column equals the End Point TNS, indicating that there is only one failing path for the clk clock domain.© December 2009 Altera Corporation TimeQuest Timing Analyzer Quick Start TutorialProceduresTimeQuest Timing Analyzer Quick Start Tutorial© December 2009 Altera Corporation After you generate the Summary (Setup) report, generate a clock hold check summaryfor the design with the procedures in Table 2–21.Figure 2–7 shows the Summary (Hold) report.The Summary (Hold) report indicates that the clk clock node meets the timingconstraints by 0.661 ns.Specify all timing constraints and exceptions prior to performing a full compilationwith the procedures in Table 2–22. This ensures that the Fitter optimizes for the criticalpaths in the design.You can use the Report Unconstrained Paths command to verify that you haveconstrained all paths in the fir_filter design.Figure 2–8 shows the Unconstrained Paths Summary report.The Unconstrained Paths Summary report indicates that there are numerousunconstrained paths and details the types of paths.To fully constrain this design, utilize the full set of SDC constraints provided by theTimeQuest Timing Analyzer.To fully constrain the fir_filter design, constrain all input and output ports. Use theSet Input Delay and Set Output Delay dialog boxes, or the set_input_delay andset_output_delay constraints to specify the input and output delay values.Table 2–21.Generating the Summary (Hold) ReportFigure 2–7.Summary (Hold) ReportTable 2–22.Specifying Timing Constraints and ExceptionsFigure 2–8.Unconstrained Paths Summary ReportProceduresBecause additional constraints are applied to the design, create an additional SDC thatcontains only the input and output constraints with the text editor (for example,inout_delay.sdc). Add the input and output delay assignments shown in Table2–23to the new SDC created in “Step 10: Save Constraints to an SDC File”.Table2–23.Input and Output Delay AssignmentsAll ports should be constrained in the design after you read the SDC containing theinput and output delay constraints.1Remember to update the timing netlist after reading the new constraints. For more information, refer to “Step 7: Update the Timing Netlist”.To verify all ports are constrained in the design, regenerate the Unconstrained PathsSummary report (Figure2–9).Figure2–9.Regenerated Unconstrained Paths Summary ReportGenerate specific timing check reports for clocks or nodes in the design with theprocedures in Table2–24. The procedures in Table2–24 generate a report where clkclocks the destination register to the design destination register busacc:inst3|result and reports the top 10 worst paths.© December 2009 Altera Corporation TimeQuest Timing Analyzer Quick Start TutorialConclusion Table2–24.Generate a Report Timing ReportFigure2–10 shows the Report Timing report.Figure2–10.Report Timing ReportUse the Report Top Failing Paths command in the Tasks pane to generate a reportthat details the top failing paths in the design.ConclusionAs you create new constraints or exceptions, rerun the Quartus II Fitter to optimizethe design based on your new constraints or exceptions. Multiple iterations on thedesign may be necessary to achieve the desired results.TimeQuest Timing Analyzer Quick Start Tutorial© December 2009 Altera Corporation© December 2009 Altera Corporation TimeQuest Timing Analyzer Quick Start Tutorial3.Script ExamplesCommands and Tcl ScriptsThis section includes commands and accompanying Tcl scripts to execute the entireflow from the command line. Use this method to completely execute the entire flow.Enter the command in Example 3–1 at a command prompt to source the scripts.Example 3–2 shows the content of the timequest_setup.tcl script. Use this script tospecify the TimeQuest Timing Analyzer as the default timing analysis tool.1The Classic Timing Analyzer is the default timing analyzer in the Quartus II software.Example 3–3 shows the content of the main_postmap.tcl script. Use this script tocreate post-map data, set up the timing netlist, read in golden.sdc , and generate initialreports for the design.Example 3–1.Source the Scriptsquartus_sh –t timequest_setup.tcl rquartus_sta –t main_postmap.tcl rquartus_sh –t fit_sdc_setup.tcl rquartus_sta –t main_postfit.tcl rExample 3–2.The timeqest_setup.tcl Script#open the filtref projectproject_open filtref r#set the TimeQuest analyzer as the default timing analyzerset_global_assignment -name USE_TIMEQUEST_TIMING_ANALYZER ON r#close the projectproject_close r3–2Chapter 3:Script ExamplesCommands and Tcl ScriptsExample3–3.The main_postmap.tcl Script#file main_postmap.tcl#Include the flow package to create a post-map netlistpackage require ::quartus::flow r#open the project in TimeQuestproject_open filtref r#create a post-map databaseexecute_module -tool map r#create the timing netlist based on the post-map resultscreate_timing_netlist -post_map r#read in the constraints from the golden SDC fileread_sdc golden.sdc r#update the timing netlist with the new constraintsupdate_timing_netlist r#generated a clock reportreport_clocks r#generated a clock-to-clock reportreport_clock_transfers r#delete our post-map timing netlistdelete_timing_netlist r#close the TimeQuest projectproject_close rExample3–4 shows the content of the fit_sdc_setup.tcl script. Use this script to addthe golden.sdc file to the filtref design. This allows the Quartus II Fitter to optimizethe design according to the constraints you specify.Example3–4.The fit_sdc_setup.tcl Script#open the filtref projectproject_open filtref r#add the filtref.sdc file to our Quartus II projectset_global_assignment -name SDC_FILE golden.sdc r#close the projectproject_close rExample3–5 shows the content of the main_postfit.tcl script. Use this script to createa post-fit database, set up the timing netlist, read in the golden.sdc and io_cons.sdcfiles, and generate reports for the design.TimeQuest Timing Analyzer Quick Start Tutorial© December 2009 Altera CorporationCommands and Tcl ScriptsExample3–5.The main_postfit.tcl Script#Include the flow package to create a post-fit netlistpackage require ::quartus::flow r#open the project in TimeQuestproject_open filtref r#create a post-fit databaseexecute_module -tool fit r#create a post-fit timing netlistcreate_timing_netlist r#read the golden SDC file and the I/O SDC fileread_sdc golden.sdc rread_sdc io_cons.sdc r#update the post-fit timing netlist with constraintsupdate_timing_netlist r#report unconstrained pathsreport_clocks rcreate_timing_summary -setup rcreate_timing_summary -hold rcreate_timing_summary -recovery rcreate_timing_summary -removal rreport_ucp r#delete our post-map timing netlistdelete_timing_netlist r#close the TimeQuest projectproject_close rExample3–6 and Example3–7 show the contents of the golden.sdc and io_cons.sdcfiles, respectively.Example3–6.The golden.sdc File#create the 50 MHz 50/50 clockcreate_clock –period 20 [get_ports clk]r#create the 100 MHz 60/40 clockcreate_clock –period 10 –waveform {0 6} [get_ports clkx2]r#cut the clk and clkx2 domainsset_clock_groups -group [get_clocks clk] -group [get_clocks clkx2]rExample3–7.The io_cons.sdc File#set the input delays for the designset_input_delay -clock clk 1.0 [get_ports {d[*] reset newt}]r#set the output delays for the designset_output_delay -clock clk 1.5 [get_ports {yn_out[0] yn_out[1] \yn_out[2] yn_out[3] yn_out[4] yn_out[5] yn_out[6] yn_out[7] yvalid follow}]r© December 2009 Altera Corporation TimeQuest Timing Analyzer Quick Start TutorialCommands and Tcl Scripts TimeQuest Timing Analyzer Quick Start Tutorial© December 2009 Altera Corporation© December 2009 Altera CorporationTimeQuest Timing Analyzer Quick Start TutorialAdditional InformationRevision HistoryThe following table shows the revision history for this user guide.How to Contact AlteraFor the most up-to-date information about Altera ® products, see the following table.Typographic ConventionsThe following table shows the typographic conventions that this document uses.Note:(1)You can also contact your local Altera sales office or sales representative.1–2Typographic ConventionsTimeQuest Timing Analyzer Quick Start Tutorial© December 2009 Altera Corporation。

Timequest timing analyzer使用方法

步骤1:执行初始编译

在应用时序约束设计之前,创建一个初始数据库:post-map。

表 1-1. 执行初始编译(1)

3.也可为初始数据库创建一个post-fit网表。

不过,创建一个post-map网表耗时较少。

图1 Analysis & Synthesis

当您直接从Quartus II软件中运行TimeQuest Timing Analyzer时,当前工程将会自动打开。

如果使用GUI,那么当出现下面的消息时,请选择No:

"No SDC files were found in the Quartus Settings File and filtref.sdc doesn't exist. Would you like to generate an SDC file from the Quartus Settings File?"

图2TimeQuest Timing Analyzer

步骤3:创建一个Post-map时序网表

在指定时序要求之前,请创建一个时序网表。

表3-1. 创建一个Post-Map时序网表

注意:不要在Tasks面板中使用Create Timing Netlist命令来创建一个post-map时序网表。

默认情况下,Create Timing Netlist创建一个post-fit数据库。

图3 Create Timing Netlist

图4 Input netlist

图5waiting

图7Create clock

图8设置参数

图9指定时钟

图10 Create clock设置完毕

图11Drive PLL clocks

图12Update Timing Netlist

步骤6:保存到SDC文件

在为设计指定时钟约束并更新时序网表后,您可以通过表6-1中的程序来选择创建SDC 文件。

通过TimeQuest Timing Analyzer GUI或者在控制台(console)中指定的约束不会自动保存。

因此,Altera建议单独保存利用文本编辑器可以手动编辑的一个golden SDC 文件。

这使您能够根据自身的规范输入注释并组织文件。

如下图:

而不是从TimeQuest GUI的Constraints下拉菜单输入约束:

图14时钟报告

图15时钟传输报告(Clock Transfers Report)

完成编译后,TimeQuest Timing Analyzer在Compilation Report中生成时钟建立和时钟保持的检查总结报告。

步骤10:在TimeQuest中验证时序

要获得指定路径中详细的时序分析数据,请查看TimeQuest Timing Analyzer中的时序分析结果。

完全执行布线布局功能(place-and-route)后,运行"步骤2:运行TimeQuest Timing Analyzer"中所介绍的TimeQuest Timing Analyzer,生成一个post-fit时序网表,通过表10-1中的程序,读取SDC文件并更新时序网表来生成关于最新编译的报告。

#1. Summary报告:

表 10-1. 生成关于Latest Compilation的报告

Summary (Setup)报告

clkx2时钟没有出现在Summary (Setup)报告中,这是因为clk和clkx2之间所有的时钟路径已经声明是伪路径。

此外,fir_filter设计不包含任何寄存器到寄存器的路径,其中目的寄存器路径由clkx2来驱动。

Summary (Setup)报告中的Slack列表明clk能满足约束,并有11.588 ns的余量。

End Point TNS列是指定时钟域中所有的总负裕量(TNS)的总和。

使用这个值来测量指定时钟域中失败路径的总数。

#3. Clock Hold报告:

生成Summary (Setup)报告后,通过表 2-21中的程序,生成一个时钟保持检查总结。

表 10-3. 生成Summary (Hold) Report

图16Summary (Hold)报告

Summary (Hold)报告表明clk时钟节点符合时序约束,并有0.661 ns的余量。

#4. Unconstrained Paths报告:

在执行全编译之前,通过表10-4中的程序指定所有的时序约束和例外。

这样可以确保Fitter 优化设计中的关键路径。

您可以使用Report Unconstrained Paths命令来验证已经约束

fir_filter设计中的所有路径。

表 10-4. 指定时序约束和例外

图17Unconstrained Paths总结报告

#5. Set_input_delay / set_output_delay设置:

Unconstrained Paths总结报告表明有大量的未约束路径,并详细介绍了这些路径的类型。

要充分约束此设计,利用由TimeQuest Timing Analyzer所提供的整套SDC约束。

要充分约束fir_filter设计,约束所有的输入和输出端口。

使用Set Input Delay和Set Output Delay 对话框,或set_input_delay和set_output_delay约束来指定输入和输出延迟值。

由于附加约束应用于设计,通过文本编辑器(例如:inout_delay.sdc)创建仅包含输入和输出约束的额外SDC。

添加表10-5所示的输入和输出延迟分配到"步骤8:保存约束到SDC文件"创建的新SDC中。

表10-5. 输入和输出延迟分配

使用Tasks面板中的Report Top Failing Paths命令来生成一个报告,该报告详细介绍了设计中的最差的失败路径。

也可以通过菜单设置。