3.3《十天学会LM4F232,玩转CORTEX M4 》中断使用

- 格式:pdf

- 大小:188.76 KB

- 文档页数:4

Cortex-M4的中断与异常处理11.4.3异常模式11.4.3.1异常状态不活跃.这种异常是不活跃,不等待。

等待.例外的是等待由处理器处理。

来⾃外设或软件的中断请求可以将相应的中断状态更改为挂起。

活跃。

这种异常是被服务处理器,但还没有完成。

异常处理程序可以中断另⼀个异常处理程序的执⾏。

在这种情况下,两个异常都处于活动状态。

活跃和等待。

该异常服务由处理器和存在来⾃相同源的现⾏异常。

11.4.3.2异常类型重置异常。

重置是⼀种复位调⽤上电或热复位。

这种异常模式将复位作为⼀种特殊形式。

当发⽣复位时,处理器运⾏停⽌,有可能在⼀个指令的任何点。

当复位置为⽆效,重新开始执⾏从向量表中复位⼊⼝的地址。

执⾏是特权执⾏的线程模式。

NMI异常。

⾮屏蔽中断(NMI)可以通过⼀个外设或由软件触发发出信号。

这是最⾼优先级的异常,⽐其他复位都⾼。

它是永久启⽤并拥有-2⼀个固定的优先级。

NMI不能被掩蔽或通过任何其它异常阻⽌激活,也不能被通过⽐复位之外的任何异常抢占。

硬故障的发⽣是由于异常处理期间有错误的异常,或者因为异常不能被任何异常机制管理。

硬故障拥有-1固定的优先级,这意味着他们有更⾼的优先级⽐配置优先级的任何异常。

内存管理故障。

内存管理故障的发⽣是由于内存保护相关的故障异常引起的。

该MPU或固定存储器保护限制决定了该故障指令和数据存储器事务。

该故障⽤来取消指令对不执⾏(XN)存储区域的操作,即使MPU被禁⽤。

总线故障。

总线故障的发⽣是因为⼀个指令或数据存储器事务的存储器相关的故障异常。

这可能是由⼀个总线上的存储器系统中检测到错误。

应⽤故障。

应⽤故障是因为涉及到指令执⾏的故障发⽣了异常,包括:未定义指令;⼀个⾮法的未对齐访问;⽆效状态的指令执⾏;异常返回⼀个错误。

SVCall异常。

系统调⽤(SVC)是由SVC指令触发了异常。

在OS环境,应⽤程序可以使⽤SVC指令来访问OS内核函数和器件驱动。

PendSV异常。

PendSV的是系统级的服务中断驱动的请求。

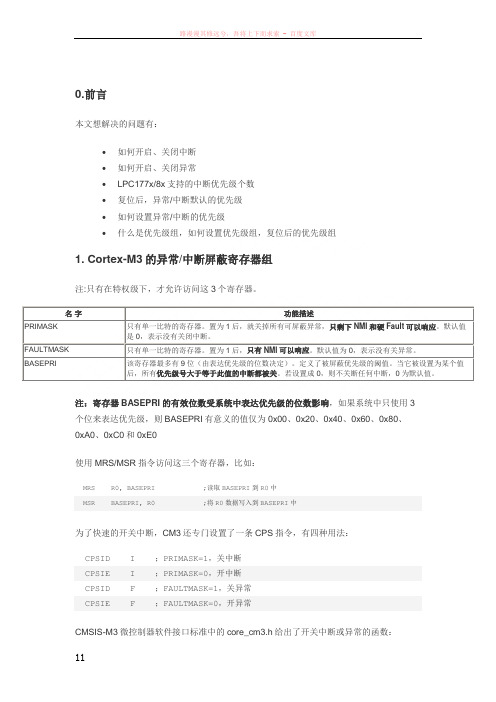

0.前言本文想解决的问题有:•如何开启、关闭中断•如何开启、关闭异常•LPC177x/8x支持的中断优先级个数•复位后,异常/中断默认的优先级•如何设置异常/中断的优先级•什么是优先级组,如何设置优先级组,复位后的优先级组1. Cortex-M3的异常/中断屏蔽寄存器组注:只有在特权级下,才允许访问这3个寄存器。

名字功能描述PRIMASK 只有单一比特的寄存器。

置为1后,就关掉所有可屏蔽异常,只剩下NMI和硬Fault可以响应。

默认值是0,表示没有关闭中断。

FAULTMASK 只有单一比特的寄存器。

置为1后,只有NMI可以响应。

默认值为0,表示没有关异常。

BASEPRI 该寄存器最多有9位(由表达优先级的位数决定)。

定义了被屏蔽优先级的阈值。

当它被设置为某个值后,所有优先级号大于等于此值的中断都被关。

若设置成0,则不关断任何中断,0为默认值。

注:寄存器BASEPRI的有效位数受系统中表达优先级的位数影响,如果系统中只使用3个位来表达优先级,则BASEPRI有意义的值仅为0x00、0x20、0x40、0x60、0x80、0xA0、0xC0和0xE0使用MRS/MSR指令访问这三个寄存器,比如:MRS R0, BASEPRI ;读取BASEPRI到R0中MSR BASEPRI, R0 ;将R0数据写入到BASEPRI中为了快速的开关中断,CM3还专门设置了一条CPS指令,有四种用法:CPSID I ;PRIMASK=1,关中断CPSIE I ;PRIMASK=0,开中断CPSID F ;FAULTMASK=1,关异常CPSIE F ;FAULTMASK=0,开异常CMSIS-M3微控制器软件接口标准中的core_cm3.h给出了开关中断或异常的函数:1.1 开/关中断1:/**2: * @brief Set the Priority Mask value3: *4: * @param priMask PriMask5: *6: * Set the priority mask bit in the priority mask register7: */8:static __INLINE void __set_PRIMASK(uint32_t priMask)9: {10:register uint32_t __regPriMask __ASM("primask");11: __regPriMask = (priMask);12: }使用__set_PRIMASK(1)关闭中断;__setPRIMASK(0)开启中断。

cortex中断函数定义Cortex中断函数定义Cortex中断函数是在ARM Cortex-M系列微控制器中用于处理中断事件的函数。

中断是一种事件驱动的机制,当特定的事件发生时,系统会立即跳转到相应的中断服务函数进行处理。

在Cortex-M系列微控制器中,中断函数的定义有一定的规范和要求,以确保中断处理的正确性和可靠性。

中断函数的定义需要遵循一定的格式。

在Cortex-M系列微控制器中,通常会使用汇编语言编写中断服务函数。

汇编语言是一种低级别的语言,可以直接操作硬件,提供了更高的灵活性和效率。

因此,中断函数的定义通常会以汇编语言的形式呈现。

在定义中断函数时,需要注意保存和恢复CPU寄存器的状态。

由于中断处理过程中,系统会跳转到中断服务函数执行,因此需要保存当前CPU的寄存器状态,以便在中断处理完毕后能正确恢复。

在Cortex-M系列微控制器中,一般会使用堆栈来保存和恢复寄存器状态。

中断函数的定义还需要根据具体的中断事件进行相应的处理。

不同的中断事件可能需要不同的处理方式和操作。

例如,外部中断事件可能需要读取外部输入信号的状态;定时器中断事件可能需要更新定时器的计数值;串口中断事件可能需要读取或发送数据等。

因此,在定义中断函数时,需要根据具体的中断事件进行相应的操作。

中断函数的定义还需要考虑中断优先级和嵌套中断的情况。

Cortex-M系列微控制器支持多级中断优先级,不同的中断事件可以设置不同的优先级,以确保高优先级的中断能够优先处理。

同时,中断函数的定义还需要考虑可能发生的嵌套中断情况,即在一个中断处理过程中,可能会发生其他中断事件。

在这种情况下,需要正确处理嵌套中断的优先级和顺序。

中断函数的定义还需要考虑中断处理的结束条件和返回方式。

在中断处理完毕后,需要恢复中断处理前的状态,并返回到中断发生前的执行点。

在Cortex-M系列微控制器中,通常会使用特定的汇编指令来实现中断的结束和返回。

总结起来,Cortex中断函数的定义需要遵循一定的格式和规范,包括保存和恢复CPU寄存器的状态、根据具体中断事件进行相应的操作、考虑中断优先级和嵌套中断的情况,以及正确处理中断的结束和返回。

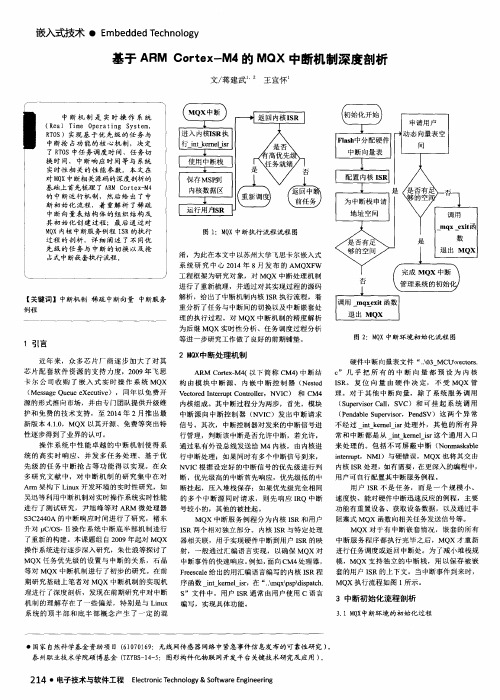

Cortex-M4内核知识点总结余明目录Cortex-M4内核知识点总结 (1)1 ARM处理器简介 (5)2 架构 (6)2.1架构简介 (6)2.2编程模型 (6)2.3存储器系统 (9)2.4复位和复位流程 (13)3 指令集 (15)3.1 CM4指令集特点 (15)3.2 Cortex-M处理器间的指令集比较 (15)3.3 汇编指令简要介绍 (15)3.3.1 处理器内传送数据 (15)3.3.2 存储器访问指令 (16)3.3.3 算数运算 (17)3.3.4 逻辑运算 (18)3.3.5 移位 (18)3.3.6 异常相关指令 (18)4 存储器系统 (19)4.1 存储器外设 (19)4.2 Bootloader (19)4.3位段操作 (20)4.4 存储器大小端 (20)5 异常和中断 (22)5.1 中断简介 (22)5.2异常类型 (22)5.3 中断管理 (23)5.4 异常或中断屏蔽寄存器 (24)5.4.1 PRIMASK (24)5.4.2 FAULMASK (M0中无) (24)5.4.3 BASEPRI(M0中无) (24)5.5 中断状态及中断行为 (24)5.5.1 中断状态 (24)5.5.2 中断行为 (25)5.6 各Cortex-M处理器NVIC差异 (27)6 异常处理 (29)6.1 C实现的异常处理 (29)6.2 栈帧 (29)6.3 EXC_RETURN (30)6.4异常流程 (31)6.4.1 异常进入和压栈 (31)6.4.2 异常返回和出栈 (32)7 低功耗和系统控制特性 (33)7.1 低功耗模式 (33)7.1 SysTick定时器 (33)8 OS支持特性 (35)8.1 OS支持特性简介 (35)8.2 SVC和PendSV (35)8.3 实际的上下文切换 (36)1 ARM处理器简介ARM处理器的种类很多,从手机上的高端处理器芯片到面向微控制器的芯片,都有ARM的身影。

STM32F4事件和中断使用步骤事件的产生过程和中断的产生过程一样可由EXTI_InitStructure.EXTI_Mode来配置为中断模式或事件模式1中断模式是通过一系列过程产生,然后等待处理器来干某件事情2事件模式是通过一系列过程产生,产生的是一个事件(比如一个方波或唤醒闹钟)外部中断:步骤1 嵌套向量中断控制器 NVIC 配置1)定义中断/事件初始化类型结构体(已定义在misc文件里)NVIC_InitTypeDef NVIC_InitStructure;2)定义在那个中断线NVIC_InitStructure.NVIC_IRQChannel=3)指定中断抢占优先级NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority=4)指定中断响应子优先级NVIC_InitStructure.NVIC_IRQChannelSubPriority=5)使能中断通道NVIC_InitStructure.NVIC_IRQChannelCmd=6)调用中断初始化函数NVIC_Init(&NVIC_InitStructure);步骤2 EXTI外部中断/事件控制配置1)定义外部中断/事件初始化结构体EXTI_InitTypeDef EXTI_InitStructure;已定义在xxx_exti文件2)外部中断对应GPIO引脚初始化配置3)启用SYSCFG所在总线的时钟RCC_APB2PeriphClockCmd();已定义在xxx_rcc文件里4)调用步骤1配置NVIC5)连接GPIO引脚到外部中断线SYSCFG_EXTILineConfig(EXTI_PortSourceGPIOx,EXTI_PinSou rcex);已定义在xxx_syscfg文件6)初始化外部中断/事件结构体的成员EXTI_InitStructure.EXTI_Line=EXTI_Linex;//中断线xEXTI_InitStructure.EXTI_Mode=; //中断模式或事件模式xxx_exti文件里EXTIMode_TypeDef结构体EXTI_InitStructure.EXTI_Trigger=; //触发方式上升,下降,边沿在EXTITrigger_TypeDef结构体EXTI_InitStructure.EXTI_LineCmd=ENABLE;//中断线的状态启用或禁用(DISABLE)EXTI_Init(&EXTI_InitStructure);//依据上面的参数初始化已在xxx_exti文件里定义。

在咱们嵌入式工程应用中,中断作为最经常使用的异步手腕是必不可少的,而且在一个应用程序中,一个中断往往是不够用的,多个中断混合利用乃最多级中断嵌套也常常会利用到,而如此就涉及到一个中断优先级的问题。

以咱们最熟悉的Cortex-M系列为例,咱们明白ARM从Cortex-M系列开始引入了NVIC 的概念(Nested Vectors Interrupts Controller),即嵌套向量中断操纵器,以它为核心通过一张中断向量表来操纵系统中断功能,NVIC能够提供以下几个功能:1)可嵌套中断支持;2)向量中断支持;3)动态优先级调整支持;4)中断可屏蔽。

抛开其他不谈,那个地址咱们只说说中断优先级的问题。

咱们明白NVIC的核心工作原理即是对一张中断向量表的保护上,其中M4最多支持240+16个中断向量,M0+那么最多支持32+16个中断向量,而这些中断向量默许的优先级那么是向量号越小的优先级越高,即从小到大,优先级是递减的。

可是咱们确信可不能知足于默许的状态(人往往不知足于约束,换句俗语说确实是不喜爱按套路出牌,呵呵),而NVIC那么恰恰提供了这种灵活性,即支持动态优先级调整,不管是M0+仍是M4除3个中断向量之外(复位、NMI和HardFault,他们的中断优先级为负数,它们3个的优先级是最高的且不可更改),其他中断向量都是能够动态调整的。

只是需要注意的是,中断向量表的前16个为内核级中断,以后的为外部中断,而内核级中断和外部中断的优先级那么是由两套不同的寄放器组来操纵的,其中内核级中断由SCB_SHPRx 寄放器来操纵(M0+为SCB_SHPR[2:3],M4为SCB_SHPR[1:3]),外部中断那么由NVIC_IPRx来操纵(M0+为NVIC_IPR[0:7],M4为NVIC_IPR[0:59]),如以下图所示:M0+中断优先级寄放器:M4中断优先级寄放器:其中M4所支持的动态优先级范围为0~15(8位中只有高四位[7:4]才有效),而M0+所支持的动态优先级范围那么为0~3(8位中只有高两位[7:6]才有效),而且秉承着号越小优先级越高的原那么(0最高,15或3为最小),同时也间接说明了什么缘故复位(-3)、NMI(-2)和HardFault(-1)优先级最高的缘故,很简单,人家都是负的了,谁还能比他们高,呵呵,而且这三位中复位优先级最高,NMI第二,HardFault最低(那个最低仅限于这三者)。

ARM Cortex—M处理器家族是一组为嵌入式系统制造的32位处理器。

这些处理器被用在很多诸如IOT设备,设备,汽车等等的东西中。

Cortex—M处理器的一个酷点是它们能处理中断,这意味着它们能对事件迅速作出反应。

在文章中,我们将讨论Cortex—M处理器如何

处理中断,我们将专注于所涉及的步骤和概念。

当一个Cortex—M处理器中断时,就像在电子游戏上按下暂停按钮。

处理器很快地将它所做的一切保存在堆栈上,类似于在游戏中保存你

的进度。

它记得它在哪里,它在做什么,和所有重要的环境。

是时候找出真正造成中断的原因了。

处理器检查其特殊的内存图称为

中断矢量表,这就像一个导致不同中断服务常规(ISR)的藏宝图。

这就像在游戏中寻找正确的路径来解决特定的挑战。

一旦处理器知道哪一个ISR去,就像跳进游戏的新关卡。

它开始执行

中断处理器代码,这就像用一套新的指令处理一个新的任务。

就像在

游戏中,处理器可以永远回到它留下的地方,继续冒险!

在ARM Cortex—M的微妙舞蹈中,中断处理是一种优雅的芭蕾舞,

它拯救了现在的时刻,从迷人的矢量台上寻找ISR的悄悄位置区域,

并跳入ISR的等待怀里,执行中断处理者的卡住密码。

这种受试过程

使处理器能够以优雅和高效的空气来响应外部事件的呼唤,将Cortex—M处理器铸成实时嵌入系统的发光星。