DSP第二章C54x结构与工作原理——总线结构和存储器结构

- 格式:ppt

- 大小:501.50 KB

- 文档页数:31

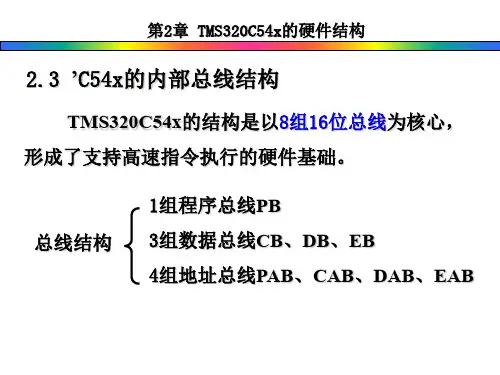

T M S320C54x D S P(精)TMS320C54x DSP CPU与外设第一章综述1 总线结构C54x包括8条16比特宽度的总线,其中:●一条程序总线(PB)●三条数据总线(CB、DB、EB)●四条地址总线(PAB、CAB、DAB、EAB)2CPUC54x的CPU结构包括:●40比特的ALU,其输入来自16比特立即数、16比特来自数据存储器的数据、暂时存储器、T中的16比特数、数据存储器中两个16比特字、数据存储器中32比特字、累加器中40比特字。

●2个40比特的累加器,分为三个部分,保护位(39-32比特)、高位字(31-16比特)、低位字(15-0比特)。

●桶型移位器,可产生0到31比特的左移或0到16比特的右移。

●17×17比特的乘法器●40比特的加法器●比较选择和存储单元CSSU●数据地址产生器DAGEN●程序地址产生器PAGEN3外设C54x包括:●通用I/O引脚,XF和BIO●定时器●PLL时钟产生器●HPI口,8比特或16比特●同步串口●带缓存串口,BSP●多路带缓存串口,McBSP●时分复用串口,TDM●可编程等待状态产生器●可编程bank-switching模块●外部总线接口●IEEE1149.1标准JTAG口第二章存储器一般而言,C54x的存储空间可达192K16比特字,64K程序空间,64K数据空间,64KI/O空间。

依赖其并行的工艺特性和片上RAM双向访问的性能,在一个机器周期内,C54x可以执行4条并行并行存储器操作:取指令,两操作数读,一操作数写。

使用片内存储器有三个优点:高速执行(不需要等待),低开销,低功耗。

1 存储空间分配图(以C549为例)复位后,中断矢量表位于程序区FF80H 位置,可重新定位于程序空间任何一个128字的页面(其地址高9比特即页号由PMST 中IPTR 确定)。

2 程序存储区C54x 有片内ROM 、DARAM 、SARAM ,这些区域可以通过软件配置到程序空间。

《DSP技术与应用》学时:32(含8学时实验)第2章TMS320C54XDSP硬件结构本 章 内 容1、TMS32054XDSP结构特点2、TMS32054XDSP结构框图3、TMS32054XDSP总线结构4、TMS32054XDSP存储器结构5、TMS32054XDSP处理器结构6、TMS32054XDSP片上外设7、TMS32054XDSP芯片引脚8、TMS32054XDSP复位操作结构特点TMS32054XDSP结构特点• 10-25ns的指令周期(40-100MIPS)----高效快速• 192K×16位的(最小)可寻址存储空间----哈佛结构• 4组内部总线及双地址生成单元----多总线结构• 2—6级的并行流水线操作----流水线结构• 两个40位累加器ACCA、ACCB• 40位算术逻辑单元(ALU),包括一个40位的桶型移位寄存器• 17×17位硬件乘法器,允许16位带符号或不带符号的乘法• 8个辅助寄存器及一个堆栈• 1.8V,2.5V,3.3V低功耗节电模式,宜于电池供电应用• 丰富的片内外设,包括串、并接口,软件可编程定时器、等待状态发生器及可配置PLL的时钟发生器所有’C54x片内部都含有数据存储器和程序存储器,但不同型号芯片的RAM和ROM容量及驻留区域是不相同的64K程序存储空间64K程序存储空间64K数据存储空间两个控制位可通过PMST寄存器软件设置,其状态对VC5402DSP程序存储空间配置的影响见下表MP/MC OVLY程序存储空间配置1064K的程序存储空间全部定义为外部程序存储器,需片外寻址11007FH—3FFFH(约16K字)DARAM可定义为片内程序存储器;4000H—FFFFH(48K字)定义为外部程序存储器,需片外寻址000000H—EFFFH(60K字)定义为外部程序存储器,需片外寻址;F000H—FFFFH(4K字)定义为片内程序存储器(2K字保留)01007FH—3FFFH(约16K字)DARAM可定义为片内程序存储器;4000H—EFFFH(44K字)定义为外部程序存储器,需片外寻址;F000H—FFFFH(4K字)定义为片内存储器(2K保留)VC5402DSP片内含有16k字的DARAM,驻留在数据存储空间的0000H—3FFFH区间内,可片内寻址。