半导体封装工艺介绍共44页

- 格式:ppt

- 大小:3.63 MB

- 文档页数:44

半导体封装主要工艺流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!半导体封装主要工艺流程一、准备工作阶段。

在进行半导体封装之前,需要进行充分的准备。

半导体制造工艺Zhang.2008.6.4 Tel: 622131 / 49半导体发展史1. 60年前,第一只晶体管在贝尔实验室诞生,从此人类步入了飞速发展的电子时代。

2. 50年前,第一块集成电路在TI公司诞生,从此我们进入了微电子时代。

3. 40年前,仙童公司出走的“8叛逆”中的诺依斯、摩尔和葛罗夫创立了Intel公司,来自仙童公司的另一位员工C.Sporck 则创立了AMD。

他们的创业引发了自硅谷席卷全球的高科技创业热潮!4. 30年前(1978年2月16日),芝加哥的Ward Christiansen和Randy Seuss开发出第一个计算机的公告牌系统,成为普及Internet的启明星,人类从此进入互联网时代。

5. 现在,3G、移动视频、GPS、高清电视、RFID… 数不清的高科技梦想要实现,所依靠的都是半导体技术的发展!“世界上没有哪一个工业,像半导体产业一样充满创新和变革。

”2 / 49半导体制造过程分类− 前段(Front End)制程晶圆处理制程(Wafer Fabrication;简称 Wafer Fab)、晶圆针测制程(Wafer Probe);− 后段(Back End)封装(Packaging)、测试制程(Final Test)3 / 49晶圆制造过程−晶棒成长−晶棒裁切与检测−外径研磨−切片−圆边−表层研磨−蚀刻−抛光−清洗−检验−包装4 / 495 / 49封装测试过程6 / 49半导体器件封装概述1. 半导体组装技术(Assembly technology)的提高主要体现在它的封装型式(Package)不断发展。

2. 通常所指的组装(Assembly)可定义为:利用膜技术及微细连接技术将半导体芯片(Chip)和框架(Leadframe)或基板(Sulbstrate)或塑料薄片(Film)或印刷线路板中的导体部分连接以便引出接线引脚,并通过可塑性绝缘介质灌封固定,构成整体立体结构的工艺技术。

半导体光电器件封装工艺解释说明以及概述1. 引言1.1 概述半导体光电器件封装工艺是将半导体光电器件通过封装技术进行保护和连接,从而实现其正常工作和应用的过程。

在现代科技领域中,半导体光电器件广泛应用于通信、信息技术、医疗设备等各个领域,其封装工艺的质量和稳定性对整个系统性能的影响至关重要。

1.2 文章结构本文将分为五个主要部分进行论述。

引言部分旨在概述半导体光电器件封装工艺,介绍文章的结构以及明确文章的目的。

第二部分将解释什么是半导体光电器件封装工艺,并探讨其重要性及作用以及封装工艺的发展历程。

第三部分将详细说明半导体光电器件封装工艺的主要步骤和流程,并给出各个步骤的具体操作与技术要点,还包括常见的封装工艺问题及相应解决方法。

第四部分将对半导体光电器件封装市场现状和趋势进行概述,并比较与评价国内外相关技术,同时展望未来的发展方向和挑战。

最后一部分是结论部分,总结文章主要观点和论证结果,给出对半导体光电器件封装工艺发展的建议,并提供读者启示和展望。

1.3 目的本文旨在全面介绍半导体光电器件封装工艺,解释其定义与重要性,并说明该工艺的步骤、操作技巧以及常见问题解决方法。

同时,通过概述市场现状和趋势以及对比国内外技术,探讨未来发展方向和面临的挑战。

通过本文的阐述,读者将对半导体光电器件封装工艺有更深入全面的了解,并能够为其在实际应用中提供指导和展望。

2. 半导体光电器件封装工艺解释:2.1 什么是半导体光电器件封装工艺:半导体光电器件封装工艺是将制造好的半导体光电器件在保护壳体中进行封装和组装的过程。

通过封装,可以保护器件不受外界环境的干扰,并提供连接外部电路所需的引脚接口,以便实现器件与其他元器件之间的联接。

2.2 封装工艺的重要性及作用:封装工艺在半导体光电器件制造过程中起着重要的作用。

首先,封装能够提供对光学元素、半导体芯片等关键部分的保护,降低因环境变化引起的温度、气候、振动等因素带来的不利影响。

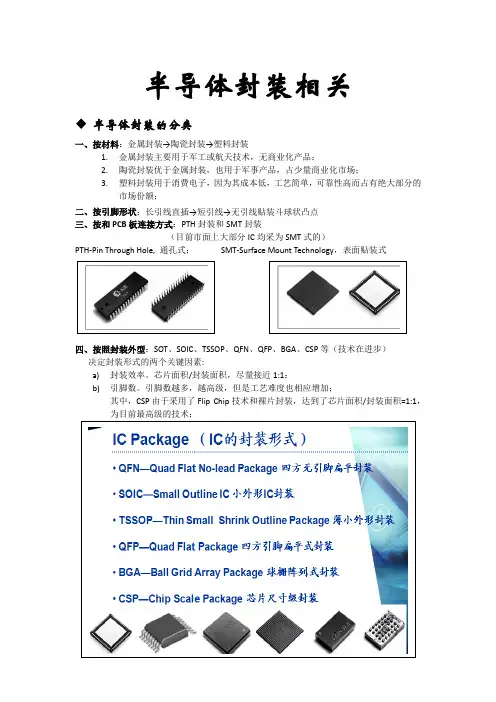

半导体封装相关 半导体封装的分类一、按材料:金属封装→陶瓷封装→塑料封装1. 金属封装主要用于军工或航天技术,无商业化产品;2. 陶瓷封装优于金属封装,也用于军事产品,占少量商业化市场;3. 塑料封装用于消费电子,因为其成本低,工艺简单,可靠性高而占有绝大部分的市场份额;二、按引脚形状:长引线直插→短引线→无引线贴装斗球状凸点三、按和PCB 板连接方式:PTH 封装和SMT 封装(目前市面上大部分IC 均采为SMT 式的)PTH-Pin Through Hole, 通孔式; SMT-Surface Mount Technology ,表面贴装式四、按照封装外型:SOT 、SOIC 、TSSOP 、QFN 、QFP 、BGA 、CSP 等(技术在进步) 决定封装形式的两个关键因素:a) 封装效率。

芯片面积/封装面积,尽量接近1:1; b) 引脚数。

引脚数越多,越高级,但是工艺难度也相应增加;其中,CSP 由于采用了Flip Chip 技术和裸片封装,达到了芯片面积/封装面积=1:1,为目前最高级的技术;◆半导体封装技术的发展历程50年代的TO型圆形金属封装70年代,芯片封装流行的是双列直插封装(DIP)、单列直插封装(SIP)、针栅阵列封装(PGA)等都属于通孔插装式安装器件80年代,表面贴装技术(SMT)的封装形式兴起,主要有小外型封装(SOP),引线间距为1.27mm、塑料片式载体(PLCC),引线间距为1.27mm、四边引线扁平封装(QFP)等。

最终四边引线扁平封装(QFP)成为主流的封装形式(0.3mm已是QFP引脚间距的极限)其后相继出现了各种改进型,如TQFP(薄型QFP)、VQFP(细引脚间距QFP)、SQFP(缩小型QFP)、PQFP(塑封QFP)、Tape QFP(载带QFP)和$OJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小形SOP)、TSSOP(薄的缩小型SOP)等90年代,以面阵排列、球形凸点为引脚、封装密度大为提高的BGA(焊球阵列封装)便应运而生。

半导体封装的工艺流程半导体封装,这可是个相当精妙的过程,就好像是给一颗珍贵的宝石打造一个完美的外壳,让它能够璀璨夺目。

你知道吗?半导体封装的第一步是芯片切割。

想象一下,那一个个小小的芯片就像是待采摘的成熟果实,得小心翼翼地从晶圆上切下来。

这可不是随便一刀切就行的,得精准,稍有偏差,就可能前功尽弃。

这就像雕刻大师在雕琢一件绝世珍品,每一刀都得恰到好处。

接着是芯片贴装。

芯片就如同一个娇贵的小宝宝,得轻柔地把它放在合适的位置,还得保证它稳稳当当,舒舒服服。

要是贴得不好,那后面的工作可就全乱套啦。

然后是引线键合,这就好比是给芯片牵线搭桥,让它能够和外界沟通交流。

那细细的引线,就像是月老手中的红线,把芯片和外部世界紧紧相连。

再来就是塑封,这一步就像是给芯片穿上一件厚厚的棉袄,保护它不受外界的风吹雨打。

而且这棉袄还得合身,不能太紧也不能太松。

封装完成后,还得进行各种测试。

这就好像是给芯片进行一场严格的考试,只有成绩优异的才能过关。

要是通不过,那可就得回炉重造啦。

在整个半导体封装的工艺流程中,每一个环节都至关重要。

哪怕是一点点的小疏忽,都可能导致整个产品的失败。

这就像盖房子,地基没打好,房子能牢固吗?每一个步骤都需要高度的专注和精湛的技术,就如同一位大厨在烹饪一道顶级美食,火候、调料、时间,样样都得精准把握。

你说,要是封装过程中出了岔子,那之前所有的努力不都白费了?所以啊,半导体封装可不是闹着玩的,得严谨、得精细、得用心。

这就是半导体封装的工艺流程,复杂却又充满魅力,不是吗?。

三⼤半导体BGA封装⼯艺及流程⼀、引线键合半导体PBGA的封装⼯艺流程1、PBGA基板的制备在BT树脂/玻璃芯板的两⾯层压极薄(12~18µm厚)的铜箔,然后进⾏钻孔和通孔⾦属化。

⽤常规的PCB加3232艺在基板的两⾯制作出图形,如导带、电极、及安装焊料球的焊区阵列。

然后加上焊料掩膜并制作出图形,露出电极和焊区。

为提⾼⽣产效率,⼀条基⽚上通常含有多个PBG基板。

2、封装⼯艺流程圆⽚减薄→圆⽚切削→芯⽚粘结→等离⼦清洗→引线键合→等离⼦清洗→模塑封装→装配焊料球→回流焊→表⾯打标→分离→最终检查→测试⽃包装。

⼆、FC-CBGA的封装⼯艺流程1、陶瓷基板FC-CBGA的基板是多层陶瓷基板,它的制作是相当困难的。

因为基板的布线密度⾼、间距窄、通孔也多,以及基板的共⾯性要求较⾼等。

它的主要过程是:先将多层陶瓷⽚⾼温共烧成多层陶瓷⾦属化基⽚,再在基⽚上制作多层⾦属布线,然后进⾏电镀等。

在CBGA的组装中,基板与芯⽚、PCB板的CTE失配是造成CBGA产品失效的主要因素。

要改善这⼀情况,除采⽤CCGA 结构外,还可使⽤另外⼀种陶瓷基板--HITCE陶瓷基板。

展开剩余44%2、封装⼯艺流程圆⽚凸点的制备->圆⽚切割->芯⽚倒装及回流焊->底部填充导热脂、密封焊料的分配->封盖->装配焊料球->回流焊->打标->分离->最终检查->测试->包装。

三、引线键合TBGA的封装⼯艺流程1、TBGA载带TBGA的载带通常是由聚酰亚胺材料制成的。

在制作时,先在载带的两⾯进⾏覆铜,然后镀镍和镀⾦,接着冲通孔和通孔⾦属化及制作出图形。

因为在这种引线键合TBGA中,封装热沉⼜是封装的加固体,也是管壳的芯腔基底,因此在封装前先要使⽤压敏粘结剂将载带粘结在热沉上。

2、封装⼯艺流程圆⽚减薄→圆⽚切割→芯⽚粘结→清洗→引线键合→等离⼦清洗→液态密封剂灌封→装配焊料球→回流焊→表⾯打标→分离→最终检查→测试→包装。

半导体封装技术大全1、BGA(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚BGA仅为31mm 见方;而引脚中心距为0.5mm 的30 4 引脚QFP 为40mm 见方。

而且BGA不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Motorola 公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。

2、BQFP(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和ASIC 等电路中采用此封装。

引脚中心距0.635mm,引脚数从84 到196 左右(见QFP)。

3、碰焊PGA(butt joint pin grid array) 表面贴装型PGA 的别称(见表面贴装型PGA)。

4、C-(ceramic)表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

5、Cerdip用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。