电源EMI滤波器的PCB设计

- 格式:doc

- 大小:968.00 KB

- 文档页数:4

第二篇抗干扰3(部分)3 提高敏感器件的抗干扰性能提高敏感器件的抗干扰性能是指从敏感器件这边考虑尽量减少对干扰噪声的拾取,以及从不正常状态尽快恢复的方法。

提高敏感器件抗干扰性能的常用措施如下:(1)布线时尽量减少回路环的面积,以降低感应噪声。

(2)布线时,电源线和地线要尽量粗。

除减小压降外,更重要的是降低耦合噪声。

(3)对于单片机闲置的I/O口,不要悬空,要接地或接电源。

其它IC的闲置端在不改变系统逻辑的情况下接地或接电源。

(4)对单片机使用电源监控及看门狗电路,如:IMP809,IMP706,IMP813,X25043,X25045等,可大幅度提高整个电路的抗干扰性能。

(5)在速度能满足要求的前提下,尽量降低单片机的晶振和选用低速数字电路。

(6)IC器件尽量直接焊在电路板上,少用IC座。

第三篇印制电路板的可靠性设计-去耦电容配置在直流电源回路中,负载的变化会引起电源噪声。

例如在数字电路中,当电路从一个状态转换为另一种状态时,就会在电源线上产生一个很大的尖峰电流,形成瞬变的噪声电压。

配置去耦电容可以抑制因负载变化而产生的噪声,是印制电路板的可靠性设计的一种常规做法,配置原则如下:●电源输入端跨接一个10~100uF的电解电容器,如果印制电路板的位置允许,采用100uF以上的电解电容器的抗干扰效果会更好。

●为每个集成电路芯片配置一个0.01uF的陶瓷电容器。

如遇到印制电路板空间小而装不下时,可每4~10个芯片配置一个1~10uF钽电解电容器,这种器件的高频阻抗特别小,在500kHz~20MHz范围内阻抗小于1Ω,而且漏电流很小(0.5uA以下)。

●对于噪声能力弱、关断时电流变化大的器件和ROM、RAM等存储型器件,应在芯片的电源线(Vcc)和地线(GND)间直接接入去耦电容。

●去耦电容的引线不能过长,特别是高频旁路电容不能带引线。

第四篇电磁兼容性和PCB设计约束(缺具体数据)PCB布线对PCB的电磁兼容性影响很大,为了使PCB上的电路正常工作,应根据本文所述的约束条件来优化布线以及元器件/接头和某些IC所用去耦电路的布局(一)、PCB材料的选择通过合理选择PCB的材料和印刷线路的布线路径,可以做出对其它线路耦合低的传输线。

直流电源EMI滤波器的设计直流电源EMI滤波器的设计原则、网络结构、参数选择1 设计原则-满足最大阻抗失配插入损耗要尽可能增大,即尽可能增大信号的反射。

设电源的输出阻抗和与之端接的滤波器的输人阻抗分别为ZO和ZI,根据信号传输理论,当ZO≠ZI时,在滤波器的输入端口会发生反射,反射系数p=(ZO-ZI)/(ZO+ZI)显然,ZO与ZI相差越大,p便越大,端口产生的反射越大,EMI信号就越难通过。

所以,滤波器输入端口应与电源的输出端口处于失配状态,使EMI信号产生反射。

同理,滤波器输出端口应与负载处于失配状态,使EMI信号产生反射。

即滤波器的设什应遵循下列原则:源内阻是高阻的,则滤波器输人阻抗就应该是低阻的,反之亦然。

负载是高阻的,则滤波器输出阻抗就应该是低阻的,反之亦然。

对于EMI信号,电感是高阻的,电容是低阻的,所以,电源EMI滤波器与源或负载的端接应遵循下列原则:如果源内阻或负载是阻性或感性的,与之端接的滤波器接口就应该是容性的。

如果源内阻或负载是容性的,与之端接的滤波器接口就应该是感性的。

2 EMI滤波器的网络结构EMI信号包括共模干扰信号CM 和差模干扰信号DM,CM 和DM 的分布如图1所示。

它可用来指导如何确定EMI滤波器的网络结构和参数。

EMI滤波器的基本网络结构如图2 所示。

上述4种网络结构是电源EMI滤波器的基本结构,但是在选用时,要注意以下的间题:双向滤波功能——电网对电源、电源对电网都应该有滤波功能。

能有效地抑制差模干扰和共模干扰——工程设计中重点考虑共模干扰的抑制。

最大程度地满足阻抗失配原则。

几种实际使用的电源EMI滤波器的网络结构如图3 所示。

3 电源EMI滤波器的参数确定方法a)放电电阻的取值在允许的情况下,电阻取值要求越小越好,需要考虑以下情况:第一,电阻要求采用二级降额使用,保证可靠性。

降额系数为0.75 V,0. 6 W。

根据欧姆定律可求出n>(0.75Ve)2/(0.6 Pe)。

开关电源EMI滤波器的设计要使EMI滤波器对EMI信号有最佳的衰减特性,设计与开关电源共模、差模噪声等效电路端接的EMI滤波器时,就要分别设计抗共模干扰滤波器和抗差模干扰滤波器才能收到满意的效果。

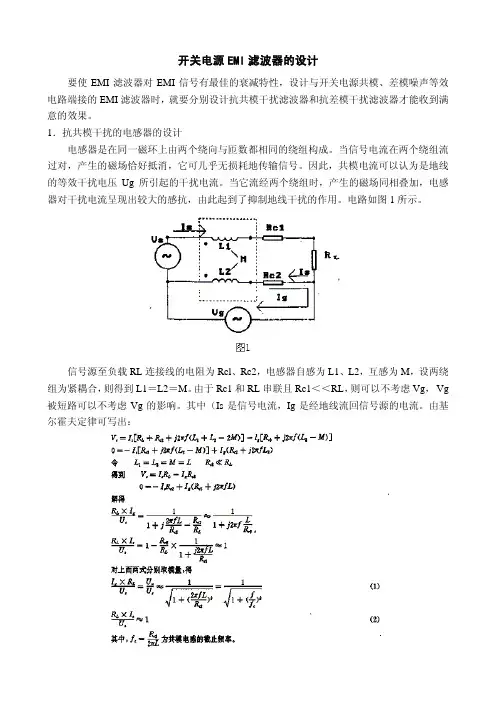

1.抗共模干扰的电感器的设计电感器是在同一磁环上由两个绕向与匝数都相同的绕组构成。

当信号电流在两个绕组流过对,产生的磁场恰好抵消,它可几乎无损耗地传输信号。

因此,共模电流可以认为是地线的等效干扰电压Ug所引起的干扰电流。

当它流经两个绕组时,产生的磁场同相叠加,电感器对干扰电流呈现出较大的感抗,由此起到了抑制地线干扰的作用。

电路如图1所示。

信号源至负载RL连接线的电阻为Rcl、Rc2,电感器自感为L1、L2,互感为M,设两绕组为紧耦合,则得到L1=L2=M。

由于Rc1和RL串联且Rc1<<RL,则可以不考虑Vg, Vg 被短路可以不考虑Vg的影响。

其中(Is是信号电流,Ig是经地线流回信号源的电流。

由基尔霍夫定律可写出:式(2)表明负载上的信号电压近似等于信号源电压,即共模电感传输有用信号时几乎不引入衰减。

由(1)式得知,共模千扰电流Ig随f:fc的比值增大而减小。

当f:fc的比值趋于无穷时,Ig=0,即干扰信号电流只在电感器的两个绕组中流过而不经过地线,这样就达到了抑制共模干扰的作用。

所以,可以根据需要抑制的干扰电压频率来设置电感器截止频率。

一般来说,当干扰电压频率f≥5fc时,即Vn:Vg≤0.197,就可认为达到有效抑制地线中心干扰的目的。

2.抗差模干扰的滤波器设计差模干扰的滤波器可以设计成Π型低通滤波器,电路如图2所示。

这种低通滤波器主要是设置电路截止频率人的值达到有效地抑制差模传导干扰的目的。

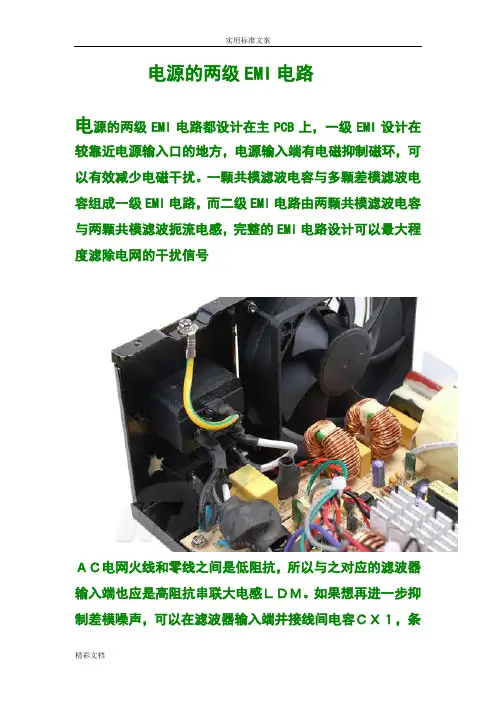

电源的两级EMI电路

电源的两级EMI电路都设计在主PCB上,一级EMI设计在较靠近电源输入口的地方,电源输入端有电磁抑制磁环,可以有效减少电磁干扰。

一颗共模滤波电容与多颗差模滤波电容组成一级EMI电路,而二级EMI电路由两颗共模滤波电容与两颗共模滤波扼流电感,完整的EMI电路设计可以最大程度滤除电网的干扰信号

AC电网火线和零线之间是低阻抗,所以与之对应的滤波器输入端也应是高阻抗串联大电感LDM。

如果想再进一步抑制差模噪声,可以在滤波器输入端并接线间电容CX1,条

件是它的阻抗要比AC电网火线、零线之间的阻抗还要低得多。

:Cx=0.1—2.0uF。

CY=2.0nF—33nF。

Lc=几—几十mH,随工作电流不同而取不同的参数值,如电流为25A时Lc=1.8mH。

电流为0.3A时,Lc=47mH。

另外在滤波元件选择中,一定要保证输入滤波器的谐振频率低于开1-8关电源的工作频率。

由于开关电源的开关频率谐波噪声源阻抗为低阻抗,所以与之相对应的滤波器输出端应是高阻抗串联大电感LDM。

PCB EMI设计规范IC的电源PIN都有一个0.1UF的去耦电容,对于BGA CHIP,要求在BGA的四角分别有0.1UF、0.01UF的电容共8个。

对PCB走线的电源尤其要注意加滤波电容,如VTT等。

这不仅对稳定性有影响,对EMI也有很大的影响。

1 、IC的电源处理1.1)保证每个IC的电源PIN都有一个0.1UF的去耦电容,对于BGA CHIP,要求在BGA的四角分别有0.1UF、0.01UF的电容共8个。

对PCB走线的电源尤其要注意加滤波电容,如VTT 等。

这不仅对稳定性有影响,对EMI也有很大的影响。

2、时钟线的处理2.1)建议先走时钟线。

2.2)频率大于等于66M的时钟线,每条过孔数不要超过2个,平均不得超过1.5个。

2.3)频率小于66M的时钟线,每条过孔数不要超过3个,平均不得超过2.5个2.4)长度超过12inch的时钟线,如果频率大于20M,过孔数不得超过2个。

2.5)如果时钟线有过孔,在过孔的相邻位置,在第二层(地层)和第三层(电源层)之间加一个旁路电容,以确保时钟线换层后,参考层(相邻层)的高频电流的回路连续。

旁路电容所在的电源层必须是过孔穿过的电源层,并尽可能地靠近过孔,旁路电容与过孔的间距最大不超过300MIL。

2.6)所有时钟线原则上不可以穿岛。

下面列举了穿岛的四种情形。

2.6.1) 跨岛出现在电源岛与电源岛之间。

此时时钟线在第四层的背面PCB走线,第三层(电源层)有两个电源岛,且第四层的PCB走线必须跨过这两个岛。

2.6.2) 跨岛出现在电源岛与地岛之间。

此时时钟线在第四层的背面PCB走线,第三层(电源层)的一个电源岛中间有一块地岛,且第四层的PCB走线必须跨过这两个岛。

如图2.6-2所示。

2.6.3) 跨岛出现在地岛与地层之间。

此时时钟线在第一层PCB走线,第二层(地层)的中间有一块地岛,且第一层的PCB走线必须跨过地岛,相当于地线被中断。

如图2.6-3所示。

2.6.4) 时钟线下面没有铺铜。

开关电源EMI滤波器的设计_王金霞煤矿电气开关电源EMI滤波器的设计王金霞1,杨庆江1,王金凤2(11黑龙江科技学院电信学院,哈尔滨150027; 21太平洋线路板公司,辽宁大连116001)摘要:文章首先分析了开关电源电磁干扰问题产生的原因及种类,建立开关电源EMI滤波器的共模和差模等效模型以分析噪声的传播方式,结合滤波器所需对应的开关电源工作频率为基础来设计滤波器,无需复杂的计算,对不同工作频率的开关电源有较强的针对性。

最后通过实例验证了此设计方法的可行性。

关键词:滤波器;开关电源;噪声;仿真;电磁干扰中图分类号:TN713 文献标识码:A 文章编号:1008 -8725(2009)05 -0033 -03Designing EMI Filter and SimulationWANG Jin-xia1, YANG Qing-jiang1, WANG Jin-feng2(1.College of Electric and Information, Heilongjiang Institute of Science and T echnology, Harbin 150027, China; 2.Pacific CircuitCompany,Dalian 116001, China)Abstract:In this paper first of all the category and causes of the switching mode power supp ly EMI are ana-lyzed.Second build the equivalentmodels for common mode and di fferential mode of switching power supplyEMI fi lter, this procedure is based on the analysis of noise and the frequency ofSMPS. This procedure needsno complex computing and fits SMPS with certain frequency well. Lastly, the feasibility of this design methodis verified by simulation.Key words:filter; SMPS; noise; simulation; EMI0 前言开关电源的特点是频率高、效率高、功率密度高和可靠性高。

电源滤波器的电磁兼容性设计0 引言电磁兼容性(EMC)是指电子、电器设备共处一个环境中能互不干扰、兼容工作的能力。

一个现代电子和电器产品(设备、系统)的电磁兼容性对保证产品正常功能的发挥起着至关重要的作用,这已是国内外业界公认的事实。

本文结合国军标的电磁兼容实验传导干扰项目及实验中遇到的问题分析了传导干扰产生的原因及测试方法,介绍了电源滤波器的设计及设备的电磁兼容设计中滤波器的选择方法。

首先介绍传导干扰产生的原因。

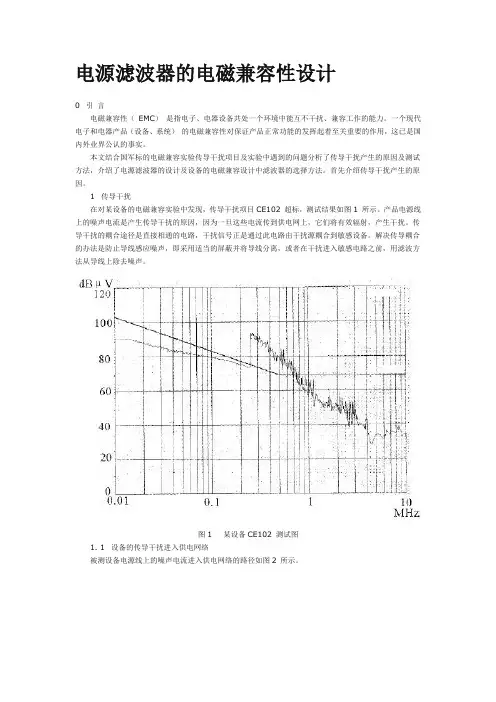

1 传导干扰在对某设备的电磁兼容实验中发现,传导干扰项目CE102 超标,测试结果如图1 所示。

产品电源线上的噪声电流是产生传导干扰的原因,因为一旦这些电流传到供电网上,它们将有效辐射,产生干扰。

传导干扰的耦合途径是直接相通的电路,干扰信号正是通过此电路由干扰源耦合到敏感设备。

解决传导耦合的办法是防止导线感应噪声,即采用适当的屏蔽并将导线分离,或者在干扰进入敏感电路之前,用滤波方法从导线上除去噪声。

图1 某设备CE102 测试图1. 1 设备的传导干扰进入供电网络被测设备电源线上的噪声电流进入供电网络的路径如图2 所示。

图2 在一个装置中产生的噪声链通过电源线图1. 2 利用阻抗稳定网络测量传导干扰利用阻抗稳定网络测量传导干扰的布置图如图3 所示。

图3 利用阻抗稳定网络测量传导发射图典型的阻抗稳定网络电原理图如图4 所示。

图4 典型FCC 阻抗稳定网络电原理图测量的电压由差模和共模电流两部分组成,用这些电流表示的相电压和中线电压为:用理想的L ISN 测量的共模和差模电流对传导干扰的影响见图5 .图5 用理想L ISN 测量的共模和差模电流对传导干扰的影响图从图5 中可看出共模噪声电流可对测量的传导干扰做出贡献,而且它们是通过地线返回,这一事实给出了减小传导干扰的一种有效方法,就是在地线中放一个电感来抑制共模电流,如图6 所示。

图6 利用安全地线电感阻隔共模电流双线制产品不采用地线连接,因此可认为没有共模电流,然而机壳与场地金属墙之间的电容也会构成共模电流回路。

5 电源EMI滤波器的PCB设计5.1 概述电源EMI滤波器的设计对于实现及改善电子设备和系统的电磁兼容性意义重大,它不但可降低设备产生的传导干扰,而且作为无源二端口网络具有互易性,可增强设备对电网侧的传导噪声,射频辐射干扰,高压噪声,快速瞬变电脉冲群等电磁干扰的抗扰度。

正确设计EMI 滤波器的PCB是充分发挥EMI滤波器性能的重要保证。

5.2 EMI滤波器的基本结构下图为EMI滤波器的基本结构:L N PEL1C Y1C Y2L2LNPE 图63 EMI滤波器的基本结构L1 ,L2为绕制在同一铁芯上的共模电感,其匝数相等,C Y1,C Y2为共模电容,L1与Cy1 ,L2与Cy2构成共模低通滤波器。

5.3 布局考虑5.3.1 输入线与输出线的布置在开关电源中,EMI滤波器的输出接开关整流器,属污染源,输出线上的噪声通过电场藕合或磁场藕合到输入线,会使EMI滤波器的效果大大降低,为了减小影响,要求EMI 滤波器的输入线与输出线间尽量隔离,不能邻近平行走线,以避免上述影响。

见下图。

⌒⌒⌒⌒⌒⌒●●●●●●●inputoutput○○←→噪声耦合C x CyC x图64 EMI 滤波器的输入线与输出线布置5.3.2 多级滤波器级联多级滤波器级联时,级间距离尽量做到远些,避免级间电感互感藕合。

多级滤波器布局的布局,根据这一原则,选择相应的排列方式,一般是按直线型排列,且相邻两个电感方向互相垂直较好。

5.3.3 EMI 滤波器的位置图65 EMI 滤波器的位置EMI 滤波器,一般布置在电源线入口处,远离开关管,输出整流管,变压器,输出电感等产生噪声的源头,使EMI 滤波器有一个比较干净的工作环境。

为此,在整体布局时,应将开关管,输出整流管,变压器等污染源布置在尽量远离输入输出端口处。

已标准的前面输入输出电源模块为例,比较好的布局如下图所示,A ,B ,C 三处距离尽量远一些。

如果因为结构或其它方面的原因使滤波器与噪声源之间的距离不能缩得很短,则建议在将滤波器用金属罩或其它结构屏蔽起来,并将屏蔽可靠接地。

EMI滤波电感设计技术 2009-08-05 14:14 阅读11 评论0字号:大中小EMI滤波器正常工作的开关类电源(SMPS)会产生有害的高频噪声,它能影响连接到相同电源线上的电子设备像计算机、仪器和马达控制。

用一个EMI滤波器插入电源线和SMPS之间能消除这类干扰(图1)。

一个差模噪声滤波器和一个共模噪声滤波器能够串联或在许多情况下单独使用共模噪声滤波器。

600)makesmallpic(this,6 00,1800);">图1 EMI滤波器的插入一、共模电感设计在一个共模滤波器内,电感的每一个绕阻和电源输入线中的任一根导线相串联。

(对于电源的输入线来讲)电感绕组的接法和相位是这样的,第一个绕组产生的磁通会与第二个绕组产生的磁通相削. 于是,除了泄漏阻抗的小损耗和绕组的直流电阻以外,电感至电源输入线的插入阻抗为另。

由于磁通的阻碍,SMPS的输入电流需要功率,因此将通过滤波器,滤波器应没有任何明显的损耗。

共模噪声的定义是出现在电源输入线的一根或二根导线上的有害电流通过电感的地返回噪声源的噪声。

此电流要视共模电感的任何一个或二个绕组的全部阻抗,因为它不能被返回的电流所抵消。

共模噪声电压是电感绕组上的衰减,应从有害噪声中保持电源输入线的畅通。

1.1、选择电感材料开关电源正常工作频率20KHz以上,而电源产生的有害噪声比20KHz高,往往在100KHz ~50MHz之间。

对于电感来讲,大多数选择适当和高效费比的铁氧体,因为在有害频带内能提供最高的阻抗。

当看到公共参数如磁导率和损耗系数就去识别材料是困难的。

图2给出铁氧体磁环J-42206-TC 绕10匝后的阻抗ZS和频率的关系曲线。

600)makesmallpic(this,600,180 0);">图2铁氧体磁环的阻抗和频率的关系在1~10MHz之间绕组到达最大阻抗,串联感抗XS和串联电阻RS(材料磁导率和损耗系数的函数)共同产生总阻抗Zt。

EMI滤波器的设计原理随着电子设备、计算机与家用电器的大量涌现和广泛普及,电网噪声干扰日益严重并形成一种公害。

特别是瞬态噪声干扰,其上升速度快、持续时间短、电压振幅度高(几百伏至几千伏)、随机性强,对微机和数字电路易产生严重干扰,常使人防不胜防,这已引起国内外电子界的高度重视。

电磁干扰滤波器(EMI Filter)是近年来被推广应用的一种新型组合器件。

它能有效地抑制电网噪声,提高电子设备的抗干扰能力及系统的可靠性,可广泛用于电子测量仪器、计算机机房设备、开关电源、测控系统等领域。

1 电磁干扰滤波器的构造原理及应用1.11 构造原理电源噪声是电磁干扰的一种,其传导噪声的频谱大致为10kHz~30MHz,最高可达150MHz。

根据传播方向的不同,电源噪声可分为两大类:一类是从电源进线引入的外界干扰,另一类是由电子设备产生并经电源线传导出去的噪声。

这表明噪声属于双向干扰信号,电子设备既是噪声干扰的对象,又是一个噪声源。

若从形成特点看,噪声干扰分串模干扰与共模干扰两种。

串模干扰是两条电源线之间(简称线对线)的噪声,共模干扰则是两条电源线对大地(简称线对地)的噪声。

因此,电磁干扰滤波器应符合电磁兼容性(EMC)的要求,也必须是双向射频滤波器,一方面要滤除从交流电源线上引入的外部电磁干扰,另一方面还能避免本身设备向外部发出噪声干扰,以免影响同一电磁环境下其他电子设备的正常工作。

此外,电磁干扰滤波器应对串模、共模干扰都起到抑制作用。

1.2 基本电路及典型应用电磁干扰滤波器的基本电路如图1所示。

该五端器件有两个输入端、两个输出端和一个接地端,使用时外壳应接通大地。

电路中包括共模扼流圈(亦称共模电感)L、滤波电容C1~C4。

L对串模干扰不起作用,但当出现共模干扰时,由于两个线圈的磁通方向相同,经过耦合后总电感量迅速增大,因此对共模信号呈现很大的感抗,使之不易通过,故称作共模扼流圈。

它的两个线圈分别绕在低损耗、高导磁率的铁氧体磁环上,当有电流通过时,两个线圈上的磁场就会互相加强。

PCB 板设计的EMI 和EMS 问题分析PCB 板的接口连接线及电缆的电磁兼容性问题;

分别来看EMI 和EMS 这两个方面;

EMI-辐射发射的问题:

在下示意图中与电路板相连的电缆也是产生辐射问题的原因之一,因为高速信号电流在电缆中流动由于环路和阻抗不匹配等原因;很易对外产生共模或差模的电磁辐射。

EMS-对于抗干扰问题:(EFT 的设计问题)

注意:排线电缆对参考接地有分布电容;我们进行耦合群脉冲试验时;高频的干扰信号耦合进来了。

这时候要检查GPIO 控制的输入接口要滤波(最简单用RC)和系统的供电的电源要进行干扰滤波;。

5 电源EMI滤波器的PCB设计

5.1 概述

电源EMI滤波器的设计对于实现及改善电子设备和系统的电磁兼容性意义重大,它不但可降低设备产生的传导干扰,而且作为无源二端口网络具有互易性,可增强设备对电网侧的传导噪声,射频辐射干扰,高压噪声,快速瞬变电脉冲群等电磁干扰的抗扰度。

正确设计EMI 滤波器的PCB是充分发挥EMI滤波器性能的重要保证。

5.2 EMI滤波器的基本结构

下图为EMI滤波器的基本结构:

L N PE

L1

C Y1C Y2

L2

L

N

PE 图63 EMI滤波器的基本结构

L1 ,L2为绕制在同一铁芯上的共模电感,其匝数相等,C Y1,C Y2为共模电容,L1与Cy1 ,L2与Cy2构成共模低通滤波器。

5.3 布局考虑

5.3.1 输入线与输出线的布置

在开关电源中,EMI滤波器的输出接开关整流器,属污染源,输出线上的噪声通过电场藕合或磁场藕合到输入线,会使EMI滤波器的效果大大降低,为了减小影响,要求EMI 滤波器的输入线与输出线间尽量隔离,不能邻近平行走线,以避免上述影响。

见下图。

⌒⌒⌒⌒⌒

⌒●

●

●

●

●

●

●

input

output

○

○

←→

噪声耦合

C x Cy

C x

图64 EMI 滤波器的输入线与输出线布置

5.3.2 多级滤波器级联

多级滤波器级联时,级间距离尽量做到远些,避免级间电感互感藕合。

多级滤波器布局的布

局,根据这一原则,选择相应的排列方式,一般是按直线型排列,且相邻两个电感方向互相垂直较好。

5.3.3 EMI 滤波器的位置

图65 EMI 滤波器的位置

EMI 滤波器,一般布置在电源线入口处,远离开关管,输出整流管,变压器,输出电感等产生噪声的源头,使EMI 滤波器有一个比较干净的工作环境。

为此,在整体布局时,应将开关管,输出整流管,变压器等污染源布置在尽量远离输入输出端口处。

已标准的前面输入输出电源模块为例,比较好的布局如下图所示,A ,B ,C 三处距离尽量远一些。

如果因为结构或其它方面的原因使滤波器与噪声源之间的距离不能缩得很短,则建议在将滤波器用金属罩或其它结构屏蔽起来,并将屏蔽可靠接地。

5.3.4 共模/差模电感的布置

在EMI 滤波器中,共模电感会产生强烈的杂散磁场,这些杂散磁场容易干扰其它器件,因此滤波电容应尽量远离,尤其是电容引线较长时更是如此。

其它敏感信号线也要避免从该区域穿过。

共模(差模)电感是由线圈绕在磁芯上组成,电感上的线圈很容易拾取干扰,因此尤其要注意使电感远离开关管变压器等易于产生干扰的地方。

下图B 中输出滤波电感产生干扰输入共模电感,使EMI 测试超标,在图A 中,将共模电感移开,并转换摆放方向,EMI 下降明显.

输入共模电

感

输入Y 电容

输出滤波电感

输入共模电感

输入Y 电容

输出滤波电感

A 正确布局

B 错误布局

图66共模/差模电感的布置

5.3.5 三相EMI 滤波器的线圈布置

三相EMI 滤波器的线圈要靠近放置,会产生电流补偿效应。

磁场泄漏会减少,插入损耗提高。

5.3.6 电容的布置

1 Y 电容放置在靠近接地螺钉的位置,使Y 电容和接地螺钉的走线最短,一般走线超过3~4CM 则电容的效果将接近于零。

Y 电容因为与机壳相连,所以布板时需要注意安规问题,必须按照有关规范执行。

5.4 布线考虑

通过认真仔细的布线,才能使EMI 滤波器发挥出预期的功能,随意的走线将使滤波器的功能较少甚至消失,下面是布线时的一些需要注意的地方。

5.4.1 电容的引线最短

抑制差模噪声电容的印制导线较细时,应使电容的引线最短,见下图。

图67 电容的引线最短

5.4.2 电容的引线开槽

抑制差模噪声电容的印制导线较宽时,在保证过电流的基础上应在电容焊盘处的铜皮上开一个近1mm小长槽,见下图。

图68 电容引线的开槽

5.4.3 接地线设计

抑制共模噪声电容的印制导线的画法,应使电容的引线最短,地线应尽量短且应适当加粗,见下图

地线短且适当加粗

●

图69 接地线设计

推荐的办法是在满足安规的前提下,对EMI滤波器部分进行大面积的铺地处理,所有走线由地平面所包围,然后将大面积地和机壳可靠相连。

5.4.4接地螺钉孔设计

接地螺钉孔金属化,且焊盘尺寸要大于安装螺钉及垫片尺寸,保证PCB上接地的可靠性。