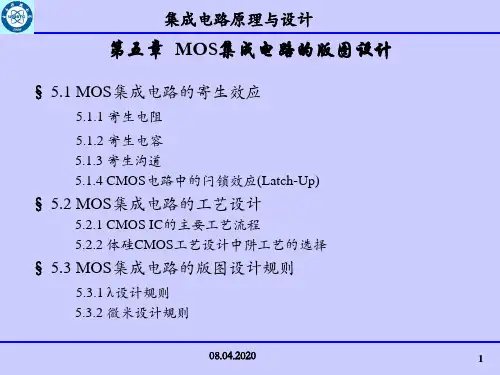

第五章 MOS电路版图设计

- 格式:ppt

- 大小:3.50 MB

- 文档页数:69

MOS管及简单CMOS逻辑门电路原理图现代单片机主要是采用C MOS工艺制成的。

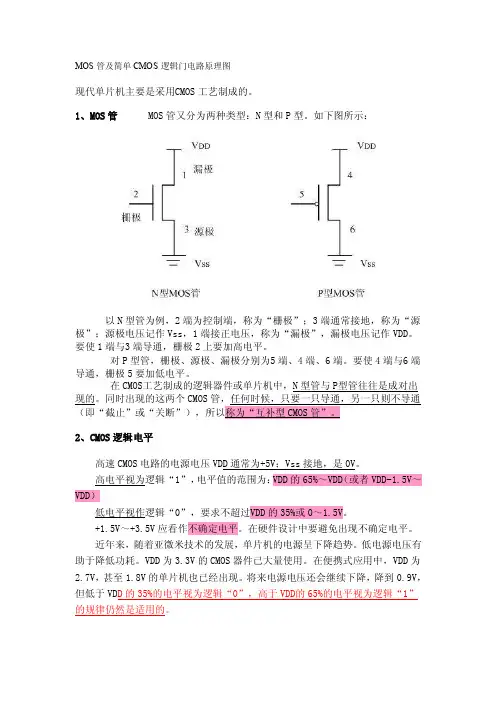

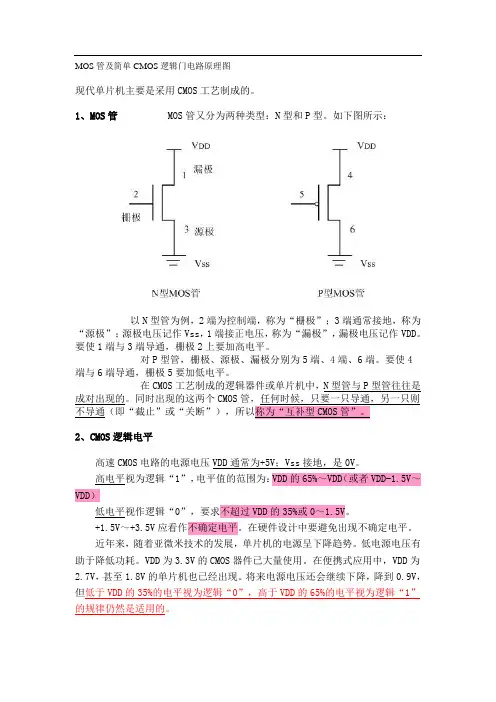

1、MOS管 MOS管又分为两种类型:N型和P型。

如下图所示:以N型管为例,2端为控制端,称为“栅极”;3端通常接地,称为“源极”;源极电压记作Vss,1端接正电压,称为“漏极”,漏极电压记作VDD。

要使1端与3端导通,栅极2上要加高电平。

对P型管,栅极、源极、漏极分别为5端、4端、6端。

要使4端与6端导通,栅极5要加低电平。

在CMOS工艺制成的逻辑器件或单片机中,N型管与P型管往往是成对出现的。

同时出现的这两个CMO S2、CMOS逻辑电平高速CMOS电路的电源电压VDD通常为+5V;Vss接地,是0V。

高电平视为逻辑“1”,电平值的范围为:VDD的65%~VDD(或者VDD-1.5V~VDD)低电平视作逻辑“0”,要求不超过V DD的35%或0~1.5V。

+1.5V~+3.5V应看作不确定电平。

在硬件设计中要避免出现不确定电平。

近年来,随着亚微米技术的发展,单片机的电源呈下降趋势。

低电源电压有助于降低功耗。

VDD为3.3V的CMO S器件已大量使用。

在便携式应用中,VDD为2.7V,甚至1.8V的单片机也已经出现。

将来电源电压还会继续下降,降到0.9V,但低于VDD的35%的电平视为逻辑“0”,高于VDD的65%的电平视为逻辑“1”的规律仍然是适用的。

3、非门非门(反向器)是最简单的门电路,由一对CMO S管组成。

其工作原理如下:A端为高电平时,P型管截止,N型管导通,输出端C的电平与Vss保持一致,输出低电平;A端为低电平时,P型管导通,N型管截止,输出端C的电平与VDD一致,输出高电平。

4、与非门与非门工作原理:①、A、B输入均为低电平时,1、2管导通,3、4管截止,C端电压与V DD 一致,输出高电平。

![毕业设计(论文)-cmos运算放大电路的版图设计[管理资料]](https://uimg.taocdn.com/15f996a177232f60dccca185.webp)

目录摘要 (3)第一章引言 (3)§ (3)§ CMOS 电路的发展和特点 (5)第二章CMOS运算放大器电路图 (8)§Pspice软件介绍 (8)Pspice运行环境 (12)Pspice功能简介 (12)§CMOS运算放大器电路图的制作 (14)§小结 (20)第三章版图设计 (20)§L-EDIT软件介绍 (20)§设计规则 (21)§集成电路版图设计 (24)PMOS版图设计 (24)NMOS版图设计 (27)CMOS运算放大器版图设计 (27)优化设计 (32)第四章仿真 (40)§DRC仿真 (41)§LVS 对照 (42)第五章总结 (48)附录 (50)参考文献 (52)致谢 (53)摘要介绍了CMOS运算放大电路的版图设计。

并对PMOS、NMOS、CMOS运算放大器版图、设计规则做了详细的分析。

通过设计规则检查(DRC)和版图与原理图对照(LVS)表明,此方案已基本达到了集成电路工艺的要求。

关键词:CMOS 放大器 NMOS PMOS 设计规则检查版图与原理图的对照AbstractThe layout desigen of CMOS operation amplifer is presented in this the layouts and design rules of PMOS,NMOS, and CMOS operation amplifer. The results of design rule check(DRC)and layout verification schmatic(LVS) shown that the project have already met to the needs of IC fabricated processing. Keywords: CMOS Amplifer NMOS PMOS DRC LVS第一章引言1.1 集成电路版图设计的发展现状和趋势集成电路的出现与飞速发展彻底改变了人类文明和人们日常生活的面目。

MOS管及简单CMOS逻辑门电路原理图现代单片机主要是采用CMOS工艺制成的。

1、MOS管 MOS管又分为两种类型:N型和P型。

如下图所示:以N型管为例,2端为控制端,称为“栅极”;3端通常接地,称为“源极”;源极电压记作Vss,1端接正电压,称为“漏极”,漏极电压记作VDD。

要使1端与3端导通,栅极2上要加高电平。

对P型管,栅极、源极、漏极分别为5端、4端、6端。

要使4端与6端导通,栅极5要加低电平。

在CMOS工艺制成的逻辑器件或单片机中,N型管与P型管往往是成对出现的。

同时出现的这两个CMOS管,任何时候,只要一只导通,另一只则不导通(即“截止”或“关断”),所以称为“互补型CMOS管”。

2、CMOS逻辑电平高速CMOS电路的电源电压VDD通常为+5V;Vss接地,是0V。

高电平视为逻辑“1”,电平值的范围为:VDD的65%~VDD(或者VDD-1.5V~VDD)低电平视作逻辑“0”,要求不超过VDD的35%或0~1.5V。

+1.5V~+3.5V应看作不确定电平。

在硬件设计中要避免出现不确定电平。

近年来,随着亚微米技术的发展,单片机的电源呈下降趋势。

低电源电压有助于降低功耗。

VDD为3.3V的CMOS器件已大量使用。

在便携式应用中,VDD为2.7V,甚至1.8V的单片机也已经出现。

将来电源电压还会继续下降,降到0.9V,但低于VDD的35%的电平视为逻辑“0”,高于VDD的65%的电平视为逻辑“1”的规律仍然是适用的。

3、非门非门(反向器)是最简单的门电路,由一对CMOS管组成。

其工作原理如下:A端为高电平时,P型管截止,N型管导通,输出端C的电平与Vss保持一致,输出低电平;A端为低电平时,P型管导通,N型管截止,输出端C的电平与V DD一致,输出高电平。

4、与非门与非门工作原理:①、A、B输入均为低电平时,1、2管导通,3、4管截止,C端电压与V DD 一致,输出高电平。

②、A输入高电平,B输入低电平时,1、3管导通,2、4管截止,C端电位与1管的漏极保持一致,输出高电平。

MOS 管及简单CMOS 逻辑门电路原理图现代单片机主要是采用CMO 工艺制成的。

1、MOS 管 MOS 管又分为两种类型:N 型和P 型。

如下图所示:V DD45 Ic6=VssP 型MOS 管以N 型管为例,2端为控制端,称为“栅极”;3端通常接地,称为 “源极”;源极电压记作Vss , 1端接正电压,称为“漏极”,漏极电压记作VDD 要使1端与3端导通,栅极2上要加高电平。

对P 型管,栅极、源极、漏极分别为 5端、4端、6端。

要使4 端与6端导通,栅极5要加低电平。

在CMO 工艺制成的逻辑器件或单片机中,N 型管与P 型管往往是 成对出现的。

同时出现的这两个 CMO 管,任何时候,只要一只导通,另一只则 不导通(即“截止”或“关断”),所以称为“互补型—CMO 管”。

.2、CMO 逻辑电平高速CMO 电路的电源电压 VDD S 常为+5V; Vss 接地,是0V 。

高电平视为逻辑“ 1”,电平值的范围为:VDD 勺65%-VDD 或者VDD-1.5V 〜VDD低电平视作逻辑“ 0”,要求不超过 VDD 的35%或 0〜1.5V 。

+1.5 V 〜+3.5V 应看作不确定电平。

在硬件设计中要避免出现不确定电平。

近年来,随着亚微米技术的发展,单片机的电源呈下降趋势。

低电源电压有 助于降低功耗。

VDD 为3.3V 的CMO 器件已大量使用。

在便携式应用中, VDC 为2.7V ,甚至1.8V 的单片机也已经出现。

将来电源电压还会继续下降,降到0.9V , 但低于VDD 的 35%勺电平视为逻辑“ 0”,高于VDD 勺65%勺电平视为逻辑“ 1” 的规律仍然是适用的。

VDD VssV DD_ VssI 订]原理图非门(反向器)是最简单的门电路,由一对 CMOS 管组成。

其工作原理如 下: A 端为高电平时,P 型管截止,N 型管导通,输出端C 的电平与Vss 保持一 致,输出低电平;A 端为低电平时,P 型管导通,N 型管截止,输出端C 的电平 与V DD —致,输出高电平。

MOS管功率放大器电路图与原理图文及其解析放大器电路的分类本文介绍MOS管功率放大器电路图,先来看看放大器电路的分类,按功率放大器电路中晶体管导通时间的不同可分:甲类功率放大器电路、乙类功率放大器电路和丙类功率放大器电路。

甲类功率放大器电路,在信号全范围内均导通,非线性失真小,但输出功率和效率低,因此低频功率放大器电路中主要用乙类或甲乙类功率放大电路。

功率放大器是根据信号的导通角分为A、B、AB、C和D类,我国亦称为甲、乙、甲乙、丙和丁类。

功率放大器电路的特殊问题(1)放大器电路的功率功率放大器电路的任务是推动负载,因此功率放大电路的重要指标是输出功率,而不是电压放大倍数。

(2)放大器电路的非线形失真功率放大器电路工作在大信号的情况时,非线性失真时必须考虑的问题。

因此,功率放大电路不能用小信号的等效电路进行分析,而只能用图解法进行分析。

(3)放大器电路的效率效率定义为:输出信号功率与直流电源供给频率之比。

放大电路的实质就是能量转换电路,因此它就存在着转换效率。

常用MOS管功率放大器电路图MOS管功率放大器电路图是由电路稳压电源模块、带阻滤波模块、电压放大模块、功率放大模块、AD转换模块以及液晶显示模块组成。

(一)MOS管功率放大器电路图-系统设计电路实现简单,功耗低,性价比很高。

该电路,图1所示是其组成框图。

电路稳压电源模块为系统提供能量;带阻滤波电路要实现50Hz频率点输出功率衰减;电压放大模块采用两级放大来将小信号放大,以便为功率放大提供足够电压;功率放大模块主要提高负载能力;AD转换模块便于单片机信号采集;显示模块则实时显示功率和整机效率。

(二)MOS管功率放大器电路图-硬件电路设计1、带阻滤波电路的设计采用OP07组成的二阶带阻滤波器的阻带范围为40~60 Hz,其电路如图2所示。

带阻滤波器的性能参数有中心频率ω0或f0,带宽BW和品质因数Q。

Q值越高,阻带越窄,陷波效果越好。

2、放大电路的设计电压放大电路可选用两个INA128芯片来对微弱信号进行放大。