ARM 指令集表格

- 格式:doc

- 大小:95.50 KB

- 文档页数:5

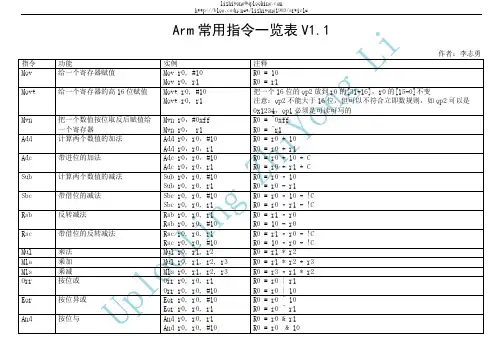

Arm常用指令一览表V1.1作者:李志勇指令功能实例注释Mov 给一个寄存器赋值Mov r0, #10Mov r0, r1R0 = 10R0 = r1Movt 给一个寄存器的高16位赋值Movt r0, #10Movt r0, r1把一个16位的op2放到r0的[31-16],r0的[15-0]不变注意:op2不能大于16位,但可以不符合立即数规则,如op2可以是0x1234,op1必须是可读可写的Mvn 把一个数值按位取反后赋值给一个寄存器Mvn r0,#0xffMvn r0, r1R0 = ~0xffR0 = ~r1Add 计算两个数值的加法Add r0,r0,#10Add r0,r0,r1R0 = r0 + 10R0 = r0 + r1Adc 带进位的加法Adc r0,r0,#10Adc r0,r0,r1R0 = r0 + 10 + CR0 = r0 + r1 + CSub 计算两个数值的减法Sub r0,r0, #10Sub r0, r0, r1R0 = r0 – 10R0 = r0 - r1Sbc 带借位的减法Sbc r0, r0, #10Sbc r0, r0, r1R0 = r0 – 10 - !CR0 = r0 – r1 - !CRsb 反转减法Rsb r0, r0, r1Rsb r0, r0, #10R0 = r1 – r0R0 = 10 - r0Rsc 带借位的反转减法Rsc r0, r0, r1Rsc r0, r0, #10R0 = r1 – r0 - !CR0 = 10 – r0 - !CMul 乘法Mul r0, r1, r2 R0 = r1 * r2Mla 乘加Mul r0, r1, r2, r3 R0 = r1 * r2 + r3Mls 乘减Mls r0, r1, r2, r3 R0 = r3 – r1 * r2Orr 按位或Orr r0, r0, r1Orr r0, r0, #10R0 = r0 | r1R0 = r0 | 10Eor 按位异或Eor r0, r0, #10Eor r0, r0, r1R0 = r0 ^ 10R0 = r0 ^ r1And 按位与And r0, r0, r1And r0, r0, #10R0 = r0 & r1R0 = r0 & 10Bic 位取反 Bic r0, r0, r1 Bic r0, r0, #10 R0 = r0 & (~r1) R0 = r0 & (~10) Lsr 逻辑右移 R0, lsr r1 R0, lsr #10 R0 >>> r1 R0 >>> 1 Lsl 逻辑左移 R0, lsl r1 R0, lsl #1 R0 <<< r1 R0 <<< 1 Asr 算术右移 R0, asr r1 R0, asr #1 R0 >> r1 R0 >> 1Ror 循环右移 R0, ror r1 R0, ror #1 (R0 >>> r1) | (R0 <<< (32 – r1)) (R0 >>> 1) | (R0 <<< (32 – 1)) Cmp 比较Cmp r0, r1 Cmp r0, #10 R0 – r1 影响cpsr 标志位 R0 – 10 影响cpsr 标志位 Teq 比较(按位异或) Teq r0, r1 Teq r0, #10 R0 ^ r1 影响cpsr 标志位 R0 ^ 10 影响cpsr 标志位 Tst 比较(按位与)Tst r0, r1 Tst r0, #10 R0 & r1 影响cpsr 标志位 R0 & 10 影响cpsr 标志位 Mrs 读cpsr Mrs r0, cpsr R0 = cpsr Msr 写cpsr Msr cpsr, r0 Cpsr = r0Swi 软中断 Swi 10 产生软中断异常 Svc 等同于swiSvc 10产生软中断异常 Ldr把数据从内存加载的寄存器Ldr r0, addr ldr r0, =addr ldr r1, [r0] ldr r1, [r0, #4] ldr r1, [r0, #4]! ldr r1, [r0], #4 R0 = *addr R0 = addr R1 = *r0R1 = *(r0 + 4)R1 = *(r0 + 4); r0 += 4 R1 = *r0; r0 += 4 Str 把数据从寄存器保存的内存Str r0, addr Str r1, [r0] Str r1, [r0, #4] Str r1, [r0, #4]! Str r1, [r0], #4*addr = r0 *r0 = r1*(r0 + 4) = r1*(r0 + 4) = r1; r0 += 4 *r0 = r1; r0 += 4Ldm 把数据从内存加载的寄存器 Ldmfd sp!, {r0-r12, lr} 把寄存器的值放到慢递减栈中 Stm把数据从寄存器保存的内存Stmfd sp!, {r0-r12, lr} 从慢递减栈中把值取到寄存器Push 压栈 Push {r0-r12, lr} 把寄存器的值放到慢递减栈中 Pop 出栈 Pop {r0-r12, lr} 从慢递减栈中把值取到寄存器 b 跳转B lable 跳到lable 处执行Bl 跳转并保存返回地址 Bl lable 保存下一条指令的地址到lr ,并跳转到lable 处执行 Bx 跳转(可切换状态)Bx r0跳转到r0所指的位置执行Clz 计算一个数值高位零的个数 Clz r0, r1计算r1中开头的零的个数,把计算结果放到r0 Qadd 饱和加法 Qadd r0, r0, r1 运算结果的饱和到[0x80000000,0x7fffffff]Qadd8 饱和8位加法 Qadd8 r0, r0, r1 r1和r2的每一个字节分别相加,饱和到[-2^7, 2^7-1] 注意:每一个操作数都是寄存器,不影响Q 位Qadd16 饱和16位加法 Qadd16 r0, r0, r1 r1和r2的每一个16位相加,饱和到[-2^15, 2^15-1] 注意:每一个操作数都是寄存器,不影响Q 位 Qsub 饱和减法Qsub r0, r0, r1 运算的结果饱和到[0x80000000,0x7fffffff]Qsub16 饱和16位减法 Qsub16 r0, r0, r1 r1和r2的每一个16位分别相减,饱和到[-2^15, 2^15-1] 注意:每一个操作数都是寄存器 ,不影响Q 位Qsub8 饱和8位减法 Qsub8 r0, r0, r1 r1和r2的每一个字节分别相减,饱和到[-2^7, 2^7-1] 注意:每一个操作数都是寄存器 ,不影响Q 位 Ssat有符号饱和Ssat r0, #sat, r11<=sat<=32把r1饱和到[-2^(sat-1), 2^(sat-1)-1],结果放到r0,如果饱和会置位Q注意:把r1饱和到sat 个位,饱和后符号不变 Ssat16 有符号16位饱和 Ssat16 r0, #sat, r11<=sat<=16把r1中的每一个16位饱和到[-2^(sat-1), 2^(sat-1)-1],结果放到r0,如果饱和会置位Q注意:把r1中的每一个16位饱和到sat 个位,饱和后符号不变 Usat 无符号饱和 Usat r0, #sat, r10<=sat<=31把r1饱和到[0, 2^sat-1],结果放到r0,如果饱和会置位Q 注意:负数饱和到0 Usat16 无符号16位饱和 Usat16 r0, #sat, r1usat16 r0,#sat,r1 0<=sat<=31把r1中的两个16位分别饱和到[0, 2^sat-1],结果放到r0,如果饱和会置位Q注意:负数饱和到0Rev大小端转换 Rev r0, r1把r1进行大小端转换,结果放到r0Rev16 16位大小端转换 Rev16 r0, r1 把r1的每个16位进行大小端转换,结果放到r0 Revsh 16位大小端转换并有符号扩展 Revsh r0, r1 把r1的低16位进行大小端转换,并扩展为一个32位的有符号数 Rbit 位反转 Rbit r0, r1 把r1进行位顺序翻转,结果放到r0 Uxtb16 无符号8位扩展16位 Uxtb16 r0,r1 把r1中的两个8位数无符号扩展为两个16位数,结果放到r0 Uxtb 无符号8位扩展32位 Uxtb8 r0,r1 把r1中的8位数无符号扩展为一个32位数,结果放到r0 Uxth 无符号16位扩展32位 Uxth r0,r1 把r1中的16位数无符号扩展为一个32位数,结果放到r0 Sxtb16 有符号8位扩展16位 Sxtb16 r0,r1 把r1中的两个8位数有符号扩展为两个16位数,结果放到r0 Sxtb 有符号8位扩展32位 Sxtb8 r0,r1 把r1中的8位数有符号扩展为一个32位数,结果放到r0 Sxth 有符号16位扩展32位 Sxth r0,r1 把r1中的16位数有符号扩展为一个32位数,结果放到r0注意:这里并不是arm 指令集的全部,只是arm 指令集中比较常用的指令,如想查看全部指令集,请到arm 官方网站自行下载:。

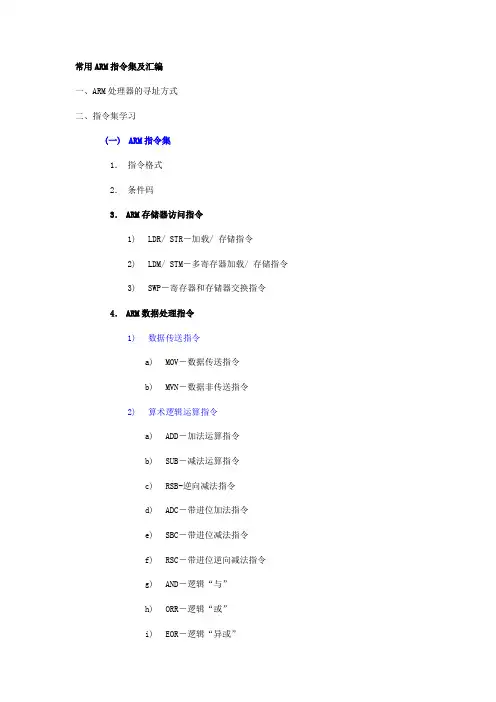

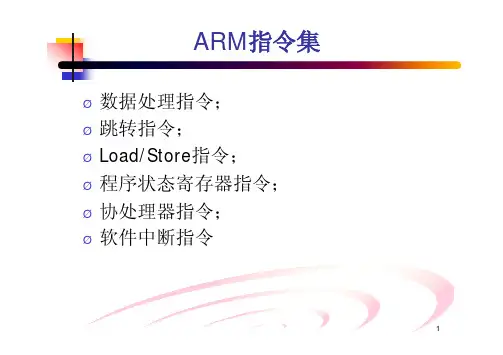

常用ARM指令集及汇编一、ARM处理器的寻址方式二、指令集学习(一)ARM指令集1.指令格式2.条件码3.ARM存储器访问指令1)LDR/ STR-加载/ 存储指令2)LDM/ STM-多寄存器加载/ 存储指令3)SWP-寄存器和存储器交换指令4.ARM数据处理指令1)数据传送指令a)MOV-数据传送指令b)MVN-数据非传送指令2)算术逻辑运算指令a)ADD-加法运算指令b)SUB-减法运算指令c)RSB-逆向减法指令d)ADC-带进位加法指令e)SBC-带进位减法指令f)RSC-带进位逆向减法指令g)AND-逻辑“与”h)ORR-逻辑“或”i)EOR-逻辑“异或”j)BIC-位清除指令3)比较指令a)CMP-比较指令b)CMN-负数比较指令c)TST-位测试指令d)TEQ-相等测试指令4)乘法指令a)MUL-32位乘法指令b)MLA-32位乘加指令c)UMULL-64位无符号乘法指令d)UMLAL-64位无符号乘加指令e)SMULL-64位有符号乘法指令f)SMLAL-64位有符号乘加指令5.ARM分支指令1)B-分支指令2)BL-带连接的分支指令3)BX-带状态切换的分支指令6.ARM协处理器指令1)CDP-协处理器数据操作指令2)LDC-协处理器数据读取指令3)STC-协处理器数据写入指令4)MCR-ARM处理器到协处理器的数据传送指令5)MRC-协处理器到ARM处理器的数据传送指令7.ARM杂项指令1)SWI-软中断指令2)MRS-读状态寄存器指令3)MSR-写状态寄存器指令8.ARM伪指令1)ADR-小范围的地址读取伪指令2)ADRL-中等范围的地址读取伪指令3)LDR-大范围的地址读取伪指令4)NOP-空操作伪指令(二)Thumb指令集1.Thumb指令集和ARM指令集的区别2.Thumb存储器访问指令1)LDR/ STR-加载/ 存储指令2)PUSH/ POP-寄存器入栈 / 出栈指令3)LDMIA/ STMIA-多寄存器加载/ 存储指令3.Thumb数据处理指令1)数据传送指令a)MOV-数据传送指令b)MVN-数据非传送指令c)NEG-数据取负指令2)算术逻辑运算指令a)ADD-加法运算指令b)SUB-减法运算指令c)ADC-带进位加法指令d)SBC-带进位减法指令e)MUL-乘法运算指令f)AND-逻辑“与”g)ORR-逻辑“或”h)EOR-逻辑“异或”i)BIC-位清除指令j)ASR-算术右移指令k)LSL-逻辑左移指令l)LSR-逻辑右移指令m)ROR-循环右移指令3)比较指令a)CMP-比较指令b)CMN-负数比较指令c)TST-位测试指令4.Thumb分支指令1)B-分支指令2)BL-带连接的分支指令3)BX-带状态切换的分支指令5.Thumb杂项指令1)SWI-软中断指令6.Thumb伪指令1)ADR-小范围的地址读取伪指令2)LDR-大范围的地址读取伪指令3)NOP-空操作伪指令。

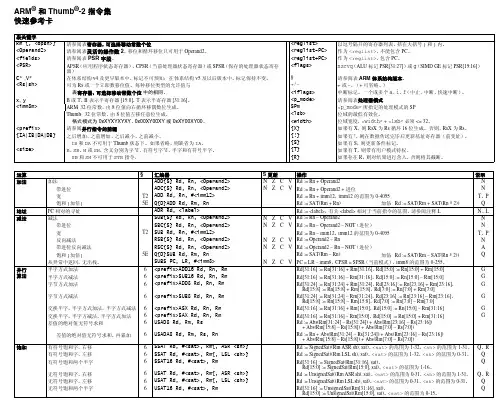

ARM®和 Thumb®-2 指令集快速参考卡表关键字Rm {, <opsh>}请参阅表寄存器,可选择移动常数个位<reglist>以逗号隔开的寄存器列表,括在大括号 { 和 } 内。

<Operand2>请参阅表灵活的操作数 2。

移位和循环移位只可用于 Operand2。

<reglist-PC>作为<reglist>,不能包含 PC。

<fields>请参阅表PSR 字段。

<reglist+PC>作为<reglist>,包含 PC。

<PSR>APSR(应用程序状态寄存器)、CPSR(当前处理器状态寄存器)或 SPSR(保存的处理器状态寄存器)<flags>nzcvq(ALU 标记 PSR[31:27])或g(SIMD GE 标记 PSR[19:16])C*,V*在体系结构 v4 及更早版本中,标记不可预知;在体系结构 v5 及以后版本中,标记保持不变。

§请参阅表ARM 体系结构版本。

<Rs|sh>可为 Rs 或一个立即数移位值。

每种移位类型的允许值与+/-+ 或 –。

(+ 可省略。

)表寄存器,可选择移动常数个位中的相同。

<iflags>中断标记。

一个或多个a、i、f(中止、中断、快速中断)。

x、y B 或 T,B 表示半寄存器 [15:0],T 表示半寄存器 [31:16]。

<p_mode>请参阅表处理器模式<imm8m>ARM:32 位常数,由 8 位值向右循环移偶数位生成。

SPm<p_mode>所指定的处理模式的 SPThumb: 32 位常数,由 8 位值左移任意位生成,<lsb>位域的最低有效位。

格式模式为 0xXYXYXYXY、0x00XY00XY 或 0xXY00XY00。

ARM汇编伪指令ARM条件码CPSR位[31:24]为条件位域,用f表示;位[23:16]为状态位域,用s表示;位[15:8] 为扩展位域,用x表示;位[7:0] 为控制位域,用c表示;与指令MSR相关关于移位中断向量表APCS寄存器使用约定Load and Store指令LDR R0,[R1] ;将存储器地址为R1的字数据读入寄存器R0。

LDR R0,[R1,R2] ;将存储器地址为R1+R2的字数据读入寄存器R0。

LDR R0,[R1,#8] ;将存储器地址为R1+8的字数据读入寄存器R0。

LDR R0,[R1,R2] !;将存储器地址为R1+R2的字数据读入寄存器R0,并将新地址R1+R2写入R1。

LDR R0,[R1,#8] !;将存储器地址为R1+8的字数据读入寄存器R0,并将新地址 R1+8写入R1。

LDR R0,[R1],R2 ;将存储器地址为R1的字数据读入寄存器R0,并将新地址 R1+R2写入R1。

LDR R0,[R1,R2,LSL#2]!;将存储器地址为R1+R2×4的字数据读入寄存器R0,并将新地址R1+R2×4写入R1。

LDR R0,[R1],R2,LSL#2 ;将存储器地址为R1的字数据读入寄存器R0,并将新地址R1+R2×4写入R1。

LDRB R0,[R1] ;将存储器地址为R1的字节数据读入寄存器 R0,并将R0的高24 位清零。

LDRB R0,[R1,#8] ;将存储器地址为R1+8的字节数据读入寄存器R0,并将 R0的高24位清零。

LDRH R0,[R1] ;将存储器地址为R1的半字数据读入寄存器 R0,并将R0的高16位清零。

LDRH R0,[R1,#8] ;将存储器地址为R1+8的半字数据读入寄存器R0,并将R0 的高16位清零。

LDRH R0,[R1,R2] ;将存储器地址为R1+R2的半字数据读入寄存器R0,并将 R0的高16位清零。

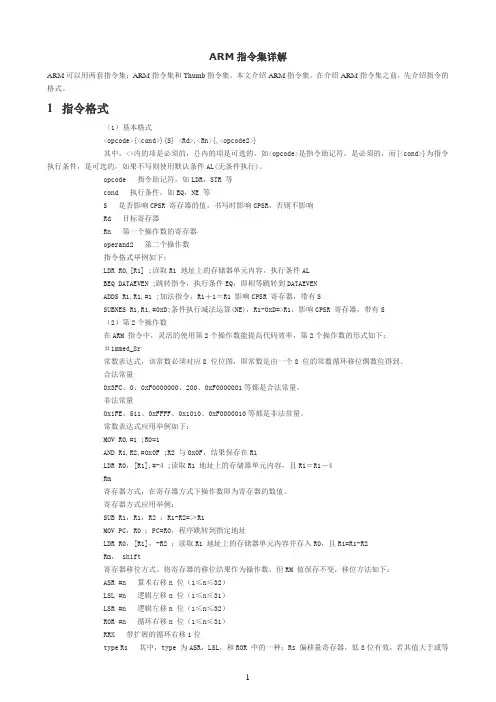

ARM指令集详解ARM可以用两套指令集:ARM指令集和Thumb指令集。

本文介绍ARM指令集。

在介绍ARM指令集之前,先介绍指令的格式。

1 指令格式(1)基本格式<opcode>{<cond>}{S} <Rd>,<Rn>{,<opcode2>}其中,<>内的项是必须的,{}内的项是可选的,如<opcode>是指令助记符,是必须的,而{<cond>}为指令执行条件,是可选的,如果不写则使用默认条件AL(无条件执行)。

opcode 指令助记符,如LDR,STR 等cond 执行条件,如EQ,NE 等S 是否影响CPSR 寄存器的值,书写时影响CPSR,否则不影响Rd 目标寄存器Rn 第一个操作数的寄存器operand2 第二个操作数指令格式举例如下:LDR R0,[R1] ;读取R1 地址上的存储器单元内容,执行条件ALBEQ DATAEVEN ;跳转指令,执行条件EQ,即相等跳转到DATAEVENADDS R1,R1,#1 ;加法指令,R1+1=R1 影响CPSR 寄存器,带有SSUBNES R1,R1,#0xD;条件执行减法运算(NE),R1-0xD=>R1,影响CPSR 寄存器,带有S(2)第2个操作数在ARM 指令中,灵活的使用第2个操作数能提高代码效率,第2个操作数的形式如下:#immed_8r常数表达式,该常数必须对应8 位位图,即常数是由一个8 位的常数循环移位偶数位得到。

合法常量0x3FC、0、0xF0000000、200、0xF0000001等都是合法常量。

非法常量0x1FE、511、0xFFFF、0x1010、0xF0000010等都是非法常量。

常数表达式应用举例如下:MOV R0,#1 ;R0=1AND R1,R2,#0x0F ;R2 与0x0F,结果保存在R1LDR R0,[R1],#-4 ;读取R1 地址上的存储器单元内容,且R1=R1-4Rm寄存器方式,在寄存器方式下操作数即为寄存器的数值。

ARM速查指令集(快速查找)

在本文档的汇编语法中,用 # 前缀表示立即值,用 & 表示十六进制值,用 % 表示二进制值,用 {花括号} 表示指令中可选的设置字段或位。

下面表格中粗体的指令是核心 ARM 指令,其他的是值得包含的位和片段、移位选项和汇编器助记码(mnemonic)... 还列出了协处理器指令。

但是用于 RISC OS 机器的 ARM 处理器不支持协处理器,只在一个可访问的芯片中提供了实际上的协处理器功能。

其中包括设置 ARM、cache、MMU 的设施,等...

RISC OS 的 BASIC 汇编器的伪指令

浮点指令指令索引。

ARM处理器的指令集ARM处理器的指令找了好久都没有找到完整版,在这里我把所有用过的ARM指令都整理下来,方便大家参考。

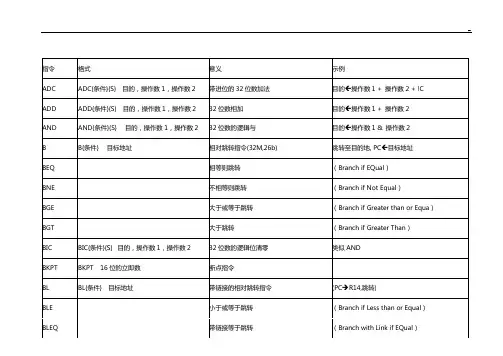

ADC(不更改状态寄存器): 带进位的加法(Addition with Carry)ADCS(更改状态寄存器)R1, R5, R9 ; R1=R5+R9,带进位ADD : 加法(Addition)ADD R0, R1, #256 ; R0 = R1 + 256AND : 逻辑与(logical AND)AND R0, R0, #3 ; R0 = 保持R0 的位0和1,丢弃其余的位。

BIC : 位清除(Bit Clear)BIC R0, R0, #%1011 ; 清除R0 中的位0、1、和3。

保持其余的不变。

EOR : 逻辑异或(logical Exclusive OR)EOR R0, R0, #3 ; 反转R0 中的位0 和1MOV : 传送(Move)MOV PC, R14 ; PC=R14MOVS PC, R14 ; 退出到调用者并恢复标志位(不遵从32-bit 体系)MVN : 传送取反的值(MoveNegative)MVN R0, #4 ; R0 = -5ORR : 逻辑或(logical OR)ORR R0, R0, #3 ; 设置R0 中位0 和1RSB : 反向减法(Reverse Subtraction)RSB R0, R1, R2 ; R0 = R2 - R1RSC : 带借位的反向减法(Reverse Subtraction with Carry)RSC{条件}{S} <dest>, <op 1>, <op 2>dest = op_2 - op_1 - !carrySBC : 带借位的减法(Subtraction with Carry)SBC{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 - op_2 - !carrySUB : 减法(Subtraction)SUB R0, R1, #256 ; R0 = R1 - 256ARM 处理器组建了可以与数据处理指令(ADC、ADD、AND、BIC、CMN、CMP、EOR、MOV、MVN、ORR、RSB、SBC、SUB、TEQ、TST)一起使用的桶式移位器(barrel shifter)。

ARM汇编指令集1 跳转指令1.1 跳转指令B:B LABLE ;跳转到标号LABEL处B 0X1111 ;跳转到绝对地址0X1111处1.2 带连接的跳转指令 BL:START …BL NEXT ;跳转到标号NEXT处,同时保存当前PC到R14中… ;返回地址…NEXT… ;子程序入口MOV PC,R14 ;返回1.3 带状态切换的跳转指令BX:MOV R0, #0X0201BX R0 ;程序跳转到0x0200处,微处理器切换到Thumb状态(地址必须是4的倍数,否则产生不可预知的后果)2算术运算指令2.1不带进位加法指令ADDADD R0, R1, R2 ;R0← (R1)+(R2)ADD R0, R1, #112 ;R0← (R1)+ 112ADD R0, R1, R2, LSL #1 ;R0←(R1)+(R2<<1) ;将R2中的值左移1位,再与R1值相加,结果送R02.2带进位加法指令 ADCADDS R0, R3, R6 ;加最低位字节,不带进位ADCS R1, R4, R7 ;加第二个字,带进位ADCS R2, R5,R8 ;加第三个字,带进位;三句话实现了96bit加法运算,由于ARM寄存器宽度只有32bit所以分三次相加2.3 不带进位减法指令SUB ;S—进位标志SUB R0, R1, R2 ;R0←(R1)- (R2)SUB R0, R1, #112 ;R0←(R1)- 112SUB R0, R1 ,R2 LSL#1 ;R0←(R1)- (R2<<1)2.4 带进位减法指令SBCSUBS R0, R3, R6 ;减最低位字节,不带进位SBCS R1, R4, R7 ;减第二个字,带进位SBCS R2, R5, R8 ;减第三个字,带进位;三句话实现了96bit减法运算,由于ARM寄存器宽度只有32bit所以分三次相减2.5 不带进位逆向减法指令RSBRSB R0, R1, R2 ;R0←(R2)- (R1)RSB R0, R1, #112 ;R0← 112- (R1)RSB R0, R1, R2, LSL#1 ;R0←(R2<<1)-R12.6 带进位逆向减法指令RSCRSBS R0, R6, R3 ;减最低字节的字,不带进位RSCS R1, R7, R4 ;减第二个字,带进位RSCS R2, R8, R5 ;减第三个字,带进位;三句话实现了96bit减法运算,由于ARM寄存器宽度只有32bit所以分三次相减2.732位乘法指令MULMUL R0, R1, R2 ;R0←(R1) X(R2)MULS R0, R1, R2 ;R0←(R1) X(R2) ;更新CPSR标志位2.8乘-累加指令 MLAMLA R0, R1, R2, R3 ;R0←(R1) X(R2)+(R3)MLAS R0, R1, R2, R3 ;R0←(R1) X(R2)+(R3) ;更新CPSR标志位2.9 无符号数长乘指令 UMULLMOV R5, #0X01MOV R8, #0X02UMULL R0, R1, R5, R8 ;(R1) (R0)←(R5)X(R8);UMULL指令实现64bit无符号数乘法2.10无符号长乘-累加指令 UMLALMOV R0, #0X01MOV R1, #0X02MOV R5, #0X01MOV R8, #0X02UMLAL R0, R1, R5, R8 ;R0←(R0) +(R5)X(R8)低字节;R1←(R1) +(R5) X(R8)高字节;UMLAL 指令为64位无符号乘-累加指令2.11有符号长乘指令SMULLMOV R5, #0X01MOV R8, #0X02SMULL R0, R1, R5, R8 ;(R1) (R0)←(R5)X(R8);SMULL指令实现64bit有符号数乘法2.12 有符号长乘-累加指令 SMLALMOV R0, #0X01MOV R1, #0X02MOV R5, #0X01MOV R8, #0X02SMLAL R0, R1, R5, R8 ;R0←(R0) +(R5)X(R8)低字节;R1←(R1) +(R5) X(R8)高字节; SMLAL 指令为64位有符号乘-累加指令2.13 比较指令 CMPCMP R1, #0X10 ;比较BGT TAG ;R1> #0X10转到TAG标号处……2.14负数比较指令 CMNCMN R0, #1 ;判断R0中的值是否为1的补码,是则置标志位Z为13逻辑运算指令3.1“与”指令 ANDMOV R0, 0XFFAND R0, R0, #3 ;取出R0的最低2bit3.2“或”指令 ORRMOV R0, 0XFFORR R0, R0, #33.3“异或”指令 EORMOV R0, 0XFFEOR R0, R0, #3 ;R0←(R0)^(0X03)3.4位清除指令 BICMOV R0, 0XFFBIC R0, R0, #B11 ;寄存器R0的低2bit被清零3.5测试比较指令 TSTTST R1, #b11 ;测试寄存器R1中的第0位和第1位,更新CPSR中标志位,应用中会在TST指令后加一条跳转指令。