51单片机CPLD综合开发板完整电路图

- 格式:pdf

- 大小:180.01 KB

- 文档页数:2

基于CPLD的数字电压表设计作者:陈世夏,纪明霞,戚甫峰来源:《现代电子技术》2010年第11期摘要:双积分型ADC具有转换精度高,速度慢的特点,因而被广泛应用于高精度数字仪器仪表中。

该设计的主要创新点是以可编程器件(CPLD)为核心,采用积分电路、检零比较器等组成16位ADC,控制部分采用51单片机,能实现自动量程转换。

由于采用了CPLD技术,减少了外界干扰和所占空间,而且大大提高了系统的响应时间,提高了数字电压表的性能。

关键词:CPLD; 数字电压表; 积分电路; OP07中图分类号:TP216 文献标识码:A文章编号:1004-373X(2010)11-0164-03Desing of Digital Voltmeter Based on CPLDCHEN Shi-xia, JI Ming-xia, QI Fu-feng(Qingdao Branch, Navy Aeronautical Engineering Academy, Qingdao 266041, China)Abstract: Since the double integral type of ADC takes on the characteristics of high conversion accuracy and slow speedt, it is widely used in the high-precision digital instruments. The double integral electro circuit, zero-checking comparator and FPGA are adopted in the design to makeup the 16 bit ADC. AT80C51 single chip computer is used in the control section, which is also able to compare zero automatically and carry the transform of capacity rules. Because the interferes from outside and the space occupied by electro circuits are reduced through the employment of FPGA technology, the system response time and the performance of digital voltmeter are improved enormously.Keywords: CPLD; digital voltmeter; integral circuit; OP07设计了基于CPLD的数字电压表,采用CPLD器件作为核心处理电路,用单片机进行控制,能较好地减小外界干扰,提高分辨率。

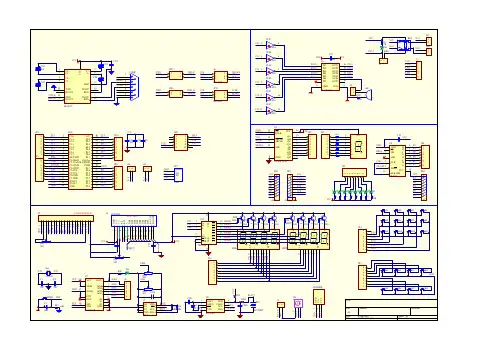

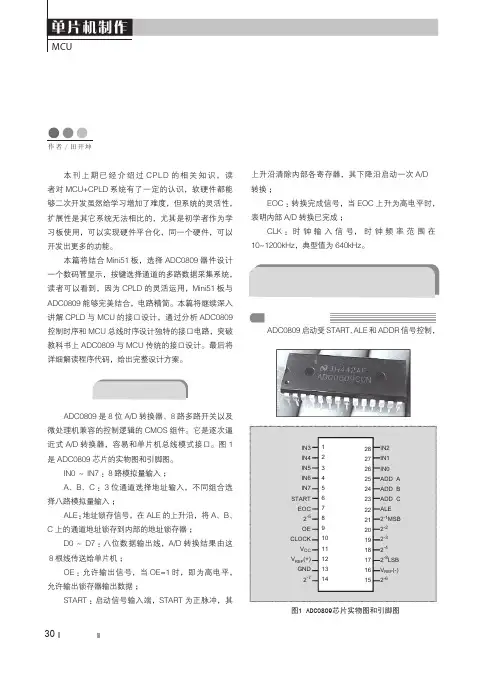

基于CPLD的单片机接口设计作者:田开坤徐海霞来源:《现代电子技术》2008年第02期摘要:现在分离元件在很多电路设计中还在普遍使用,完成逻辑转换、地址译码、数据锁存等任务,在PLD技术相当成熟的今天,采用PLD代替传统分离元器件,将会极大地减小PCB尺寸,节约成本。

对CPLD器件和开发工具进行研究,提出一种单片机与CPLD总线接口方案。

运用该方案设计单片机系统实现A/D,D/A,LCD等多种外设的接口,电路简洁,并给出CPLD电路设计方案,总体电路原理图和关键程序代码。

关键词:CPLD;分离元件;PLD;中图分类号:TP331.1 文献标识码:B 文章编号:1004-373X(2008)02-034-TIAN Kaikun,(Electrician and Electronics Experiment Center,Hubei NormalAbstract:Many circuit design still use separative components in nowadays,completes the logic to transform,the address decoding,the data lock saves and so on.Today the PLD technology has become more and more mature,using the PLD technology instead of tradational separative components not only reduce the PCB size,but also save the cost.This paper researches CPLD devices and the reference tools,proposes a bus interface between single chip computer and CPLD.The single chip computer system contain A/D,D/A,LCD and something else,adopting this way,making the circuit more easy and clear.This paper also gives CPLD circuit design scheme,circuit theory graphic and theKeywords:CPLD;separative c1 引言随着PLD(可编程器件)技术的成熟,应用越来越广泛。

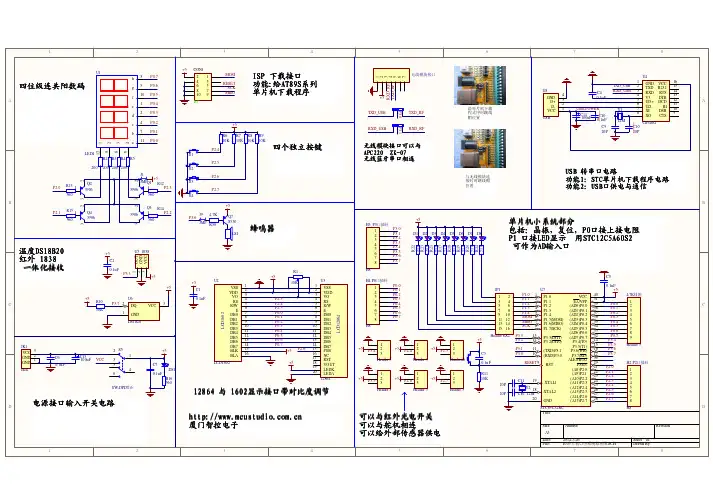

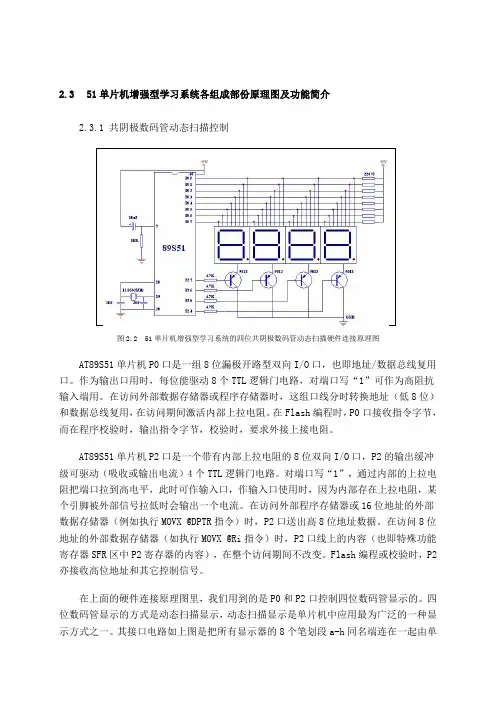

2.3 51单片机增强型学习系统各组成部份原理图及功能简介2.3.1 共阴极数码管动态扫描控制图2.2 51单片机增强型学习系统的四位共阴极数码管动态扫描硬件连接原理图AT89S51单片机P0口是一组8位漏极开路型双向I/O 口,也即地址/数据总线复用口。

作为输出口用时,每位能驱动8个TTL 逻辑门电路,对端口写“1”可作为高阻抗输入端用。

在访问外部数据存储器或程序存储器时,这组口线分时转换地址(低8位)和数据总线复用,在访问期间激活内部上拉电阻。

在Flash 编程时,P0口接收指令字节,而在程序校验时,输出指令字节,校验时,要求外接上接电阻。

AT89S51单片机P2口是一个带有内部上拉电阻的8位双向I/O 口,P2的输出缓冲级可驱动(吸收或输出电流)4个TTL 逻辑门电路。

对端口写“1”,通过内部的上拉电阻把端口拉到高电平,此时可作输入口,作输入口使用时,因为内部存在上拉电阻,某个引脚被外部信号拉低时会输出一个电流。

在访问外部程序存储器或16位地址的外部数据存储器(例如执行MOVX @DPTR 指令)时,P2口送出高8位地址数据。

在访问8位地址的外部数据存储器(如执行MOVX @Ri 指令)时,P2口线上的内容(也即特殊功能寄存器SFR 区中P2寄存器的内容),在整个访问期间不改变。

Flash 编程或校验时,P2亦接收高位地址和其它控制信号。

在上面的硬件连接原理图里,我们用到的是P0和P2口控制四位数码管显示的。

四位数码管显示的方式是动态扫描显示,动态扫描显示是单片机中应用最为广泛的一种显示方式之一。

其接口电路如上图是把所有显示器的8个笔划段a-h同名端连在一起由单51单片机增强型学习系统片机的P0.0~P0.7控制,而每一个数码管的公共极(阴极)是各自独立地受单片机P2.7~P2.4控制。

CPU向字段输出口P0口送出字形码时,所有数码管接收到相同的字形码,但究竟是那个数码管亮则取决于P2.7~P2.4的输入结果,所以我们就可以自行决定何时显示哪一位了。

《国外电子元器件》2008年第6期1引言现代控制系统中控制对象可能是复杂、分散的,而且往往是并行、独立工作的,但整体上它们是相互关联的有机组合[1]。

因此,控制信号的时序逻辑则要求更加精确。

CPLD单片机为控制系统提供了技术支持,由CPLD和单片机组成的多机系统具有逻辑控制方便,时序精确,并行工作,人机接口友好等优点。

因此,本文提出了一种基于CPLD与单片机控制的多路精确延时控制系统的设计方案。

2设计指标与系统原理2.1设计指标输出多路脉宽为10ms正脉冲信号;脉冲输出时间独立调节、显示;时间调整范围与精度为微秒级的调整范围为1 ̄199μs,调节精度为1μs;毫秒级的调整范围为1 ̄199ms,调整精度为1ms;提供计时基准信号和工作状态提示声音;9V电池供电。

2.2系统设计原理2.2.1系统时钟本系统设计由CPLD和多个单片机组成,CPLD对24MHz高精度一体化晶体振荡器二分频得到多路同步时钟信号作为多个单片机的系统时钟,并由各个单片机外脉冲信号引脚XTAL2注入[2],二分频确保信号的占空比为50%,满足单片机时钟脉冲信号高低电平持续时间大于20ns和最高脉冲频率为基于单片机+CPLD的多路精确延时控制系统设计谭凤军(瑞能北方风电设备有限公司,内蒙古包头014033)摘要:根据多路精确延时控制系统的设计参数指标,利用单片机和CPLD的功能特性与片上资源,设计了基于CPLD与多个单片机的多路精确延时控制系统,实现了多路独立调整、显示,并能输出多个精确的延时控制信号。

给出了系统电路原理图、软件流程和实际应用效果。

该系统设计可为其他同步控制系统提供借鉴。

关键词:控制系统;单片机;CPLD;精确延时;中断中图分类号:TP271+.82文献标识码:A文章编号:1006-6977(2008)06-0026-04Designofmuliti-channelsexactdelaytimecontrolsystembasedonmicrocontroller&CPLDTANFeng-jun(REpowerNorth(CHINA)Co.,Ltd,Baotou014033,China)Abstract:Accordingtothedesignobjectsofthemuliti-channelsexactdelaytimecontrolsystem,utiliz-ingthecharactersofthemicrocontroller&CPLDandtheresourcesofon-chip.Thispaperpresentsamuliti-channelsexactdelaytimecontrolsystembasedonmicrocontroller&CPLD,whichmayindepen-dentlyadjustanddisplay,andcanoutputmulti-channelsexactdelaytimecontrolsignals.Thesystemcircuitandthesoftwareflowdiagramsaregiveninthispaper.Andthepracticalapplicationcharacteris-ticistest.Thissystemcanofferreferenceforothersynchroniccontrolsystem.Keywords:controlsystem;microcontroller;CPLD;exactdelaytime;interrupter研究与开发收稿日期:2008-04-10稿件编号:200804011作者简介:谭凤军(1978-),男,内蒙古包头人,工程硕士,电器工程师,从事大型风力发电机控制系统研究,嵌入式控制系统开发。