基于STM32的四路抢答器原理图

- 格式:pdf

- 大小:514.57 KB

- 文档页数:2

1.设计目的当今的社会竞争日益激烈,选拔人才,评选优胜,知识竞赛之类的活动愈加频繁,而在竞赛中往往分为几组参加,这时针对主持人提出的问题,如果要是让抢答者用举手等方法,这在某种程度上会因为主持人的主观误断造成比赛的不公平性。

比赛中为了准确、公正、直观地判断出第一抢答者,这就要有一种抢答设备作为裁判员,这就必然离不开抢答器。

在数字电路设计的过程中具体的目的如下:1)巩固和加深对电子电路基本知识的理解,提高综合运用本课程所学知识的能力。

2)培养根据设计需要选学参考书籍,查阅相关手册、图表和文献资料的自学能力,并掌握抢答器的基本原理,掌握4D锁存器、计数器、555定时器的工作原理和使用方法。

3)通过电路方案的分析、论证和比较,设计计算和选取元器件、电路组装、调试和检测等环节,初步掌握简单实用电路的分析方法和工程设计方法。

4)学会简单电路的实验调试和性能指标的测试方法,提高学生动手能力和进行数字电子电路实验的基本技能,学会使用Multisim仿真软件。

2.设计要求及方案论证2.1设计要求(1)四组参赛者在进行抢答时(用4组彩灯代表),当抢先者按下面前的按钮时,抢答器能准确地判断出抢先者,并以声、光为标志。

要求声响、光亮时间为9秒后自动熄灭。

(2)抢答器应具有互锁功能,某组抢答后能自动封锁其他各组进行抢答。

(3)抢答器应具有限时(抢答时间、回答问题时间)的功能。

限时档次分别为30秒、60秒、90秒;时间到时应发出声响。

同时,时间数据要用数码管显示出来。

(4)抢答者犯规或违章时,应自动发出警告信号,以提示灯光闪为标志。

(5)系统应具有一个总复位开关。

2.2方案论证方案一,用优先编码器74LS148和74LS279锁存器实现抢答和锁存功能,用加法器74LS160实现计数功能,但此方案电路繁琐复杂,不做选用。

方案二,用4D触发器74LS175实现抢答并锁存功能,用计数器74LS192实现定时功能,此方案电路相对简单,并且74LS192可以实现减数倒计时功能,所以选用方案二。

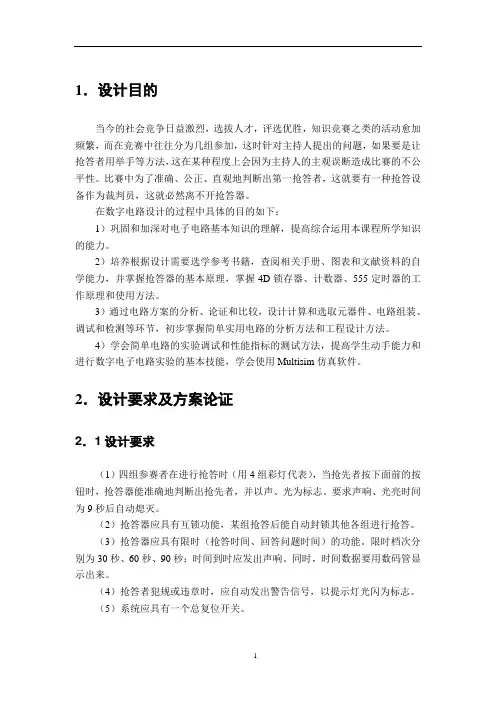

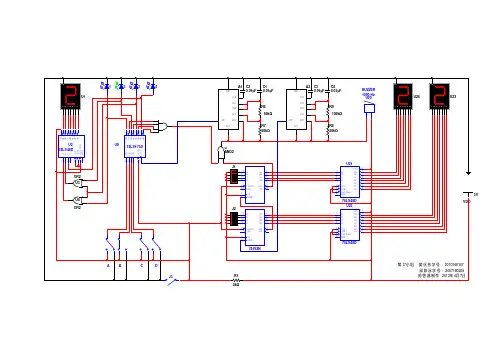

电路组成及工作原理四路竞赛抢答器总电路原理图如图1所示。

图1 四路竞赛抢答器原理图1.抢答器电路原理:如图2,IO1,IO2,IO3,IO4分别为抢答器按钮的输入端,开始抢答,假设IO1抢答成功,通过四D触发器输出Q1=1,Q1’=0,而Q 2’=Q3’=Q4’=1,通过四输入与非门后,输出高电平,再经过反相器输出低电平,再经过两输入与非门,输出低电平,此时四D触发器处于保持状态,并且其他按钮的输入不起作用,IO1的抢答信号被锁存。

此时LED1发光并且蜂鸣器发出响声。

其他抢答按钮同理。

图2 抢答器部分电路图2.计时电路原理:计时电路为两片74LS160用置数法构成的31进制计数器,因为可以为了让答题者直观的看到30S这个时间点,所以设置了31进制的计数器。

两片的四个输入端均接低电平,两片的输出端分别接七段译码管直接显示数字,高位的74LS160芯片的Q1Q2接到一个二输入的与非门(U8A)输出到计数器的LD端、三输入与非门端、反相器端。

输出到LD端是为了构成31进制计数器,当高位变为3时,计数器置0。

输出到三输入与非门(U9A)和时钟脉冲、开关的电平信号一起输入到与非门中,这就是为什么能控制计时的开始与暂停了,当开关输入低电平时,无论是否有时钟信号,时钟均不发生改变,此时时钟信号为无效信号;而当开关输入高电平时,U8A输出也为高,因此,时钟信号为有效信号,因此,凭借这样的类似锁存的电路,就可以控制计时的开始与暂停。

而当时间到了30s时,U8A输出为低电平,时钟信号又成为无效信号,时间被停止在30s,此时将U8A信号通过一个反相器输出到蜂鸣器,蜂鸣器发出响声。

图3 计时器电路3.555函数发生器:输出高电平时间:T1=(R1+R2)Cln2 输出低电平时间:T2=R2Cln2 振荡周期:T=(R1+2R2)Cln2图4 555函数发生器。

课程设计说明书题目:基于STM32的四路抢答器学院:年级专业:学号:学生姓名:指导教师:摘要在各种智力竞赛场合,抢答器是必不可少的最公正的用具。

在我们各种竞赛中我们也经常能看到有抢答的环节,某些举办方采用让选手通过举答题板的方法判断选手的答题权,这在某种程度上会因为主持人的主观误断造成比赛的不公平性,而抢答器的应用就能避免这种弊端。

今天随着科技的不断进步抢答器的制作也更加追求精益求精,人们摆脱了耗费很多元件仅来实现用指示灯和一些电路来实现简单的抢答功能,使第一个抢答的参赛者的编号能通过指示灯显示出来,避免不合理的现象发生。

但这种电路不易于扩展,而且当有更高要求时就无法实现,例如参赛人数的增加。

随着数字电路的发展,数字抢答器诞生了,它易于扩展,可靠性好,集成度高,而且费用低,功能更加多样,是一种高效能的产品。

而如今在市场上销售的抢答器大多采用可编程逻辑元器件,或利用单片机技术进行设计。

本文实现了一个基于嵌入式STM32单片机的4路抢答器系统设计,本系统设计主要分为硬件设备和软件控制两大部分。

外部硬件使用STM32单片机作为控制中心,用4个按键作为抢答输入,抢答开始后,抢答成功者的LED灯标识为红色闪烁,并且显示各抢答输入的时间。

关键词:智能抢答器,STM32,按键输入,数码管显示目录摘要 (2)目录 (3)第1章绪论 (5)1.1课题研究的相关背景 (5)1.2选题的目的和意义 (5)1.3课题研究的内容 (5)1.4国内外研究现状 (6)1.5抢答器目前存在的主要问题 (6)第2章抢答器的系统概述 (7)2.1系统的主要功能 (7)2.2抢答器的工作流程 (7)2.3STM32的功能及简介 (7)2.4抢答器的优点及组成 (10)2.5本章小结 (11)第3章系统的硬件设计与开发 (11)3.1系统硬件总体设计 (11)3.2STM32最小系统 (12)3.4时钟频率电路的设计 (14)3.5复位电路的设计 (15)3.6数码管显示 (16)3.7键盘电路的设计 (16)3.8LED电路 (18)3.9本章小结 (18)第4章系统的软件设计与开发 (19)4.4主要程序分析 (20)4.5本章小结 (29)第5章总结与展望 (30)5.1总结 (30)5.2展望 (31)致谢 (32)参考文献 (33)第1章绪论1.1 课题研究的相关背景抢答器是一种应用非常广泛的设备,在各种竞赛、抢答场合中,它能迅速、客观地分辨出最先获得发言权的选手。

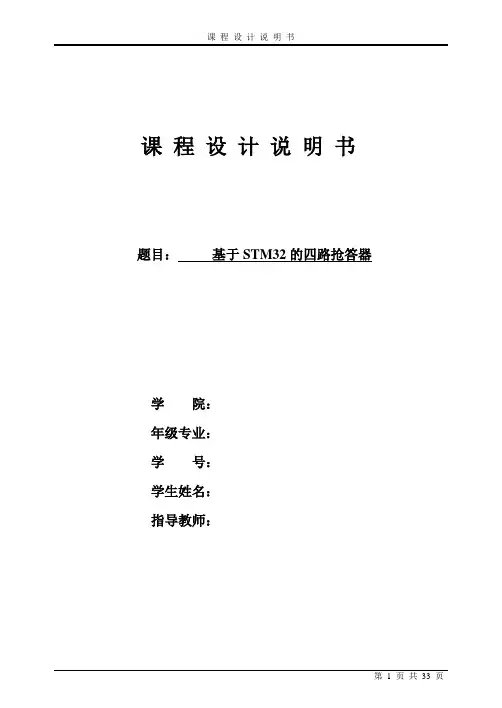

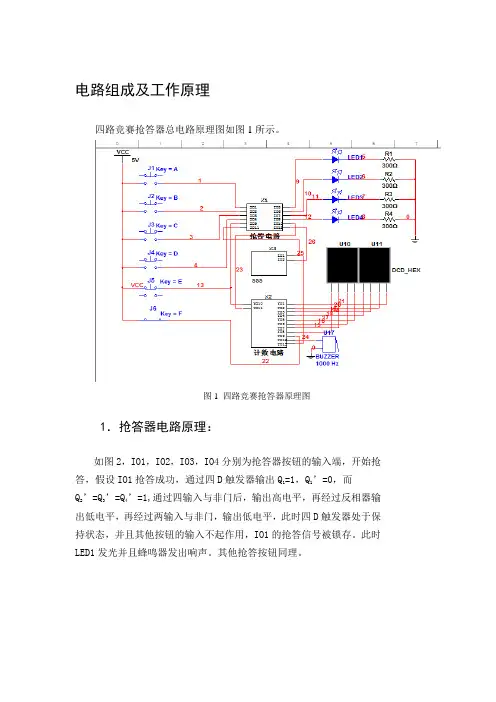

电路组成及工作原理四路竞赛抢答器总电路原理图如图1所示。

图1 四路竞赛抢答器原理图1.抢答器电路原理:如图2,IO1,IO2,IO3,IO4分别为抢答器按钮的输入端,开始抢答,假设IO1抢答成功,通过四D触发器输出Q1=1,Q1’=0,而Q 2’=Q3’=Q4’=1,通过四输入与非门后,输出高电平,再经过反相器输出低电平,再经过两输入与非门,输出低电平,此时四D触发器处于保持状态,并且其他按钮的输入不起作用,IO1的抢答信号被锁存。

此时LED1发光并且蜂鸣器发出响声。

其他抢答按钮同理。

图2 抢答器部分电路图2.计时电路原理:计时电路为两片74LS160用置数法构成的31进制计数器,因为可以为了让答题者直观的看到30S这个时间点,所以设置了31进制的计数器。

两片的四个输入端均接低电平,两片的输出端分别接七段译码管直接显示数字,高位的74LS160芯片的Q1Q2接到一个二输入的与非门(U8A)输出到计数器的LD端、三输入与非门端、反相器端。

输出到LD端是为了构成31进制计数器,当高位变为3时,计数器置0。

输出到三输入与非门(U9A)和时钟脉冲、开关的电平信号一起输入到与非门中,这就是为什么能控制计时的开始与暂停了,当开关输入低电平时,无论是否有时钟信号,时钟均不发生改变,此时时钟信号为无效信号;而当开关输入高电平时,U8A输出也为高,因此,时钟信号为有效信号,因此,凭借这样的类似锁存的电路,就可以控制计时的开始与暂停。

而当时间到了30s时,U8A输出为低电平,时钟信号又成为无效信号,时间被停止在30s,此时将U8A信号通过一个反相器输出到蜂鸣器,蜂鸣器发出响声。

图3 计时器电路3.555函数发生器:输出高电平时间:T1=(R1+R2)Cln2输出低电平时间:T2=R2Cln2振荡周期:T=(R1+2R2)Cln2图4 555函数发生器。

编号:审定成绩:XXXX大学课程设计(单片机)设计(论文)题目:四人抢答器电路的制作与调试(单片机)学院名称:计算机学院学生姓名:X X专业:计算机科学与技术班级:学号:指导教师:X X X答辩组负责人:填表时间:2005 年 6 月XXXX大学教务处P2-M4.1抢答器功能分析抢答器是竞赛问答中一种常用的必备装置,从原理上讲,它是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

本课题介绍一款采用D触发器数字集成电路制成的数字显示四路抢答器,它利用数字集成电路的锁存特性,实现优先抢答和数字显示功能,要求如下:1.设计一个可供4名选手参加比赛的4路数字显示抢答器。

他们的编号分别为“1”、“2”、“3”、“4”各用一个抢答按钮,编号与参赛者的号码一一对应。

2.抢答器具有数据锁存功能,并将锁存的数据用LED数码管显示出抢答成功者的号码。

3.抢答器对抢答选手动作的先后有很强的分辨能力,即使他们的动作仅相差几毫秒,也能分辨出抢答者的先后来。

即不显示后动作的选手编号。

4.主持人具有手动控制开关,可以手动清零复位,为下一轮抢答做准备。

一、抢答器的组成抢答器的一般组成框图如图2-4-1所示。

它主要由开关阵列电路、触发锁存电路、编码器、7段显示译码器、数码显示器等几部分组成。

下面逐一给予介绍。

图2-4-1抢答器的组成框图(1) 开关阵列电路该电路由多路开关所组成,每一竞赛者与一组开关相对应。

开关应为常开型,当按下开关时,开关闭合;当松开开关时,开关自动弹出断开。

(2) 触发锁存电路当某一开关首先按下时,触发锁存电路被触发,在输出端产生相应的开关电平信息,同时为防止其它开关随后触发而产生紊乱,最先产生的输出电平变化又反过来将触发电路锁定。

(3) 编码器编码器的作用是将某一开关信息转化为相应的8421BCD码,以提供数字显示电路所需要的编码输入。

(4) 7段显示译码器译码驱动电路将编码器输出的8421BCD码转换为数码管需要的逻辑状态,并且为保证数码管正常工作提供足够的工作电流。

module jiaozhiqi(clk,out,waveout);input clk;output out,waveout;reg[0:0] out;reg[0:0] waveout;reg code0,code1,code2,code3;reg A[15:0];reg B[15:0];reg[4:0] I,J,f;wire clk;reg c;reg[30:0] count;//将个变量进行初始化initialbeginI<=0;J<=0;f<=0;code0<=1;code1<=0;code2<=0;code3<=0;end//分频器的产生,可以调节交织器的频率大小always @(posedge clk)begincount=count+1;if(count==1)begincount=0;c=~c;endend//这里分两个部分,一是伪随机码的产生,二是交织码的产生always @(posedge c)begincode0<=1;code1<=1;code2<=1;code3<=0;if(code0|code1|code2|code3)begincode0<=code0^code3; //用模二加法产生反馈信号,产生伪随机码code1<=code0;code2<=code1;code3<=code2;endif(I==15) //循环机制的产生,用于产生4*4的数组beginI=0;f=~f;endelseI=I+1;if(J==3)beginJ=0;endelseJ=J+1;if(!f) //当第一个循环周期时,pn码按行写入A,同时B按列读出,但此时B里面的单元为都0,所以第一个循环begin //周期内,out(未交织)和waveout(交织后)输出均为0;A[I]<=code3;out<=B[I];if(I<4)waveout<=B[0+4*J];else if(I<8)waveout<=B[1+4*J];else if(I<12)waveout<=B[2+4*J];elsewaveout<=B[3+4*J];endelse // 第二个循环周期,pn码开始写入B,因为A在前面第一个周期已经写满(16个值),begin //A可以同时按行按列读出了,此时交织才正式开始。

目录一、实验目的 (3)二、设计要求与内容 (3)三、设计原理3.1总体设计方案 (3)3.1.1设计思路 (3)3.1.2总电路框图 (3)3.2各模块设计方案及原理3.2.1抢答器 (3)3.2.2计时器 (5)四、电路仿真4.1倒计时电路 (6)4.2抢答器 (6)五、实验结果与析 (7)六、主要元器件 (8)七、实习总结 (9)四路数字抢答器一、实验目的结合我们所学的有关电子线路课程,综合实现四路抢答器的设计。

二、设计要求与内容(1)要求实现ABCD四路抢答器的设计,每一组都具有独立的抢答按键,要求某路抢答后,其他三路抢答无效;(2)某路抢答信号到达后,指示该路已抢答的独立灯发光,发出提示音,并用数码管显示抢答的组号(以ABCD表示);(3)裁判桌上的公共通道号显示(以ABCD表示);(4)抢答时间的定时与报警,具体实现可自拟。

扩展内容:①记录某路的抢答次数或抢到得次数;②记录某路的分数;③路数的扩展。

三、设计原理及过程3.1总体设计方案3.1.1设计思路①要准确判断出第一抢答者的信号并将其锁存,实现这一功能可选择使用触发器或锁存器等。

得到第一信号后其他组的抢答信号无效,并且第一信号在主持人发出抢答命令后才有效。

②第一信号发出后,用编码、译码及数码显示电路显示抢答者的组别,发光二极管亮。

③主持人按下抢答按钮后,开始30秒倒计时,在此时间内抢答有效,若30秒内无人抢答,主持人清零后开始新一轮抢答。

3.1.2总电路框图3.2各模块设计方案及原理3.2.1抢答电路抢答电路实现选手抢答并锁存,同时发光二极管发光,数码显示。

使用优先编码器74LS148和锁存器74LS279来完成。

该电路主要完成两个功能:一是分辨出选手按键的先后,并锁存优先抢答者的编号,同时译码显示电路显示编号(采用七段数字数码显示管);二是禁止其他选手按键,其按键无效。

工作过程:开关S 处于清除端时,RS 触发器R 、S 端均为0,使译码器74LS48的优先编码工作标志端位0,处于工作状态。

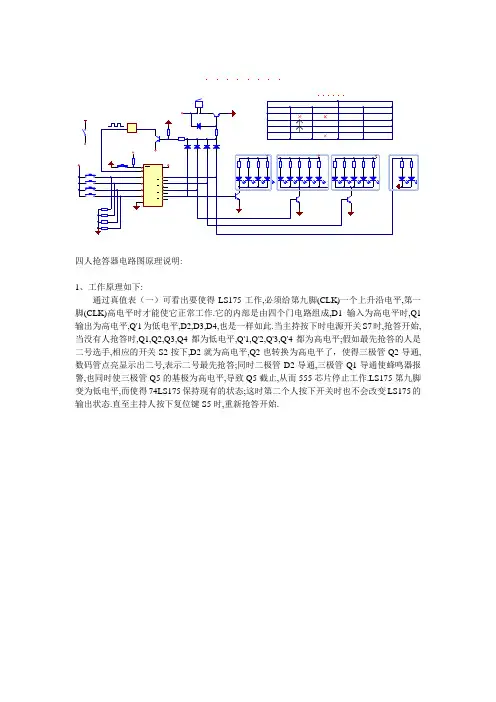

四路智力竞赛抢答器制作根据下图完成下列工作任务:1.参照下图正确组装电路;2.电路组装完毕后,对电路进行相关电路参数测量;3.根据检测结果分析故障原因,排除故障。

图7-19四路智力竞赛抢答器电路原理图操作步骤1.准备工具2.核对元器件数量与型号1)用万用表检测电阻阻值是否正确2)用万用表检测发光二极管极性用万用表R×10k档,当正向接入时,能使发光二极管导通,如果万用表指针向右偏转过半,同时二极管发出微弱的光电,表明正向介入,此时黑表笔为正极,红表笔为负极。

否则发光二极管存在质量问题。

3)用万用表检测按钮开关接点4)检测74LS175集成芯片正确判定74LS175集成芯片引脚功能与排列顺序。

图7-20集成芯片74LS175引脚及排列用万用表鉴别74LS175集成芯片质量方法:下表是74LS175集成芯片逻辑功C L R入,1Q、2Q、3Q、4Q用万用表测,应为0.4V以下,即逻辑0;输出端Q1、Q2、4用万用表表测用为3.6V左右,即逻辑1,是高电平输出。

若将输入端Q3、Q1D接地,CLR端悬空(逻辑1),CLK端由接地到悬空的瞬间,用万用表测输出端1Q、2Q应在0.4V以下(即逻辑0),用万用表测输出端Q1、Q2应为3.6V左右(即逻辑1),是高电平输出,则此集成块合格。

5)检测74LS20芯片74LS20芯片引脚及排列如下图所示。

图7-21集成芯片74LS20引脚及排列74LS20芯片测试方法同74LS175,根据它的逻辑功能来测量。

74LS20芯片就可判断其逻辑功能能是否正常。

6)检测74LS04芯片74LS04芯片引脚及排列如下图所示。

图7-22集成芯片74LS04引脚及排列74LS043.元器件布局本次任务采用万能板进行安装,首先应该在万能板上进行元器件布局。

元器件布局之前应该读懂电路原理图,在确认电气原理图没有问题之后进行元器件布局。

元器件布局应合理,接线尽可能少和短,确保电气性能优良。

基于单片机实现智能4路抢答器的设计报告惠州学院数字电子技术课程设计说明书题目:基于单片机(89C52)的四人抢答器系部:电子科学系班级:09级电信二班学生姓名:学号:指导教师:2011年12月29日智能四路抢答器目录一、前言 (2)二、方案设计 (2)1、方案比较 (2)2、系统总体设计方案与实现框图 (3)三、理论分析 (3)四、电路设计 (4)1、按键部分 (4)2、显示部分 (5)3、总原理图 (6)五、软件流程图模块 (7)六、结论 (8)七、程序 (9)一、前言本设计要求能够在主持人按下开始键后,四个参赛者开始抢按自己的按键,谁的按键先按下,谁面前的灯就会亮并且有相应的提示,当参赛者耗时太多时又会有相应的提示。

根据设计的要求,本系统采用独立式按键,通过单片机不停的扫描按键来控制LED灯和蜂鸣器,并用定时器T0、T1来定超时的时间,其中抢答定时时间可以由主持人随意的修改。

当超时的时候让蜂鸣器响和点亮相应的LED灯(T0用于参赛者回答问题的定时,T1用于参赛者抢答时间的选定)。

二、方案设计1、方案比较(1)、总体设计方案一:采用可编程I/O口扩展芯片81558155作为单片机的扩展接口能实现很多功能,但是这个系统并不复杂,用8155会浪费很多的资源,而且8155要用P0和P2端口作为地址线对它进行读写,这样不仅浪费端口还使得编程变的复杂。

从节省资源和简化编程的角度考虑,放弃了此方案。

方案二:直接采用AT89C51单片机直接用单片机不仅编程被简化,还有效的利用了各个端口。

8051单片机的资源完全够这个系统的要求。

所以最终选择了此方案。

(2)、模块方案一:采用4*4矩阵键盘此种键盘是常用的按键扫描方法,但是本系统只需要六个按键,这样就会浪费十个,而且矩阵按键扫描要送数读数,对于编程很复杂,最终放弃了此方案。

方案二:采用独立式键盘本系统只要8个按键就可以,用独立式键盘不仅节省端口还使编程变得简单。

题目:四路智能抢答器电路班级:姓名:学号:小组成员:日期:2010-12-26目录一、设计目的 (3)二、设计要求 (3)三、方案论证与比较 (4)四、设计原理 (5)五、硬件制作与调试 (6)六、设计小结 (7)七、参考书目 (8)一、设计目的1、通过课程设计,对数字逻辑的基本内容有进一步的了解,特别是时序逻辑电路的设计。

能把所学到的数字逻辑理论知识进行实践,操作。

2、提高动手能力的同时对常用的集成芯片有一定的了解,在电路设计方面有感性的认识。

3、另外还要掌握电路原理和分析电路设计流程,每个电路的设计都要有完整的设计流程。

这样才能在分析电路有良好的思路,便于找出错的原因。

二、设计要求设计一个4路智能抢答器,具体设计要求如下:1、抢答器同时供4名选手,分别用4个按钮S1~S4表示。

2、设置一个系统清除和抢答控制开关S,该开关由主持人控制。

3、抢答器具有锁存与显示功能。

即选手按动按钮,锁存相应的编号,并在LED数码管上显示,同时二极管发出红灯提示。

选手抢答实行优先锁存,优先抢答选手的编号一直保持到主持人将系统清除为止。

4、抢答器具有定时抢答功能,且一次抢答的时间由主持人设定(如25秒)。

当主持人启动“开始”键后,定时器进行减计时。

5、选手在设定的时间内进行抢答,抢答有效,定时器停止工作,显示器上显示选手的编号和抢答的时间,并保持到主持人将系统清除为止。

6、如果定时时间已到,无人抢答,本次抢答无效,系统报警灯并禁止抢答,定时显示器上显示00。

7、抢答器具有暂停功能,当暂停时选手禁止抢答。

三、方案论证与比较设计的方案有以下几种:1、电路选用优先编码器74LS148 、锁存器74LS373 和74LS48译码器来完成。

该电路主要完成两个功能:一是分辨出选手按键的先后,并锁存优先抢答者的编号,同时译码显示电路显示编号;二是禁止其他选手按键,其按键操作无效。

再由555定时器秒脉冲产生电路、十进制同步加减计数器74LS192减法计数电路、74ls47译码器和2个7段数码管即相关电路组成。

基于STM32的多路抢答器设计与制作Design and Make of Multiple Answering Device onSTM3内容摘要抢答不仅仅需要参与者,还需要裁判,而裁判的作用是整个过程中是最终要的,他是影响结果的一个很重要因素,在古代,裁判只能通过肉眼去判断谁先抢答,但是人的肉眼的能力是有限的,很难精准的得出正确的选择,如果出现相差不大的情况,裁判很容易就会错判,导致结果的错误而改变。

而随着时代的不断变化,人们也想到很多去增加判断的精确度的方法,如敲锣,打鼓等都被应用到抢答中,这时候裁判的判断点又多了一个,但是这还不够精确,错判的几率相对来说还是有些大,而随着时代的变更发展,敲锣打鼓和肉眼已经不能够满足人们对于抢答精准的需求,随着发展,以按键配合二极管为主的抢答器就出现了,它从一开始的单路按键功能简单到多路按键功能复杂,然后慢慢出现以单片机为核心的多路抢答器,再蜕变成从有线连接到无线连接的多路抢答器,从结构复杂功能简单到结构简单功能繁多,它一直在随着时代的发展而在不断改进中,人们对于抢答器的功能的要求增长越来越高,抢答器的更新换代也越来越快,它的功能和精准度也就变得越来越多。

本文是基于STM32的多路抢答器的设计与制作,它支持多线路抢答,可以精确判断哪一路先完成抢答,人可以通过1602LCD液晶显示,LED灯,数码管看到哪一个是第一抢答者,抢答者面前的灯会亮起,LED显示屏会显示抢答者的信息,数码管会显示可回到倒计时,在裁判进行复位前全部抢答者不能进行操作;当回答时间快要结束时,蜂鸣器会发出警告和LED灯的闪烁来提醒参赛者和裁判时间快结束了,当时间到达后,抢答者面前的灯将会熄灭,这时候裁判可通过按下复位键,让抢答者们可以重新操作,进行下一轮抢答。

关键词:多路抢答器、STM32、1602液晶显示、LED灯、按键AbstractResponding not only requires participants, but also the referee, and the role of the referee is the final one in the whole process. He is a very important factor affecting the result. In ancient times, the referee can only judge who responded first by the naked eye, but the person The ability of the naked eye is limited, it is difficult to accurately draw the correct choice, if there is not much difference, the referee will easily misjudge, leading to wrong results and change. With the continuous changes of the times, people also think of many ways to increase the accuracy of judgments, such as knocking gongs, playing drums, etc., are applied to the answer. At this time, the referee has one more judgment point, but this is not accurate enough. The probability of misjudgment is still relatively large, and with the development of the times, drumming and drumming and the naked eye have been unable to meet people's demand for accurate answering. With the development, answering devices based on buttons and diodes are mainly used. Appeared, it was from the beginning of thesingle-channel key function is simple to multi-channel key function is complex, and then slowly appeared multi-channel answering device with the single-chip as the core, and then transformed into a multi-channel answering device from wired connection to wireless connection, from The structure is complicated and the function is simple to the structure is simple and has many functions. It has been constantly improving with the development of the times. The requirements for the function of the answering device are growing higher and higher, and the updating and updating of the answering device are getting faster and faster. The functions and precision of the UPS become more and more.This article is based on the design and production of STM32multi-channel answering device, it supports multi-line answering, you can accurately determine which way to complete the answering first, people can see which one is the first responder through 1602LED LCD display, LED lights, digital , The light in front of the responder will light up, the LED display will show the information of the responder, the digital tube will show that it can return to the countdown, and all the responders cannot operate before thereferee resets; A warning and a flashing LED light will be issued to remind the contestants and the referee that the time is almost over. When the time is up, the light in front of the responder will go out. At this time, the referee can press the reset button to allow the responders to re-operate For the next round of rush answers.Key words:Multi-channel answering device, STM32, 1602 LCD display, LED lights , buttons目录1.绪论 (1)1.1多路抢答器的应用 (1)1.2多路抢答器的发展前景 (1)1.3多路抢答器的选题目的和意义 (1)1.4多路抢答器存在的问题 (2)2.总体设计方案 (3)2.1多路抢答器的基本系统设计 (3)2.2多路抢答器的主要功能 (3)2.3多路抢答器优点 (3)2.4多路抢答器的架构程序框图 (4)3.元器件选型和原理图设计 (5)3.1 元器件的选型 (5)3.2多路抢答器的原理图设计 (5)4.系统焊接和调试 (15)4.1多路抢答器系统的焊接 (15)4.2多路抢答器系统的焊接调试 (15)5.软件 (16)5.1软件介绍 (16)5.2代码思路架构 (16)5.3代码编程 (17)5.4代码调试 (19)6.多路抢答器的调试 (20)6.1单路调试 (20)6.2多路调试 (20)6.3系统是否可以进行锁定和倒计时报警 (20)6.4系统是否可以通过按钮复原 (21)6.5系统的错误与解决方法 (21)7.项目总结 (22)致谢 (23)1.绪论1.1多路抢答器的应用抢答的模式其实在古时候就已经出现,古人会通过抢答来作为竞赛,考试,决策,争夺等事情得到结果的一种重要方式,这个方式的实现就需要作为评判标准的一种工具,那就是抢答器。