WIRE的用法

- 格式:ppt

- 大小:4.14 MB

- 文档页数:43

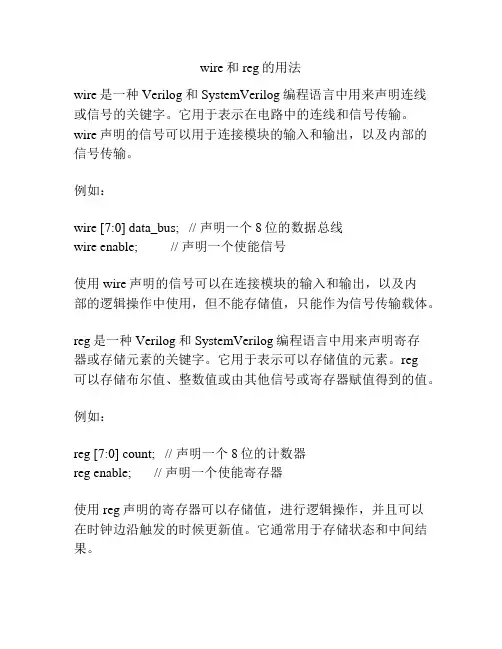

wire和reg的用法

wire是一种Verilog和SystemVerilog编程语言中用来声明连线或信号的关键字。

它用于表示在电路中的连线和信号传输。

wire声明的信号可以用于连接模块的输入和输出,以及内部的信号传输。

例如:

wire [7:0] data_bus; // 声明一个8位的数据总线

wire enable; // 声明一个使能信号

使用wire声明的信号可以在连接模块的输入和输出,以及内

部的逻辑操作中使用,但不能存储值,只能作为信号传输载体。

reg是一种Verilog和SystemVerilog编程语言中用来声明寄存

器或存储元素的关键字。

它用于表示可以存储值的元素。

reg

可以存储布尔值、整数值或由其他信号或寄存器赋值得到的值。

例如:

reg [7:0] count; // 声明一个8位的计数器

reg enable; // 声明一个使能寄存器

使用reg声明的寄存器可以存储值,进行逻辑操作,并且可以

在时钟边沿触发的时候更新值。

它通常用于存储状态和中间结果。

1。

With the help of 在~~帮助下under the leadership / care of 在~~领导/关心下2。

be strict with sb。

对~人要求严格be strict in sth。

对~事要求严格3。

at present=at the present time 目前for the present 暂时4。

in the sun/sunshine 在阳光下under the sun 在世界上5. lie in 位于~~之内lie on 同~~接壤lie to 位于~~之外6。

at least 至少in the least 丝毫,一点7. by name 名叫in the name of 以~~名义8。

in the air 空中,在流传on the air 播出9. in the way 挡路,障碍,用~~方法in a way 在某点上,在某种程度上get one’s own way to do 随心所欲give way 让步,屈服lose one’s way 迷路by the way 顺便说一下on one’s way to 在去~~的路上Come this way 这边走10。

at the corner 在拐角处(外角)in the corner 在角落里(内角)on the corner 在角落上(外角上)11。

judge by / from 根据~~来判断judge for oneself 由某人自己来判断12。

at the end (of) 在~~结束时at the beginning of 在~~开始时at the back of 在~~背后,支持at the age of ~~岁时at the foot of 在~~脚下at the bottom of 在~~底部at the top of 在~~顶上at/on the edge of 在~~边上13。

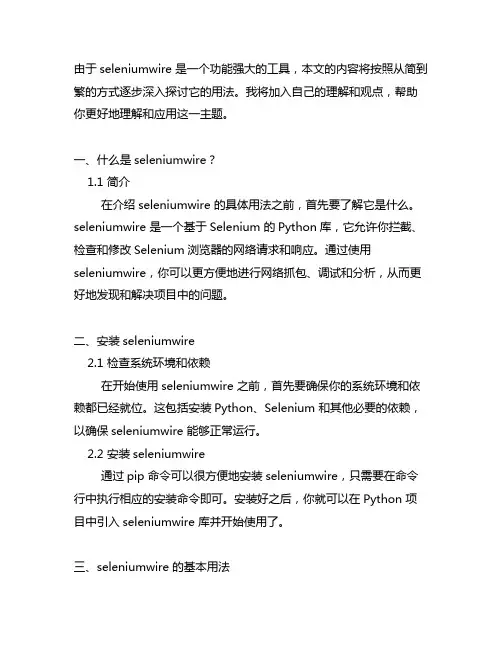

由于seleniumwire 是一个功能强大的工具,本文的内容将按照从简到繁的方式逐步深入探讨它的用法。

我将加入自己的理解和观点,帮助你更好地理解和应用这一主题。

一、什么是seleniumwire?1.1 简介在介绍seleniumwire 的具体用法之前,首先要了解它是什么。

seleniumwire 是一个基于Selenium 的Python库,它允许你拦截、检查和修改Selenium浏览器的网络请求和响应。

通过使用seleniumwire,你可以更方便地进行网络抓包、调试和分析,从而更好地发现和解决项目中的问题。

二、安装seleniumwire2.1 检查系统环境和依赖在开始使用seleniumwire 之前,首先要确保你的系统环境和依赖都已经就位。

这包括安装Python、Selenium 和其他必要的依赖,以确保seleniumwire 能够正常运行。

2.2 安装seleniumwire通过pip 命令可以很方便地安装seleniumwire,只需要在命令行中执行相应的安装命令即可。

安装好之后,你就可以在Python 项目中引入seleniumwire 库并开始使用了。

三、seleniumwire 的基本用法3.1 拦截网络请求通过seleniumwire,你可以拦截浏览器发出的网络请求,包括请求头、请求体、响应头和响应体等信息。

这为你提供了极大的灵活性,可以在请求发送之前或者响应返回之后对其进行修改、记录或者分析。

3.2 修改网络请求除了拦截网络请求外,seleniumwire 还允许你修改请求的参数、头部信息等,以便模拟不同的网络环境和测试用例。

这对于一些需要在特定网络情况下进行测试的场景非常有帮助。

四、高级用法和技巧4.1 自定义代理通过seleniumwire,你可以自定义代理服务器来拦截浏览器的网络请求,这为你提供了更高级和灵活的网络管理能力。

你可以使用自己搭建的代理服务器来对请求和响应进行定制化处理。

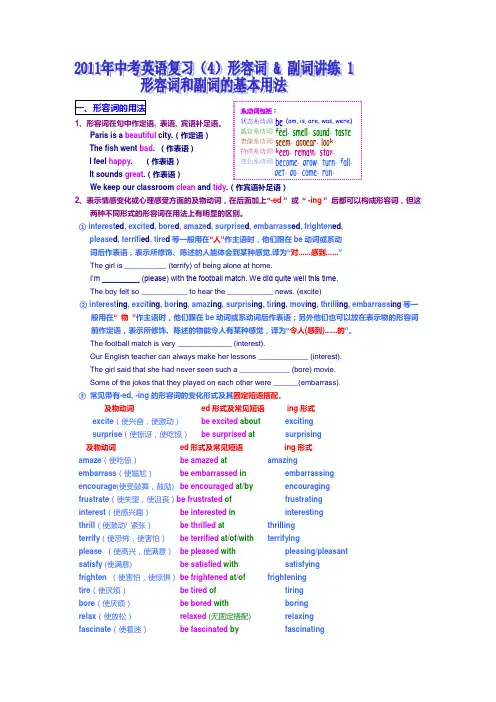

1、形容词在句中作定语, 表语, 宾语补足语。

Paris is a beautiful city.(作定语)The fish went bad. (作表语)I feel happy. (作表语)It sounds great.(作表语)We keep our classroom clean and tidy.(作宾语补足语)2、表示情感变化或心理感受方面的及物动词,在后面加上“-ed”或“ -ing”后都可以构成形容词,但这两种不同形式的形容词在用法上有明显的区别。

① interest ed, excite d, bore d, amaze d, surprise d, embarrass ed, frighten ed,please d, terrifi ed, tire d等一般用在“人”作主语时,他们跟在be动词或系动词后作表语,表示所修饰、陈述的人能体会到某种感觉,译为“对......感到......”The girl is __________(terrify) of being alone at home.I’m _________ (please) with the football match. We did quite well this time.The boy felt so ___________to hear the ___________ news. (excite)② interest ing, excit ing, bor ing, amaz ing, surpris ing, tir ing, mov ing, thrill ing, embarrass ing等一般用在“物”作主语时,他们跟在be动词或系动词后作表语;另外他们也可以放在表示物的形容词前作定语,表示所修饰、陈述的物能令人有某种感觉,译为“令人(感到)......的”。

The football match is very _____________ (interest).Our English teacher can always make her lessons ____________ (interest).The girl said that she had never seen such a ____________ (bore) movie.Some of the jokes that they played on each other were ______(embarrass).③常见带有-ed, -ing的形容词的变化形式及其固定短语搭配。

Verilog是一种硬件描述语言,用于描述数字电路的行为和结构。

在Verilog中,wire和reg是两种不同的数据类型,用于声明变量和信号。

它们在硬件描述中有着不同的用途和特性,下面将逐一介绍它们的用法。

一、wire的用法1. wire是一种连续赋值的数据类型,用于声明线性网络中传输的数据信号。

它可以用于描述连续赋值逻辑,例如门级电路或组合逻辑电路。

2. wire声明的变量可以直接连接到门或其他逻辑元件的输出端,用于传输信号。

它具有无限电流容量和一定的延迟,适用于逻辑连线和数据传输。

3. 在Verilog中,wire类型的变量可以用于描述多个逻辑门的输出连接,形成连续的逻辑网络。

这种连续的信号传输方式适合于组合逻辑电路或数据通路的描述。

4. wire类型的信号在仿真和综合时会被视为连续赋值的信号,具有连续事件敏感的特性。

它在逻辑综合时会被映射为硬件电路中的连线或连线段,并具有一定的电气特性。

5. 在Verilog的模块中,通过wire声明的变量可以用于模块的端口连接和内部信号传输。

它可以与其他wire类型的信号直接相连,用于数据传输和逻辑连接。

二、reg的用法1. reg是一种寄存器类型的数据类型,用于声明存储器中的寄存器或寄存器堆。

它可以用于描述时序赋值逻辑,例如寄存器、触发器或时序逻辑电路。

2. reg声明的变量可以存储时序逻辑元件的输出信号,用于存储状态或数据。

它具有有限的存储容量和存储器延迟,适用于状态存储和时序逻辑的描述。

3. 在Verilog中,reg类型的变量可以用于描述寄存器存储器、寄存器堆或时序逻辑电路中的状态变量。

这种离散的信号存储方式适合于状态机、定时器或计数器的描述。

4. reg类型的信号在仿真和综合时会被视为时序赋值的信号,具有时钟事件敏感的特性。

它在逻辑综合时会被映射为硬件电路中的寄存器或存储器单元,并具有存储器控制的特性。

5. 在Verilog的模块中,通过reg声明的变量可以用于存储器端口连接和状态存储。

seleniumwire用法-回复SeleniumWire用法SeleniumWire是针对Selenium的一个增强库,它提供了一个简单但强大的接口,可以对浏览器的网络流量进行控制和修改。

这使得开发人员能够更好地测试和控制Web应用程序,并进行更深入的网络流量分析。

本文将一步一步地介绍SeleniumWire的用法,并提供示例代码和说明。

第1步:安装SeleniumWire和相关依赖首先,我们需要安装SeleniumWire和其依赖。

您可以使用Python的包管理工具pip来安装它们。

在命令行中运行以下命令来安装SeleniumWire和Selenium:pip install seleniumwirepip install selenium第2步:导入库和驱动器接下来,我们需要导入SeleniumWire的包和Selenium的驱动器。

请在你的Python脚本中添加以下导入语句:pythonfrom seleniumwire import webdriverfrom selenium.webdriver.chrome.service import Servicefrom selenium.webdriver.chrome.options import Options这些导入语句将允许我们使用SeleniumWire的功能,并设置Chrome 驱动器的选项。

第3步:配置选项和创建驱动器在创建WebDriver对象之前,我们还需要进行一些配置。

我们可以使用Selenium的Options类来配置Chrome驱动器的选项。

以下是一个示例代码段,显示了如何配置Chrome驱动器的SeleniumWire选项:python# 设置Chrome选项options = Options()# 使用SeleniumWiredriver =webdriver.Chrome(service=Service("path/to/chromedriver"), options=options)您需要将"path/to/chromedriver"替换为您计算机上的实际路径。

fpga里的wire用法FPGA(Field-Programmable Gate Array)是一种可编程逻辑芯片,具有动态可重构的性能,可以实现多种应用。

FPGA里面的wire是一种重要的基本元素,可以用于实现信号传输并连接多个FPGA模块。

本文将详细介绍FPGA里的wire 用法,并逐步解释wire的工作原理和常见应用场景。

一、FPGA中wire的定义Wire在FPGA里面通常被描述为一种信号线,用于连接不同的电气单元和设备。

Wire可以看作是一种虚拟电线,通过模拟电路中的导线来连接FPGA中各模块之间的信号路径,使得信号能够被正确地传递。

Wire可以连接FPGA中的各种模块,如逻辑单元、存储器单元、时钟源等等,用于实现可编程逻辑电路的运算和控制功能。

Wire是FPGA里面最常用的数据类型之一,也是实现可编程逻辑电路的核心元素之一。

二、wire的声明和初始化在FPGA里面,wire的声明和初始化非常简单,只需要使用特定的语法进行声明,即可创建一个空的wire变量。

一般来说,wire变量的声明是通过在代码中使用wire关键字实现的。

例如:verilogwire a, b, c; 声明三个wire变量在声明之后,wire变量就可以连接到其他模块的输入端或输出端,用于实现数据传输。

例如,可以通过以下方式将信号a连接到逻辑模块的输入端:verilogand_gate U1 ( .a(a), .b(b), .c(c) ); 使用wire变量连接到AND逻辑门输入端在上面的代码中,我们使用wire变量a、b和c来连接到逻辑门U1的三个输入端口。

这样,当输入a和b都为1时,输出端口c将会为1。

三、wire的应用场景1. 连接逻辑单元将wire连接到逻辑单元的输入端口或输出端口是FPGA中wire最常见的应用场景之一。

这种应用方式可以实现不同模块之间的数据传输和运算,如将信号从一个模块输出到下一个模块的输入。

verilog中的wire用法

Verilog中的wire是一种数据类型,用于连接模块中的各个部分。

它可以被看作是一种电线或者电缆,用于传输信号。

在Verilog中,wire的用法如下:

1. 连接模块中的各个部分

wire可以被用来连接模块中的各个部分,比如将一个模块的输出连接到另一个模块的输入。

这种连接通常是通过模块的端口完成的,wire可以在模块的端口定义中使用。

2. 用于信号传输

wire可以用于传输信号,比如将一个模块的输出信号传输到另一个模块的输入端口。

这种传输通常是通过wire来完成的。

3. 用于中间信号传输

wire也可以用于中间信号传输,比如将一个模块的输出信号传输到另一个模块的中间信号。

这种传输通常是通过wire来完成的。

4. 用于连接多个模块

wire可以用于连接多个模块,比如将一个模块的输出信号连接到多个模块的输入端口。

这种连接通常是通过wire来完成的。

5. 用于连接多个信号

wire可以用于连接多个信号,比如将多个模块的输出信号连接到一个模块的输入端口。

这种连接通常是通过wire来完成的。

总之,wire是Verilog中非常重要的一种数据类型,它可以用于连接模块中的各个部分,传输信号,连接多个模块和连接多个信号。

Arduino的Wire用法1. 简介Arduino是一种开源电子平台,用于构建各种交互式项目。

它使用简单的硬件和软件,非常适合初学者和专业人士。

Wire库是Arduino的标准库之一,用于实现I2C (Inter-Integrated Circuit)通信协议。

本文将介绍Wire库的用法以及如何使用它进行I2C通信。

2. I2C通信协议I2C是一种串行通信协议,用于在多个设备之间进行数据传输。

它由两根线组成:SDA(Serial Data Line)和SCL(Serial Clock Line)。

SDA线用于数据传输,SCL线用于时钟同步。

每个设备都有一个唯一的地址,用于在总线上进行通信。

I2C通信协议支持多主机和多从机的架构。

主机是发起通信的设备,从机是接收和响应通信的设备。

主机负责生成时钟信号以及发送和接收数据,从机只能在主机的请求下发送和接收数据。

3. Wire库的引入在Arduino中使用Wire库进行I2C通信,需要引入Wire库。

可以通过在代码的顶部添加以下语句来实现:#include <Wire.h>4. Wire库的基本用法4.1 初始化在使用Wire库之前,需要初始化I2C总线。

可以在setup()函数中添加以下语句来实现:void setup() {Wire.begin();}4.2 主机发送数据主机通过调用Wire.beginTransmission(address)方法开始向从机发送数据。

address参数是从机的地址。

然后,可以使用Wire.write(data)方法将数据写入发送缓冲区。

最后,通过调用Wire.endTransmission()方法将数据发送给从机。

以下是一个例子,演示如何向从机发送一个字节的数据:void loop() {Wire.beginTransmission(8); // 发送给地址为8的从机Wire.write(42); // 发送数据Wire.endTransmission(); // 发送数据delay(1000);}4.3 从机接收数据从机通过调用Wire.onReceive()函数来接收主机发送的数据。

wiresocks用法wiresocks是一款非常强大且常用的网络工具,它被广泛应用于网络安全领域。

本文将详细介绍wiresocks的用法,并一步一步地回答有关该工具的各种问题。

第一部分:什么是wiresocks?wiresocks是一个基于SOCKS5代理的网络工具,其主要作用是加密和转发网络流量。

它使用了一种称为"数采劫持"(data tethering)的技术,通过在数据包的包头和包尾插入特定的数据,使得网络流量在传输过程中变得不可见和不可辨识。

这种特性使得wiresocks极其适用于绕过网络审查和访问限制的场景,例如在某些国家被封锁的网站、绕过防火墙等。

第二部分:wiresocks的安装与配置1. 安装wiresocks首先,你需要从wiresocks的官方网站或开源项目中下载wiresocks的安装包。

根据你的操作系统,选择合适的版本。

2. 配置wiresocks安装完成后,需要进行一些基本配置。

在配置文件中,你需要设置服务器地址、端口号、密码以及其他一些可选项,以满足你的具体需求。

这些配置可以通过命令行参数或者编辑配置文件来完成。

3. 运行wiresocks一切准备就绪后,你可以运行wiresocks并开始享受其提供的服务。

通过命令行运行"wiresocks"命令即可启动wiresocks并监听指定的端口。

你也可以将其配置为在系统启动时自动运行。

第三部分:wiresocks的功能和用途1. 加密网络流量wiresocks使用加密技术来加密网络流量,从而防止第三方窃取敏感信息。

这使得你的网络连接更加安全和隐私。

2. 绕过网络审查和限制wiresocks的主要优势之一是可以帮助用户绕过网络审查和访问限制。

它可以将网络流量转发到其他国家或地区的服务器,并通过其代理功能来实现访问被封锁的网站。

3. 提高网络速度和稳定性在某些情况下,wiresocks可以提供更快的网络连接速度和更稳定的网络连接。

千里之行,始于足下。

Verilog中 reg和wire 用法和区别以及always和assign的区别在Verilog中,`reg`和`wire`是用来声明信号类型的关键字。

1. reg:- `reg`是寄存器类型,在时序逻辑电路中使用,常用于存储和传输数据。

- `reg`可以保存过去的值,并且在每个时钟周期内更新。

- 在`always`块中使用`reg`类型来表示存储信号的状态。

2. wire:- `wire`是线网类型,在组合逻辑电路中使用,用于连接和传输信号。

- `wire`用于连接不同的模块、输入和输出端口之间的信号传输。

- `wire`不能保存过去的值,只用于传输当前的信号值。

3. always:- `always`块是Verilog中用来描述时序逻辑的结构。

- `always`块可以用于检测时钟信号、状态转换以及状态更新。

- `reg`类型通常用于存储状态变量,在`always`块中进行更新和控制。

4. assign:- `assign`语句用于描述组合逻辑的连接关系。

- `assign`语句将一个表达式连接到一个`wire`类型的信号上。

- `assign`语句在时序逻辑中是禁止使用的,只能用于连接组合逻辑。

区别:- `reg`用于时序逻辑,`wire`用于组合逻辑。

第1页/共2页锲而不舍,金石可镂。

- `reg`可以存储过去的值,在每个时钟周期内更新;`wire`只用于传输当前的信号值。

- `always`用于描述时序逻辑的行为,`assign`用于描述组合逻辑的连接关系。

- `always`块中使用`reg`类型,`assign`语句中使用`wire`类型。

机电的英文名词1. motor(名词):- 词性解释:可数名词。

- 意思:电动机;马达。

- 用法:通常用于描述各种机械设备中的动力装置。

- 近义词:engine。

- 双语例句:This motor is so powerful! It's like a little beast that can make my machine run like crazy.(这个电动机好强大!它就像一只小野兽,能让我的机器疯狂运转。

)2. generator(名词):- 词性解释:可数名词。

- 意思:发电机。

- 用法:用于产生电能的设备。

- 近义词:dynamo。

- 双语例句:The generator saved us when the power wentout. Man, it was a real lifesaver!(停电的时候发电机救了我们。

哇,它真是个救命稻草!)3. transformer(名词):- 词性解释:可数名词。

- 意思:变压器。

- 用法:改变电压的设备。

- 近义词:voltage converter。

- 双语例句:The transformer is like a magic box that can change the voltage. Isn't that amazing?(变压器就像一个魔法盒子,可以改变电压。

这难道不神奇吗?)4. circuit breaker(名词):- 词性解释:可数名词。

- 意思:断路器。

- 用法:在电路中起保护作用。

- 近义词:fuse。

- 双语例句:The circuit breaker kicked in just in time. Phew!That was a close one.(断路器及时跳闸了。

哎呀!好险啊。

)5. switch(名词):- 词性解释:可数名词。

- 意思:开关。

- 用法:控制电路通断。

- 近义词:toggle。

1、从仿真角度来说,HDL语言面对的是编译器,相当于使用软件思路,此时:wire对应于连续赋值,如assign;reg对应于过程赋值,如always,initial;2、从综合角度,HDL语言面对的是综合器,相当于从电路角度来思考,此时:wire型变量综合出来一般情况下是一根导线。

reg变量在always中有两种情况:(1)always @(a or b or c)形式的,即不带时钟边沿的,综合出来还是组合逻辑;(2)always @(posedge clk)形式的,即带有边沿的,综合出来一般是时序逻辑,会包含触发器(Flip-Flop)3、设计中,输入信号一般来说不能判断出上一级是寄存器输出还是组合逻辑输出,对于本级来说,就当成一根导线,即wire型。

而输出信号则由自己来决定是reg还是组合逻辑输出,wire和reg型都可以。

但一般的,整个设计的外部输出(即最顶层模块的输出),要求是reg输出,这比较稳定、扇出能力好。

4、Verilog中何时要定义成wire型?情况一:assign语句例如:reg a,b;wire out;......assign out = a & b;如果把out定义成reg型,对不起,编译器报错! 情况二:元件实例化时必须用wire型例如:wire dout;ram u_ram(.....out(dout);)wire为无逻辑连线,wire本身不带逻辑性,所以输入什么就的输出什么。

所以如果用always语句对wire变量赋值,对不起,编译器报错。

那么你可能会问, assign c = a & b; 不是对wire的赋值吗?并非如此,综合时是将 a & b综合成 a、b经过一个与门,而c是连接到与门输出线,真正综合出来的是与门&,不是c。

5、何时用reg、何时用wire?大体来说,reg和wire类似于C、C++的变量,但若此变量要放在begin...end之内,则该变量只能是reg型;在begin...end之外,则用wire型;使用wire型时,必须搭配assign;reg型可以不用。

verilog之wire和regverilog之wire和reg1、区别wire为线,reg为寄存器。

⾄少初期这两个名词的意思是这样的。

wire在电路设计中指代的就是某个点的逻辑值,⽽reg则指代某个寄存器输出的逻辑值。

这个理解可以覆盖⼤部分的使⽤。

⽽不在这⼀范围内的就是使⽤always写组合逻辑。

这时的reg具备的只有语法意义,⽽没有电路意义。

always块内要求使⽤reg类型,拓展了always的⽤法,但是降低了verilog与电路的对应性。

在端⼝声明中,wire是输⼊的唯⼀类型。

可以从电路来理解,reg变量只有存在被赋值的语句才有意义,如果使其作为模块的输⼊,那么这个reg变量就会需要在模块内写输⼊的赋值,显然不合理。

没有赋值的reg就是wire。

⾄于输出,则是可以选择reg和wire。

reg可以使⽤,是模块内有reg的赋值语句。

如果没有,编译器会警告然后将该端⼝在RTL视图中剥离。

好像⼀些编译器会直接删除这部分语句。

wire⾃然也可以。

wire在模块内肯定有连线。

同样,在激励⽂件中,reg作为其他模块的输⼊,也是基于要在激励⽂件中编写其他模块的输⼊。

输出则是默认wire类型。

这⾥主要防⽌模块输出为reg。

reg和reg在端⼝相连是⾮法的。

这⾥可能是考虑到reg变量的赋值只能在always等结构中,端⼝处显然不存在这⼀结构。

2、使⽤通过前⾯的总结可以看到使⽤中的结构是:源⽂件:module test(input wire a,output wire/reg b);//===========endmodule激励⽂件module test_tb;reg a_in;wire b_out;test U1(.a(a_in),.b(b_out));//////////////endmodule上层⽂件:module test_top(//////////////////);reg/wire a_in;wire b_outtest U2(.a(a_in),.b(b_out));endmodule⼩总结:在端⼝声明中,⼀定是reg数据向外输出,绝对不能出现数据向reg输⼊。

outweigh :[aut'wei]v.比... 重要, 比... 有价值例句与用法:1. On balance, his accomplishments outweigh his faults.权衡起来,他的成就要大于他的过失。

undesirable :[.ʌndi'zairəbəl]adj. 不受欢迎的, 不良的, 不合意的, 讨厌的n. 不受欢迎的人, 不良分子例句与用法:1. Faced with two equally undesirable alternatives.进退维谷,左右为难面临两种同样不受欢迎的选择2. She's a most undesirable influence.她是个专门不起好作用的人。

weed :[wi:d]n.杂草, 野草n.衣服,丧服vi.除草, 清除, 淘汰Eradicating :[i'rædi.keit][ 自动跳转自: eradicating ]vt.根除, 根绝,消灭例句与用法:1. They attempted to eradicate crime.他们力图根除罪恶。

2. Smallpox has almost been eradicated.天花几乎已经被消灭了。

suppress :[sə'pres]vt.镇压, 隐瞒, 压制, 止住, 禁止例句与用法:1. Something that serves to suppress, check, or eliminate.抑制物用来压制、控制或消除的事物2. The revolt was suppressed in a matter of hours.叛乱在几小时之内就镇压下去了。

3. Mr Baruch stated what he thought the best method of suppressing opium smoking and the people heartily entered into his views.巴鲁克先生讲述了他所认为的禁止抽鸦片烟的最好方法,大家都热烈赞同。

wire.newset的用法1.引言本文将介绍w ir e.ne w se t的使用方法及其在编程中的应用。

w i re.n ew se t是一个功能强大的工具,它可以帮助开发者更好地管理和操作数据集合。

2.什么是wir e.newse tw i re.n ew se t是一个用于创建数据集合的函数。

通过wi re.n e ws et函数,开发者可以方便地建立并操作各种类型的集合,如数组、列表、字典等。

3.创建数组使用wi re.n ew se t函数,我们可以轻松地创建一个数组。

下面是创建空数组和带有初始元素的数组的示例代码:```m ar kd ow nw i re.n ew se tm yA rra yw i re.n ew se tm yA rra y[1,2,3,4,5]```4.创建列表除了数组,w ir e.new s et还可以用来创建列表。

列表是一种有序集合,可以包含各种类型的元素。

下面是创建空列表和带有初始元素的列表的示例代码:```m ar kd ow nw i re.n ew se tm yL istw i re.n ew se tm yL ist["a pp le","b an ana","or an ge"]```5.创建字典字典是一种键值对的集合,通过w ir e.ne w s e t函数,我们可以创建一个字典。

下面是创建空字典和带有初始元素的字典的示例代码:```m ar kd ow nw i re.n ew se tm yD ictw i re.n ew se tm yD ict{"n am e":"Jo hn","a ge":30,"ci ty":"N ew Yo r k"}```6.操作集合w i re.n ew se t不仅可以用来创建集合,还可以对集合进行各种操作。