数字设计课件第七章时序逻辑设计原理

- 格式:ppt

- 大小:1.50 MB

- 文档页数:105

实验七时序逻辑电路设计一、实验目的1. 学习用集成触发器构成计数器的方法。

2. 熟悉中规模集成十进制计数器的逻辑功能及使用方法。

3. 学习计数器的功能扩展。

4. 了解集成译码器及显示器的应用。

二、实验原理计数器是一种重要的时序逻辑电路,它不仅可以计数,而且用作定时控制及进行数字运算等。

按计数功能计数器可分加法、减法和可逆计数器,根据计数体制可分为二进制和任意进制计数器,而任意进制计数器中常用的是十进制计数器。

根据计数脉冲引入的方式又有同步和异步计数器之分。

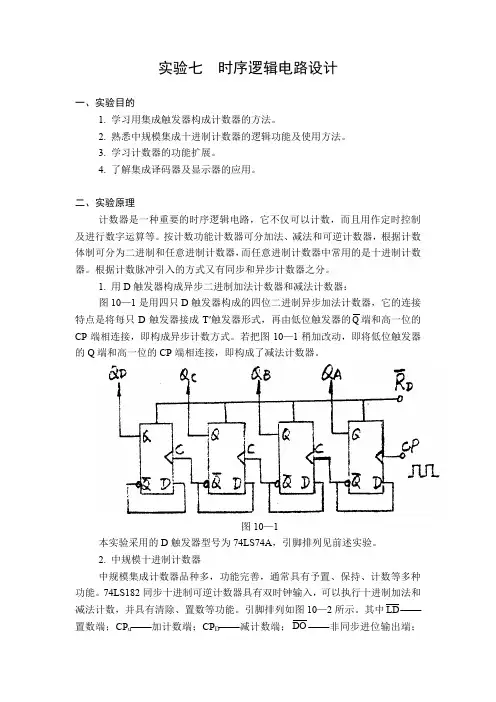

1. 用D触发器构成异步二进制加法计数器和减法计数器:图10—1是用四只D触发器构成的四位二进制异步加法计数器,它的连接特点是将每只D触发器接成T'触发器形式,再由低位触发器的Q端和高一位的CP端相连接,即构成异步计数方式。

若把图10—1稍加改动,即将低位触发器的Q端和高一位的CP端相连接,即构成了减法计数器。

图10—1本实验采用的D触发器型号为74LS74A,引脚排列见前述实验。

2. 中规模十进制计数器中规模集成计数器品种多,功能完善,通常具有予置、保持、计数等多种功能。

74LS182同步十进制可逆计数器具有双时钟输入,可以执行十进制加法和减法计数,并具有清除、置数等功能。

引脚排列如图10—2所示。

其中LD−−置数端;CP u−−加计数端;CP D−−减计数端;DO−−非同步进位输出端;CO−−非同步借位输出端;Q A、Q B、Q C、Q D−−计数器输出端;D A、D B、D C、D D−−数据输入端;CR−−清除端。

表10—1为74LS192功能表,说明如下:当清除端为高电平“1”时,计数器直接清零(称为异步清零),执行其它功能时,CR置低电平。

当CR为低电平,置数端LD为低电平时,数据直接从置数端D A、D B、D C、D D置入计数器。

当CR为低电平,LD为高电平时,执行计数功能。

执行加计数时,减计数端CP D接高电平,计数脉冲由加计数端Cp u输入,在计数脉冲上升沿进行842编码的十进制加法计数。

电子设计中的时序逻辑设计时序逻辑设计是电子设计中非常重要的一个部分,它主要涉及到在数字电路中对信号的时序进行控制和调整,以确保电路能够按照预定的顺序正确地工作。

在电子设备中,时序逻辑设计直接影响着整个系统的性能、稳定性和功耗等方面。

首先,时序逻辑设计需要考虑时钟信号的控制。

时钟信号是数字系统中非常关键的一个信号,它提供了同步的时序参考,确保各个部分能够同时工作。

在时序逻辑设计中,需要合理地设置时钟信号的频率、相位和占空比等参数,以保证整个系统的稳定性和可靠性。

其次,时序逻辑设计还涉及到时钟域的概念。

数字系统中的不同部分可能工作在不同的时钟频率下,这就涉及到时钟域之间的数据传输和同步。

在时序逻辑设计中,需要考虑时钟域之间的同步问题,采取合适的方法来确保数据的正确传输和处理。

此外,时序逻辑设计还需要考虑信号的延迟和时序约束。

在数字系统中,信号的传输会存在一定的延迟,这可能会导致时序不一致的问题。

因此,在时序逻辑设计中,需要对信号的延迟进行分析和优化,以满足系统的时序约束要求,确保数据的正确性和稳定性。

在实际的时序逻辑设计中,通常会采用时序分析工具来辅助设计。

时序分析工具可以帮助设计工程师对时序逻辑进行建模和仿真,提前发现潜在的时序问题,并进行相应的优化。

通过时序分析工具,可以有效地提高设计的可靠性和稳定性。

总的来说,时序逻辑设计在电子设计中具有非常重要的地位,它直接影响着数字系统的性能和稳定性。

设计工程师需要充分理解时序逻辑设计的原理和方法,合理地设计时钟信号控制、时钟域同步和信号延迟等,以确保系统能够按照预期的时序要求正确地工作。

通过良好的时序逻辑设计,可以提高数字系统的性能和可靠性,满足不同应用领域的需求。