串口通信FPGA实现

- 格式:doc

- 大小:459.34 KB

- 文档页数:12

带fifo的Uart发送器的FPGA实现FPGA使用Altera公司EP4C15F17C8N芯片,它的性能优越,支持大部分IP核使用。

常用它来学习NIOS II。

使用它实现带FIFO的串口。

首先,对uart的实现进行设计。

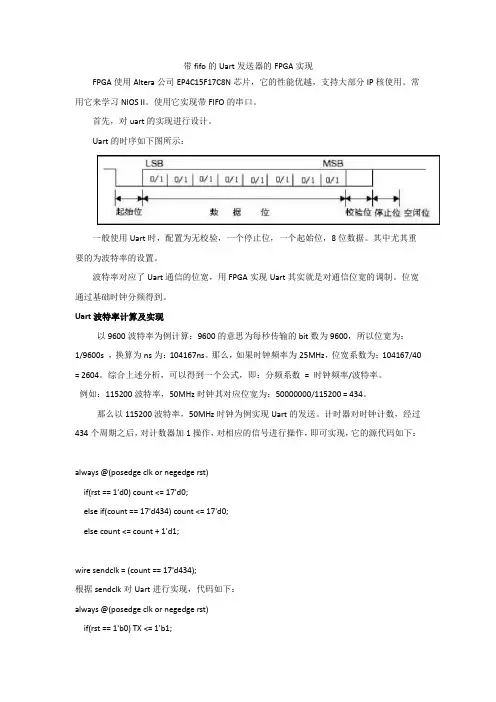

Uart的时序如下图所示:一般使用Uart时,配置为无校验,一个停止位,一个起始位,8位数据。

其中尤其重要的为波特率的设置。

波特率对应了Uart通信的位宽,用FPGA实现Uart其实就是对通信位宽的调制。

位宽通过基础时钟分频得到。

Uart波特率计算及实现以9600波特率为例计算:9600的意思为每秒传输的bit数为9600,所以位宽为:1/9600s ,换算为ns为:104167ns。

那么,如果时钟频率为25MHz,位宽系数为:104167/40 = 2604。

综合上述分析,可以得到一个公式,即:分频系数= 时钟频率/波特率。

例如:115200波特率,50MHz时钟其对应位宽为:50000000/115200 = 434。

那么以115200波特率,50MHz时钟为例实现Uart的发送。

计时器对时钟计数,经过434个周期之后,对计数器加1操作,对相应的信号进行操作,即可实现,它的源代码如下:always @(posedge clk or negedge rst)if(rst == 1'd0) count <= 17'd0;else if(count == 17'd434) count <= 17'd0;else count <= count + 1'd1;wire sendclk = (count == 17'd434);根据sendclk对Uart进行实现,代码如下:always @(posedge clk or negedge rst)if(rst == 1'b0) TX <= 1'b1;else if(FIFOempty == 1'b1) begin TX <= 1'b1; endelsecase(txcount)4'd0: TX <= 1'b0; //start bit is low4'd1: TX <= fifodata[0];4'd2: TX <= fifodata[1];4'd3: TX <= fifodata[2];4'd4: TX <= fifodata[3];4'd5: TX <= fifodata[4];4'd6: TX <= fifodata[5];4'd7: TX <= fifodata[6];4'd8: TX <= fifodata[7];4'd9: TX <= 1'b1; // stop bitsdefault: TX <= 1'b1 ;endcase它包含了一个有限状态机。

FPGA实现SPIFPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以实现不同的数字电路功能。

SPI(Serial Peripheral Interface)是一种同步串行通信协议,常用于连接外围设备和主控制器。

在本文中,将介绍如何使用FPGA实现SPI。

1.确定硬件资源:首先,需要确定FPGA中可用的IO资源。

SPI需要至少4个IO口,分别是主设备的时钟引脚(SCK),主设备输出的数据引脚(MOSI),主设备输入的数据引脚(MISO)和片选引脚(SS)。

根据所用的FPGA型号,可以查找对应的引脚定义。

2.确定SPI时序:SPI的时序是非常重要的,不同设备可能有不同的时序规范。

一般情况下,SPI的时序包括时钟下降沿数据采样、时钟上升沿数据输出等。

SPI的时序图可以在设备的数据手册中找到。

3. 编写SPI控制器:SPI控制器可以用硬件描述语言如VHDL或Verilog编写。

控制器的功能包括生成时钟、控制数据的发送和接收、以及处理片选信号。

a.时钟生成:SPI通信需要一个时钟信号来驱动数据的传输。

可以通过计数器模块来生成控制器的时钟信号。

计数器的频率一般是SPI时钟频率的若干倍。

b. 数据发送:对于主设备(Master),要发送数据给外设,可以使用移位寄存器(Shift Register)来存储要发送的数据。

可以使用计数器生成移位寄存器的时钟信号,通过串行输入数据,并在时钟的上升沿时将数据发送到MOSI引脚。

c.数据接收:对于主设备,要接收外设发送的数据,可以使用另一个移位寄存器来接收MISO引脚传输的数据。

可以使用计数器生成移位寄存器的时钟信号,通过MISO引脚接收数据,并在时钟的下降沿时将数据存储到接收寄存器。

d.片选控制:SPI通信需要一个片选信号来选择要与主设备通信的外设。

可以通过一个时序控制器实现片选信号的生成。

在与一些外设通信时,使能片选信号,否则禁用片选信号。

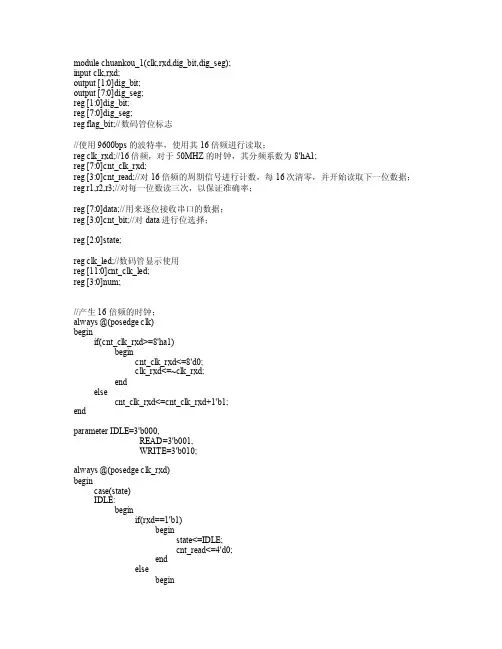

module chuankou_1(clk,rxd,dig_bit,dig_seg);input clk,rxd;output[1:0]dig_bit;output[7:0]dig_seg;reg[1:0]dig_bit;reg[7:0]dig_seg;reg flag_bit;//数码管位标志//使用9600bps的波特率,使用其16倍频进行读取;reg clk_rxd;//16倍频,对于50MHZ的时钟,其分频系数为8'hA1;reg[7:0]cnt_clk_rxd;reg[3:0]cnt_read;//对16倍频的周期信号进行计数,每16次清零,并开始读取下一位数据;reg r1,r2,r3;//对每一位数读三次,以保证准确率;reg[7:0]data;//用来逐位接收串口的数据;reg[3:0]cnt_bit;//对data进行位选择;reg[2:0]state;reg clk_led;//数码管显示使用reg[11:0]cnt_clk_led;reg[3:0]num;//产生16倍频的时钟;always@(posedge clk)beginif(cnt_clk_rxd>=8'ha1)begincnt_clk_rxd<=8'd0;clk_rxd<=~clk_rxd;endelsecnt_clk_rxd<=cnt_clk_rxd+1'b1;endparameter IDLE=3'b000,READ=3'b001,WRITE=3'b010;always@(posedge clk_rxd)begincase(state)IDLE:beginif(rxd==1'b1)beginstate<=IDLE;cnt_read<=4'd0;endelsebeginif(cnt_read<4'd15)begincnt_read<=cnt_read+1'b1;state<=IDLE;endelsebegincnt_read<=4'd0;state<=READ;endendendREAD:beginif(cnt_bit<=4'd7)beginif(cnt_read==4'd4)begincnt_read<=cnt_read+1'b1;r1<=rxd;state<=READ;endelse if(cnt_read==4'd9)begincnt_read<=cnt_read+1'b1;r2<=rxd;state<=READ;endelse if(cnt_read==4'd12)begincnt_read<=cnt_read+1'b1;r3<=rxd;state<=READ;endelse if(cnt_read==4'd15)beginif((r1==r2)&&(r2==r3)&&(r1==r3))begindata[cnt_bit]<=r3;//取值;state<=READ;cnt_read<=4'd0;cnt_bit<=cnt_bit+1'b1;endelsebegincnt_bit<=4'd0;state<=IDLE;cnt_read<=4'd0;endendelsebeginstate<=READ;cnt_read<=cnt_read+1'b1;endendelsebeginstate<=WRITE;cnt_bit<=4'd0;endendWRITE://此状态暂时未用;beginstate<=IDLE;enddefault:state<=IDLE;endcaseend//以下是数码管显示部分;parameter segcode0=8'b1100_0000;parameter segcode1=8'b1111_1001;parameter segcode2=8'b1010_0100;parameter segcode3=8'b1011_0000;parameter segcode4=8'b1001_1001;parameter segcode5=8'b1001_0010;parameter segcode6=8'b1000_0010;parameter segcode7=8'b1111_1000;parameter segcode8=8'b1000_0000;parameter segcode9=8'b1001_0000;parameter segcodea=8'h88;parameter segcodeb=8'h83;parameter segcodec=8'hc6;parameter segcoded=8'ha1;parameter segcodee=8'h86;parameter segcodef=8'h8e;always@(posedge clk)beginif(cnt_clk_led>=12'h9c3)begincnt_clk_led<=12'd0;clk_led<=~clk_led;endelsecnt_clk_led<=cnt_clk_led+1'b1;endalways@(posedge clk_led)beginflag_bit<=flag_bit+1'b1;case(flag_bit)1'b0:dig_bit<=2'b10;1'b1:dig_bit<=2'b01;endcaseendalways@(posedge clk_led)begincase(flag_bit)1'b0:num<=data[3:0];1'b1:num<=data[7:4];endcaseendalways@(num)begincase(num)4'd0:dig_seg<=segcode0;4'd1:dig_seg<=segcode1;4'd2:dig_seg<=segcode2;4'd3:dig_seg<=segcode3;4'd4:dig_seg<=segcode4;4'd5:dig_seg<=segcode5;4'd6:dig_seg<=segcode6;4'd7:dig_seg<=segcode7;4'd8:dig_seg<=segcode8;4'd9:dig_seg<=segcode9;4'd10:dig_seg<=segcodea;4'd11:dig_seg<=segcodeb;4'd12:dig_seg<=segcodec;4'd13:dig_seg<=segcoded;4'd14:dig_seg<=segcodee;4'd15:dig_seg<=segcodef;endcaseendendmodule。

FPGA和单片机串行通信接口的实现FPGA(Field-Programmable Gate Array)和单片机(Microcontroller)是两种常用的数字电子设备,它们在串行通信接口方面有不同的实现方式。

首先,我们需要了解串行通信是一种将数据以位的形式逐个传输的通信方式。

常见的串行通信协议包括UART(Universal Asynchronous Receiver/Transmitter)、SPI(Serial Peripheral Interface)和I2C (Inter-Integrated Circuit)等。

对于FPGA和单片机之间的串行通信,我们可以基于以下几种方式进行实现:1. UART:UART是一种常见的串行通信协议,可以实现全双工的通信。

在FPGA和单片机之间建立UART通信,需要在FPGA中实现UART模块,并将其与单片机的UART接口连接。

在FPGA中,我们可以使用硬件语言(如Verilog或VHDL)来实现UART模块,该模块负责将FPGA内部的数据通过UART协议进行封装和解封装。

单片机与FPGA之间通过TX(发送)和RX (接收)引脚建立连接。

单片机可以通过串口发送数据给FPGA,FPGA接收到数据后进行处理,然后再通过串口将处理后的数据发送给单片机。

2.SPI:SPI是一种用于片上外设之间通信的串行通信协议,常用于FPGA与外部设备(例如传感器、显示器等)之间的通信。

在FPGA和单片机之间建立SPI通信,需要在FPGA中实现SPI控制器,并将其与单片机的SPI接口连接。

FPGA通过把数据写入SPI发送缓冲区或从SPI接收缓冲区读取数据来实现与单片机的通信。

单片机通过控制SPI接口的时钟、数据和使能信号来与FPGA进行数据传输。

3.I2C:I2C是一种双线制串行总线,常用于连接多个设备的系统,例如FPGA、单片机和其他外部设备之间的通信。

在FPGA和单片机之间建立I2C通信,需要在FPGA中实现I2C控制器,并将其与单片机的I2C接口连接。

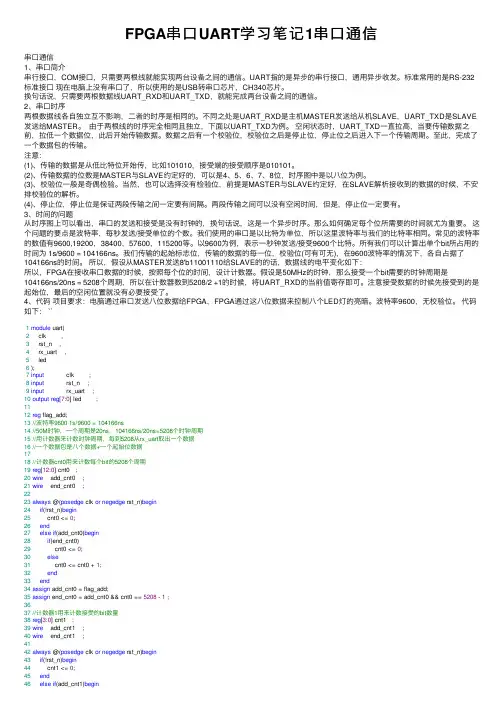

FPGA串⼝UART学习笔记1串⼝通信串⼝通信1、串⼝简介串⾏接⼝,COM接⼝,只需要两根线就能实现两台设备之间的通信。

UART指的是异步的串⾏接⼝,通⽤异步收发。

标准常⽤的是RS-232标准接⼝现在电脑上没有串⼝了,所以使⽤的是USB转串⼝芯⽚,CH340芯⽚。

换句话说,只需要两根数据线UART_RXD和UART_TXD,就能完成两台设备之间的通信。

2、串⼝时序两根数据线各⾃独⽴互不影响,⼆者的时序是相同的。

不同之处是UART_RXD是主机MASTER发送给从机SLAVE,UART_TXD是SLAVE 发送给MASTER。

由于两根线的时序完全相同且独⽴,下⾯以UART_TXD为例。

空闲状态时,UART_TXD⼀直拉⾼,当要传输数据之前,拉低⼀个数据位,此后开始传输数据。

数据之后有⼀个校验位,校验位之后是停⽌位,停⽌位之后进⼊下⼀个传输周期。

⾄此,完成了⼀个数据包的传输。

注意:(1)、传输的数据是从低⽐特位开始传,⽐如101010,接受端的接受顺序是010101。

(2)、传输数据的位数是MASTER与SLAVE约定好的,可以是4、5、6、7、8位,时序图中是以⼋位为例。

(3)、校验位⼀般是奇偶检验。

当然,也可以选择没有检验位,前提是MASTER与SLAVE约定好,在SLAVE解析接收到的数据的时候,不安排校验位的解析。

(4)、停⽌位,停⽌位是保证两段传输之间⼀定要有间隔。

两段传输之间可以没有空闲时间,但是,停⽌位⼀定要有。

3、时间的问题从时序图上可以看出,串⼝的发送和接受是没有时钟的,换句话说,这是⼀个异步时序。

那么如何确定每个位所需要的时间就尤为重要。

这个问题的要点是波特率,每秒发送/接受单位的个数。

我们使⽤的串⼝是以⽐特为单位,所以这⾥波特率与我们的⽐特率相同。

常见的波特率的数值有9600,19200,38400,57600,115200等。

以9600为例,表⽰⼀秒钟发送/接受9600个⽐特。

FPGA实现RS-232串口收发的仿真过程(Quartus+Synplify+ModelSim)(2007-09-11 12:17:37)网上关于RS—232的异步收发介绍得很多,最近没事学着摸索用ModelSim来做时序仿真,就结合网上的参考资料和自己的琢磨,做了这个东西.针对我这个小程序结合FPGA的开发流程,主要走了以下几步:1。

文本程序输入(Verilog HDL)2。

功能仿真(ModelSim,查看逻辑功能是否正确,要写一个Test Bench)3。

综合(Synplify Pro,程序综合成网表)4. 布局布线(Quartus II,根据我选定的FPGA器件型号,将网表布到器件中,并估算出相应的时延)5。

时序仿真(ModelSim,根据时延做进一步仿真)这里贴出我的程序和各个详细步骤,能和各位正在学习的新手们一起分享。

0。

原理略一、文本程序输入(Verilog HDL)发送端:module trans(clk,rst,TxD_start,TxD_data,TxD,TxD_busy);input clk,rst,TxD_start;input[7:0]TxD_data; // 待发送的数据output TxD, // 输出端口发送的串口数据TxD_busy;reg TxD;reg [7:0] TxD_dataReg; // 寄存器发送模式,因为在串口发送过程中输入端不可能一直保持有效电平reg [3:0]state;parameter ClkFrequency = 25000000;// 时钟频率-25 MHzparameter Baud = 115200;// 串口波特率-115200// 波特率产生parameter BaudGeneratorAccWidth = 16;reg [BaudGeneratorAccWidth:0]BaudGeneratorAcc;wire [BaudGeneratorAccWidth:0] BaudGeneratorInc = ((Baud〈<(BaudGeneratorAccWidth—4))+(ClkFrequency>>5))/(ClkFrequency>〉4);wire BaudTick = BaudGeneratorAcc[BaudGeneratorAccWidth];wire TxD_busy;always @(posedge clk or negedge rst)if(~rst)BaudGeneratorAcc <= 0;else if(TxD_busy)BaudGeneratorAcc <= BaudGeneratorAcc[BaudGeneratorAccWidth-1:0]+ BaudGeneratorInc;// 发送端状态wire TxD_ready = (state==0);// 当state = 0时,处于准备空闲状态,TxD_ready = 1 assign TxD_busy = ~TxD_ready; // 空闲状态时TxD_busy = 0// 把待发送数据放入缓存寄存器TxD_dataRegalways @(posedge clk or negedge rst)if(~rst)TxD_dataReg <= 8’b00000000;else if(TxD_ready &TxD_start)TxD_dataReg <= TxD_data;// 发送状态机always @(posedge clk or negedge rst)if(~rst)beginstate 〈= 4’b0000;// 复位时,状态为0000,发送端一直发1电平TxD <= 1'b1;endelsecase(state)4’b0000: if(TxD_start) beginstate <= 4’b0100;// 接受到发送信号,进入发送状态end4’b0100: if(BaudTick) beginstate <= 4’b1000;// 发送开始位—0电平TxD <= 1'b0;end4'b1000: if(BaudTick)beginstate <= 4'b1001;// bit 0TxD <= TxD_dataReg[0];end4'b1001:if(BaudTick) beginstate <= 4’b1010; // bit 1TxD 〈= TxD_dataReg[1];end4’b1010:if(BaudTick) beginstate <= 4'b1011; // bit 2TxD <= TxD_dataReg[2];end4'b1011:if(BaudTick)beginstate <= 4'b1100; // bit 3TxD 〈= TxD_dataReg[3];end4'b1100: if(BaudTick) beginstate 〈= 4’b1101;// bit 4TxD <= TxD_dataReg[4];end4'b1101:if(BaudTick) beginstate 〈= 4’b1110;// bit 5TxD 〈= TxD_dataReg[5];end4'b1110:if(BaudTick) beginstate <= 4’b1111; // bit 6TxD <= TxD_dataReg[6];end4’b1111:if(BaudTick) beginstate 〈= 4’b0010;// bit 7TxD <= TxD_dataReg[7];end4'b0010: if(BaudTick) beginstate 〈= 4'b0011;// stop1TxD 〈= 1’b1;end4’b0011:if(BaudTick)beginstate 〈= 4’b0000;// stop2TxD 〈= 1'b1;enddefault: if(BaudTick)beginstate 〈= 4’b0000;TxD 〈= 1’b1;endendcaseendmodule接收端:module rcv(clk,rst,RxD,RxD_data,RxD_data_ready,);input clk,rst,RxD;output[7:0] RxD_data; // 接收数据寄存器output RxD_data_ready;// 接收完8位数据,RxD_data 值有效时,RxD_data_ready 输出读信号parameter ClkFrequency = 25000000;// 时钟频率-25MHzparameter Baud = 115200; // 波特率-115200reg[2:0]bit_spacing;reg RxD_delay;reg RxD_start;reg[3:0] state;reg[7:0]RxD_data;reg RxD_data_ready;// 波特率产生,使用8倍过采样parameter Baud8 = Baud*8;parameter Baud8GeneratorAccWidth = 16;wire [Baud8GeneratorAccWidth:0]Baud8GeneratorInc = ((Baud8〈<(Baud8GeneratorAccWidth—7))+(ClkFrequency>〉8))/(ClkFrequency>>7);reg [Baud8GeneratorAccWidth:0]Baud8GeneratorAcc;always @(posedge clk or negedge rst)if(~rst)Baud8GeneratorAcc 〈= 0;elseBaud8GeneratorAcc <= Baud8GeneratorAcc[Baud8GeneratorAccWidth—1:0] + Baud8GeneratorInc;// Baud8Tick 为波特率的8倍-115200*8 = 921600wire Baud8Tick = Baud8GeneratorAcc[Baud8GeneratorAccWidth];// next_bit 为波特率-115200always @(posedge clk or negedge rst)if(~rst||(state==0))bit_spacing 〈= 0;else if(Baud8Tick)bit_spacing <= bit_spacing + 1;wire next_bit = (bit_spacing==7);// 检测到RxD 有下跳沿时,RxD_start 置1,准备接收数据always@(posedge clk)if(Baud8Tick)beginRxD_delay 〈= RxD;RxD_start <= (Baud8Tick & RxD_delay & (~RxD));end// 状态机接收数据always@(posedge clk or negedge rst)if(~rst)state 〈= 4’b0000;else if(Baud8Tick)case(state)4'b0000:if(RxD_start)state <= 4’b1000;// 检测到下跳沿4’b1000: if(next_bit)state 〈= 4'b1001;// bit 04'b1001: if(next_bit) state <= 4'b1010;// bit 14’b1010:if(next_bit) state 〈= 4’b1011; // bit 24’b1011: if(next_bit) state <= 4'b1100;// bit 34’b1100: if(next_bit)state 〈= 4'b1101;// bit 44'b1101:if(next_bit)state <= 4’b1110; // bit 54'b1110: if(next_bit) state <= 4'b1111; // bit 64'b1111: if(next_bit) state 〈= 4'b0001; // bit 74'b0001: if(next_bit) state 〈= 4’b0000;// 停止位default: state <= 4'b0000;endcase// 保存接收数据到RxD_data 中always @(posedge clk or negedge rst)if(~rst)RxD_data 〈= 8’b00000000;else if(Baud8Tick &&next_bit && state[3])RxD_data <= {RxD,RxD_data[7:1]};// RxD_data_ready 置位信号always @(posedge clk or negedge rst)if(~rst)RxD_data_ready <= 0;elseRxD_data_ready <= (Baud8Tick && next_bit &&state==4'b0001); endmodule为了测试收发是否正常,写的Test Bench`timescale 1ns / 1nsmodule rs232_test;reg clk,rst,TxD_start;reg [7:0]TxD_data;wire[7:0] RxD_data;wire //RxD,TxD,TxD_busy,RxD_data_ready;trans trans(.clk(clk),。

fpga利用io口实现rs422通信的代码RS422通信是一种全双工、差分信号传输的串行通信协议。

相较于RS232通信协议,RS422通信协议传输距离更远、传输速度更快、噪声干扰更小,并且能够支持多个设备同时通信。

在本文中,我们将介绍如何利用FPGA的IO口实现RS422通信。

首先,我们需要为FPGA选择一个支持RS422协议的IO口。

以下是常用的几种IO口:1. 差分输出:FPGA通过两个相反的信号线向外输出差分信号。

3. 孤立输入:FPGA通过单一信号线接收差分信号,并通过内部电路将差分信号转换为单压缩信号。

在本文中,我们将选择差分输入的方式进行RS422通信。

接下来,我们需要配置FPGA的IO口。

一般来说,FPGA会提供相应的IP核用于配置IO口,我们可以通过IP核配置管理器进行配置。

以下是常见的IO口配置:1. 设置IO口的功能:将IO口设置为输入、输出或双向模式。

2. 设置IO口的电平:确定IO口的高电平和低电平的电压值。

3. 设置IO口的上下拉电阻:控制IO口的输入输出电阻。

4. 设置IO口的保护电路:为了保护IO口不受过电压或过电流的损坏,通常需要为IO 口配置保护电路。

接下来,我们可以开始编写FPGA的代码。

以下是实现RS422通信的代码:```verilogmodule RS422 (input clk, //时钟信号input rst, //复位信号input [7:0] rx, //接收端口output [7:0] tx, //发送端口output de, //差分输出使能output re, //差分输入使能output [1:0] ie //输入使能);//定义常量localparam BIT_CNT = 8; //一帧数据位数 localparam CNT_MAX = 16'h3FFF; //计数器最大值 localparam BAUD_RATE = 9600; //波特率//计数器reg [15:0] cnt;always @(posedge clk or posedge rst) beginif (rst) begincnt <= 0;end else beginif (cnt >= CNT_MAX) begincnt <= 0;end else begincnt <= cnt + 1;endendend//接收数据wire [BIT_CNT-1:0] rx_data;reg rx_flag;reg rx_err;reg rx_done;uart_rx #(BIT_CNT) uart_rx_inst (.rx(rx),.clk(clk),.rst(rst),.data(rx_data),.flag(rx_flag),.err(rx_err),.done(rx_done));assign tx = tx_data;//差分接收器使能信号assign re = 1;//输入使能assign ie[0] = tx_done;assign ie[1] = rx_done;endmodule```以上代码中,我们使用了一个基于计数器的时序生成器来产生波特率同步信号,用于控制发送和接收的时序。

在FPGA中实现RS485通信,需要控制发送方和接收方的差分信号输出和输入。

以下是一个基本的步骤:

1. 定义输入输出端口:在Verilog代码中,通过定义不同的输入输出端口来实现发送和接收功能。

2. 编码数据:发送方将要发送的数据通过编码后转换成差分信号输出。

常用的编码方式有NRZ(非归零码)、Manchester码等。

3. 接收数据:接收设备检测到双绞线上的RS485电平的每一个单bit数据,将其转换为普通的TTL电平信号,并通过接收器输出脚送给UART控制器的接收脚。

4. 解码数据:UART控制器将接收脚上的每一个单bit信号按照UART协议进行接收解码,得到以字节为单位的实际数据。

5. 数据解析:MODBUS协议栈将UART接收到的多个字节数据进行解析得到完整的数据帧,并解帧得到实际的数据部分。

在实际应用时,MODBUS协议栈一般由CPU通过软件方式实现。

以上步骤仅供参考,建议咨询专业人士获取具体信息。

基于FPGA的串口通信电路设计[摘要]串行通信接口是一种应用广泛的通信接口。

目前,大部分处理器都集成了支持rs-232接口的通用异步收发器,本文基于fpga开发板设计了一个串口数据采集和处理程序,介绍了用verilog hdl硬件描述语言来开发波特率发生器、接收模块和发送模块这三个模块,以及系统各个模块的具体设计方法和原理,用quartus ii软件进行仿真并给出结果,分别验证各个模块的正确性及用fpga实现串行通信的可行性。

[关键词]串行通信 rs-232 verilog hdl fpga中图分类号:tn 文献标识码:a 文章编号:1009-914x(2013)08-320-011.fpga概述fpga现场可编程逻辑门阵列是数字系统设计的主要硬件平台,其主要特点是完全由用户通过软件进行配置和编程,从而完成某种特定的功能,且可以反复擦写。

fpga具有运算速度快、根据需求在内部嵌入硬/软ip核,以及反复编程,擦写,使用的特点,被广泛应用于通信,数字信号处理,工业控制等领域。

2.rs232串口通信接口串口即串行数据接口主要用于网管控制或主业务数据的传输,支持数据的双向传输,速率9600-115200bps,即可以完成和pc的通信,也可以完成与带有标准串口的外设相连。

其中串口接口分为带插孔和带插针的两种,其中插针端称为dce,插孔端称为dte。

3.串口通信的verilog hdl实现本设计要求在fpga开发板上实现波特率为115200bps,停止位为1比特、1比特校验位的串口通信,并要求和pc机通过串口调试助手完成双向通信。

3.1波特率发生器模块的verilog hdl实现波特率发生器实际上是一个分频器,从给定的系统时钟频率得到要求的波特率。

一般来讲,为了提高系统的容错性处理,要求波特率发生器的输出时钟为实际串口数据波特率的n倍,n可以取值为8、16、32、64等。

在本设计中,系统的时钟为50mhz,取n为16,则分频系数为50000000/(16*115200)=27.127,取整为27。

FPGA与单片机实现串行通信FPGA(Field-Programmable Gate Array)和单片机是两种常见的嵌入式系统设计元件。

FPGA是一种可编程逻辑芯片,可以重新配置内部逻辑电路以实现各种不同的功能。

它由大量的逻辑门、存储单元和I/O(输入/输出)资源组成。

相比于单片机,FPGA具有更高的灵活性和通用性,并且可以实现更高性能的应用。

单片机则是一种集成了处理器、内存和各种外设接口的微控制器芯片。

它通常具有较小的尺寸和低功耗特性,适用于较简单的应用场景。

单片机通常使用汇编语言或高级编程语言进行程序设计,并通过输入/输出引脚与外部设备进行通信。

串行通信是一种将数据按照位的顺序依次传输的通信方式。

在FPGA与单片机之间实现串行通信有多种方法,其中常见的包括USART、SPI、I2C和UART等。

USART(Universal Synchronous/AsynchronousReceiver/Transmitter)是一种通用的串行接口,可以工作在同步或异步模式下。

FPGA和单片机可以通过USART接口进行双向数据传输。

USART接口包含多个引脚,包括数据线、时钟线和控制线。

通过配置合适的配置参数,可以实现不同的通信速率和数据格式。

SPI(Serial Peripheral Interface)是一种全双工的串行通信协议,常用于外设与控制器之间进行高速数据传输。

SPI接口由四根线组成,包括主机输出(MISO)、主机输入(MOSI)、时钟(SCLK)和片选(SS)线。

FPGA可以作为SPI主机,单片机作为SPI从机,通过配置合适的时序和数据格式实现数据的传输。

I2C(Inter-Integrated Circuit)是一种双线串行总线,用于短距离内的设备通信。

I2C由两根线组成,包括串行数据线(SDA)和串行时钟线(SCL)。

FPGA和单片机可以通过I2C接口进行双向数据传输。

在I2C通信中,所有设备都必须拥有唯一的地址,以便正确识别和通信。

FPGA设计与应用串口通信实验报告班级:1105103姓名:苏林效学号:1110510321日期:2014年10月29日实验性质:验证性实验类型:必做开课单位:电信院学时:2学时一、实验目的1、了解串口通信的基本原理;2、掌握锁相环的基本原理和使用方法;3、掌握起始位和停止位的含义及实现方法;4、掌握VHDL状态机的基本使用方法;5、掌握基本的接口设计和调试技巧;二、实验准备2.1 串口通信原理(1分)串口通信是以字节为单位,按位传输数据和接收数据的。

先看一下发送数据:串行线缆的两端事先约定好串行传输的参数(传输速度、传输格式等),之后进行传输,①当没有数据传输的时候,发送端向数据线上发送“1”;②当要传输数据时,发送端先发送一个“0”来表示要传输数据了,这样当接收端检测到“0”便可以知道有数据到来了;③开始传输后,数据以约定的速度和格式传输;④每次传输完成一个字节之后,都在其后发送一个停止位“1”。

这样,发送数据就结束了。

再来看接收数据,初始状态是等待状态,接收的一直是“1”,当检测到0时进入检验状态,在检验状态下如果再检测到0(一般采用过采样)则进入接收数据状态,当接收完8位比特数后判断是否有停止位,如果有则此字节接收结束,重新进入等待状态准备接受下一字节。

2.2 锁相环的基本原理(1分)锁相环是以锁定输入载波信号的相位为目标的一种载波环实现形式。

它由三部分组成:鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)。

如上图。

锁相环的工作原理:压控振荡器的输出经过采集并分频,后与基准信号同时输入鉴相器。

鉴相器通过比较上述两个信号的相位差,输出结果通过环路滤波器,滤除噪声和高频分量,然后输出一个直流脉冲电压,用它来控制VCO ,使它的频率改变,使()lim 0c p t θ=。

经过较短时间后,VCO 的输出稳定于某一值。

环路一旦进入锁定状态后,压控振荡器的输出信号与环路的输入信号(参考信号)相位时刻保持一致。

三、代码及测试3.1程序及分析(2分)顶层原理图如上所示,主要包括三个模块,锁相环(输出57.69MHz )、分频(输出接受时的10倍采样速率和数码管显示速率)、接受(按57.6kbps 接受从串口发来的数据)。

分频模块代码: LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY DIV ISPORT(CLK : IN STD_LOGIC; --锁相环输出时钟57.69MCOUT1 : OUT STD_LOGIC;--分频器输出采样时钟576kCOUT2 : OUT STD_LOGIC);--分频器产产生扫描时钟100hzEND DIV;ARCHITECTURE BEHAV OF DIV ISBEGINPROCESS(CLK)V ARIABLE COUT1_NUM : STD_LOGIC_VECTOR(5 DOWNTO 0):=(OTHERS => '0'); --输出时钟1 计数器V ARIABLE COUT2_NUM : STD_LOGIC_VECTOR(18 DOWNTO 0):=(OTHERS => '0'); --输出时钟2 计数?V ARIABLE COUT1_1 : STD_LOGIC;V ARIABLE COUT2_2 : STD_LOGIC;BEGINIF RISING_EDGE(CLK) THENIF COUT1_NUM >= 49 THENCOUT1_1 := NOT COUT1_1;COUT1_NUM := (OTHERS => '0');ELSECOUT1_NUM := COUT1_NUM + 1;END IF;IF COUT2_NUM >= 288450 THENCOUT2_2 := NOT COUT2_2;COUT2_NUM := (OTHERS => '0');ELSECOUT2_NUM := COUT2_NUM + 1;END IF;COUT1 <= COUT1_1;COUT2 <= COUT2_2;END IF;END PROCESS;END BEHAV;接受模块代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY COM_REC ISPORT(CLK_10 : IN STD_LOGIC;--输入时钟,按10倍采样,是rs232串口速率的10倍CLK_DIS : IN STD_LOGIC;-- DISPLAY CLKINNUM : IN STD_LOGIC;--输入的值LED_EN : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);LED : OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END;ARCHITECTURE BEHAV OF COM_REC ISTYPE STATE IS (SPARE, READY, REC, STOP);--定义接受4状态SIGNAL TR_INNUM : STD_LOGIC_VECTOR(7 DOWNTO 0); --接收到8位数SIGNAL LED_L : STD_LOGIC_VECTOR(6 DOWNTO 0);--控制两位数码管显示SIGNAL LED_H : STD_LOGIC_VECTOR(6 DOWNTO 0);BEGINPROCESS(CLK_10)V ARIABLE TR_INNUM_NUM : INTEGER RANGE 0 TO 15 := 0; --对接受到得每一位数计数V ARIABLE TRUE : STD_LOGIC := '0';V ARIABLE CURRENT_STATE : STATE := SPARE;--当前状态V ARIABLE SAM_NUM_0 : INTEGER RANGE 0 TO 15 := 0;--对采样次数计数V ARIABLE SAM_NUM_1 : INTEGER RANGE 0 TO 15 := 0;BEGINIF CLK_10'EVENT AND CLK_10 = '1' THENIF CURRENT_STATE = SPARE THENIF INNUM = '0' THENSAM_NUM_0 := SAM_NUM_0 + 1;--第一次采样到零点,即改变状态CURRENT_STATE := READY;ELSECURRENT_STATE := SPARE;END IF;ELSIF CURRENT_STA TE = READY THENIF INNUM = '0' THENSAM_NUM_0 := SAM_NUM_0 + 1;ELSESAM_NUM_1 := SAM_NUM_1 + 1;END IF;IF (SAM_NUM_0 + SAM_NUM_1) >= 10 THEN--判断是否真开端IF SAM_NUM_0 >= 6 THENCURRENT_STATE := REC;SAM_NUM_0 := 0;SAM_NUM_1 := 0;ELSECURRENT_STATE := SPARE;END IF;ELSECURRENT_STATE := READY;END IF;ELSIF CURRENT_STA TE = REC THENIF INNUM = '0' THENSAM_NUM_0 := SAM_NUM_0 + 1;ELSESAM_NUM_1 := SAM_NUM_1 + 1;END IF;IF (SAM_NUM_0 + SAM_NUM_1) >= 10 THEN --接受数据判断IF SAM_NUM_0 >= 6 THENTR_INNUM(TR_INNUM_NUM) <= '0';ELSETR_INNUM(TR_INNUM_NUM) <= '1';END IF;SAM_NUM_0 := 0;SAM_NUM_1 := 0;TR_INNUM_NUM := TR_INNUM_NUM + 1;IF TR_INNUM_NUM >= 8 THENCURRENT_STATE := STOP;TR_INNUM_NUM := 0;ELSECURRENT_STATE := REC;END IF;ELSECURRENT_STATE := REC;END IF;ELSIF CURRENT_STA TE = STOP THENIF INNUM = '1' THENSAM_NUM_1 := SAM_NUM_1 + 1;ELSESAM_NUM_0 := SAM_NUM_0 + 1;END IF;IF (SAM_NUM_0 + SAM_NUM_1) >= 10 THEN IF SAM_NUM_1 >= 6 THENTRUE := '1';CURRENT_STATE := SPARE;END IF;SAM_NUM_0 := 0;SAM_NUM_1 := 0;ELSECURRENT_STATE := STOP;END IF;ELSECURRENT_STATE := SPARE;END IF;END PROCESS;LED_H <="0111111" when TR_INNUM(7 downto 4) = 0 else "0000110" when TR_INNUM(7 downto 4) = 1 else"1011011" when TR_INNUM(7 downto 4) = 2 else"1001111" when TR_INNUM(7 downto 4) = 3 else"1100110" when TR_INNUM(7 downto 4) = 4 else"1101101" when TR_INNUM(7 downto 4) = 5 else"1111101" when TR_INNUM(7 downto 4) = 6 else"0000111" when TR_INNUM(7 downto 4) = 7 else"1111111" when TR_INNUM(7 downto 4) = 8 else"1101111" when TR_INNUM(7 downto 4) = 9 else"1110111" when TR_INNUM(7 downto 4) = 10 else"1111100" when TR_INNUM(7 downto 4) = 11 else"0111001" when TR_INNUM(7 downto 4) = 12 else"1011110" when TR_INNUM(7 downto 4) = 13 else"1111001" when TR_INNUM(7 downto 4) = 14 else"1110001";LED_L <="0111111" when TR_INNUM(3 downto 0) = 0 else "0000110" when TR_INNUM(3 downto 0) = 1 else"1011011" when TR_INNUM(3 downto 0) = 2 else"1001111" when TR_INNUM(3 downto 0) = 3 else"1100110" when TR_INNUM(3 downto 0) = 4 else"1101101" when TR_INNUM(3 downto 0) = 5 else"1111101" when TR_INNUM(3 downto 0) = 6 else"0000111" when TR_INNUM(3 downto 0) = 7 else"1111111" when TR_INNUM(3 downto 0) = 8 else"1101111" when TR_INNUM(3 downto 0) = 9 else"1110111" when TR_INNUM(3 downto 0) = 10 else"1111100" when TR_INNUM(3 downto 0) = 11 else"0111001" when TR_INNUM(3 downto 0) = 12 else"1011110" when TR_INNUM(3 downto 0) = 13 else"1111001" when TR_INNUM(3 downto 0) = 14 else"1110001";PROCESS(CLK_DIS)V ARIABLE A : STD_LOGIC;BEGINIF RISING_EDGE(CLK_DIS) THENIF A = '0' THENLED <= LED_L;LED_EN <= "0001";A := '1';ELSELED <= LED_H;LED_EN <= "0010";A := '0';END IF;END IF;END PROCESS;END BEHAV;3.2 SignalTap II波形测试结果(1分)此实验要求发送16进制的21H,实际发送的是十进制的33,而数码管却显示21,高四位(0010)、低四位(0001)。