EDA报告:智力竞赛抢答器

- 格式:doc

- 大小:375.50 KB

- 文档页数:13

学生课程设计报告课程名称:EDA数字抢答器目录一、课程设计目的 (3)二、课程设计题目描述和要求 (3)三、课程设计报告内容 (4)四、结论 (21)五、结束语 (22)六、参考书目 (22)一、课程设计目的.设计一个可容纳4组参赛的数字式抢答器。

通过此次设计熟练掌握VHDL 语言,并掌握设计所用的软件。

二、课程设计题目描述和要求在许多比赛活动中,为了准确、公正、直观地判断出第一抢答者通常设置一台抢答器,通过数显、灯光及音响等多种手段指示出第一抢答者。

同时,还可以设置计分、犯规及奖惩计录等多种功能。

本设计的具体要求是:(1) 设计制作一个可容纳四组参赛者的数字智力抢答器,每组设置一个抢答按钮供抢答者使用。

(2) 电路具有第一抢答信号的鉴别和锁存功能。

(3) 系统具有计分电路。

(4) 系统具有犯规电路。

系统设计方案:系统的输入信号有:各组的抢答按钮A、B、C、D,系统清零信号CLR,系统时钟信号CLK,计分复位端RST,加分按钮端ADD,计时预置控制端LDN,计时使能端EN,计时预置数据调整按钮可以用如TA、TB表示;系统的输出信号有:四个组抢答成功与否的指示灯控制信号输出口可用如LEDA、LEDB、LEDC、LEDD表示,四个组抢答时的计时数码显示控制信号若干,抢答成功组别显示的控制信号若干,各组计分动态显示的控制信号若干。

整个系统至少有三个主要模块:抢答鉴别模块;抢答计时模块;抢答计分模块,其他功能模块(犯规警告模块,输出显示模块)。

三、课程设计报告内容按照要求,我们可以将整个系统分为四个主要模块:抢答鉴别模块;抢答计时模块;抢答计分模块;译码显示模块。

对于需显示的信息,需要增加或外接译码器,进行显示译码。

考虑到实验开发平台提供的输出显示资源的限制,我们将组别显示和计时显示的译码器内设,而将各组的计分显示的译码器外接。

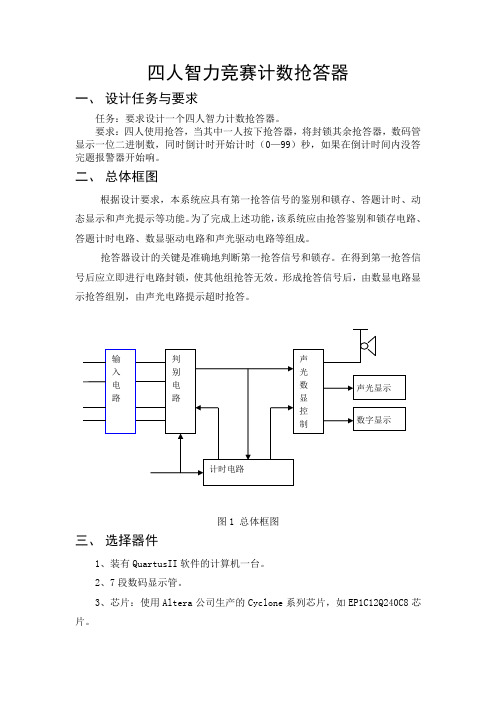

整个系统的大致组成框图如图2.1所示。

图2.1 LED A LED B LED C LED D3.1抢答鉴别模块3.1.1抢答鉴别模块的功能抢答队伍共分为四组A,B,C,D。

四人智力竞赛计数抢答器一、设计任务与要求任务:要求设计一个四人智力计数抢答器。

要求:四人使用抢答,当其中一人按下抢答器,将封锁其余抢答器,数码管显示一位二进制数,同时倒计时开始计时(0—99)秒,如果在倒计时间内没答完题报警器开始响。

二、总体框图根据设计要求,本系统应具有第一抢答信号的鉴别和锁存、答题计时、动态显示和声光提示等功能。

为了完成上述功能,该系统应由抢答鉴别和锁存电路、答题计时电路、数显驱动电路和声光驱动电路等组成。

抢答器设计的关键是准确地判断第一抢答信号和锁存。

在得到第一抢答信号后应立即进行电路封锁,使其他组抢答无效。

形成抢答信号后,由数显电路显示抢答组别,由声光电路提示超时抢答。

图1 总体框图三、选择器件1、装有QuartusII软件的计算机一台。

2、7段数码显示管。

3、芯片:使用Altera公司生产的Cyclone系列芯片,如EP1C12Q240C8芯片。

4、EDA实验箱一个。

5,下载接口是数字芯片的下载接口(JTAG)主要用于FPGA芯片的数据下载。

6、时钟源。

Cyclone的性能特性Cyclone器件的性能足以和业界最快的FPGA进行竞争。

Cyclone FPGA内部包括可配置逻辑模块CLB(Configurable Logic Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。

FPGA的基本特点主要有:1)采用FPGA设计ASIC电路,用户不需要投片生产,就能得到合用的芯片。

2)FPGA可做其它全定制或半定制ASIC电路的中试样片。

3)FPGA内部有丰富的触发器和I/O引脚。

4)FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。

5) FPGA采用高速CHMOS工艺,功耗低,可以与CMOS、TTL电平兼容。

可以说,FPGA芯片是小批量系统提高系统集成度、可靠性的最佳选择之一。

四、功能模块1:library ieee;use ieee.std_logic_1164.all;entity feng isport(cp,clr:in std_logic;q :out std_logic);end feng;architecture feng_arc of feng isbeginprocess(cp,clr)beginif clr='0' thenq<='0';elsif cp'event and cp='0' thenq<='1';end if;end process;end feng_arc;此程序为抢答鉴别模块feng该模块主要实现抢答和鉴别的功能。

燕山大学EDA课程设计报告书智力竞赛抢答器姓名:李学森班级:08电子信息工程3班学号:080104020063 成绩:一、设计题目:智力竞赛抢答器二、设计要求:1 .五人参赛每人一个按钮,主持人一个按钮,按下就开始;2 .每人一个发光二极管,抢中者灯亮;3 .有人抢答时,喇叭响两秒钟;4 .答题时限为10秒钟,从有人抢答开始,用数码管倒计时间,0,9,8…1,0;倒计时到0的时候,喇叭发出两秒声响。

三、设计内容:1.设计方案:主持人控制总开关,主持人置高电平后,系统进入准备工作。

有人抢答时,相应的二极管发光,同时数码管开始倒计时,且喇叭响两秒钟。

当倒计时再次到0的时候,喇叭再响2秒钟。

我设计的方案由五个高低电平控制相应的发光二极管,第六个用于主持人复位。

由二极管控制数码管和其中一个喇叭,再由数码管控制另一喇叭。

因此把整个课题分成四个模块:抢答器、10s倒计时器、分频器、2s计时器。

2.模块①:抢答器control为置零端,主持人控制,L1-L5由每位选手控制。

Q1-Q5为发光二极管,主持人置低电平后,Q1-Q5都被置零。

当主持人置为高电平时,抢答开始,抢答成功者对应的二极管发光,通过与门将cp信号封锁,并输入低电平到DFF中,则其他选手再次按键时结果不会改变,实现了一人抢答后,其他人不能再做答。

主持人按H清零后即可再次抢答。

此模块的仿真波形如下:仿真说明:当CONTROL为高电平时,即主持人按键以后,L1最先抢答成功,显示L1是高电平,使其对应的二极管发光模块②:十秒倒计时器此十秒钟倒计时器是由74190与7448组成的十进制减法计数器,它保留预制置数端、CP信号端、计数输出端,TNUP置高电平进行减法计算,其余的端口都置为0。

LDN是置零端,当它等于1的时候,74190有效,倒计时开始。

当输出0、9、--1时,D触发器输出结果总是0,不影响CP信号。

当输出从1到0时,D触发器输出结果为1,则CP信号被封锁。

EDA抢答器设计报告设计背景抢答器是一种常见的电子设备,通常用于各种知识竞赛和考试中,可以有效的提高比赛的交互性和趣味性。

随着科技的不断发展,现在的抢答器逐渐向着数字化、智能化的方向发展,其中EDA抢答器成为了新的热点。

EDA是“Electronic Design Automation”的缩写,即电子设计自动化,主要利用计算机和相关软件工具进行各种电子设计任务,如芯片设计、电路布局等,其应用范围非常广泛。

而EDA抢答器则是一个结合了电子设计和抢答器功能的产品。

设计目标本次设计的EDA抢答器,主要目标是实现以下四个方面的功能:1.抢答功能:支持多个参赛者使用抢答器参与竞赛,可先后应答,同时记录每个参赛者的答题时间,以便后续评分;2.显示功能:支持在抢答器上显示参赛者的编号和抢答结果;3.报警功能:可根据比赛要求设置倒计时时间,并在时间结束时自动报警;4.可扩展性:支持通过扩展硬件模块或软件升级的方式扩展其功能,如增加LED灯模块、无线联网模块等。

设计方案硬件设计电路原理图本次设计采用STM32F103C8T6开发板作为主控制器,同时配合7个按键(K1 - K7)、一个LCD屏幕(1602)以及一个蜂鸣器(BZ1)完成了抢答器的基本功能设计。

其电路原理图如下图所示:硬件元器件以下是本次设计所用到的硬件元器件和其相应参数:•STM32F103C8T6主控制器•7个按键:K1 - K7•LCD屏幕:1602•蜂鸣器:BZ1•电阻:10kΩ、220Ω•电容:22pF、10uF•晶振:8MHz按键布局具体的按键布局如下图所示:软件设计编程语言与开发环境本次设计采用C语言进行编程,开发环境为Keil5。

抢答逻辑流程本次设计的抢答流程如下:1.开始运行程序,LCD屏幕显示“Game Ready!”;2.在规定时间内,参赛者按下对应的按键抢答,LCD屏幕显示相应参赛者编号,同时蜂鸣器发出短促的声音表示抢答成功;3.抢答结束后,根据抢答时间的顺序和正确性进行评分,将得分结果显示在LCD屏幕上;4.每次比赛可以显示多个参赛者的得分结果,比赛结束后可以通过按下K1键来清零得分并重新开始下一轮比赛。

SOPC/EDA综合课程设计报告设计题目:智力抢答器设计者:学号:班级:指导老师:完成时间:目录第一章智力抢答器的设计方案分析 (3)第一节基于VHDL的智能抢答器 (3)1.1.1设计目的及要求 (3)1.1.2设计分析与设计思路 (4)第二章抢答器各模块的原理及介绍 (5)第一节系统的框图及介绍 (5)2.1.1结构框图及系统框图 (5)第二节模块的介绍 (5)2.2.1抢答鉴别模块QDJB (5)2.2.2计时模块JSQ (6)2.2.3记分模块JFQ (6)2.2.4译码器显示模块YMQ (7)第三节抢答器的VHDL源程序 (8)2.3.1各模块的VHDL源程序 (8)一、抢答鉴别模块QDJB的VHDL源程序 (8)二、计时模块JSQ的VHDL源程序 (9)三、记分模块JFQ的VHDL源程序 (10)四、译码显示模块YMQ的VHDL源程序 (12)五、顶层原理图文件 (14)第三章仿真波形 (15)第一节仿真波形 (15)3.1.1抢答鉴别模块QDJB (15)3.1.2计时模块JSQ (15)3.1.3记分模块JFQ (16)3.1.4 译码显示模块YMQ (16)第四章附录 (18)4.1结束语 (18)4.2参考文献 (19)4.3共阴极七段数码管 (20)第一章智力抢答器的设计方案分析第一节、基于VHDL的智能抢答器1.1.1设计目的及要求EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

利用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC版图或PCB版图的整个过程的计算机上自动处理完成。

EDA智力竞赛抢答器设计一、实训目的:1、了解竞赛抢答器的工作原理;2、熟悉VHDL语言编程,了解实际设计中的优化方案。

二、实训内容:设计一个数字式竞赛抢答器,可以判断第一抢答者,并具备计分功能。

抢答器可以容纳四组参赛者同时抢答,每组设置一个按钮供抢答者使用。

设置抢答器使能信号,当此信号有效时,若参赛者按下抢答开关,则抢答器能判断出第一抢答者并指示该组抢答成功,其他组参赛者的抢答开关不起作用;若提前抢答,则对相应的参赛者发出警报。

如果抢答成功的参赛者满足得分条件,则增加相应的分数,答错不扣分。

鉴别模块library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity jianbie isport(EN1,RST1:in std_logic;A,B,C,D:in std_logic;A1,B1,C1,D1:out std_logic;STA TES:out std_logic_vector(3 downto 0));end jianbie;architecture one of jianbie issignal tmp:std_logic;beginprocess(A,B,C,D,RST1,tmp)beginif RST1='1' thentmp<='1';STATES<="0000";elsif tmp='1' thenif (A='1'AND B='0'AND C='0'AND D='0' ) thenA1<='1'; B1<='0'; C1<='0'; D1<='0'; STA TES<="0001"; tmp<='0';ELSIF (A='0'AND B='1'AND C='0'AND D='0') THENA1<='0'; B1<='1'; C1<='0'; D1<='0';STATES<="0010";tmp<='0';ELSIF (A='0'AND B='0'AND C='1'AND D='0') THENA1<='1'; B1<='0'; C1<='1'; D1<='0'; STATES<="0011"; tmp<='0';ELSIF (A='0'AND B='0'AND C='0'AND D='1') THENA1<='0'; B1<='0'; C1<='0'; D1<='1'; STATES<="0100";tmp<='0';else tmp<='1';STATES<="0000";end if ;end if;end process p1;end one;计分模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY jifen ISPORT(RST1: IN STD_LOGIC;ADD: IN STD_LOGIC;CHOS: IN STD_LOGIC_VECTOR(3 DOWNTO 0);AA2,AA1,AA0,BB2,BB1,BB0: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CC2,CC1,CC0,DD2,DD1,DD0: OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END ENTITY jifen ;ARCHITECTURE ART OF jifen ISBEGINPROCESS(RST1,ADD,CHOS) ISV ARIABLE POINTS_A2,POINTS_A1: STD_LOGIC_VECTOR(3 DOWNTO 0);V ARIABLE POINTS_B2,POINTS_B1: STD_LOGIC_VECTOR(3 DOWNTO 0);V ARIABLE POINTS_C2,POINTS_C1: STD_LOGIC_VECTOR(3 DOWNTO 0);V ARIABLE POINTS_D2,POINTS_D1: STD_LOGIC_VECTOR(3 DOWNTO 0); BEGINIF (ADD'EVENT AND ADD='1') THENIF RST1='1' THENPOINTS_A2:="0001"; POINTS_A1:="0000";POINTS_B2:="0001"; POINTS_B1:="0000";POINTS_C2:="0001"; POINTS_C1:="0000";POINTS_D2:="0001"; POINTS_D1:="0000";ELSIF CHOS="0001" THENIF POINTS_A1="1001" THENPOINTS_A1:="0000";IF POINTS_A2="1001" THENPOINTS_A2:="0000";ELSEPOINTS_A2:=POINTS_A2+'1';END IF;ELSEPOINTS_A1:=POINTS_A1+'1';END IF;ELSIF CHOS="0010" THENIF POINTS_B1="1001" THENPOINTS_B1:="0000";IF POINTS_B2="1001" THENPOINTS_B2:="0000";ELSEPOINTS_B2:=POINTS_B2+'1';END IF;ELSEPOINTS_B1:=POINTS_B1+'1';END IF;ELSIF CHOS="0100" THENIF POINTS_C1="1001" THENPOINTS_C1:="0000";IF POINTS_C2="1001" THENPOINTS_C2:="0000";ELSEPOINTS_C2:=POINTS_C2+'1';END IF;ELSEPOINTS_C1:=POINTS_C1+'1';END IF;ELSIF CHOS="1000" THENIF POINTS_D1="1001" THENPOINTS_D1:="0000";IF POINTS_D2="1001" THENPOINTS_D2:="0000";ELSEPOINTS_D2:=POINTS_D2+'1';END IF;ELSEPOINTS_D1:=POINTS_D1+'1';END IF;END IF;END IF;AA2<=POINTS_A2; AA1<=POINTS_A1; AA0<="0000";BB2<=POINTS_B2; BB1<=POINTS_B1; BB0<="0000";CC2<=POINTS_C2; CC1<=POINTS_C1; CC0<="0000";DD2<=POINTS_D2; DD1<=POINTS_D1; DD0<="0000"; END PROCESS;END ARCHITECTURE ART;显示模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY xianshi ISPORT(AIN4:IN STD_LOGIC_VECTOR(3 DOWNTO 0);DOUT7:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END xianshi;ARCHITECTURE ART OF xianshi ISBEGINPROCESS(AIN4)BEGINCASE AIN4 ISWHEN "0000"=>DOUT7<="0111111"; --0WHEN "0001"=>DOUT7<="0000110"; --1WHEN "0010"=>DOUT7<="1011011"; --2WHEN "0011"=>DOUT7<="1001111"; --3WHEN "0100"=>DOUT7<="1100110"; --4WHEN "0101"=>DOUT7<="1101101"; --5WHEN "0110"=>DOUT7<="1111101"; --6WHEN "0111"=>DOUT7<="0000111"; --7WHEN "1000"=>DOUT7<="1111111"; --8WHEN "1001"=>DOUT7<="1101111"; --9WHEN OTHERS=>DOUT7<="0000000";END CASE;END PROCESS;END ARCHITECTURE ART;顶端模块library ieee;use ieee.std_logic_1164.all;entity diangduan isport(EN1 : in std_logic;RST1: IN STD_LOGIC;A,B,C,D: in std_logic;ADD: in std_logic;A1:out std_logic;B1:out std_logic;C1:out std_logic;D1:out std_logic;STATES :OUT STD_LOGIC_VECTOR(3 DOWNTO 0);FIRST:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);SCOREA2,SCOREA1,SCOREA0:OUT std_logic_vector(6 downto 0);SCOREB2,SCOREB1,SCOREB0:OUT std_logic_vector(6 downto 0);SCOREC2,SCOREC1,SCOREC0:OUT std_logic_vector(6 downto 0);SCORED2,SCORED1,SCORED0:OUT std_logic_vector(6 downto 0));END diangduan;ARCHITECTURE rtl OF diangduan ISCOMPONENT jianbie ISport(EN1: in std_logic;RST1:in std_logic;A,B,C,D: in std_logic;A1:out std_logic;B1:out std_logic;C1:out std_logic;D1:out std_logic;STATES :OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT jianbie;COMPONENT jifen isPORT(RST1: IN STD_LOGIC;ADD: IN STD_LOGIC;CHOS: IN STD_LOGIC_VECTOR(3 DOWNTO 0);AA2,AA1,AA0,BB2,BB1,BB0: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CC2,CC1,CC0,DD2,DD1,DD0: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END COMPONENT jifen;COMPONENT xianshi ISPORT(AIN4: IN STD_LOGIC_VECTOR(3 DOWNTO 0);DOUT7:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END COMPONENT xianshi;SIGNAL Q: STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL AA2,AA1,AA0: std_logic_vector(3 downto 0);SIGNAL BB2,BB1,BB0: std_logic_vector(3 downto 0);SIGNAL CC2,CC1,CC0: std_logic_vector(3 downto 0);SIGNAL DD2,DD1,DD0: std_logic_vector(3 downto 0);BEGINU1:jianbie PORT MAP(EN1,RST1,A,B,C,D,A1,B1,C1,D1,STATES);-- U2:counter PORT MAP(ADD,Q,SCOREA2,SCOREA1,SCOREA0,SCOREB2,SCOREB1,SCOREB0,SCOREC2,S COREC1,SCOREC0,SCORED2,SCORED1,SCORED0);U2:jifen PORT MAP(RST1,ADD,Q,AA2,AA1,AA0,BB2,BB1,BB0,CC2,CC1,CC0,DD2,DD1,DD0);U3:xianshi PORT MAP(Q,FIRST);U4:xianshi PORT MAP(AA2,SCOREA2);U5:xianshi PORT MAP(AA1,SCOREA1);U6:xianshi PORT MAP(AA0,SCOREA0);U7:xianshi PORT MAP(BB2,SCOREB2);U8:xianshi PORT MAP(BB1,SCOREB1);U9:xianshi PORT MAP(BB0,SCOREB0);U10:xianshi PORT MAP(CC2,SCOREC2);U11:xianshi PORT MAP(CC1,SCOREC1);U12:xianshi PORT MAP(CC0,SCOREC0);U13:xianshi PORT MAP(DD2,SCORED2);U14:xianshi PORT MAP(DD1,SCORED1);U15:xianshi PORT MAP(DD0,SCORED0);END rtl;。

一、实验目的设计一个四人抢答器:1、四人参赛,每人一个按钮,主持人一个按钮,按下就复位使得所有输出无效,抬起时开始抢答。

2、每人一个发光二极管,抢中者灯亮。

3、用一个数码管计时,0、1、2、3、4、5、6、7、8、9。

4、抢答开始时,优先抢答者灯亮,并有10秒的时间回答,自己的发光二极管始终亮,若计时到9时无回答,则答题无效,灯熄灭,抢答重新开始。

二、实验电路设计图及实验原理由三部分组成,第一部分为抢答器,此部分为关键,实现四人的抢答优先判断功能;第二部分为计时器,对答题者限制时间,从抢答开始必须在10秒内回答;第三部分为七段译码器,是计时器的输出连接到实验箱的七段数码管的各个管脚上。

各个部分器件的设计如下:其中QIANGDA器件:其中调用了元件kongzhi:其中又调用了元件suo:以上整个QIANGDA部分用图表示相当于:SA、SB、SC、SD为四位抢答者的输入,R为主持人的输入,QA、QB、QC、QD为四个抢答者的输出。

当初始状态时,主持人按下复位键,锁存器R输入为0,所有输出均为0,则B端均为1;开始抢答后,主持人抬起复位键,所有R输入变为1,等待抢答;当第一个人抢答后,其锁存器的S端输入为0,则其输出变为1,同时所有B 端变为0,所有S端变为1,使四个锁存器均维持原值,即优先抢答者输出仍为1,其他三人无论输入如何其输出均为0,实现抢答功能。

其中JISHI器件:此部分为计时功能,当有人抢答开始,从0计时,每个时钟上升沿时计数加1,到9后计时结束。

其中QIDUAN器件:D为四位输入,Q为七位输出,从高位到低位分别于七段译码器的a~g 相连。

当D为0时,使七段数码管输出0,当D为1时,使七段数码管输出1……当D为9时,使七段数码管输出9。

三、测试结果管脚锁定:下载到实验箱上时,时钟信号CLK锁到管脚122,四个抢答者的输入端SA、SB、SC、SD分别锁到管脚86、87、88、89,主持人输入端锁到管脚72,四个输出QA、QB、QC、QD分别锁到管脚41、39、38、37,Z锁到管脚8使一个数码管工作,Q6锁到管脚51,Q5锁到管脚49,Q4锁到管脚48,Q3锁到管脚47,Q2锁到管脚46,Q1锁到管脚44,Q0锁到管脚43,使数码管显示示数。

燕山大学EDA课程设计报告书题目:智力竞赛抢答器姓名:韩承姣、彭赛、袁广召班级:电子信息工程2班学号:************120104020046120104020047成绩:一、设计题目及要求题目名称:智力竞赛抢答器要求:1.10人参赛每人一个按钮,主持人一个按钮,按下就开始;2.每人一个发光二极管,抢中者灯亮;同时用两位数码管显示抢中的选手编号(01号~10号),无人抢答时显示00。

3.有人抢答时,喇叭响两秒钟;4.答题时限为10秒钟,从有人抢答开始,用一位数码管倒计时间,0、9、8…1、0;倒计时到0的时候,蜂鸣器响两秒。

5. 设置加分和扣分按钮,答对一题按一次加分键加2分,答错按一次扣分键扣1分;用两位数码管显示得分情况,注意:显示其中一名选手的得分即可。

二、设计过程及内容(包括○1总体设计的文字描述,即由哪几个部分构成的,各个部分的功能及如何实现方法;○2主要模块比较详尽的文字描述,并配以必要的图片加以说明,但图片数量无需太多)由上图可知我们的总电路由七个模块组成,下面来分别介绍一下它们模块一:10人抢答电路模块功能:该模块中主持人开关负责清零,平时状态下为低电平使74273芯片一直处于清零状态,抢答无效;当该开关为高电平时开始抢答,i号抢答后,相应的Qi会输出高电平,经过反相器后变为低电平,再经过与门后,与门输出变为低电平,该低电平与时钟信号相与之后仍为低电平,此时74273芯片停止工作,其他人抢答无效,第一轮抢答结束。

使主持人开关处于低电平,为第二轮抢答做准备。

(在电路图中的D触发器为防抖动电路)电路图:仿真结果:仿真结果说明:当可以抢答时,10,9,8,7,都抢答,最终显示的是最先抢答的10号,其余抢答都没有效。

模块二:分频模块功能:该模块利用3个74160芯片来构成0~365循环,当给进脉冲为366HZ时,该模块的输出进位1即为1HZ ,此时分频后信号的每个周期为1s,为以后10s倒计时做准备。

EDA课程设计设计题目:智力竞赛抢答器一.电路功能:可满足8个组,同时参加竞赛。

抢答器复位后,数码显示为0,在竞赛主持人出完题并示意抢答开始后,每个组都可以通过各自的按钮开关发出抢答信号,抢答器一旦接收到某组最先发出的信号后,立即让数码管显出该组的组号,同时发出音响提示,且对后来组发出的抢答信号一律不与理睬。

主持人用复位钮复位抢答器,数码显示归0,提示音停止,在抢答组回答完问题后,重复前述过程,可进行下一题抢答。

二.原理框图(见附图)三.设计要求用VHDL语言描述抢答器逻辑功能,经编译后仿真,仿真波形正确后,加上段码译码器编译通过后方可在实验箱上下载,做真实电路验证。

四. 撰写设计报告给出设计方案框图,包括模块的划分,信息的传递关系;给出各模块的VHDL程序;给出每个模块的仿真波形图,并附以文字说明;写出设计的心得体会和收获。

一.结构描述法1(先锁存后编码)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY scq_8 ISPORT (g: IN STD_LOGIC_VECTOR (8 DOWNTO 1); rst, en: IN STD_LOGIC;q: OUT STD_LOGIC_VECTOR (8 DOWNTO 1)); END scq_8;ARCHITECTURE one OF scq_8 ISBEGINPROCESS ( rst, en)BEGINIF rst='0' THENq<= "11111111";ELSIF en ='1' THENq<=g;END IF;END PROCESS;END one;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY bm8_4 ISPORT(d: IN STD_LOGIC_VECTOR(8 DOWNTO 1); sum: OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END bm8_4;ARCHITECTURE one OF bm8_4 ISBEGINPROCESS(d)BEGINCASE d ISWHEN "11111110" => sum<="0001";WHEN "11111101" => sum<="0010";WHEN "11111011" => sum<="0011";WHEN "11110111" => sum<="0100";WHEN "11101111" => sum<="0101";WHEN "11011111" => sum<="0110";WHEN "10111111" => sum<="0111";WHEN "01111111" => sum<="1000";WHEN OTHERS => sum<="0000";END CASE;END PROCESS;END one;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY DECL7S ISPORT(A: IN STD_LOGIC_VECTOR(3 DOWNTO 0);LED7S: OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END;ARCHITECTURE one OF DECL7S ISBEGINPROCESS(A)BEGINCASE A ISWHEN "0000" => LED7S <= "0111111";WHEN "0001" => LED7S <= "0000110";WHEN "0010" => LED7S <= "1011011";WHEN "0011" => LED7S <= "1001111";WHEN "0100" => LED7S <= "1100110";WHEN "0101" => LED7S <= "1101101";WHEN "0110" => LED7S <= "1111101";WHEN "0111" => LED7S <= "0000111";WHEN "1000" => LED7S <= "1111111";WHEN "1001" => LED7S <= "1101111";WHEN "1010" => LED7S <= "1110111";WHEN "1011" => LED7S <= "1111100";WHEN "1100" => LED7S <= "0111001";WHEN "1101" => LED7S <= "1011110";WHEN "1110" => LED7S <= "1111001";WHEN "1111" => LED7S <= "1110001";WHEN OTHERS => NULL;END CASE;END PROCESS;END;四.状态机描述法LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY qdq8_1 ISPORT(rst,clk: STD_LOGIC;g: IN STD_LOGIC_VECTOR(8 DOWNTO 1);q: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);sq: OUT STD_LOGIC );END qdq8_1;ARCHITECTURE one OF qdq8_1 ISTYPE s IS (s0,s1);SIGNAL crt_s: s;SIGNAL sum: STD_LOGIC_VECTOR(3 DOWNTO 0); BEGINPROCESS(rst,clk,g)BEGINIF rst='0' THEN crt_s<=s0;ELSIF clk'event AND clk='1' THENCASE crt_s ISWHEN s0 => q<="0000";sq<='0';CASE g ISWHEN "11111110" => sum<="0001";crt_s<=s1;WHEN "11111101" => sum<="0010";crt_s<=s1;WHEN "11111011" => sum<="0011";crt_s<=s1;WHEN "11110111" => sum<="0100";crt_s<=s1; WHEN "11101111" => sum<="0101";crt_s<=s1; WHEN "11011111" => sum<="0110";crt_s<=s1; WHEN "10111111" => sum<="0111";crt_s<=s1; WHEN "01111111" => sum<="1000";crt_s<=s1; WHEN OTHERS => crt_s<=s0;END CASE;WHEN s1 => q<=sum; sq<='1';crt_s<=s1;END CASE;END IF;END PROCESS;END one;。

EDA技术课程设计报告专业班次:111032学员姓名:方杰指导教员:朱四华设计日寸间:2013.11.13——2013.11.19海军航空工程学院四系405教研室设计课题题目:八路智力抢答器一、设计任务与要求1.抢答器同时供8名选手或8个代表队比赛,分别用8个按钮SO、S7表示。

2.设置一个系统清除和抢答控制开关S,该开关由主持人控制。

3.抢答器具有锁存与显示功能。

即选手按动按钮,锁存相应的编号,并在优先抢答选手的编号一直保持到主持人将系统清除为止。

4.抢答器具有定时抢答功能,且一次抢答的时间由主持人设定(如,30秒)。

当主持人启动"开始"键后,定时器进行减计时,同时扬声器发出短暂的声响,声响持续的时间0.5秒左右。

5.参赛选手在设定的时间内进行抢答,抢答有效,定时器停止工作,显示器上显示选手的编号和抢答的时间,并保持到主持人将系统清除为止。

6.如果定时时间已到,无人抢答,本次抢答无效,系统报警并禁止抢答,定时显示器上显示00o二、电路原理分析与方案设计设计思路:设定一条控制总线s控制整个系统的运作,高电平有效。

设定一个清零控制,用于清除上一次抢答的显示,高电平清零。

另设定了一个自主的计数器置数控制seto由于DE2板上仅提供50MHz和27MHz的时钟,需设定lpm_counter分频器(或者74LS292、74LS56分频器)对系统时钟进行分频,计数器主要是用两个74LS190,通过这两个计数器,进行30秒的倒数。

设计方案有两种:1.直接写一个程序,包括所要求的功能,2.按功能模块分别写程序,然后用原理图联系起来.三、单元电路分析与设计根据设计要求,我们把整个电路分为:抢答模块、倒计时模块、报警系统、闪烁系统、附加记录选手抢答分数模块。

在这个模块中,在主持人按下开关之前,开关控制的倒计时模块反馈一高电 平到图中的与非门中,同时74279的Q1反馈一高电平,从而使EIN'的输入为 高电平,从而使优先编码器的输出封锁在高电平,从而杜绝了在“开始前抢答有 效”问题的出现。

燕山大学EDA课程设计报告书题目:智力竞赛抢答器姓名:韩承姣、彭赛、袁广召班级:电子信息工程2班学号:120104020045120104020046120104020047 成绩:一、设计题目及要求题目名称:智力竞赛抢答器要求:1.10人参赛每人一个按钮,主持人一个按钮,按下就开始;2.每人一个发光二极管,抢中者灯亮;同时用两位数码管显示抢中的选手编号(01号~10号),无人抢答时显示00。

3.有人抢答时,喇叭响两秒钟;4.答题时限为10秒钟,从有人抢答开始,用一位数码管倒计时间,0、9、8…1、0;倒计时到0的时候,蜂鸣器响两秒。

5. 设置加分和扣分按钮,答对一题按一次加分键加2分,答错按一次扣分键扣1分;用两位数码管显示得分情况,注意:显示其中一名选手的得分即可。

二、设计过程及内容(包括○1总体设计的文字描述,即由哪几个部分构成的,各个部分的功能及如何实现方法;○2主要模块比较详尽的文字描述,并配以必要的图片加以说明,但图片数量无需太多)由上图可知我们的总电路由七个模块组成,下面来分别介绍一下它们模块一:10人抢答电路模块功能:该模块中主持人开关负责清零,平时状态下为低电平使74273芯片一直处于清零状态,抢答无效;当该开关为高电平时开始抢答,i号抢答后,相应的Qi会输出高电平,经过反相器后变为低电平,再经过与门后,与门输出变为低电平,该低电平与时钟信号相与之后仍为低电平,此时74273芯片停止工作,其他人抢答无效,第一轮抢答结束。

使主持人开关处于低电平,为第二轮抢答做准备。

(在电路图中的D触发器为防抖动电路)电路图:仿真结果:仿真结果说明:当可以抢答时,10,9,8,7,都抢答,最终显示的是最先抢答的10号,其余抢答都没有效。

模块二:分频模块功能:该模块利用3个74160芯片来构成0~365循环,当给进脉冲为366HZ时,该模块的输出进位1即为1HZ ,此时分频后信号的每个周期为1s,为以后10s倒计时做准备。

(因为该模块原理简单不再附相应电路图)模块三:喇叭模块功能:当有人抢答时,T触发器的脉冲控制端由低电平变为高电平,此时T触发器触发,Q由0变为1,蜂鸣器开始发出响声,74160芯片开始工作进行0~2的循环,当输出端为0010时(此时QB输出为1),QB的输出经过反相器变为0作用在LDN端使芯片清零,同时到达T触发器的CLRN端使触发器清零,也使蜂鸣器停止发出响声。

在该过程中蜂鸣器共响了两秒。

(该电路中QB的输出端后经过的D触发器是为了滤除毛刺确保QB的输出端不再有其他状态。

)电路图:仿真结果:仿真结果说明:8号抢答后,喇叭响了2秒。

模块四:组号显示该图有10个输入端,8个输出端,中间由几个或门连接,一次只会有一个信号输入,当其中一个有信号输入时,通过几个或门,输出信号为二进制该组号,其中4个为个位,另外4个为十位。

如:当7号有信号输入时,后方输出为0000 0111;当10号有信号输入时,后方输出为0001 0000。

该图用来分别显示抢答的组号。

模块五:扫描器该图由一个八进制,四个8位数据选择器,一个7448译码器,一个与非门组成,有一个时钟信号,。

数据选择器上为各个需要选择的输入信号。

数据选择器上有各个需要选择的信号输入段,当有时钟信号是,开始运作,八进制数输出S1、S2、S3由000开始运行,当到达111时,通过与非门信号输出0进入八进制器使重新从000开始运行。

如当S1、S2、S3为010时,4个8位数据选择器上输入段A1、B1、C1、D1信号输入可以通过数据选择器接入到译码器中,通过译码器输出端的7个接口接到数码管上来显示这4个信号显示的数值。

而S1、S2、S3输出接到数码管上的3个选择接口使数码管应该显示的数码管显示。

模块六:倒计时模块倒计时模块要实现的功能为,从有人抢答开始,用一位数码管倒计时间,0、9、8…1、0;倒计时到0的时候,蜂鸣器响两秒。

要实现倒计时功能,则需要由74191组成的十六进制加减法计数器,74191计时器保留预制置数端,预置数为1010,CP信号端输入1Hz的触发脉冲信号;要实现蜂鸣器响两秒,需要由74160组成的十进制加法计数器,74160计时器保留预制置数端,预置数为0000,CP信号端输入1Hz 的触发脉冲信号。

设计电路如图1当bian输入由低电平变为高电平时(即有人抢答时),T触发器由初状态0翻转为1,此时开始倒计时,由10倒计时到0。

74191输出信号经或门输出到D触发器中,同时74191的输出信号用或非门输入到74160,倒计时结束即输出为0000时,或门输出信号经D触发器延迟(使74191倒计时时可以显示出0)后输入到T触发器的CLRN端使T触发器清零,74191停止倒计时;同时,或非门输出信号由低电平变为高电平,T触发器由初状态0翻转为1,此时74160开始计数,蜂鸣器开始蜂鸣,当74160计数到0010时,输出端经与非门输入到T触发器的CLRN端使T触发器清零,蜂鸣器停止蜂鸣,74160停止计时。

仿真结果如图2,仿真结果图显示,当输入信号bian变为高电平时,开始倒计时当十秒倒计时完毕后,蜂鸣器蜂鸣两秒,计时结束,整个模块停止工作。

模块七:记分器模块记分器模块要实现的功能是,答对一题按一次加分键加2分,答错按一次扣分键扣1分。

要实现按一次加分键加两分,则需要一个由74160组成的十进制计数器实现按一次加分键给计分器两个信号,74160计时器保留预制置数端,预置数为0000,CP信号端输入触发脉冲信号。

同理,要实现按一次减分键减一分,需要一个由74160组成的十进制计数器实现按一次减分键给记分器一个信号。

要实现加减计分,则需要由两个74168组成的十进制的加减计数器。

两个74168计时器保留预制置数端,预置数为0000,CP信号端输入触发脉冲信号,上升沿为触发信号触发74168。

U/DN为高电平时74168为加法计数器状态,当输出为9时TCN为低电平,当U/DN为低电平时74168为减法计数器,当输出为0时TCN为低电平。

设计电路如图3当答题正确时,主持人按一次加分键,加分信号端由低电平转为高电平(D触发器为防抖动电路),此时74168处于加法计数器状态,加分信号输入到T触发器使其由初状态0翻转为1,使74160开始计数,由0000计数到0100时输出信号经反相器输入到74160和T触发器的CLRN端清零,使74160停止工作。

74160输出端Q0信号给74168,当74160计数时,Q0变化0-1-0-1-0,即传给74168两个脉冲信号,此时74168加两个数后停止计数等待下一次加减分信号。

同理,当答题错误时,主持人按一次减分键,减分信号端由低电平转为高电平(D触发器为防抖动电路),此时74168处于减法计数器状态,减分信号输入到T触发器使其由初状态0翻转为1,使74160开始计数,由0000计数到0010时输出信号经反相器输入到74160和T触发器的CLRN 端清零,使74160停止工作。

74160输出端Q0信号给74168,当74160计数时,Q0变化0-1-0,即传给74168一个脉冲信号,此时74168减一个数后停止计数等待下一次加减分信号。

加分信号时,个位74168和十位74168均处于加法计数器状态,个位74168计数到9时再计数,TCN由低电平变为高电平,给十位74168一个触发信号,使十位74168加一个数,实现进位;减分信号时,个位74168和十位74168均处于减法计数器状态,个位74168计数到0时再计数,TCN 由低电平变为高电平,给十位74168一个触发信号,使十位74168减一个数,实现借位。

仿真结果如图4,仿真结果显示第一次加分信号为高电平,计数器显示为2,第二次加分信号为高点,显示结果为4,第三次减分信号为高电平,显示为3,第四次加分信号为高电平,显示结果为5,第五次加分信号为高电平,显示结果7,第六次加分信号为高电平,显示结果为9,第七次加分信号为高电平,显示结果为11,实现进位。

三、设计结论(包括设计过程中出现的问题;对EDA课程设计感想、意见和建议)韩承姣:我主要进行的是10人抢答电路的设计,分频器设计,喇叭响两秒模块的设计。

1.(1)在开始进行抢答设计时曾利用10个D触发器分别进行设计,该方法虽然与我们现在用的集成D触发器芯片原理相同但设计过程极其繁琐,而且连线多,密很容易出错。

(2)开始时对试验箱不熟悉,在主持人选用哪种开关上有多余考虑。

2.在进行喇叭模块设计时,最开始使用的是D触发器进行对芯片进行控制,后来仿真时发现喇叭不受抢答信号的控制,最后经过试验改为T触发器。

3.该次EDA设计对我的感触:第一点,我的理论知识不错,但把理论知识转化为解决实际问题的能力太差,独立思考的能力有待提高,在以后的课堂理论学习过程中注重老师提出的锻炼人思维的问题。

第二点,在这次的设计中有些过于急切,没把老师给的相应资料看全,所以在设计时有些模块时花费时间过多,有些模块经过同学提醒才知道。

彭赛:在这次EDA设计中,我主要负责的是倒计时模块和记分器模块。

在设计仿真中,不断出错不断改正,同时自己也有一些深刻体会。

1、在倒计时模块,我发现虽然电路图逻辑上是正确的,但是计算机并不是理想状态的仿真,有时会出现毛疵,因此我们要根据实际情况来调试改正原理图,不能只追求逻辑上的正确。

2、在记分器模块遇到的问题最多,无论是设计过程中还是仿真过程中。

在设计期间我发现自己有很多不懂的知识,都要通过查书来获得。

仿真过程中也总是有些问题,一遍遍调试,一遍遍仿真改正。

这些情况让我发现了自己的优点也发现了自己的缺点,在这过程中我懂得了在保持自己活跃的思维及还可以的动手能力的情况下,我更要加强自己的知识储备量,努力扩充完善自己的理论知识。

经过一个多星期的努力,从最初的毫无头绪,到后来的逐渐完成。

在整个完成过程中,我得到了老师和同学的大力帮助,非常感谢他们。

袁广召:实验中,我深刻的体会到在设计过程中,需要反复实践,其过程很可能相当烦琐,有时花很长时间设计出来的电路还是需要重做,那时心中未免有点灰心,有时还特别想放弃,此时更加需要静下心,查找原因。

设计思路是最重要的,只要你的设计思路是成功的,那你的设计已经成功了一半。

因此我们应该在设计前做好充分的准备,像查找详细的资料,为我们设计的成功打下坚实的基础。

(注:可编辑下载,若有不当之处,请指正,谢谢!)。