基于单片机与FPGA的等精度频率计设计

- 格式:pdf

- 大小:263.11 KB

- 文档页数:4

基于单片机和FPGA的等精度频率计一、设计任务工作频率通信系统极为重要的参数,频率测量是通信系统基本的参数测试之一。

本设计的主要任务是使用单片机与 EDA 技术设计制作一个简易的等精度频率测试仪,可对输入周期信号的频率进行测量、显示。

被测信号的频率范围和测试的精度要求见相应的设计任务书。

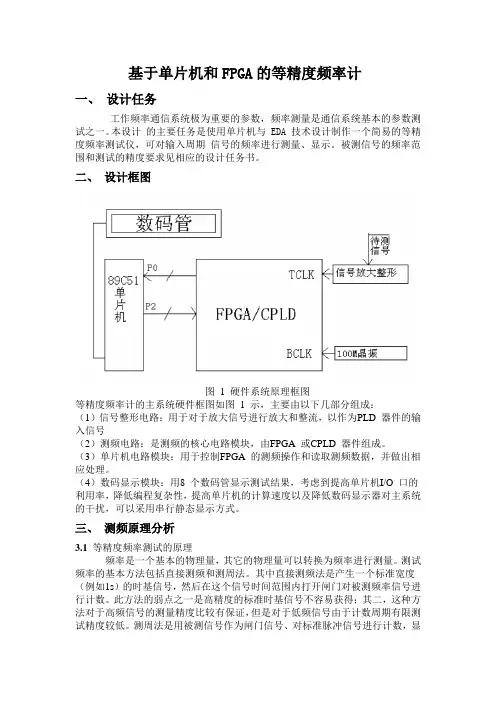

二、设计框图图 1 硬件系统原理框图等精度频率计的主系统硬件框图如图1 示,主要由以下几部分组成:(1)信号整形电路:用于对于放大信号进行放大和整流,以作为PLD 器件的输入信号(2)测频电路:是测频的核心电路模块,由FPGA 或CPLD 器件组成。

(3)单片机电路模块:用于控制FPGA 的测频操作和读取测频数据,并做出相应处理。

(4)数码显示模块:用8 个数码管显示测试结果,考虑到提高单片机I/O 口的利用率,降低编程复杂性,提高单片机的计算速度以及降低数码显示器对主系统的干扰,可以采用串行静态显示方式。

三、测频原理分析3.1 等精度频率测试的原理频率是一个基本的物理量,其它的物理量可以转换为频率进行测量。

测试频率的基本方法包括直接测频和测周法。

其中直接测频法是产生一个标准宽度(例如1s)的时基信号,然后在这个信号时间范围内打开闸门对被测频率信号进行计数。

此方法的弱点之一是高精度的标准时基信号不容易获得;其二,这种方法对于高频信号的测量精度比较有保证,但是对于低频信号由于计数周期有限测试精度较低。

测周法是用被测信号作为闸门信号、对标准脉冲信号进行计数,显然这种方法适合测量低频信号的频率。

等精度测频法的核心思想是用两个计数器分别对标准和被测脉冲进行计数,计数的时间严格同步于被测脉冲。

这种方法的最大优点是测试的精度和被测信号的频率无关,因而可以做到等精度测量。

其测试原理如图2 示。

预置闸门信号是测试命令,即测频的使能信号,该信号为高电平的期间进行测频。

但是当预置闸门信号为高电平时,测频并不是立即开始,而是要等到被测信号的上升沿到来以后,实际闸门信号跳为高电平,测频才真正开始。

第一章课题研究概述1.1课题研究的目的和意义在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此,频率的测量就显得更为重要。

测量频率的方法有多种,其中电子计数器测量频率具有精度高、使用方便、测量迅速,以及便于实现测量过程自动化等优点,是频率测量的重要手段之一。

目前常用的测频方案有三种:方案一:完全按定义式F=NT进行测量。

被测信号Fx经放大整形形成时标ГX,晶振经分频形成时基TR。

用时基TR开闸门,累计时标ГX 的个数,则有公式可得Fx=1ГX=NTR。

此方案为传统的测频方案,其测量精度将随被测信号频率的下降而降低。

方案二:对被信号的周期进行测量,再利用F=1T(频率=1周期)可得频率。

测周期时,晶振FR经分频形成时标ГX,被测信号经放在整形形成时基TX控制闸门。

闸门输出的计数脉冲N=ГXTR,则TX=NГX。

但当被测信号的周期较短时,会使精度大大下降。

方案三:等精度测频,按定义式F=NT进行测量,但闸门时间随被测信号的频率变化而变化。

如图1所示,被测信号Fx经放大整形形成时标ГX,将时标ГX经编程处理后形成时基TR。

用时基TR开闸门,累计时标ГX的个数,则有公式可得Fx=1ГX=NTR。

此方案闸门时间随被测信号的频率变化而变化,其测量精度将不会随着被测信号频率的下降而降。

本次实验设计中采用的是第三种测频方案。

等精度频率计是数字电路中的一个典型应用,其总体设计方案有两种:方案一:采用数字逻辑电路制作,用IC拼凑焊接实现。

其特点是直接用现成的IC组合而成,简单方便,但由于使用的器件较多,连线复杂,体积大,功耗大,焊点和线路较多将使成品稳定度与精确度大打折扣,而且会产生比较大的延时,造成测量误差、可靠性差。

方案二:采用可编程逻辑器件(CPLD)制作。

随着现场可编程门阵列FPGA的广泛应用,以EDA工具作为开发手段,运用VHDL等硬件描述语言语言,将使整个系统大大简化,提高了系统的整体性能和可靠性。

基于单片机IP核的等精度频率计设计摘要FPGA就是目前最受欢迎的可编程逻辑器件之一。

IP核是将一些在数字电路中常用但比较复杂的功能模块,设计成可修改参数的模块,让用户可以直接调用这些模块。

随着FPGA的规模越来越大,使用IP核是一个发展趋势。

传统测频原理的频率计的测量精度将随被测信号频率的下降而下降,在使用中有较大的局限性,而等精度频率计不但具有较高的测量精度,而且整个频率区域能保持恒定的测试精度。

本文结合FPGA与8051单片机的优点实现了基于FPGA的8051 IP核应用,设计一个等精度频率计。

关键词:FPGA,8051IP核,等精度频率计设计AbstractField Programmable Gate Array(FPGA)is one of the most welcomed programmable logic devices.IP core is a module which has changeable parameters.With the IP core we can implement some complex functional module in digital circuits.With the increasing scale in the FPGA,Using IP core is becoming more and more popular.Traditional frequency measurement principle of the frequency accuracy will decline with the decline of the signal frequency.It Has a greater limitations in use. Equal precision frequency meter not only has high measurement accuracy, and the whole frequency region can maintain a constant test accuracyCombining the advantages of FPGA and 805 l MCU,the paper mainly realize the application of 8051 IP core based on FPGA that design a same accuracy frequency.Key words: FPGA,8051 IP core,same accuracy frequency目录第一章绪论 (3)1.1 课题研究背景及意义 (3)1.2 主要任务 (3)第二章杭州康芯公司KX2C5F+开发板介绍 (5)2.1 KX2C5F+系统简介 (5)2.2 主要应用 (5)第三章系统设计 (7)3.1 8051单片机介绍 (7)3.2 8051单片机IP软核介绍 (7)3.3 8051单片机IP软核实用系统构建 (9)3.4 等精度频率计设计 (10)3.4.1等精度测频原理 (10)3.4.2等精度测频实现 (11)3.4.3测量占空比的原理 (13)3.4.4测量占空比的实现 (13)3.5单片机的功能 (14)3.5.1数据传输 (14)3.5.2 液晶显示 (15)3.6单片机与FPGA的组合应用 (16)第四章程序调试 (17)4.1 等精度频率计程序 (17)4.2 单片机程序和VHDL程序编译在一起下载到FPGA中 (17)第五章结果讨论 (19)总结 (20)致谢 (21)参考文献 (22)附录 (23)附录1:等精度频率计相关程序 (23)附录2 单片机相关程序 (25)第一章绪论1.1 课题研究背景及意义随着可编程逻辑设计技术的发展,每个逻辑器件中门电路的数量越来越多,一个逻辑器件就可以完成本来由很多分立逻辑器件和存储芯片完成的功能。

1.设计原理描述考虑到只基于单片机的频率测量计设计主要是以单片机为基础,原理简单,但由于自身精度问题,测量的范围小。

而基于FPGA 和单片机结合的频率测量设计主要是以单片机作为系统的主控部件,FPGA 完成对时序逻辑控制、计数功能,能较好的利用了FPGA 的高精度、高速等方面的优势。

所以,本次智能仪器的大作业我采用的是单片机作为系统的主控部件,实现整个电路的测试信号控制、数据运算和控制数码管的显示输出等。

一块复杂的现场可编程门阵列芯片完成各种时序逻辑控制、计数功能。

被测信号图 1系统组成原理框图如图1所示。

由一片FPGA 完成各种测试功能,对标准频率(采用系统内部时钟)和被测信号进行计数。

单片机对整个测试系统进行控制,包括对FPGA 测量过程的控制、测量结果资料的处理、键控制信号的读入与处理,最后将测量结果送LED 显示。

被测信号整形部分主要对被测信号限幅、放大再经过整形后送入FPGA 。

FPGA 的标准测试频率为40MHz 。

单片机由外接12MHz 标准晶振提供时钟电路。

其核心部分为单片机和可编程芯片FPGA 。

所有信号包括基准频率信号、被测信号以及自校输入信号均可在430单片机的控制下送入FPGA 芯片中,单片机将每次测试结果读入内存RAM 中,经运算处理后,送入12864显示电路显示。

用单片机软件查询键盘控制命令情况,实现开始功能、预置门时间控制功能等。

F PGA 单 片 机 放大整形 数码管显示4.硬件的单元模块设计4.1信号整形电路为了提高共模抑制比和输入信号的范围,由AD620构成前置放大电路。

放大后的信号经过耦合电容去掉直流,再由LM311组成的过零比较电路整形为方波,施密特触发器74HC14去抖后送入FPGA测量频率。

电路如图图4-1 被测信号整形电路4.2 单片机主控模块单片机测频控制电路如图4-2所示,由单片机完成整个测量电路的测试控制、数据处理和显示输出,FPGA完成各种测试功能。

基于FPGA和单片机的高精度数字频率计的设计与实现【摘要】本文介绍了基于FPGA和单片机的高精度数字频率计的设计与实现。

在文章阐述了研究背景、研究意义和研究内容。

在首先介绍了数字频率计的工作原理,然后分别讨论了基于FPGA和单片机的数字频率计的设计方案。

接着详细描述了硬件系统设计和软件系统设计。

在通过实验结果分析展示了设计的可靠性和高精度性能,并总结了设计的优缺点。

展望未来发展方向,提出了进一步优化和改进的建议。

通过本文的研究与实现,可为数字频率计的设计提供一种更高精度和更有效的解决方案,具有较好的应用前景和推广价值。

【关键词】FPGA、单片机、高精度数字频率计、硬件系统设计、软件系统设计、实验结果分析、设计优缺点总结、未来展望、数字频率计的原理、基于FPGA的设计、基于单片机的设计、研究背景、研究意义、研究内容。

1. 引言1.1 研究背景数字频率计是一种广泛应用于电子领域的重要仪器,用于准确测量信号的频率。

随着现代电子设备对频率精度的要求日益提高,高精度数字频率计的研究与应用变得越来越重要。

目前市面上的数字频率计大多基于FPGA或单片机进行设计,这两种方案各有优劣。

基于FPGA的数字频率计可以实现高速、高精度的频率测量,适用于需要处理大量数据的场景。

而基于单片机的数字频率计则更便于实现低功耗、低成本的设计,适用于对精度要求不是特别高的场合。

目前关于基于FPGA和单片机的高精度数字频率计设计的研究还比较有限,对于如何结合FPGA和单片机的特点,设计出既具有高精度又具有低成本的数字频率计仍有待探讨。

本文将重点研究基于FPGA和单片机的高精度数字频率计的设计与实现,旨在探讨如何充分发挥两者的优势,实现高精度、低成本的频率测量系统。

通过本研究,有望为数字频率计的设计与应用提供新的思路和方法。

1.2 研究意义数字频率计是现代电子技术中常用的一种测量设备,可以用于测量各种信号的频率。

随着科学技术的不断发展,对数字频率计的精度和性能要求越来越高。

基于FPGA和单片机的高精度数字频率计的设计与实现1. 引言1.1 背景介绍数字计数器是一种广泛应用于科学研究、工程技术和日常生活中的仪器设备,用于测量信号的频率、周期和脉冲数量等。

随着科技的不断发展,对于数字频率计的精度和性能要求也越来越高。

传统的数字频率计主要基于单片机或专用芯片的设计,存在精度受限、功能单一等问题。

而基于FPGA和单片机的高精度数字频率计能够充分发挥FPGA在并行计算和高速数据处理方面的优势,结合单片机的灵活性和易编程性,实现更高精度、更丰富功能的数字频率测量。

本文基于FPGA和单片机,设计并实现了一种高精度数字频率计,具有高度精准、快速响应的特点。

通过软硬件结合的设计思路,实现了数字信号频率的精确测量,同时在硬件设计和软件设计上都进行了详细优化和实现。

系统测试结果表明,该数字频率计具有较高的测量精度和稳定性,在实验中取得了良好的效果和准确的测量数据。

此设计不仅具有实用价值,还对数字频率计的进一步研究和应用具有一定的参考意义。

1.2 研究意义随着科技的发展,对于频率计的要求也越来越高,需要具备更高的精度、更快的响应速度和更广泛的适用范围。

设计和实现基于FPGA 和单片机的高精度数字频率计具有重要的研究意义。

通过本文的研究,可以深入了解数字频率计的工作原理和设计方法,为高精度频率计的研究和应用提供参考和借鉴。

本文的研究成果还可以为提高电子测量仪器的性能,推动数字频率计技术的发展做出重要的贡献。

本文的研究具有重要的理论和实践意义。

1.3 研究现状当前,数字频率计在电子测量领域具有重要的应用价值,其精度和稳定性对于提高测量精度和准确性至关重要。

目前,数字频率计的研究主要集中在硬件设计和软件算法的优化上。

在硬件设计方面,传统的数字频率计主要采用FPGA(现场可编程门阵列)作为核心控制器,实现高速、高精度的频率测量。

通过合理的电路设计和时序控制,可以实现更稳定和准确的频率计算。

在软件设计方面,研究者们致力于优化频率计算算法,提高频率计算的速度和精度。

基于FPGA 与单片机的等精度频率计的设计李国利,刘旭明,翟力欣(金陵科技学院机电工程学院,江苏南京211169)摘要:根据等精度测量原理,设计了一种基于FPGA 和单片机的等精度频率计。

系统主要包括信号预处理电路、单片机控制电路、FPGA 测频电路和显示电路等。

被测频率信号和标准频率信号经过整形放大处理后输入FPGA ,单片机控制FPGA 对两路信号进行计数并读取测频数据,单片机将读取的测频数据经过运算处理后显示。

测试结果表明,该频率计实现了整个频率测量范围内的测量精度相等,测量精度高,稳定性好。

关键词:频率计;等精度;FPGA ;单片机中图分类号:TN492文献标识码:A文章编号:1674-6236(2013)22-0171-03Design of equal precision cymometer based on FPGA and SCMLI Guo -li ,LIU Xu -ming ,ZHAI Li -xin(School of Mechanical and Electronic Engineering ,Jinling Institute of Technology ,Nanjing 211169,China )Abstract:According to the principle of equal precision measurement ,a cymometer was designed based on FPGA and single -chip microcomputer.This system was mainly composed of the signal amplification shaping circuit ,single -chip microcomputer control circuit ,FPGA frequency measurement circuit and the signal display circuit.After amplification and rectification ,the signal to be measured and the standard signal were input into FPGA.Two signals were counted in FPGA and controlled by single -chip microcomputer.After received the measuring frequency data ,single -chip microcomputer calculated and processed it ,and the result of measure was shown.The experiments show that ,the cymometer has equal measurement accuracy within the whole frequency measuring range ,and it has the advantages of high measuring precision and good operation stability.Key words:cymometer ;equal precision ;FPGA ;SCM收稿日期:2013-04-15稿件编号:201304182基金项目:金陵科技学院青年教师科研基金项目(JIT-B-201220)作者简介:李国利(1973—),男,山东滨州人,硕士,副教授。

第一章课题研究概述1.1课题研究的目的和意义在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此,频率的测量就显得更为重要。

测量频率的方法有多种,其中电子计数器测量频率具有精度高、使用方便、测量迅速,以及便于实现测量过程自动化等优点,是频率测量的重要手段之一。

目前常用的测频方案有三种:方案一:完全按定义式F=N/T进行测量。

被测信号Fx经放大整形形成时标ГX,晶振经分频形成时基TR。

用时基TR开闸门,累计时标ГX的个数,则有公式可得Fx=1/ГX=N/TR。

此方案为传统的测频方案,其测量精度将随被测信号频率的下降而降低。

方案二:对被信号的周期进行测量,再利用F=1/T(频率=1/周期)可得频率。

测周期时,晶振FR经分频形成时标ГX,被测信号经放在整形形成时基TX控制闸门。

闸门输出的计数脉冲N=ГX/TR,则TX=NГX。

但当被测信号的周期较短时,会使精度大大下降。

方案三:等精度测频,按定义式F=N/T进行测量,但闸门时间随被测信号的频率变化而变化。

如图1所示,被测信号Fx经放大整形形成时标ГX,将时标ГX经编程处理后形成时基TR。

用时基TR开闸门,累计时标ГX的个数,则有公式可得Fx=1/ГX=N/TR。

此方案闸门时间随被测信号的频率变化而变化,其测量精度将不会随着被测信号频率的下降而降。

本次实验设计中采用的是第三种测频方案。

等精度频率计是数字电路中的一个典型应用,其总体设计方案有两种:方案一:采用数字逻辑电路制作,用IC拼凑焊接实现。

其特点是直接用现成的IC组合而成,简单方便,但由于使用的器件较多,连线复杂,体积大,功耗大,焊点和线路较多将使成品稳定度与精确度大打折扣,而且会产生比较大的延时,造成测量误差、可靠性差。

方案二:采用可编程逻辑器件(CPLD)制作。

随着现场可编程门阵列FPGA的广泛应用,以EDA工具作为开发手段,运用VHDL等硬件描述语言语言,将使整个系统大大简化,提高了系统的整体性能和可靠性。

摘要频率是常用的物理量,工程中很多物理量的测量,如时间测量、速度控制等,都可转化为频率测量。

此外,还经常遇到以频率为参数的测量信号,例如流量、转速等。

所以频率测量方法的研究越来越受到重视。

基于传统测频原理的频率计的测量精度将随被测信号频率的下降而降低,在实用中有较大的局限性, 而等精度频率计不但具有较高的测量精度, 而且在整个频率区域能保持恒定的测试精度。

本课题设计的等精度数字频率计是采用当今电子设计领域流行的EDA技术,以FPGA为核心,配合STC89C51单片机。

同时,采用等精度测频原理,实现了0.01Hz--50MHz信号频率的等精度频率测量。

此外,该系统还实现测量周期、脉宽、占空比等功能。

设计中用一块FPGA芯片EP2C5Q208C8完成各种时序逻辑控制、计数功能。

在Ouartus II平台上,用VHDL语言编程完成FPGA的软件设计、编译、调试、仿真和下载。

用STC89C51单片机作为系统的主控部件,实现整个电路的测试信号控制、数据运算处理、键盘扫描和控制数码管的显示输出。

系统将单片机STC89C51的控制灵活性及FPGA芯片的现场可编程性相结合,不但大大缩短了开发研制周期,而且使本系统具有结构紧凑、体积小,可靠性高,测频范围宽、精度高等优点。

关键词:频率计;EDA技术;FPGA;单片机AbstractFrequency is commonly used physical quantity, lots of measurement of physical quantity in the project, such as the measurement of time, the control of velocity, can be changed into the measurement of frequency. Besides, the measured signal with a frequency parameter, such as the rate of flow, the rotational speed, is often encountered. So the research of the method of measuring frequency has become more and more significant in the real application.According to the principles of traditional frequency measurement , the measurement accuracy of frequency meter will decrease with the signal frequency decrease .but it has more limitations in the real application, equal precision frequency meter not only has high accuracy, but also maintains constant test accuracy in the whole frequency region .With the help of FPGA and cooperating with the single chip computer STC89C51,The digital frequency design in our program has realized the precision measurement of 0.01Hz-50MHz signal frequency by adopting the current EDA technique prevailing in the electronic designs and using the principle of multi-period synchrony frequency measurement. Besides, the system can complete the cycle, pulse width, duty cycle measurement function .In this design, using an FPGA chip EP2C5Q208C8 completes a variety of temporal logic control and counting function. In the platform of Ouartus II, using VHDL language completes FPGA software design, compiler, debugging, simulation, and download. By use of the STC89C51 single chip computer as the main controlling parts, the control of the tested signal, the scan of keyboard and the output display of LED can be realized. The system combines the control flexibility of STC89C51 with programmable performance of FPGA, consequently,not only can it shorten the period of the development and research, but also it has the advantages of compact structure, little volume, high reliability, wide scope and high precision. Keywords:Frequency meter,EDA technique,FPGA, Single chip computer目录摘要 (I)Abstract (II)目录 (III)1 绪论 (1)1.1 本课题的研究背景及意义 (1)1.2 本课题的主要内容 (2)2 系统设计的相关理论 (3)2.1 频率测量方法的研究 (3)2.1.1 常用测频方案 (3)2.1.2 等精度测频原理 (3)2.1.3 等精度测频误差分析 (5)2.2 单片机模块理论及知识 (5)2.2.1 MCS-51单片机结构简介 (5)2.2.2 Keil μvision 3软件概述 (7)2.2.3 Proteus软件概述 (7)2.3 FPGA模块理论及知识 (8)2.3.1 FPGA原理概述 (8)2.3.2 Quartus II 软件概述 (9)2.3.3 VHDL语言简介及开发优点 (11)3 系统硬件电路设计 (13)3.1 系统顶层电路组成 (13)3.2 被测信号放大整形电路设计 (13)3.3 单片机模块设计 (14)3.3.1 单片机最小系统 (14)3.3.2 键盘接口电路 (15)3.3.3 LED数码管显示电路 (17)3.4 FPGA模块电路设计 (18)3.4.1 基本单元电路 (19)3.4.2 测量与自检选择电路 (23)3.4.3 脉宽控制电路 (24)3.4.4 测频与测周期电路 (25)3.5 单片机与FPGA的相互控制电路 (26)4 系统软件设计 (28)4.1 单片机主程序设计 (28)4.2 复位自检程序设计 (28)4.3 键盘程序设计 (29)4.4 测频子程序设计 (30)4.5 测周期子程序设计 (31)4.6 测脉宽子程序设计 (32)4.7 测占空比子程序设计 (32)4.8 LED数码管显示子程序设计 (33)5 系统性能分析 (34)5.1 测量范围分析 (34)5.2 测量精度分析 (34)5.3 被测信号幅值分析 (34)结论 (35)致谢 (36)参考文献 (37)附录一FPGA程序 (38)附录二单片机程序 (41)1绪论1.1本课题的研究背景及意义EDA(Electronic Design Automation——电子设计自动化)代表了当今电子设计技术的最新发展方向,通过VHDL(V ery High Speed Integrated Circuit Hardware Description Language)硬件描述语言的设计,用FPGA(Field-Programmable Gate Array——现场可编程门阵列)来实现小型电子设备的设计,是开发仪器仪表的主流。

基于FPGA和单片机的高精度数字频率计的设计与实现一、引言数字频率计是一种用来测量信号频率的仪器,通常用于检测和控制电子电路、通讯系统、工业自动化装置等领域。

在实际应用中,频率计对于频率的测量精度要求很高,同时还需要具备快速响应、稳定性好和抗干扰能力强等特点。

本文将介绍一种基于FPGA和单片机的高精度数字频率计的设计与实现。

二、设计原理1. 信号输入高精度数字频率计的设计首先需要对信号进行采集和处理。

通常采集的信号是来自于传感器、射频发射机、计时器等设备输出的波形信号。

这些信号可能是方波、正弦波等各种周期信号,需要进行适当的信号调理才能进行后续的数字处理。

2. FPGA实时处理FPGA(Field Programmable Gate Array,现场可编程门阵列)是一种集成了大量可编程逻辑和存储器的可重构数字电路芯片。

它的设计灵活、速度快、功耗低等特点,非常适合于数字信号处理任务。

在本设计中,FPGA用于对输入信号进行数字化、滤波、计数等处理,以提高频率计的测量精度和稳定性。

3. 单片机控制和显示单片机通常用于系统的控制和显示。

它可以对FPGA进行配置和控制,同时还可以将测量结果显示在液晶屏或者其他显示设备上,方便用户进行实时监测和操作。

三、设计流程1. 信号采集和调理首先需要对采集的信号进行滤波和数字化处理,使其能够被FPGA所识别。

这一步通常需要采用运算放大器进行信号放大、滤波等处理,使得信号的波形清晰、稳定,以便后续的数字处理。

2. FPGA处理在FPGA中,需要设计一个数字频率计的计数器,用于对输入信号的周期进行计数,从而得到它的频率。

还需要设计一个时钟模块,用于控制计数器的计数频率和精度。

五、性能测试1. 测试平台搭建搭建一个测试平台,将设计的高精度数字频率计与标准信号源相连,以验证其测量精度和稳定性。

需要设计合适的测试程序,对频率计进行全面的性能测试。

2. 测试结果分析通过对测试结果进行分析,得到设计的数字频率计的测量精度、抗干扰能力、快速响应性等性能参数。

光电与通信工程学院课程设计报告书课设名称:等精度频率计年级专业及班级:姓名:学号:一、课程设计目的1、进一步熟悉 Quartus Ⅱ的软件使用方法,熟悉 keil 软件使用;2、熟悉单片机与可编程逻辑器件的开发流程及硬件测试方法;3、掌握等精度频率计设计的基本原理。

4、掌握独立系统设计及调试方法,提高系统设计能力。

实验设备EDA最小系统板一块(康芯)、PC机一台、示波器一台、信号发生器一台、万用表一个。

二、设计任务利用单片机与FPGA设计一款等精度频率计,待测脉冲的检测及计数部分由FPGA实现,FPGA的计数结果送由单片机进行计算,并将最终频率结果显示在数码管上。

要求该频率计具有较高的测量精度,且在整个频率区域能保持恒定的测试精度,具体指标如下:a)具有频率测试功能:测频范围 100Hz~5MHz。

测频精度:相对误差恒为基准频率的万分之一。

b)具有脉宽测试功能:测试范围 10μs~1s,测试精度:0.1μs。

c)具有占空比测试功能:测试精度1%~99%。

d)具有相位测试功能。

(注:任务a 为基本要求,任务 b、c、d 为提高要求)三、基本原理基于传统测频原理的频率计的测量精度将随被测信号频率的下降而降低,在实用中有较大的局限性,而等精度频率计不但具有较高的测量精度,而且在整个频率区域能保持恒定的测试精度。

3.1 等精度测频原理等精度频率计主控结构如图 1 所示预置门控信号 CL 选择为 0.1~1s 之间(通过测试实验得出结论:CL 在这个范围内选择时间宽度对测频精度几乎没有影响)。

BZH 和 TF 分别是 2 个高速计数器,BZH 对标准频率信号(频率为 Fs)进行计数,设计数结果为 Ns;TF 对被测信号(频率为Fx)进行计数,计数结果为 Nx,则有MUX64-8 模块并不是必须的,可根据实际设计进行取舍。

分析测频计测控时序,着重分析 START的作用,完成等精度频率计设计。

3.2 FPGA 模块FPGA模块所要完成的功能如图 1 所示,由于单片机的速度慢,不能直接测量高频信号,所以使用高速 FPGA 为测频核心。

基于FPGA和单片机的多功能等精度频率计设计摘要基于传统测频原理的频率计的测量精度将随着被测信号频率的下降而降低,在实用中有很大的局限性,而等精度频率计不但有较高的测量精度,而且在整个测频区域内保持恒定的测试精度。

运用等精度测量原理,结合单片机技术设计了一种数字频率计,由于采用了屏蔽驱动电路及数字均值滤波等技术措施,因而能在较宽定的频率范围和幅度范围内对频率,周期,脉宽,占空比等参数进行测量,并可通过调整闸门时间预置测量精度。

选取的这种综合测量法作为数字频率计的测量算法,提出了基于FPGA 的数字频率计的设计方案。

给出了该设计方案的实际测量效果,证明该设计方案切实可行,能达到较高的频率测量精度。

关键词等精度测量,单片机,频率计,闸门时间,FPGAABSTRACTAlong with is measured based on the traditional frequency measurement principle frequency meter measuring accuracy the signalling frequency the drop but to reduce, in is practical has the very big limitation, but and so on the precision frequency meter not only has teaches the high measuring accuracy, moreover maintains the constant test precision in the entire frequency measurement region. Using and so on the precision survey principle, unified the monolithic integrated circuit technical design one kind of numeral frequency meter, because has used the shield actuation electric circuit and technical measure and so on digital average value filter, thus could in compared in the frequency range and the scope scope which the width decided to the frequency, the cycle, the pulse width, occupied parameter and so on spatial ratio carries on the survey, and might through the adjustment strobe time initialization measuring accuracy. Selection this kind of synthesis measured the mensuration took the digital frequency meter the survey algorithm, proposed based on the FPGA digital frequency meter design proposal. Has produced this design proposal actual survey effect, proved this design proposal is practical and feasible, can achieve the high frequency measurement precisionKeywords Precision survey, microcontroller, frequency meter, strobe time,field programmable gate array1 绪论测量频率是电子测量技术中最常见的测量之一。

一种基于FPGA和单片机的频率监测系统设计本系统利用和有效的结合起来共同实现等精度频率测量和IDDS技术,发挥各自的优点,使设计变得越发简单和灵便,并具有频率测量范围宽、产生的波形频率辨别率高及精度大等特点。

系统便利灵便,测量精度和产生的波形辨别率高,能适应该代许多高精度测量和波形产生的要求,可以在各类测量系统和中得到很好的利用,频率测量在试验、通讯设备、音频视频和科学讨论中具有非常广泛的用途。

等精度测量技术具有广大的应用前景,因为其性能的优越性,在目前各个测量领域中都可以发挥着很好的作用,特殊是在海洋勘探,太空探究以及各类试验中都得到了应用。

1.DDS信号发生器的实现用法FPGA与单片机相结合的方式构成DDS信号发生器的核心部分,这是一种从相位概念动身挺直合成所需波形的一种新的全数字频率合成技术。

其中FPGA完成相位累加、波形地址查找及波形输出等功能,凌阳16位单片机实现频率控制字的输入和液晶显示部分。

FPGA与单片机通过串行输入并行输出的方式举行通信。

其总体设计框图1所示。

1.1 DDS产生原理图2是一个基本的DDFS结构框图。

DDFS 以数控的方式,产生频率可控制的正弦波、方波、三角波,电路包括了基及时钟源、相位累加器、相位调制器、波形ROM查找表、D/A转换器和低通等。

频率控制字N 和相位控制字M分离控制DDS所输出的波形的频率和正弦波的相位。

1.1.1 频率部分一个N位字长的二进制加法器的一端和一个固定时钟脉冲取样的N位相位寄存器相连,另一个输入端是外部输入的控制字M。

这样在每一个时钟到来的时候,前一次相位寄存器中的值和当前的M值相加,作为当前相位寄存器的输出。

控制字M打算了相位增量,加法器不断的第1页共5页。

光电与通信工程学院课程设计报告书课设名称:等精度频率计年级专业及班级:姓名:学号:一、课程设计目的1、进一步熟悉Quartus Ⅱ的软件使用方法,熟悉keil 软件使用;2、熟悉单片机与可编程逻辑器件的开发流程及硬件测试方法;3、掌握等精度频率计设计的基本原理。

4、掌握独立系统设计及调试方法,提高系统设计能力。

实验设备EDA最小系统板一块(康芯)、PC机一台、示波器一台、信号发生器一台、万用表一个。

二、设计任务利用单片机与FPGA设计一款等精度频率计,待测脉冲的检测及计数部分由FPGA实现,FPGA的计数结果送由单片机进行计算,并将最终频率结果显示在数码管上。

要求该频率计具有较高的测量精度,且在整个频率区域能保持恒定的测试精度,具体指标如下:a)具有频率测试功能:测频范围100Hz~5MHz。

测频精度:相对误差恒为基准频率的万分之一。

b)具有脉宽测试功能:测试范围10μs~1s,测试精度:0.1μs。

c)具有占空比测试功能:测试精度1%~99%。

d)具有相位测试功能。

(注:任务a 为基本要求,任务b、c、d 为提高要求)三、基本原理基于传统测频原理的频率计的测量精度将随被测信号频率的下降而降低,在实用中有较大的局限性,而等精度频率计不但具有较高的测量精度,而且在整个频率区域能保持恒定的测试精度。

3.1 等精度测频原理等精度频率计主控结构如图1 所示预置门控信号CL 选择为0.1~1s 之间(通过测试实验得出结论:CL 在这个范围内选择时间宽度对测频精度几乎没有影响)。

BZH 和TF 分别是2 个高速计数器,BZH 对标准频率信号(频率为Fs)进行计数,设计数结果为Ns;TF 对被测信号(频率为Fx)进行计数,计数结果为Nx,则有MUX64-8 模块并不是必须的,可根据实际设计进行取舍。

分析测频计测控时序,着重分析START的作用,完成等精度频率计设计。

3.2 FPGA 模块FPGA模块所要完成的功能如图1 所示,由于单片机的速度慢,不能直接测量高频信号,所以使用高速FPGA 为测频核心。

单片机与FPGA实现等精度频率测量和IDDS技术设计

方案

O.引言

本系统利用单片机和FPGA 有效的结合起来共同实现等精度频率测量和IDDS 技术,发挥各自的优点,使设计变得更加容易和灵活,并具有频率测量

范围宽、产生的波形频率分辨率高及精度大等特点。

系统方便灵活,测量精度和产生的波形分辨率高,能适应当代许多高精度测量和波形产生的要求,可以在各类测量系统和信号发生器中得到很好的利用,频率测量在电路实验、通讯设备、音频视频和科学研究中具有十分广泛的用途。

等精度测量技术具有广阔的应用前景,由于其性能的优越性,在目前各个测量领域中都可以发挥着很好的作用,特别是在海洋勘探,太空探索以及各类实验中都得到了应用。

1.DDS 信号发生器的实现

使用FPGA 与单片机相结合的方式构成DDS 信号发生器的核心部分,这是一种从相位概念出发直接合成所需波形的一种新的全数字频率合成技术。

其中FPGA 完成相位累加、波形地址查找及波形输出等功能,凌阳16 位单片机实现频率控制字的输入和液晶显示部分。

FPGA 与单片机通过串行输入并行输出的方式进行通信。

其总体设计框图如图1 所示。

1.1 DDS 产生原理

图2 是一个基本的DDFS 结构框图。

DDFS 以数控振荡器的方式,产生频率可控制的正弦波、方波、三角波,电路包括了基准时钟源、相位累加器、相位调制器、波形ROM 查找表、D/A 转换器和低通滤波器等。

频率控制字N 和相。

基于单片机和FPGA的等精度频率计系统设计

毛群

【期刊名称】《电子制作》

【年(卷),期】2022(30)19

【摘要】基于等精度测量原理,设计一款以FPGA和STM32单片机为控制核心的数字频率计系统,不同频率和幅度待测信号通过自动增益控制(AGC)模块实现增益控制,经过整形后由FPGA采集频率数据,送单片机计算处理获得频率值,最后由LCD显示信号频率周期。

经测试,该数字频率计检测频率范围1Hz~40MHz,精度达到10。

【总页数】4页(P8-10)

【作者】毛群

【作者单位】阿坝师范学院电子信息与自动化学院

【正文语种】中文

【中图分类】TM9

【相关文献】

1.基于单片机与FPGA的等精度频率计设计

2.基于FPGA与单片机的等精度频率计的设计

3.基于单片机与FPGA的等精度数字频率计设计

4.基于FPGA和单片机的高精度数字频率计的设计与实现

5.基于FPGA和单片机的高精度数字频率计的设计与实现

因版权原因,仅展示原文概要,查看原文内容请购买。