电子设计自动化EDA技术实验三报告模板-8线-3线优先编码器设计

- 格式:doc

- 大小:367.00 KB

- 文档页数:8

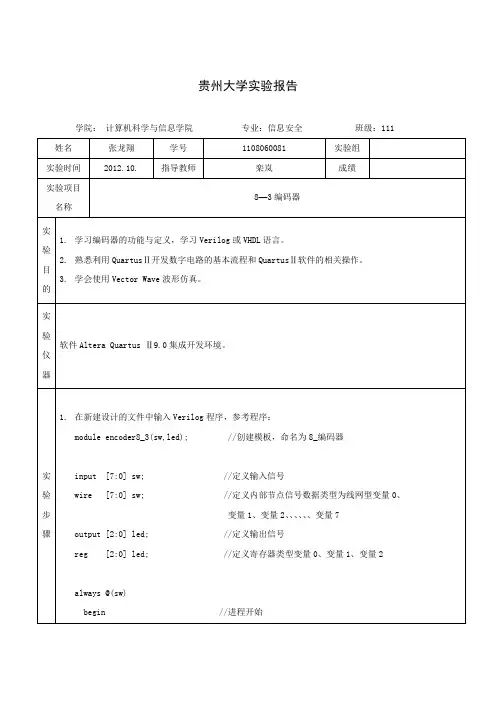

EDA实验报告班级:学号:学生:指导老师:实验一:组合逻辑设计一、实验目的:1、通过一个简单的3—8译码器的设计,让学生掌握组合逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

3、初步了解quartusⅡ原理图输入设计的全过程。

二、实验的硬件要求:1、输入:DIP拨码开关3位。

2、输出:LED灯。

3、主芯片:EP1K10TC100-3.三、实验原理:三-八译码器三输入,八输出。

当输入信号按二进制方式的表示值为N时(输入端低电平有效),输出端从零到八记,标号为N输出端低电平表示有信号产生,而其他则为高电平表示无信号产生。

因为三个输入端产生的组合状态有八种,所以输出端在每种组合中仅有一位为低电平的情况下,能表示所有的输入组合,因此不需要像编码器实验那样再用一个输出端指示输出是否有效。

但可以在输入中加入一个输出使能端,用来指示是否将当前的输入进行有效的译码。

当使能端指示输入信号无效或不用对当前信号进行译码时,输出端全为高电平,表示无任何信号。

本例设计中没有考虑使能输入端。

三个输入端:A0: 01010101A1: 00110011A2: 00001111三个输出端真值:Y0:10000000 Y1:01000000 Y2:00100000Y3:00010000 Y4:00001000 Y5:00000100 Y6:00000010Y7:00000001四、实验步骤:1、打开quartusⅡ,点击file\new菜单,选择block diagram。

根据实验要求选择器件并连线。

原理图如下:2、连好之后,单击保存,将文件保存到之前新建好的文件夹内。

3、点击Assignment\Device.选择实验要求的相关内容,截图如下:4、然后单击快键编译菜单,进行编译,编译成功后进行仿真。

根据真值表数据设置输入端的波形,点击开始仿真后,就会出现输出波形,并与真值表进行对照。

波形如下:波形与真值表一一对应,实验成功!实验二:扫描显示电路的驱动一、实验目的:了解教学系统中八位七段数码管显示模块的工作原理,设计标准扫描驱动电路模块,以备后面实验调用。

电子设计自动化(EDA)实验指引书前言近些年来,电子设计自动化(EDA)技术发展迅速。

一方面,各种大容量、高性能、低功耗可编程逻辑器件不断推出,使得专用集成电路(ASIC)生产商感受到空前竞争压力。

另一方面,浮现了许多EDA设计辅助工具,这些工具大大提高了新型集成电路设计效率,使更低成本、更短周期复杂数字系统开发成为也许。

于是一场ASIC 与FPGA/CPLD之争在所难免。

然而PLD器件具备先天竞争优势,那就是可以重复编程,在线调试。

EDA技术正是这场较劲推动引擎之一。

普通来说,EDA技术就是以计算机为平台,以EDA软件工具为开发环境,以HDL为设计语言,以可编程器件为载体,以ASIC、SOC芯片为目的器件,以电子系统设计为应用方向电子产品自动化设计过程。

设计者只需编写硬件描述语言代码,然后选取目的器件,在集成开发环境里进行编译,仿真,综合,最后在线下载调试。

整个过程,大某些工作由EDA软件完毕。

全球许多知名可编程器件提供商都推出了自己集成开发工具软件,如Altera公司MAX+PLUSⅡ、Quartus Ⅱ软件;Xilinx公司Foundation 、ISE软件,Lattice公司ispExpert 软件,Actel公司Libero软件等。

这些软件推出,极大地增进了集算法设计、芯片编程、电路板设计于一体EDA技术发展。

此外,在以SOC芯片为目的器件电子系统设计规定下,可编程器件内部开始集成高速解决器硬核、解决器软核、DSP模块、大量存储资源、高速串行收发模块、系统时钟管理器、多原则I/O接口模块,亦使得设计者更加得心应手,新一轮数字革命由此引起。

EDA技术是一门实践性很强学科,要培养出具备竞争力一流IC 设计人才,动手能力是核心。

只有通过理论学习,加上现场实验,在使用软件编程加硬件调试过程中真正获得锻炼,增长技能。

ZY11EDA13BE型实验系统采用主板加适配板加扩展板灵活构造,可以便进行基于不同PLD芯片实验开发,并易于升级,符合当前高校在此方面对人才培养规定。

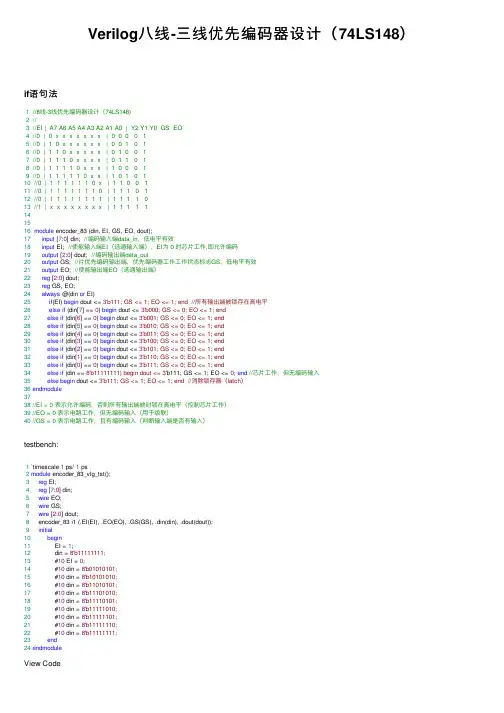

Verilog⼋线-三线优先编码器设计(74LS148)if语句法1//8线-3线优先编码器设计(74LS148)2//3//EI | A7 A6 A5 A4 A3 A2 A1 A0 | Y2 Y1 Y0 GS EO4//0 | 0 x x x x x x x | 0 0 0 0 15//0 | 1 0 x x x x x x | 0 0 1 0 16//0 | 1 1 0 x x x x x | 0 1 0 0 17//0 | 1 1 1 0 x x x x | 0 1 1 0 18//0 | 1 1 1 1 0 x x x | 1 0 0 0 19//0 | 1 1 1 1 1 0 x x | 1 0 1 0 110//0 | 1 1 1 1 1 1 0 x | 1 1 0 0 111//0 | 1 1 1 1 1 1 1 0 | 1 1 1 0 112//0 | 1 1 1 1 1 1 1 1 | 1 1 1 1 013//1 | x x x x x x x x | 1 1 1 1 1141516module encoder_83 (din, EI, GS, EO, dout);17input [7:0] din; //编码输⼊端data_in,低电平有效18input EI; //使能输⼊端EI(选通输⼊端),EI为 0 时芯⽚⼯作,即允许编码19output [2:0] dout; //编码输出端data_out20output GS; //⽚优先编码输出端,优先编码器⼯作⼯作状态标志GS,低电平有效21output EO; //使能输出端EO(选通输出端)22reg [2:0] dout;23reg GS, EO;24always @(din or EI)25if(EI) begin dout <= 3'b111; GS <= 1; EO <= 1; end //所有输出端被锁存在⾼电平26else if (din[7] == 0) begin dout <= 3'b000; GS <= 0; EO <= 1; end27else if (din[6] == 0) begin dout <= 3'b001; GS <= 0; EO <= 1; end28else if (din[5] == 0) begin dout <= 3'b010; GS <= 0; EO <= 1; end29else if (din[4] == 0) begin dout <= 3'b011; GS <= 0; EO <= 1; end30else if (din[3] == 0) begin dout <= 3'b100; GS <= 0; EO <= 1; end31else if (din[2] == 0) begin dout <= 3'b101; GS <= 0; EO <= 1; end32else if (din[1] == 0) begin dout <= 3'b110; GS <= 0; EO <= 1; end33else if (din[0] == 0) begin dout <= 3'b111; GS <= 0; EO <= 1; end34else if (din == 8'b11111111) begin dout <= 3'b111; GS <= 1; EO <= 0; end//芯⽚⼯作,但⽆编码输⼊35else begin dout <= 3'b111; GS <= 1; EO <= 1; end //消除锁存器(latch)36endmodule3738//EI = 0 表⽰允许编码,否则所有输出端被封锁在⾼电平(控制芯⽚⼯作)39//EO = 0 表⽰电路⼯作,但⽆编码输⼊(⽤于级联)40//GS = 0 表⽰电路⼯作,且有编码输⼊(判断输⼊端是否有输⼊)testbench:1 `timescale 1 ps/ 1 ps2module encoder_83_vlg_tst();3reg EI;4reg [7:0] din;5wire EO;6wire GS;7wire [2:0] dout;8 encoder_83 i1 (.EI(EI), .EO(EO), .GS(GS), .din(din), .dout(dout));9initial10begin11 EI = 1;12 din = 8'b11111111;13 #10 EI = 0;14 #10 din = 8'b01010101;15 #10 din = 8'b10101010;16 #10 din = 8'b11010101;17 #10 din = 8'b11101010;18 #10 din = 8'b11110101;19 #10 din = 8'b11111010;20 #10 din = 8'b11111101;21 #10 din = 8'b11111110;22 #10 din = 8'b11111111;23end24endmoduleView Codecase语句法1//8线-3线优先编码器设计(74LS148)2//3//EI | A7 A6 A5 A4 A3 A2 A1 A0 | Y2 Y1 Y0 GS EO4//0 | 0 x x x x x x x | 0 0 0 0 15//0 | 1 0 x x x x x x | 0 0 1 0 16//0 | 1 1 0 x x x x x | 0 1 0 0 17//0 | 1 1 1 0 x x x x | 0 1 1 0 18//0 | 1 1 1 1 0 x x x | 1 0 0 0 19//0 | 1 1 1 1 1 0 x x | 1 0 1 0 110//0 | 1 1 1 1 1 1 0 x | 1 1 0 0 111//0 | 1 1 1 1 1 1 1 0 | 1 1 1 0 112//0 | 1 1 1 1 1 1 1 1 | 1 1 1 1 013//1 | x x x x x x x x | 1 1 1 1 1141516module encoder_83_case (din, EI, GS, EO, dout);17input [7:0] din; //编码输⼊端data_in,低电平有效18input EI; //使能输⼊端EI(选通输⼊端),EI为 0 时芯⽚⼯作,即允许编码19output [2:0] dout; //编码输出端data_out20output GS; //⽚优先编码输出端,优先编码器⼯作⼯作状态标志GS,低电平有效21output EO; //使能输出端EO(选通输出端)22reg [2:0] dout;23reg GS, EO;24always @(din or EI)25if(EI)26begin dout <= 3'b111; GS <= 1; EO <= 1; end //所有输出端被锁存在⾼电平27else28casez (din) //建议⽤casez语句,casez把z/?匹配成任意。

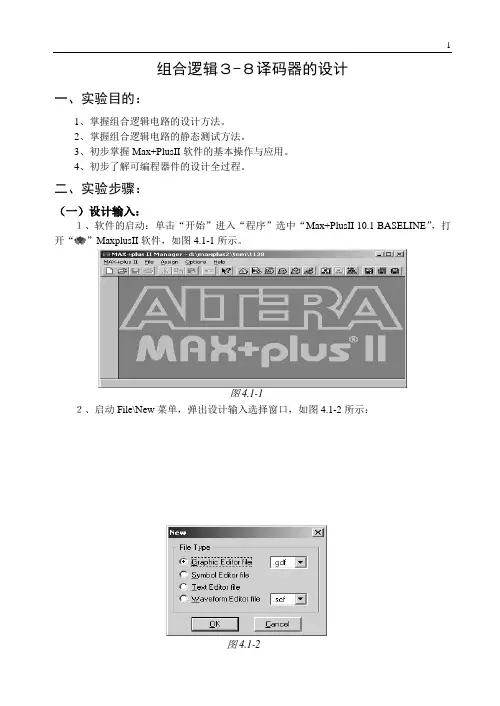

组合逻辑3-8译码器的设计一、实验目的:1、掌握组合逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

3、初步掌握Max+PlusII软件的基本操作与应用。

4、初步了解可编程器件的设计全过程。

二、实验步骤:(一)设计输入:1、软件的启动:单击“开始”进入“程序”选中“Max+PlusII 10.1 BASELINE”,打开“”MaxplusII软件,如图4.1-1所示。

图4.1-12、启动File\New菜单,弹出设计输入选择窗口,如图4.1-2所示:图4.1-23、选择Graphic Editor File ,单击OK ,打开原理图编辑器,进入原理图设计输入电路编辑状态,如图4.1-3所示:4、设计输入1)放置一个器件在原理图上a 、在原理图的空白处双击鼠标右键,出现图4.1-4:图4.1-3图4.1-4b 、在光标处输入元件名称(如:input ,output ,and2,and3,nand2,or2,not ,xor ,dff 等)或用鼠标点击库元件,按下OK 即可。

c 、如果安放相同的元件,只要按住Ctrl 键,同时用鼠标按左键拖动该元件复制即可。

d 、一个完整的电路包括:输入端口input 、电路元件集合、输出端口output 。

e 、图4.1-5为3-8译码器元件安放结果。

2)添加连线到器件的引脚上:把鼠标移到元件引脚附近,则鼠标自动由箭头变为十字,按住鼠标左键拖动,即可画出连线。

3-8译码器原理图连线后如图4.1-6所示。

图4.1-5图4.1-63)标记输入/输出端口属性分别双击输入端口的“PINNAME ”,当变成黑色时,即可输入标记符并回车确认;输出端口标记方法类似。

本译码器的三输入端分别标记为:A 、B 、C ;其八输出端分别为:D0、D1、D2、D3、D4、D5、D6、D7。

如图4.1-7所示。

4)保存原理图单击保存按钮图表,对于新建文件,出现类似文件管理器图框,请选择保存路径/文件名称保存原理图,原理图的扩展名为.gdf ,本实验中取名为test1.gdf 。

Xxxx大学课程设计任务书课程硬件课程设计题目 8-3优先级编码器设计专业姓名学号主要内容、基本要求等一、主要内容:利用EL教学实验箱、微机和QuartusⅡ软件系统,使用VHDL语言输入方法设计8-3优先编码器。

可以利用层次设计方法和VHDL语言,完成硬件设计设计和仿真。

最后在EL教学实验箱中实现。

二、基本要求:设计并实现一个8-3优先级编码器,要求I0优先级最高,I7优先级最低,编码输出为原码。

三、扩展要求:输入端加使能端,在使能端为有效的低电平时,进行编码;在使能端为无效的高电平时,输出高阻状态。

四、参考文献:[1] 杨刚,龙海燕.现代电子技术-VHDL与数据系统设计.北京:电子工业出版社,2004[2] 黄仁欣.EDA技术实用教程.北京:清华大学出版社,2006[3] 潘松.VHDL实用教程[M].成都:电子科技大学出版社,2000[4] 李国丽,朱维勇.电子技术实验指导书.合肥:中国科技大学出版社,2000[5] 宋振辉. EDA技术与VHDL.北京:北京大学出版社,2008完成期限18-19周指导教师张岩专业负责人富宇2011年6月28日目录第1章概述 (1)1.1 EDA的概念 (1)1.2 EDA技术及应用 (2)1.3 EDA技术发展趋势 (2)1.4 Quartus II特点介绍 (3)第2章硬件描述语言——VHDL (4)2.1 VHDL的简介 (4)2.2 VHDL语言的特点 (4)2.3 VHDL的设计流程 (5)第3章 8-3优先编码器的设计 (6)3.1 编码器的工作原理 (6)3.2 8-3优先编码器的设计 (6)3.3 8-3优先编码器仿真及分析 (7)3.4 在实验箱上实现8-3优先编码器 (8)结论 (11)参考文献 (12)第1章概述1.1EDA的概念EDA技术是在电子CAD技术基础上发展起来的计算机软件系统,是指以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。

8-3编码器程序设计与仿真实验1 实验目的(1) 熟悉软件的使用,了解使用EDA工具进行设计的全过程。

(2) 学会用VHDL语言进行逻辑电路设计。

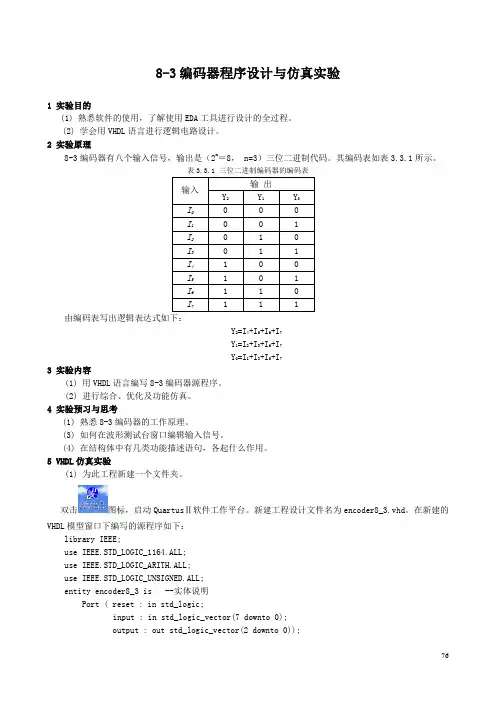

2 实验原理8-3编码器有八个输入信号,输出是(2n=8, n=3)三位二进制代码。

其编码表如表3.3.1所示。

表3.3.1 三位二进制编码器的编码表输入输出Y2 Y1Y0I0 0 0 0I10 0 1I20 1 0I30 1 1I4 1 0 0I5 1 0 1I6 1 1 0I7 1 1 1由编码表写出逻辑表达式如下:Y2=I4+I5+I6+I7Y1=I2+I3+I6+I7Y0=I1+I3+I5+I73 实验内容(1) 用VHDL语言编写8-3编码器源程序。

(2) 进行综合、优化及功能仿真。

4 实验预习与思考(1) 熟悉8-3编码器的工作原理。

(3) 如何在波形测试台窗口编辑输入信号。

(4) 在结构体中有几类功能描述语句,各起什么作用。

5 VHDL仿真实验(1)为此工程新建一个文件夹。

双击图标,启动QuartusⅡ软件工作平台。

新建工程设计文件名为encoder8_3.vhd。

在新建的VHDL模型窗口下编写的源程序如下:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity encoder8_3 is --实体说明Port ( reset : in std_logic;input : in std_logic_vector(7 downto 0);output : out std_logic_vector(2 downto 0));end encoder8_3;architecture Behavioral of encoder8_3 is --结构体beginprocess(reset,input) --进程beginif ( reset = '1') thenoutput <= "000";elsecase input iswhen "00000001" => output <= "000";when "00000010" => output <= "001";when "00000100" => output <= "010";when "00001000" => output <= "011";when "00010000" => output <= "100";when "00100000" => output <= "101";when "01000000" => output <= "110";when "10000000" => output <= "111";when others=> output<="000";end case;end if;end process;end Behavioral;(2) 创建工程及全程编译完成源代码输入后即可创建工程。

实验三: 二位比较器的设计与实现一.实验简介:这个实验将指导你通过使用ISE软件进行简单的二位比较器的设计与实现。

二.实验目的:•使用ISE软件设计并仿真。

•学会程序下载。

三.实验原理:1.ISE软件是一个支持数字系统设计的开发2.用ISE软件进行设计开发时基于相应器件型号的。

注意:软件设计时选择的器件型号是与实际下载板上的器件型号相同。

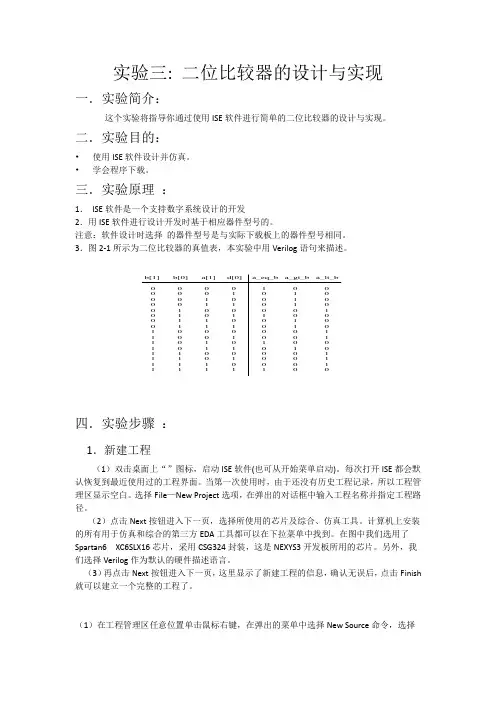

3.图2-1所示为二位比较器的真值表,本实验中用Verilog语句来描述。

b[1] b[0] a[1] d[0]0 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 1a_eq_b a_gt_b a_lt_b1 0 00 1 00 1 00 1 00 0 11 0 00 1 00 1 00 0 10 0 11 0 00 1 00 0 10 0 10 0 11 0 0四.实验步骤:1.新建工程(1)双击桌面上“”图标,启动ISE软件(也可从开始菜单启动)。

每次打开ISE都会默认恢复到最近使用过的工程界面。

当第一次使用时,由于还没有历史工程记录,所以工程管理区显示空白。

选择File—New Project选项,在弹出的对话框中输入工程名称并指定工程路径。

(2)点击Next按钮进入下一页,选择所使用的芯片及综合、仿真工具。

计算机上安装的所有用于仿真和综合的第三方EDA工具都可以在下拉菜单中找到。

在图中我们选用了Spartan6 XC6SLX16芯片,采用CSG324封装,这是NEXYS3开发板所用的芯片。

另外,我们选择Verilog作为默认的硬件描述语言。

(3)再点击Next按钮进入下一页,这里显示了新建工程的信息,确认无误后,点击Finish 就可以建立一个完整的工程了。

(1)在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择New Source命令,选择Verilog Module输入,并输入Verilog文件名。

EDA技术实验报告—3-8译码器的设计一.实验目的1.通过一个简单的3-8译码器的设计,掌握组合逻辑电路的设计方法。

2.掌握组合逻辑电路的静态测试方法。

3.初步了解QUARTUSⅡ软件的基本操作和应用。

4.初步了解可编程逻辑器件的设计全过程。

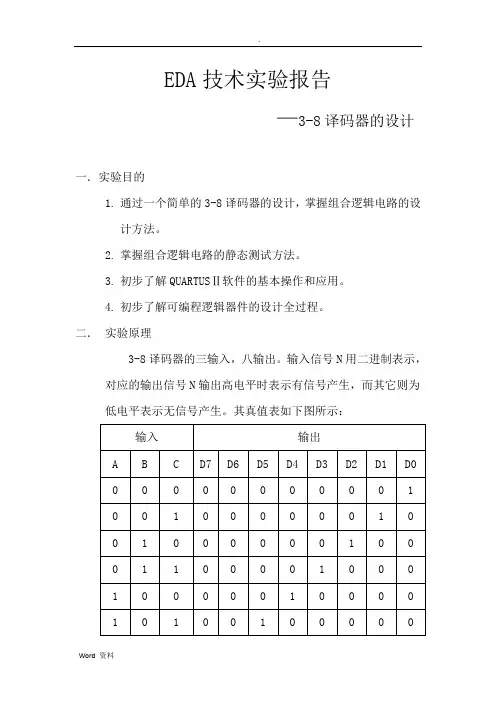

二.实验原理3-8译码器的三输入,八输出。

输入信号N用二进制表示,对应的输出信号N输出高电平时表示有信号产生,而其它则为低电平表示无信号产生。

其真值表如下图所示:当使能端指示输入信号无效或不用对当前的信号进行译码时,输出端全为高电平,表示任何信号无效。

三.实验内容用三个拨动开关来表示三八译码器的三个输入(A,B,C),用八个LED来表示三八译码器的八个输出(D0-D7)。

通过与实验箱的FPGA接口相连,来验证真值表中的内容。

表1-2拨动开关与FPGA管脚连接表表1-3LED 灯与FPGA管脚连接表(当FPGA与其对应的接口为高电平时,LED会发亮)四.实验歩骤1.建立工程文件2.建立图形设计软件(1)将要选择的器件符号放置在图形编辑器的工作区域,用正交节点工具将原件安装起来,然后定义端口的名称。

结果如下图:3.编译前设置(1)选择目标芯片(2)选择目标芯片的引脚状态4.对设计文件进行编译五.管脚的分配根据表1-2和1-3的数据进行管脚的设置1六.对文件进行仿真按下Report按钮观察仿真结果,如下:6.从设计文件到目标器件的加载七.实验现象以及结果文件加载到目标器件后,拨动拨动开关,LED灯会按照真值表对应的灯点亮。

八.实验心得通过本次实验,加深了自己对EDA技术的理解并提高了操作能力。

但是,在实验中仍然遇到了很多困难,还需提高。

电子设计自动化eda技术实验三报告模板-8线-3线优先编码器设计篇一:电子设计自动化EDA技术实验三报告模板-8线-3线优先编码器设计[1]湖南安全职业技术学院实验报告课程名称实验项目名称 8线-3线优先编码器设计实验学生班级电信0901 实验时间实验地点 EDA实训室实验成绩评定指导教师签字年月日篇二:EDA课程设计报告8线-3线优先编码器Xxxxx学院《EDA技术》课程报告设计题目:8线-3线优先编码器班级:应用电子1101班姓名:学号:指导老师:日期:目录一、8-3优先编码器设计原理分析 (3)二、8-3优先编码器模块的源程序 .............. 3 三、8-3优先编码器仿真结果 .................. 4 四、设计总结和心得体会 ...................... 5 五、参考资料 (5)一、8-3优先编码器设计原理分析8-3优先编码器输入信号为din0,din1,din2,din3,din4,din5,din6和din7,输出信号为out2、out1、out0。

输入信号中din7的优先级别最低,依次类推,din0的优先级别最高。

也就是说若din0输入为1(即为高电平)则无论后续的输入信号怎么样,对应的这种状态一样,如若din0输入为0(即为低电平)则看优先级仅次于din0的din1状态决定,依次类推。

因为din0到din7共8中状态,可以用3位二进制编码来表示。

8-3优先编码器真值表如下表所示。

表1 8-3优先编码器真值表二、8-3优先编码器模块的源程序8-3优先编码器由VHDL程序来实现,VHDL语言描述如下:LIBRARY IEEE;USE _LOGIC_; ENTITY coder ISPORT ;output : OUT STD_LOGIC_VECTOR;EANABLE: in std_logic ); END coder;ARCHITECTURE behav OF coder ISSIGNAL SINT : STD_LOGIC_VECTOR; BEGINPROCESS BEGINIF THENIF ='1') THEN output 篇三:实验三-8线3线优先编码器实验三基本组合逻辑电路的PLD实现(2)实验名称:利用原理图输入法与VerilogHDL输入法设计一个8线-3线优先编码器实验目的:1. 熟悉用可编程器件实现基本组合逻辑电路的方法。

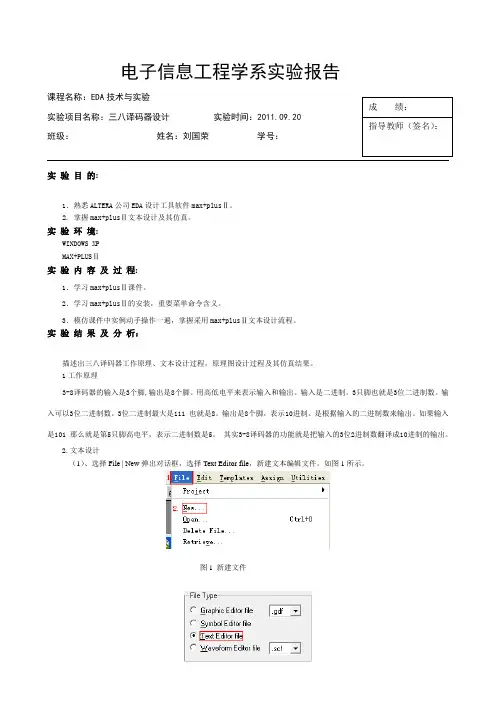

电子信息工程学系实验报告课程名称:EDA技术与实验成绩:实验项目名称:三八译码器设计实验时间:2011.09.20指导教师(签名):班级:姓名:刘国荣学号:实验目的:1.熟悉ALTERA公司EDA设计工具软件max+plusⅡ。

2. 掌握max+plusⅡ文本设计及其仿真。

实验环境:WINDOWS XPMAX+PLUSⅡ实验内容及过程:1.学习max+plusⅡ课件。

2.学习max+plusⅡ的安装,重要菜单命令含义。

3.模仿课件中实例动手操作一遍,掌握采用max+plusⅡ文本设计流程。

实验结果及分析:描述出三八译码器工作原理、文本设计过程,原理图设计过程及其仿真结果。

1工作原理3-8译码器的输入是3个脚,输出是8个脚。

用高低电平来表示输入和输出。

输入是二进制。

3只脚也就是3位二进制数。

输入可以3位二进制数。

3位二进制最大是111 也就是8。

输出是8个脚,表示10进制。

是根据输入的二进制数来输出。

如果输入是101 那么就是第5只脚高电平,表示二进制数是5。

其实3-8译码器的功能就是把输入的3位2进制数翻译成10进制的输出。

2.文本设计(1)、选择File | New弹出对话框,选择Text Editor file,新建文本编辑文件。

如图1所示。

图1 新建文件图2 选择文本文件(2)、在文本编辑窗口,输入Verilog语言,代码如下:图3编辑代码(3)、将文件命名为“ym38”保存为v文件图4 保存为v文件(4)、检查文件可行性图5 检查文件显示可行(5)、再新建一个文件夹,选择波形文件图6 新建波形文件(6)、列出端口及选择端口输入波形图7 波形端口选择图8 各段波形(7)、保存波形点击star开始仿真,结果如图图9 仿真结果3.原理图设计(1)、选择File | New,弹出对话框,选择Graphic Editor file新建一个原理图文件,如图10图10 新建原理图文件(2)、在原理图界面要放置元件的空白处双击鼠标左键,弹出Enter Symbol对话框,在对话框选择74138元件,单击OK,放置74138元件,同理,放置INPUT和OUTPUT,如图11图11放置元件(3)、在元器件的其中一个端口点中鼠标左键不放,拖到所需连线的另一个元件端口上,连好线,双击PIN_NAME,输入引脚名,最终原理图,如图12图12 最终原理图(4)、保存文件并检查可行性结果如图13可行图13 检查可行性(5)、同上设计一样的输出波形图后点击保存。

实验三:3-8译码器的设计一、实验目的1、学习Quartus II 7.2软件设计平台。

2、了解EDA的设计过程。

3、通过实例,学习和掌握Quartus II 7.2平台下的文本输入法。

4、学习和掌握3-8译码器的工作和设计原理。

5、初步掌握该实验的软件仿真过程。

二、实验仪器PC机,操作系统为Windows7/XP,本课程所用系统均为WindowsXP(下同),Quartus II 7.2设计平台。

三、实验步骤1、创建工程,在File菜单中选择New Project Wizard,弹出对话框如下图所示在这个窗口中第一行为工程保存路径,第二行为工程名,第三行为顶层文件实体名,和工程名一样。

2、新建设计文本文件,在file中选择new,出现如下对话框:选择VHDL File 点击OK。

3、文本输入,在文本中输入如下程序代码:library ieee;use ieee.std_logic_1164.all;entity variable_decoder isport(A:in STD_LOGIC;B:in STD_LOGIC;C:in STD_LOGIC;Y:out STD_LOGIC_VECTOR(7 downto 0));end variable_decoder;architecture rtl of variable_decoder isbeginprocess(A,B,C)variable COMB:std_logic_vector(2 downto 0);beginCOMB:=C&B&A;case COMB iswhen "000"=>Y<="11111110";when "001"=>Y<="11111101";when "010"=>Y<="11111011";when "011"=>Y<="11110111";when "100"=>Y<="11101111";when "101"=>Y<="11011111";when "110"=>Y<="10111111";when "111"=>Y<="01111111";when others=>Y<="XXXXXXXX";end case;end process;end rtl;然后保存到工程中,结果如下图所示:4、编译,如果有多个文件要把这个文件设为当前顶层实体,这样软件编译时就只编译这个文件。

实验报告一、三个程序:1、3_8译码器<1>HDL设计程序:module dec(out,in);output[7:0] out;input[2:0] in;assign out=1'b1<<in;endmodule<2>RTL电路图:<3>波形仿真图2、三位数值比较器<1>HDL设计程序:module compare_3(y1,y2,y3,a,b); output y1,y2,y3;input[2:0] a,b;reg y1,y2,y3;always@(a or b)beginif(a>b)begin y1=1;y2=0;y3=0;endelse if(a==b)begin y1=0;y2=1;y3=0;endelse if(a<b)begin y1=0;y2=0;y3=1;endendendmodule<2>RTL电路图:<3>波形仿真图:3、十进制计数器:<1>HDL程序设计:module cnt10c(clk,clr,q,cout);input clk,clr;output [3:0] q;output cout;reg[3:0] q;reg cout;always @ (posedge clk or posedge clr) beginif(clr)begin q<=4'b0000;cout<=1'b0;endelse if(q==4'b1001)begin q<=4'b0000;cout<=1'b1;endelse begin q<=q+1;cout<=1'b0;end endendmodule<2>RTL电路图:<3>波形仿真图:二.设计程序+测试程序1、4位寄存器(1)设计程序module reg4(q,d,reset,clk);input[3:0] d;output[3:0] q;input reset,clk;reg[3:0] q;always @ (posedge clk or posedge reset)beginif(reset) q<=4'b0;else q<=d;endendmodule(2)测试程序module reg4_Test;wire [3:0]out;reg clk,reset;reg [3:0]in;reg4 u2(.out(out),.in(in),.reset(reset),.clk(clk));initial$monitor($time,”out=%d,in=%d,reset=%d,clk=%d”,out,in,reset,clk); always #10 clk=~clk;initialbeginclk=0;reset=0;#10 in=4’b0000;#20 in=4’b0001;#30 in=4’b0010;#40 in=4’b0011;#50 in=4’b0100;#60 in=4’b0101;#70 in=4’b0110;#80 in=4’b0111;#80 reset=1;#90 in=4’b1000;#100 in=4’b1001;#100 reset=0;#110 in=4’b1010;#120 in=4’b1011;endinitial#130 $finish;endmodule2、2_4译码器(1)设计程序module decode2_4(out,in);output [3:0] out;input [1:0] in;reg [3:0] out;always@(in)begincase(in)0:out=4'b1000;1:out=4'b0100;2:out=4'b0010;3:out=4'b0001;default:out=4'b0000;endcaseendendmodule(2)测试程序module decode2_4_Test;wire [3:0] out;reg [1:0] in;decode2_4 u(.out(out),.in(in))¬;initial$monitor($time,”out=%d,in=%d”,out,in); initialbegin#10 in=2’b00;#10 in=2’b01;#10 in=2’b10;#10 in=2’b11;#10 $finish;endendmodule。

实验三8-3优先编码器和3-8线译码器一、实验目的1、熟悉常用编码器,译码器的功能逻辑。

2、熟悉VHDL的代码编写方法。

3、掌握复杂译码器的设计方法。

二、实验原理2、逻辑表达式:Y2=X4&X5&X6&X7Y1=~(~(X2)&X4&X5|~(X3)&X4&X5|~(X6)|~(X7));Y0=~(~(X1)&x2&X4&X6|~(X3)&X4&X6|~(X5)&X6|~(X7));2、3-8线码器总体思路以EP2C5中的三个拨位开关,SW3,SW2,SW1为三个输入信号,可以代表8种不同的状态,该译码器对这8种状态译码,并把所译码的结果在七段LED数码管上显示出来。

三、实验连线1、将EP2C5适配板左下角的JTAG用十芯排线和万用下载区左下角的SOPC JTAG 口连接起来,万用下载区右下角的电源开关拨到SOPC下载的一边2、请将JPLED1短路帽右插,JPLED的短路帽全部上插。

3、请将JP103的短路帽全部插上。

四、实验步骤及波形按照步骤三正确连线,参考实验二步骤,完成项目的建立,文件的命名,文件的编辑,语法检查,引脚分配,编译,下载。

8-3优先编码器参考代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY encode ISPORT(XINA :IN STD_LOGIC_VECTOR(7 DOWNTO 0);Y0,Y1,Y2: OUT STD_LOGIC;OUTA : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);LEDW: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END encode;ARCHITECTURE ADO OF encode ISSIGNAL LED: STD_LOGIC_VECTOR(2 DOWNTO 0);SIGNAL XIN: STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINXIN<=XINA;LEDW<="000";PROCESS (XIN)BEGINCASE XIN ISWHEN x"00" => OUTA<=x"3F";WHEN x"01" => OUTA<=x"06";WHEN x"02" => OUTA<=x"5B";WHEN x"04" => OUTA<=x"4F";WHEN x"08" => OUTA<=x"66";WHEN x"10" => OUTA<=x"6D";WHEN x"20" => OUTA<=x"7D";WHEN x"40" => OUTA<=x"07";WHEN x"80" => OUTA<=x"3F";WHEN OTHERS => OUTA<=x"3F";END CASE;END PROCESS;PROCESS (XIN)BEGINCASE XIN ISWHEN x"01" => LED<="001";WHEN x"02" => LED<="010";WHEN x"04" => LED<="011";WHEN x"08" => LED<="100";WHEN x"10" => LED<="101";WHEN x"20" => LED<="110";WHEN x"40" => LED<="111";WHEN x"80" => LED<="000";WHEN OTHERS => LED<="000";END CASE;END PROCESS;Y2<=LED(2);Y1<=LED(1);Y0<=LED(0);END ADO;3-8译码器参考代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY DECODE ISPORT(DATA_IN :IN STD_LOGIC_VECTOR(2 DOWNTO 0);LEDOUT,DATA_OUT :OUT STD_LOGIC_VECTOR(7 DOWNTO 0);LEDW :OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END DECODE;ARCHITECTURE ADO OF DECODE ISSIGNAL OUTA,D_OUT : STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINLEDW<="000";PROCESS (DATA_IN)V ARIABLE DIN: STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINDIN:=DA TA_IN;LEDOUT<=OUTA;DATA_OUT<=D_OUT;CASE DIN ISwhen "000" => OUTA<="00111111" ; --"0"when "001" => outa<="00000110" ; --"1"when "010" => outa<="01011011"; --"2"when "011" => outa<="01001111"; --"3"when "100" => outa<="01100110"; --"4"when "101" => outa<="01101101"; --"5"when "110" => outa<="01111101"; --"6"when "111" => outa<="00000111"; --"7"WHEN OTHERS => OUTA<="XXXXXXXX";END CASE;CASE DIN ISWHEN "000" => D_OUT<="00000000";WHEN "001" => D_OUT<="00000001";WHEN "010" => D_OUT<="00000010";WHEN "011" => D_OUT<="00000100";WHEN "100" => D_OUT<="00001000";WHEN "101" => D_OUT<="00010000";WHEN "110" => D_OUT<="00100000";WHEN "111" => D_OUT<="01000000";WHEN OTHERS=> D_OUT<="XXXXXXXX";END CASE;END PROCESS;END ADO;五、实验仿真8-3编码器引脚锁定如图:图5-1图5-2仿真波形如图:3-8译码器引脚锁定如图:图5-3波形如图:图5-4六、实验现象调试ok的EP2C5文件在文件夹decode中,可以直接调用。

湖南安全职业技术学院实验报告课程名称电子设计自动化EDA技术实验项目名称8线-3线优先编码器设计实验学生班级电信0901实验学生姓名熊飞同组学生姓名颜林、陈伟实验时间实验地点EDA实训室实验成绩评定指导教师签字年月日24其中IN 表示输入编码位,Sel 为片选信号,Y 表示输出编码值,YS 与YEX 表示器件状态,“11”表示器件未选中,“01”表示无键按下,“10”表示器件工作态。

四、实验方案设计、实验方法 1. 实验方案8-3优先编码器的VHDL 描述有多种方法,设计过程中可以根据真值表采用case …when 语句、with …select 语句、if …then 结构等多种手段实现,也可以根据真值表分析输入输出间的逻辑关系,根据逻辑关系写出其布尔表达式,根据布尔代数式调用基本逻辑门元件实现8-3优先编码器。

本实验中根据真值表用if-then 结构实现8-3优先编码器 2. 实验方法首先根据前文所述,对照真值表的列出的不同输入逻辑状态,分情况依次输出于输入的对应关系,而后编译综合,由开发系统自行实现电路功能。

五、实验步骤1. 设计输入 利用FILE\New 菜单输入VHDL 源程序,创建源文件2. 设计项目的创建1) 原文件存储…..2) 利用FILE\Project\Set Project … 3. 设计编译 ….IN0 IN1 IN2 IN3 IN4 IN5 IN6 IN7 SelY0 Y1 Y2 YS YEX6管脚分配情况如图,所选器件为EPM7032AELCC44-43. 仿真波形8线-3线优先编码器的仿真波形如下图,从波形可以得出,输入输出满足前文真值表,电路功能达到设计要求4. 时序分析图上述时间分析可以得到,输出信号存在最大4.5时间延迟,它主要与器件速度、表达逻辑的合理性有关,选用速度更高器件、优化设计可以使该值降低。

七、结论采用图形编程法实现了8线-3线优先编码器的设计,并完成了电路的设计编译、综合、逻辑仿真、时间分析,结果表明采用ALTRA的CPLD器件设计的8线-3线优先编码器,时间延迟为不超过4.5ns八、思考题8线-3线优先编码器的设计方法还可以通过什么方式实现?利用VHDL实现8线-3线优先编码器方法多样,还可以通过诸如case-when等其他结构实现…..8。

EDA实验报告班级:学号:姓名:实验一组合逻辑设计一、实验目的:通过一个简单的3-8译码器的设计,让学生掌握组合逻辑电路的设计方法。

二、实验的硬件要求:1、输入:DIP拨码开关3位2、输出:LED灯3、主芯片:EP2C8Q208C8三、实验原理:三八译码器三输入,八输出。

当输入信号按二进制方式的表示为N时,输出端从零标记到八。

因为三个输入端能产生的组合状态有八种,所以输出端在每种组合中仅有一位有效的情况下,能表示所有的输入组合。

3-8译码器真值表四、实验程序图:建立工程后,新建Block diagram/schematic file程序,在编辑窗口中选择相应原件用鼠标拖入文件中编辑,绘制完成后保存原理图,对程序进行编译,编译无误后,进行管脚配置,下图为程序图。

文本程序:library ieee;use ieee.std_logic_1164.all;entity program1 isport (A,B,C:in std_logic;D0,D1,D2,D3,D4,D5,D6,D7:out std_logic); end entity program1;architecture one of program1 issignal abc :std_logic_vector(2 downto 0); signal D :std_logic_vector(7 downto 0); beginabc <= A&B&C;process(abc)begincase abc iswhen "000"=>D<="10000000";when "100"=>D<="01000000";when "010"=>D<="00100000";when "110"=>D<="00010000";when "001"=>D<="00001000";when "101"=>D<="00000100";when "011"=>D<="00000010";when "111"=>D<="00000001";when others => null;end case;end process;D0<=D(7);D1<=D(6);D2<=D(5);D3<=D(4);D4<=D(3);D5<=D(2);D6<=D(1);D7<=D(0);end architecture one;五、实验仿真结果:仿真波形图如下:进行波形仿真完成后,用拨码开关的低三位代表译码器输入,将之与配置好的管脚相连;用led灯代表译码器的输出,将之与配置好的管脚相连。