数字逻辑第3章答案

- 格式:pdf

- 大小:186.44 KB

- 文档页数:11

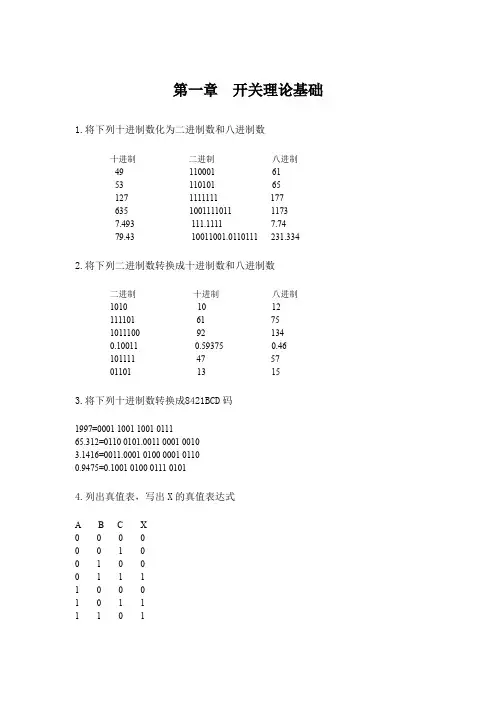

第一章开关理论基础1.将下列十进制数化为二进制数和八进制数十进制二进制八进制491100016153110101651271111111177635100111101111737.493111.11117.7479.4310011001.0110111231.3342.将下列二进制数转换成十进制数和八进制数二进制十进制八进制1010101211110161751011100921340.100110.593750.4610111147570110113153.将下列十进制数转换成8421BCD码1997=000110011001011165.312=01100101.0011000100103.1416=0011.00010100000101100.9475=0.10010100011101014.列出真值表,写出X的真值表达式A B C X00000010010001111000101111011111X=A BC+A B C+AB C+ABC5.求下列函数的值当A,B,C为0,1,0时:A B+BC=1(A+B+C)(A+B+C)=1(A B+A C)B=1当A,B,C为1,1,0时:A B+BC=0(A+B+C)(A+B+C)=1(A B+A C)B=1当A,B,C为1,0,1时:A B+BC=0(A+B+C)(A+B+C)=1(A B+A C)B=06.用真值表证明下列恒等式(1)(A⊕B)⊕C=A⊕(B⊕C)A B C(A⊕B)⊕C A⊕(B⊕C)0000000111010110110010011101001100011111所以由真值表得证。

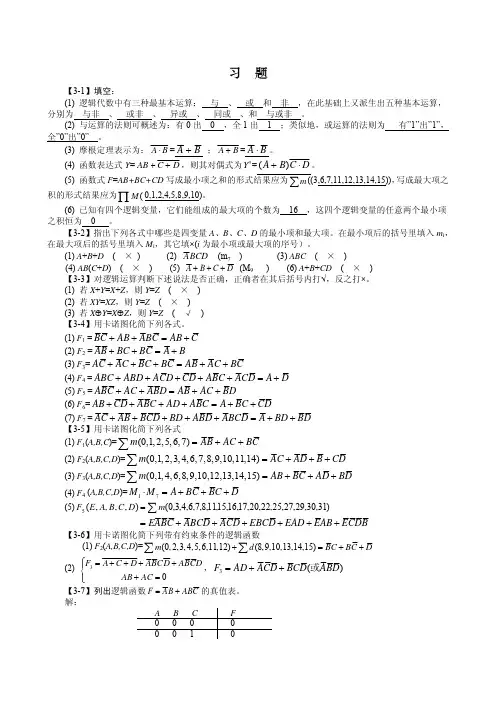

(2)A⊕B⊕C=A⊕B⊕CA B C A⊕B⊕C A⊕B⊕C00011001000100001111100001011111011111007.证明下列等式(1)A+A B=A+B 证明:左边=A+A B=A(B+B )+A B =AB+A B +A B =AB+A B +AB+A B =A+B =右边(2)ABC+A B C+AB C =AB+AC 证明:左边=ABC+A B C+AB C=ABC+A B C+AB C +ABC =AC(B+B )+AB(C+C )=AB+AC =右边(3)E D C CD A C B A A )(++++=A+CD+E证明:左边=ED C CD A C B A A )(++++=A+CD+A B C +CDE =A+CD+CD E =A+CD+E =右边(4)C B A C B A B A ++=CB C A B A ++证明:左边=CB AC B A B A ++=C B A C AB C B A B A +++)(=C B C A B A ++=右边8.用布尔代数化简下列各逻辑函数表达式(1)F=A+ABC+A C B +CB+C B =A+BC+C B (2)F=(A+B+C )(A+B+C)=(A+B)+C C =A+B (3)F=ABC D +ABD+BC D +ABCD+B C =AB+BC+BD (4)F=C AB C B BC A AC +++=BC(5)F=)()()()(B A B A B A B A ++++=B A 9.将下列函数展开为最小项表达式(1)F(A,B,C)=Σ(1,4,5,6,7)(2)F(A,B,C,D)=Σ(4,5,6,7,9,12,14)10.用卡诺图化简下列各式(1)CAB C B BC A AC F +++=0 ABC00 01 11 1011111化简得F=C(2)CB A D A B A DC AB CD B A F++++=111111AB CD 00 01 11 1000011110化简得F=DA B A +(3)F(A,B,C,D)=∑m (0,1,2,5,6,7,8,9,13,14)1111111111ABCD 00 01 11 1000011110化简得F=DBC D C A BC A C B D C ++++(4)F(A,B,C,D)=∑m (0,13,14,15)+∑ϕ(1,2,3,9,10,11)Φ1ΦΦ1ΦΦ1Φ1AB CD 00 01 11 1000011110化简得F=ACAD B A ++11.利用与非门实现下列函数,并画出逻辑图。

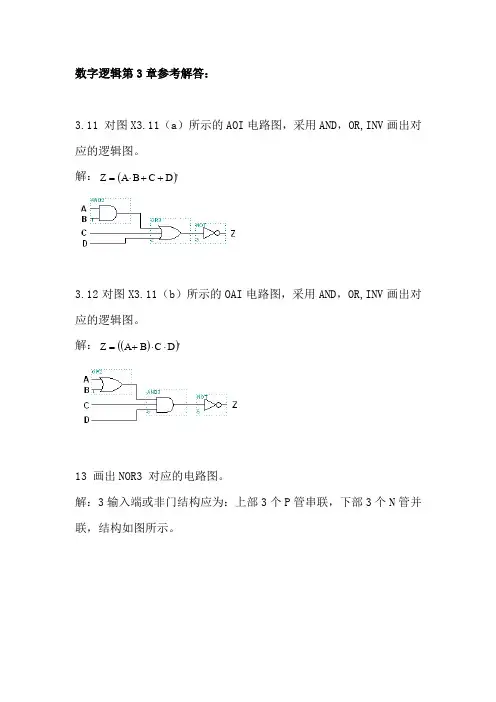

第三章(组合逻辑电路)作业及答案1、写出图3-1所示组合逻辑电路中输入输出的逻辑关系式和真值表。

图3-1:组合逻辑电路逻辑图解:(1)C A A AC B AY +=++=1(2)D B C B A CD B A CD B A D BD CD A B A Y ++=++=+=++=)(2 2、试分析图3-2所示组合逻辑电路,写出其逻辑函数表达式。

若设S 1﹑S 0为功能控制信号,A ﹑B 为输入信号,L 为输出,说明当S 1﹑S 0取不同信号值时,电路所实现的逻辑功能。

图3-2:组合逻辑电路逻辑图3、试用与门、或门和非门,或者与门、或门和非门的组合来实现如下各逻辑函数关ABS 1S=1=1&=1系,画出相应的逻辑电路图。

(1)1Y AB BC=+(2)2Y A C B=+()(3)3Y ABC B EF G=++()&&1≥Y1.1ABC.&1≥Y2.1ABC&1≥1≥&&1ABC.EFG.Y3...4、试用门电路设计4线-2线优先编码器,输入、输出信号都是高电平有效,要求任一按键按下时,G S为1,否则G S=0;还要求没有按键按下时,E O信号为1,否则为0。

5、试用逻辑门电路设计一个2选1数据选择器,输入信号为A、B,选择信号为S,输出信号为Y,要求写出真值表、逻辑函数表达式和画出逻辑电路图。

6、某公司3条装配线各需要100kW电力,采用两台发电动机供电,一台100kW,另外一台是200kW,3条装配线不同时开工,试设计一个发电动机控制电路,可以按照需求启动发电动机以达到节电的目的。

7、图3-3是由3线/8线译码器74LS138和与非门构成的组合逻辑电路,试写出P和P2的逻辑表达式,并列出真值表,说明其逻辑功能。

1BIN/OCT01201234567B AC 10074LS138P 1P 2图3-3 组合逻辑电路图8、试用3线-8线译码器74LS138和与非门实现以下多输出函数:1F AB C AB BC AC =++(,,) ∑=),,,(),,(75422m C B A F9、图3-4是由八选一数据选择器74LS151构成的组合逻辑电路,试写出当G 1G 0为各种不同取值时输出Y 与输入A 、B 的逻辑函数表达式。

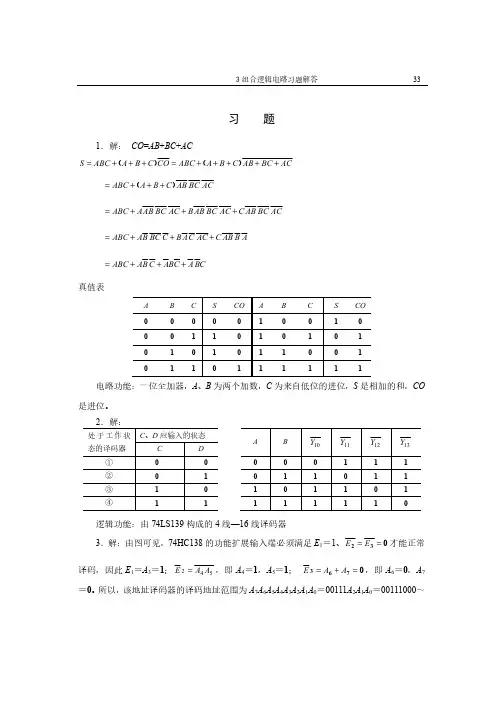

3 33习 题1.解: CO =AB +BC +ACAC BC AB C B A ABC CO C B A ABC S +++++=+++=)()(AC BC AB C B A ABC )(+++=AC BC AB C AC BC AB B AC BC AB A ABC +++= A B AB C AC C A B C BC B A ABC +++= C B A C B A C B A ABC +++=真值表A B C S CO A B C S CO 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 1 0 0 1 011111111电路功能:一位全加器,A 、B 为两个加数,C 为来自低位的进位,S 是相加的和,CO 是进位。

2.解:处于工作状态的译码器C 、D 应输入的状态C D ① 0 0 ② 0 1 ③ 1 0 ④11逻辑功能:由74LS139构成的4线—16线译码器3.解:由图可见,74HC138的功能扩展输入端必须满足E 1=1、032==E E 才能正常译码,因此E 1=A 3=1;542A A E =,即A 4=1,A 5=1; 0763=+=A A E ,即A 6=0,A 7=0。

所以,该地址译码器的译码地址范围为A 7A 6A 5A 4A 3A 2A 1A 0=00111A 2A 1A 0=00111000~3 3400111111,用十六进制表示即为38H ~3FH 。

输入、输出真值表如表P3.3-1所示。

表3.3-1 地址译码器的真值表4.解:由图写出逻辑函数并化简,得02460246L Y Y Y Y Y Y Y Y A BC ABC ABC ABC C ==+++=+++=5. 解:F AB B C A B C AB C ABC ABC =+=+++3 359.解:4选1数据选择器的逻辑表达式为: 301201101001D A A D A A D A A D A A Y +++=将A 1=A ,A 0=B ,D 0=1,D 1=C ,C D =2,D 3=C 代入得 ABC C B A BC A C B A C B A ABC C B A BC A B A Y ++++=+++=根据表达式可画出波形图:C ABL10.解:(1)写出逻辑函数表达式: C AB C B A BC A C B A C B A L ++++=(2)用卡诺图化简3 3611.解:567m m m ABC C B A ABC C AB AC AB L ++=+++=+=13. 解:D C B D C D D C A D C B D C C A F +++=++=)(0⋅+++=+++=CD D C D C A D C AB D C B D C D C A D C A令A 1=C ,A 0=D ,AB D =0,A D =1,D 2=1,D 3=0 连线图:14. 解:3 371。

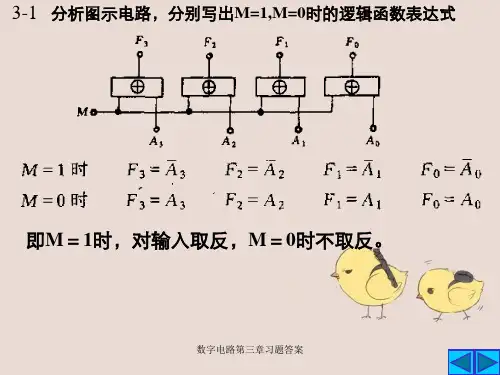

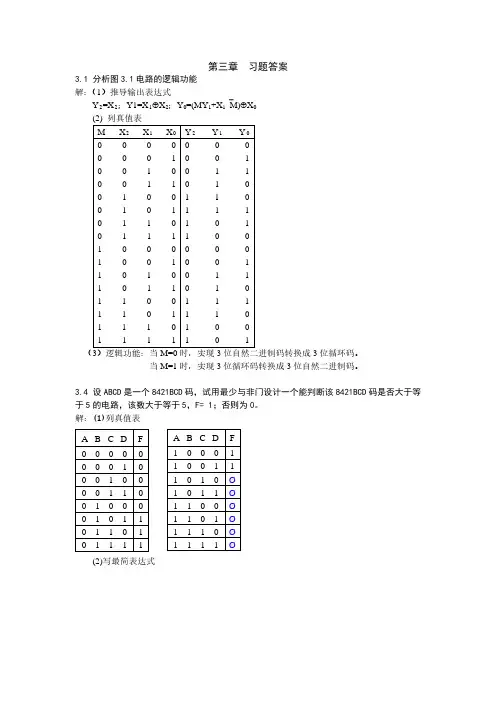

3-1 分析题图3-1所示电路,写出电路输出Y 1和Y 2的逻辑函数表达式,列出真值表,说明它的逻辑功能。

解:由题图3-1从输入信号出发,写出输出Y 1和Y 2的逻辑函数表达式为1Y A B C =⊕⊕ ; 2()()Y A B C AB A B C A =⊕⋅⋅=⊕⋅+B将上式中的A 、 B 、C 取值000~111,分别求出Y 1和Y 2,可得出真值表如题解 表3-1所示。

题解 表3-1ABCA B ⊕()A B C ⊕⋅AB1Y2Y0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 1 0 0 1 0 0 1 1 1 1 0 0 1 1 0 0 1 0 0 1 0 1 0 1 1 1 0 0 1 1 1 0 0 0 1 0 1 111111综上,由题解 表3-1可以看出,该电路实现了一位全加器的功能。

其中,A 和B 分别是被加数及加数,C 为相邻低位来的进位数;Y1为本位和数,Y 2为相邻高位的进位数。

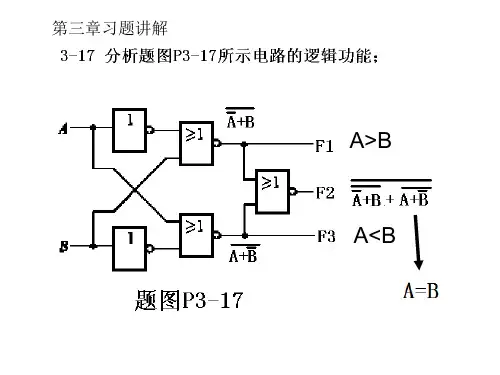

3-2 分析题图3-2所示电路,要求:写出输出逻辑函数表达式,列出真值表,画出卡诺图,并总结电路功能。

解:由题图3-2从输入信号出发,写出输出F 的逻辑函数表达式为()()F A B C D =:::将上式中的A 、 B 、C 、D 取值0000~1111,求出F ,可得真值表和卡诺图分别如题解 表3-2和题解 图3-1所示。

题解 表3-2A B C DA B : C D :F0 0 0 0 1 1 1 0 0 0 1 1 0 0 0 0 1 0 1 0 0 0 0 1 1 1 1 1 0 1 0 0 0 1 0 0 1 0 1 0 0 1 0 1 1 0 0 0 1 0 1 1 1 0 1 0 1 0 0 0 0 1 0 1 0 0 1 0 0 11 0 1 0 0 0 1 1 0 1 1 0 1 0 1 1 0 0 1 1 1 1 1 0 1 1 0 0 1 1 1 0 1 0 0 1 1 1 1 1 1 1综上,由题解 表3-2可以看出,当输入A 、 B 、C 、D 中含有偶数个“1”时,输出;否则,当输入A 、 B 、C 、D 中含有奇数个“1”时,输出。

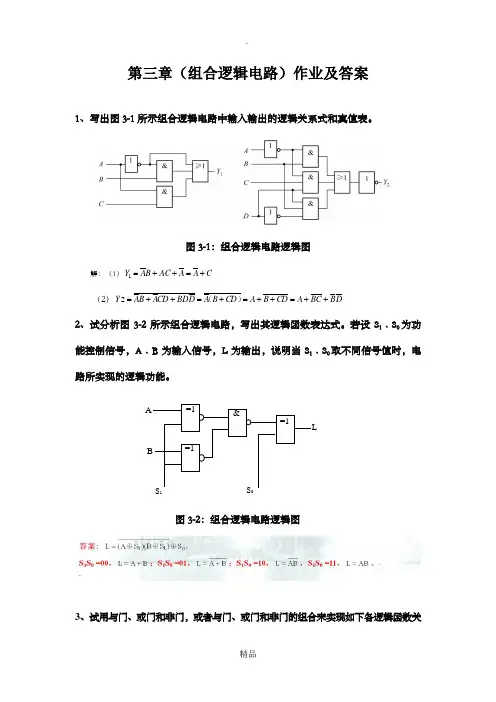

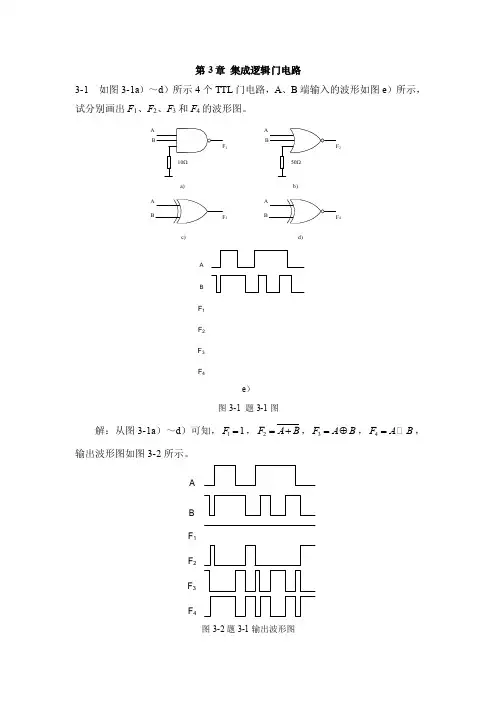

第3章集成逻辑门电路3-1 如图3-1a)~d)所示4个TTL门电路,A、B端输入的波形如图e)所示,试分别画出F1、F2、F3和F4的波形图。

A1A234a)b)c)d)F1F2F3F4BAe)图3-1 题3-1图解:从图3-1a)~d)可知,11F=,2F A B=+,3F A B=⊕,4F A B= ,输出波形图如图3-2所示。

F1F2F3F4AB图3-2题3-1输出波形图3-2 电路如图3-3a )所示,输入A 、B 的电压波形如图3-3b )所示,试画出各个门电路输出端的电压波形。

1A 23b)a)AB图3-3 题3-2图解:从图3-3a )可知,1F AB =,2F A B =+,3F A B =⊕,输出波形如图3-4所示。

F 1F 2F 3AB图3-4 题3-2输出波形3-3在图3-5a )所示的正逻辑与门和图b )所示的正逻辑或门电路中,若改用负逻辑,试列出它们的逻辑真值表,并说明F 和A 、B 之间是什么逻辑关系。

b)a)图3-5 题3-3图解:(1)图3-5a )负逻辑真值表如表3-1所示。

表3-1 与门负逻辑真值表F 与A 、B 之间相当于正逻辑的“或”操作。

(2)图3-5b )负逻辑真值表如表3-2所示。

表3-2 或门负逻辑真值表F 与A 、B 之间相当于正逻辑的“与”操作。

3-4试说明能否将与非门、或非门和异或门当做反相器使用?如果可以,各输入端应如何连接?解:与非门、或非门和异或门经过处理以后均可以实现反相器功能。

1)与非门:将多余输入端接至高电平或与另一端并联; 2)或非门:将多余输入端接至低电平或与另一端并联;3) 异或门:将另一个输入端接高电平。

3-5为了实现图3-6所示的各TTL 门电路输出端所示的逻辑关系,请合理地将多余的输入端进行处理。

b)a)AB=A B=+A BC DABC D图3-6 题3-5图解:a )多余输入端可以悬空,但建议接高电平或与另两个输入端的一端相连;b )多余输入端接低电平或与另两个输入端的一端相连;c) 未用与门的两个输入端至少一端接低电平,另一端可以悬空、接高电平或接低电平;d )未用或门的两个输入端悬空或都接高电平。

f 习题三3.1写出如图判p3.1中各逻辑图的逻辑表达式,并化简成最简与或表达式。

BCBC(a) (b)AA C(c)(d)图p3.1题3.1逻辑图解:(a )C B C B A C B C B A F +=•=(b) 1=)+(+)+(+)+(=+•+•+=C B B A C A C B B A C A F(c)CA BC AB C B A AB C B A AB F++=)⊕(+=)⊕(+=1 ABC C B A C B A C B A C B A F +++=⊕⊕=2(d)F=A⊙B⊙C= ABC C B A C B A C B A C AB B A C AB B A +++=•)+(+•+3.2、3.2、化简下列逻辑函数,并用与非门和或非门实现。

解:(1)∑)7,3,2,0(=),,(m C B A F与非门实现:BC B A BC B A F •=+=或非门实现:C B C A F +=,C B C A C B C A F F +++=)+)(+(== (2) C A C B AB C B A F ++=),,( 解:与非门实现:AB C AB C F •=+=或非门实现:C B C A F +=,C B C A C B C A F F +++=)+)(+(== ┏ (^ω^)=☞(3) ABD D C B C A B A D C B A F +++=),,,( 解:与非门实现:BCD AC AB BCD AC AB F ••=++= 或非门实现:C B D A C A B A F +++=,C BD A C A B A C B D A C A B A F F +++++++=)+)(+)(+)(+(==(4) ∑)15,14,10,8,2,0(=),,,(m D C B A F解:与非门实现:ABC BD ABC BD F •=+= 或非门实现:C B D B D A B A F +++=,C BD B D A B A C B D B D A B A F F +++++++=)+)(+)(+)(+(==(图略)3.3、分析如图p3.2所示组合逻辑电路,写出输出函数表达式,列出真值表,说明电路的逻辑功能。

第三章 时序逻辑1.写出触发器的次态方程,并根据已给波形画出输出 Q 的波形。

解:2. 说明由RS 触发器组成的防抖动电路的工作原理,画出对应输入输出波形解:3. 已知JK 信号如图,请画出负边沿JK 触发器的输出波形(设触发器的初态为0)1)(1=+++=+c b a Qa cb Q nn4. 写出下图所示个触发器次态方程,指出CP 脉冲到来时,触发器置“1”的条件。

解:(1),若使触发器置“1”,则A 、B 取值相异。

(2),若使触发器置“1”,则A 、B 、C 、D 取值为奇数个1。

5.写出各触发器的次态方程,并按所给的CP 信号,画出各触发器的输出波形(设初态为0)解:6. 设计实现8位数据的串行→并行转换器。

B A B A D +=DC B A K J ⊕⊕⊕==Q AQ B Q D Q C Q E Q F Q7. 分析下图所示同步计数电路解:先写出激励方程,然后求得状态方程状态图如下:该计数器是五进制计数器,可以自启动。

8. 作出状态转移表和状态图,确定其输出序列。

解:求得状态方程如下故输出序列为:000119. 用D 触发器构成按循环码(000→001→011→111→101→100→000)规律工作的六进制同步计数器解:先列出真值表,然后求得激励方程PS NS 输出N0 0 0 0 0 1 00 0 1 0 1 1 0 0 1 1 1 1 1 0 1 1 1 1 0 1 0 1 0 1 1 0 0 0 1 0 0 0 0 0 1化简得:逻辑电路图如下:n Q 2n Q 1n Q 012+n Q 11+n Q 10+n Q n n n nn n n n n n nnQ Q Q Q Q Q Q Q Q Q Q Q Z 121002*********+==+==+++nnn nnn nnnn QQ Q D QQ Q D QQ Q Q D 121211121122+====+==+++10. 用D 触发器设计3位二进制加法计数器,并画出波形图。