西安电子科技大学2010年微机原理试题

- 格式:doc

- 大小:170.00 KB

- 文档页数:5

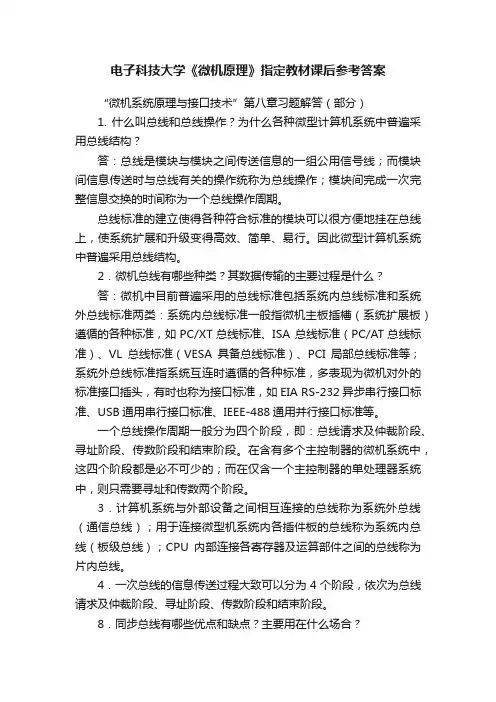

电子科技大学《微机原理》指定教材课后参考答案“微机系统原理与接口技术”第八章习题解答(部分)1. 什么叫总线和总线操作?为什么各种微型计算机系统中普遍采用总线结构?答:总线是模块与模块之间传送信息的一组公用信号线;而模块间信息传送时与总线有关的操作统称为总线操作;模块间完成一次完整信息交换的时间称为一个总线操作周期。

总线标准的建立使得各种符合标准的模块可以很方便地挂在总线上,使系统扩展和升级变得高效、简单、易行。

因此微型计算机系统中普遍采用总线结构。

2.微机总线有哪些种类?其数据传输的主要过程是什么?答:微机中目前普遍采用的总线标准包括系统内总线标准和系统外总线标准两类:系统内总线标准一般指微机主板插槽(系统扩展板)遵循的各种标准,如PC/XT总线标准、ISA 总线标准(PC/AT总线标准)、VL总线标准(VESA具备总线标准)、PCI局部总线标准等;系统外总线标准指系统互连时遵循的各种标准,多表现为微机对外的标准接口插头,有时也称为接口标准,如EIA RS-232异步串行接口标准、USB通用串行接口标准、IEEE-488通用并行接口标准等。

一个总线操作周期一般分为四个阶段,即:总线请求及仲裁阶段、寻址阶段、传数阶段和结束阶段。

在含有多个主控制器的微机系统中,这四个阶段都是必不可少的;而在仅含一个主控制器的单处理器系统中,则只需要寻址和传数两个阶段。

3.计算机系统与外部设备之间相互连接的总线称为系统外总线(通信总线);用于连接微型机系统内各插件板的总线称为系统内总线(板级总线);CPU内部连接各寄存器及运算部件之间的总线称为片内总线。

4.一次总线的信息传送过程大致可以分为4个阶段,依次为总线请求及仲裁阶段、寻址阶段、传数阶段和结束阶段。

8.同步总线有哪些优点和缺点?主要用在什么场合?答:同步并行总线时序是指总线上所有信号均以同步时钟为基准,所有接在总线上的设备的信息传输也严格与同步时钟同步。

同步并行总线的优点是简单、易实现;缺点是无法兼容总线上各种不同响应速度的设备,因为同步时钟的速度必须以最慢的响应设备为准,这样总线上的高速设备将无法发挥其高速性能。

电子科技大学微机原理大题(含答案)目录第一章概述 (4)阐述摩尔定律,它有什么限制? (4)什么是Soc?什么是IP核?它有哪几种实现形式? (4)什么是嵌入式系统?它有哪些特点? (4)第二章计算机系统的结构组成与工作原理 (5)说明RISC架构与CISC架构之间的区别 (5)举例说明计算机体系结构、组成和实现之间的关系 (5)试说明现代计算机系统中常用的并行技术及其效果? (5)某时钟频率为1.25GHz、平均CPI为5的非流水线式处理器,其升级版本引入了6级流水线,但因存在诸如锁存延迟等流水线内部延迟,升级版处理器的时钟频率必须降到1GHz。

(5)简述冯.诺依曼体系结构的核心,并分析冯.诺依曼计算机存在的瓶颈? (6)简述冯.诺依曼计算机的实质 (6)第三章微处理器体系结构及关键技术 (6)试比较计算机各体系结构的优缺点 (6)常见的流水线冒险包括哪几种?如何解决? (7)试比较随机逻辑和微码体系结构的优缺点 (7)什么是微码体系结构?微指令的作用是什么? (7)第四章总线技术与总线标准 (7)比较串、并行通信的特点,为什么现代计算机中有总线串行化的趋势? (7)试比较同步、半同步、异步总线时序的优缺点 (8)RAM与CPU的连接有哪几类信号线?简述电路设计时需要考虑的几个问题? (8)计算机系统的总线仲裁有哪几种类型?请简述串行总线仲裁。

(8) 什么是总线?微机中三总线是指?微机系统采用总线的好处是?(8)第五章存储器系统 (9)简述Cache-主存层次与主存-辅存层次的不同点。

(9)什么是高速缓存技术和虚拟存储器技术?采用它们的目的是什么?(9)什么是虚拟地址?试简述虚拟存储器的基本工作原理。

(9)什么是存储器访问的局部性原理?它有哪几种含义? (9)试为某8位计算机系统设计一个具有8KB ROM和40KB RAM的存储器。

要求ROM用EPROM芯片2732组成,从0000H地址开始;RAM用SRAM 芯片6264组成,从4000H地址开始。

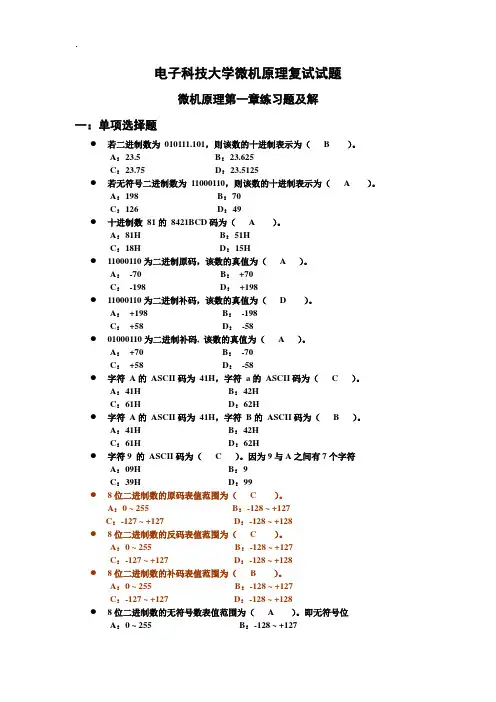

电子科技大学微机原理复试试题微机原理第一章练习题及解一:单项选择题●若二进制数为010111.101,则该数的十进制表示为( B )。

A:23.5 B:23.625C:23.75 D:23.5125●若无符号二进制数为11000110,则该数的十进制表示为( A )。

A:198 B:70C:126 D:49●十进制数81的8421BCD码为( A )。

A:81H B:51HC:18H D:15H●11000110为二进制原码,该数的真值为( A )。

A:-70 B:+70C:-198 D:+198●11000110为二进制补码,该数的真值为( D )。

A:+198 B:-198C:+58 D:-58●01000110为二进制补码, 该数的真值为( A )。

A:+70 B:-70C:+58 D:-58●字符A的ASCII码为41H,字符a的ASCII码为( C )。

A:41H B:42HC:61H D:62H●字符A的ASCII码为41H,字符B的ASCII码为( B )。

A:41H B:42HC:61H D:62H●字符9 的ASCII码为( C )。

因为9与A之间有7个字符A:09H B:9C:39H D:99●8位二进制数的原码表值范围为( C )。

A:0 ~ 255 B:-128 ~ +127C:-127 ~ +127 D:-128 ~ +128●8位二进制数的反码表值范围为( C )。

A:0 ~ 255 B:-128 ~ +127C:-127 ~ +127 D:-128 ~ +128●8位二进制数的补码表值范围为( B )。

A:0 ~ 255 B:-128 ~ +127C:-127 ~ +127 D:-128 ~ +128●8位二进制数的无符号数表值范围为( A )。

即无符号位A:0 ~ 255 B:-128 ~ +127C:-127 ~ +127 D:-128 ~ +128●n+1位符号数X的原码表值范围为( A )。

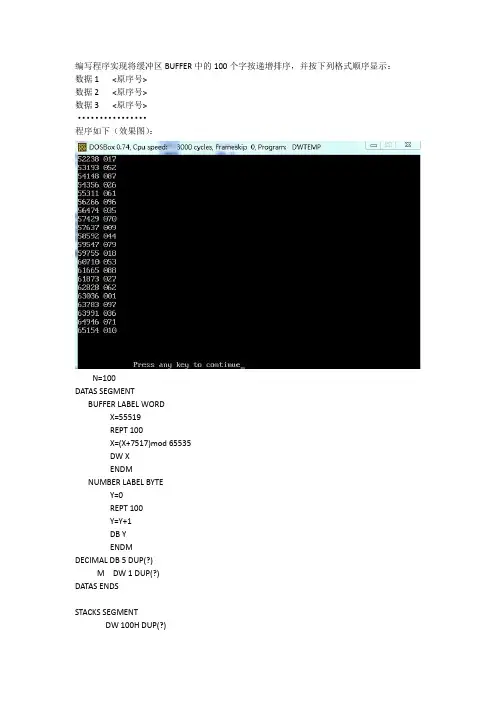

编写程序实现将缓冲区BUFFER中的100个字按递增排序,并按下列格式顺序显示:数据1 <原序号>数据2 <原序号>数据3 <原序号>················程序如下(效果图):N=100DATAS SEGMENTBUFFER LABEL WORDX=55519REPT 100X=(X+7517)mod 65535DW XENDMNUMBER LABEL BYTEY=0REPT 100Y=Y+1DB YENDMDECIMAL DB 5 DUP(?)M DW 1 DUP(?)DATAS ENDSSTACKS SEGMENTDW 100H DUP(?)TOP LABEL WORDSTACKS ENDSCODES SEGMENTASSUME CS:CODES,DS:DATAS,SS:STACKS START:MOV AX,DATASMOV DS,AXMOV ES,AXMOV AX,STACKSMOV SS,AXLEA SP,TOPXOR AX,AX ;开始程序LEA SI,BUFFERLEA DI,NUMBERCALL SORTMOV CX,N ;显示程序开始L1:MOV AX,[SI]MOV M,5CALL DISPAXDCALL DISPEMADD SI,2 ;显示数值XOR AX,AXMOV AL,[DI]MOV M,3CALL DISPAXDCALL DISPCRINC DI ;显示序号LOOP L1MOV AH,4CHMOV AL,0INT 21HSORT PROC NEARPUSH SIPUSH DIPUSH AXPUSH BXPUSH CXMOV CX,N;开始冒泡程序DEC CXLP1: ;外循环PUSH SIPUSH DIPUSH CXLP2: ;内循环MOV AX,[SI]CMP AX,[SI+2]JBE NOXCHGXCHG AX,[SI+2]MOV [SI],AXMOV BL,[DI]XCHG BL,[DI+1]MOV [DI],BLNOXCHG:ADD SI,2INC DILOOP LP2POP CXPOP DIPOP SILOOP LP1 ;冒泡结束POP CXPOP BXPOP AXPOP DIPOP SIRETSORT ENDPDISPAXD PROC NEARPUSH AXPUSH BXPUSH CXPUSH DXPUSH DILEA DI,DECIMALCALL TRANS16TO10MOV CX,MMOV BX,CXDEC BXLEA DI,DECIMAL[BX];指向最高位MOV AH,2DISPAXD2:MOV DL,[DI]ADD DL,30HDEC DIINT 21HLOOP DISPAXD2POP DIPOP DXPOP CXPOP BXPOP AXRETDISPAXD ENDPTRANS16TO10 PROC NEARPUSH AXPUSH BXPUSH CXPUSH DXPUSH DIMOV BX,10MOV CX,MTRANS1:XOR DX,DXDIV BXMOV [DI],DLINC DILOOP TRANS1POP DIPOP DXPOP CXPOP BXPOP AXRETTRANS16TO10 ENDPDISPEM PROC NEARPUSH AXPUSH DXMOV AL,20HMOV AH,02MOV DL,ALINT 21H ;显示一位字符POP DXPOP AXRETDISPEM ENDPDISPCR PROC NEARPUSH AXPUSH DXMOV AL,0AHMOV AH,02MOV DL,ALINT 21H ;显示一位字符POP DXPOP AXRETDISPCR ENDPCODES ENDSEND START。

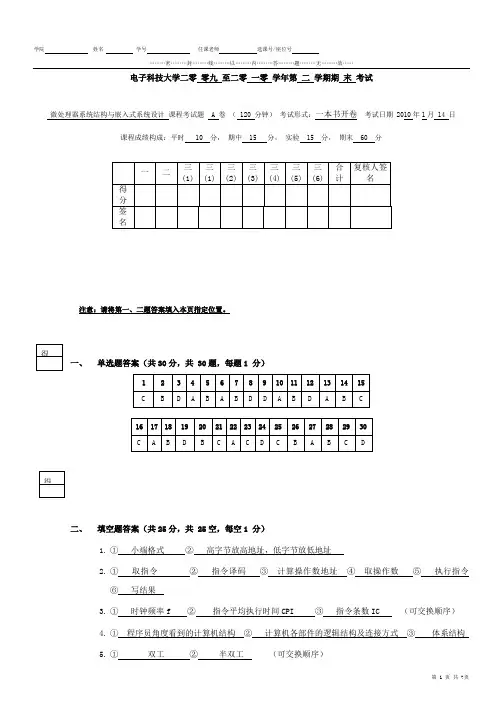

………密………封………线………以………内………答………题………无………效……电子科技大学二零 零九 至二零 一零 学年第 二 学期期 末 考试微处理器系统结构与嵌入式系统设计 课程考试题 A 卷 ( 120 分钟) 考试形式:一本书开卷 考试日期 2010年1月 14 日课程成绩构成:平时 10 分, 期中 15 分, 实验 15 分, 期末 60 分注意:请将第一、二题答案填入本页指定位置。

一、 单选题答案(共30分,共 30题,每题1 分)二、 填空题答案(共25分,共 25空,每空1 分)1. ① 小端格式 ② 高字节放高地址,低字节放低地址2. ① 取指令 ② 指令译码 ③ 计算操作数地址 ④ 取操作数 ⑤ 执行指令 ⑥ 写结果3. ① 时钟频率f ② 指令平均执行时间CPI ③ 指令条数IC (可交换顺序)4. ① 程序员角度看到的计算机结构 ② 计算机各部件的逻辑结构及连接方式 ③ 体系结构5. ① 双工 ② 半双工 (可交换顺序)………密………封………线………以………内………答………题………无………效……6.①一次存取及处理数据7.① IRQ ② FRQ (可交换顺序)8.① R0~R3 ②堆栈单元9.①初始化硬件及加载操作系统10.①功能(黑盒)②覆盖(白盒)③灰盒(可交换顺序)一、单选题(共30分,共 30题,每题1 分)1. 计算机内机器数通常采用()形式来表示。

A、原码B、反码C、补码D、ASCII码2. 组合BCD码“87H”代表的十进制真值是()。

A、78B、87C、-120D、+1203. 若下列字符码中有奇偶校验位,但没有数据错误,那么采用偶校验的字符码是( )。

A、11001011B、11010110C、11000001D、110010014. 冯·诺依曼基本思想主要是提出了()。

A、二进制和程序存储B、CPU和存储器C、二进制和存储器D、存储器和输入输出设备5. 以下叙述中,不符合RISC指令系统特点的是()。

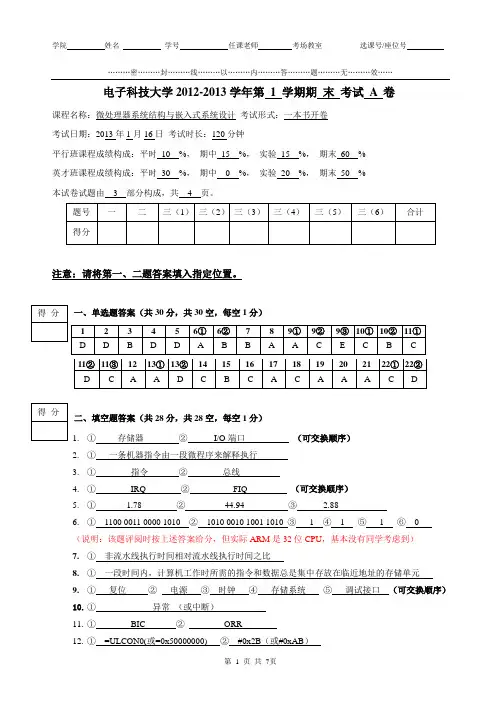

………密………封………线………以………内………答………题………无………效……电子科技大学2012-2013学年第 1 学期期 末 考试 A 卷课程名称:微处理器系统结构与嵌入式系统设计 考试形式:一本书开卷 考试日期:2013年1月16日 考试时长:120分钟平行班课程成绩构成:平时 10 %, 期中 15 %, 实验 15 %, 期末 60 % 英才班课程成绩构成:平时 30 %, 期中 0 %, 实验 20 %, 期末 50 % 本试卷试题由 3 部分构成,共 4 页。

注意:请将第一、二题答案填入指定位置。

一、单选题答案(共30分,共30空,每空1分)二、填空题答案(共28分,共28空,每空1分)1. ① 存储器 ② I/O 端口 (可交换顺序)2. ① 一条机器指令由一段微程序来解释执行3. ① 指令 ② 总线4. ① IRQ ② FIQ (可交换顺序)5. ① 1.78 ② 44.94 ③ 2.886. ① 1100 0011 0000 1010 ② 1010 0010 1001 1010 ③ 1 ④ 1 ⑤ 1 ⑥ 0 (说明:该题评阅时按上述答案给分,但实际ARM 是32位CPU ,基本没有同学考虑到)7. ① 非流水线执行时间相对流水线执行时间之比8. ① 一段时间内,计算机工作时所需的指令和数据总是集中存放在临近地址的存储单元 9. ① 复位 ② 电源 ③ 时钟 ④ 存储系统 ⑤ 调试接口 (可交换顺序) 10. ① 异常 (或中断) 11. ① BIC ② ORR12. ① =ULCON0(或=0x50000000) ② #0x2B (或#0xAB )………密………封………线………以………内………答………题………无………效……一、单选题(共30分,共30空,每空1分)1.以下常用总线标准中,不属于片内总线的是()。

A、Core ConnectB、AMBAC、AvalonD、SATA2.计算机系统中,以下不属于“异常”的是()。

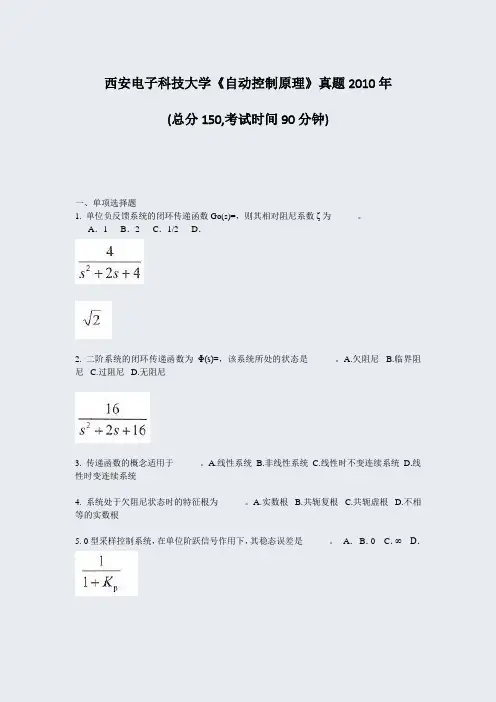

西安电子科技大学《自动控制原理》真题2010年(总分150,考试时间90分钟)一、单项选择题1. 单位负反馈系统的闭环传递函数Go(s)=,则其相对阻尼系数ζ为______。

A.1 B.2 C.1/2 D.2. 二阶系统的闭环传递函数为Φ(s)=,该系统所处的状态是______。

A.欠阻尼 B.临界阻尼 C.过阻尼 D.无阻尼3. 传递函数的概念适用于______。

A.线性系统B.非线性系统C.线性时不变连续系统D.线性时变连续系统4. 系统处于欠阻尼状态时的特征根为______。

A.实数根 B.共轭复根 C.共轭虚根 D.不相等的实数根5. 0型采样控制系统,在单位阶跃信号作用下,其稳态误差是______。

A.B.0 C.∞ D.6. 单位负反馈系统的开环传递函数为,则其相角裕量γ______。

A.180°-arctanτωcB.180°+arctanτωcC.180°-arctanτωnD.180°+arctanτωn7. 设s=σ+jω是s平面上的点,当该点映射到z平面上位于单位圆以外的区域时,则有______。

A.σ=0B.σ>0C.σ<0D.ω<08. 一阶保持器两相邻采样点之间的输出是______。

A.线性变化 B.常值 C.线性减小 D.线性增加9. 某系统开环对数幅频特性曲线第一个转折频率之前的斜率为-1,则该系统的型号为______。

A.0型系统 B.Ⅰ型系统 C.Ⅱ型系统 D.Ⅲ型系统10. 相位滞后校正装置的传递函数为Gc(s)=,其中α应为______。

A.α<1 B.0<α<1 C.α<0 D.α>111. 相位超前校正网络的传递函数为Gc(s)=,其中系数β应为______。

A.β<-1 B.β>1 C.0<β<1 D.β<012. 已知系统的输出Z变换Y(z)=,它符合附图中哪些系统?______ A.B.C.D.二、双项选择题1. 闭环控制系统的特点是______。

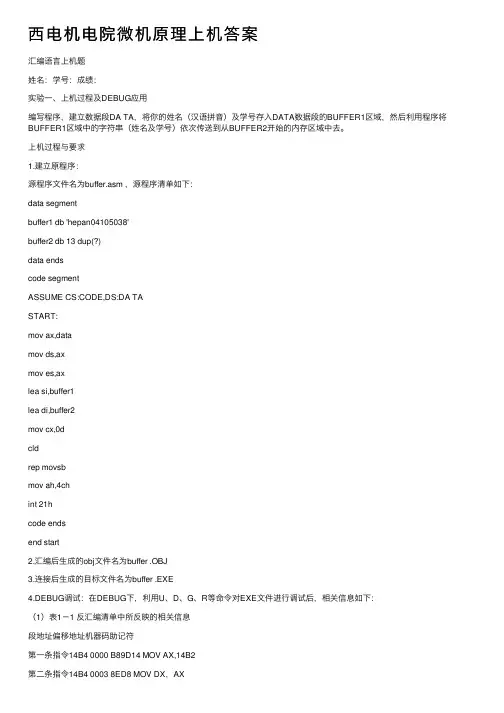

西电机电院微机原理上机答案汇编语⾔上机题姓名:学号:成绩:实验⼀、上机过程及DEBUG应⽤编写程序,建⽴数据段DA TA,将你的姓名(汉语拼⾳)及学号存⼊DATA数据段的BUFFER1区域,然后利⽤程序将BUFFER1区域中的字符串(姓名及学号)依次传送到从BUFFER2开始的内存区域中去。

上机过程与要求1.建⽴原程序:源程序⽂件名为buffer.asm ,源程序清单如下:data segmentbuffer1 db 'hepan04105038'buffer2 db 13 dup(?)data endscode segmentASSUME CS:CODE,DS:DA TASTART:mov ax,datamov ds,axmov es,axlea si,buffer1lea di,buffer2mov cx,0dcldrep movsbmov ah,4chint 21hcode endsend start2.汇编后⽣成的obj⽂件名为buffer .OBJ3.连接后⽣成的⽬标⽂件名为buffer .EXE4.DEBUG调试:在DEBUG下,利⽤U、D、G、R等命令对EXE⽂件进⾏调试后,相关信息如下:(1)表1-1 反汇编清单中所反映的相关信息段地址偏移地址机器码助记符最后⼀条指令14B4 001E D1E3 SHL BX,1*注:最后⼀条指令是对应于代码段中最后⼀条指令(2)在未执⾏程序之前,⽤D命令显⽰内存区域BUFFER1及BUFFER2中的内容,其相关信息如表1-2所⽰。

表1-2 未执⾏程序之前的数据区内容变量区段地址值偏移地址变量值(或字符串)BUFFER1 14B2 0000 hepan04105038BUFFER2 14B2 000D ………….(3)执⾏程序以后⽤D命令显⽰内存区域的相关信息,如表1-3。

表1-3 执⾏程序之后的数据区内容变量区段地址值偏移地址变量值(字符串)BUFFER1 14B2 0000 hepan04105038BUFFER2 14B2 000D hepan04105038(4)⽤R命令检查寄存器的内容如表1-4所⽰。

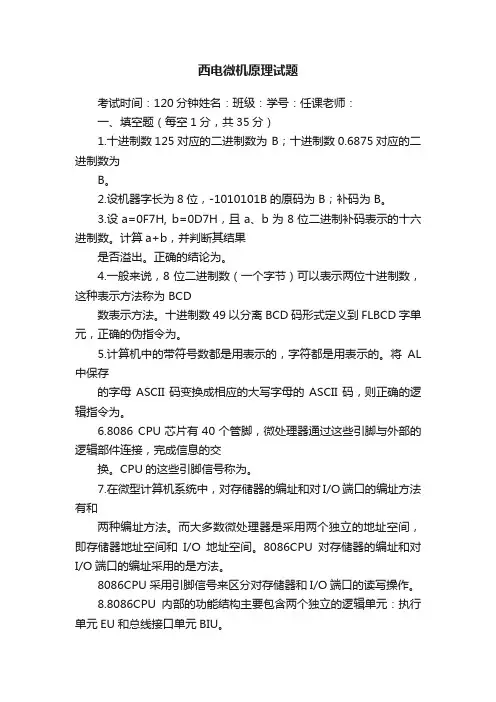

西电微机原理试题考试时间:120分钟姓名:班级:学号:任课老师:一、填空题(每空1分,共35分)1.十进制数125对应的二进制数为 B;十进制数0.6875对应的二进制数为B。

2.设机器字长为8位,-1010101B的原码为 B;补码为 B。

3.设a=0F7H, b=0D7H,且a、b为8位二进制补码表示的十六进制数。

计算a+b,并判断其结果是否溢出。

正确的结论为。

4.一般来说,8位二进制数(一个字节)可以表示两位十进制数,这种表示方法称为 BCD数表示方法。

十进制数49以分离BCD码形式定义到FLBCD 字单元,正确的伪指令为。

5.计算机中的带符号数都是用表示的,字符都是用表示的。

将AL 中保存的字母ASCII码变换成相应的大写字母的ASCII码,则正确的逻辑指令为。

6.8086 CPU芯片有40个管脚,微处理器通过这些引脚与外部的逻辑部件连接,完成信息的交换。

CPU的这些引脚信号称为。

7.在微型计算机系统中,对存储器的编址和对I/O端口的编址方法有和两种编址方法。

而大多数微处理器是采用两个独立的地址空间,即存储器地址空间和I/O地址空间。

8086CPU对存储器的编址和对I/O端口的编址采用的是方法。

8086CPU采用引脚信号来区分对存储器和I/O端口的读写操作。

8.8086CPU内部的功能结构主要包含两个独立的逻辑单元:执行单元EU和总线接口单元BIU。

其中BIU主要完成。

9.在8086CPU的寄存器组织中,通用寄存器分别为。

10.8086微处理器状态字PSW是一个16位的寄存器,一共设定了9个标志位,其中用于反映ALU前一次操作结果的状态标志分别为;若(AX)=5439H,则8086CPU 执行ADD AX,476AH指令后,OF= ;执行AND AX,476AH指令后,OF= 。

11.有一块120个字的存储区域,其起始地址为625AH:234DH,则这个存储区域的末地址单元的物理地址为。

西安电子科技大学微机原理大作业第一次上机一、实验目的1. 熟练掌握8086/8088的各种寻址方式及应用。

2.掌握DEBUG调试程序中的一些常用命令的使用方法,为以后的实验打下基础二、实验仪器586微机 1台三、实验内容1.关于数据的寻址方式练习8086/8088 提供多种方式实现操作数寻址,大体可分为7种:a. 立即寻址b. 寄存器寻址c. 直接寻址d. 寄存器间接寻址e. 寄存器相对寻址f. 基址变址寻址g. 基址变址且相对寻址掌握8086/8088的这些寻址方式,是学习汇编语言编程的关键。

指令SRC 寻址方式SRC的地址AX 推算值AX 实际值MOV AX, CX寄存器寻址0005 0005 MOV AX, 500H 立即寻址0500 0500 MOV AX, TABLE 直接寻址1541:0004 A5A 4 A5A 4MOV AX, ES:[BX] 寄存器间接寻址 1542:0004 C5C 4 C5C4MOV AX, [BX+05H] 寄存器相对寻址 1541:0009 AAA 9 AAA 9 MOV AX,寄存器相153FB8B B8B7 MOV AX, TABLE [BX] 寄存器相对寻址 1541:0008 A9A 8 A9A8MOV AX, 07H [BX] 寄存器相对寻址 1541:000B ACA B ACA BMOV AX, [BP]寄存器间接寻址 153F :0003 B4B 3 B4B 3 MOV AX, TABLE [BP] 寄存器相对寻址 1541:0007 A8A 7 A8A 7 MOV AX, 08H [BP] 寄存器相对寻址 153F :000B BCB B BCB B MOV AX, [BP+06H] 寄存器相对寻址 153F :0009 BAB 9 BAB 9 MOV AX,寄存器相1541A7A A7A6MOV AX, [BP]+05H 寄存器相对寻址153F:0008B9B8B9B8MOV AX, ES: [SI+03H] 寄存器相对寻址1542:0005C6C5C6C5MOV AX, [DI+06H] 寄存器相对寻址1541:0007A8A7A8A7MOV AX, [DI]+05H 寄存器相对寻址1541:0006A7A6A7A6MOV AX, TABLE [SI] 寄存器相对寻址1541:0006A7A6A7A6MOV AX, [SI] 寄存器间接寻址1541:0002A3A2A3A2MOV AX, TABLE 寄存器相1541A6A A6A[DI] 对寻址:00055 5MOV AX, [SI]+05H 寄存器相对寻址1541:0007A8A7A8A7MOV AX, [BX] [DI+01H] 基址变址且相对寻址1541:0006A7A6A7A6MOV AX, [BX] [SI]+03H 基址变址且相对寻址1541:0009AAA9AAA9MOV AX, TABLE [BX] [SI] 基址变址且相对寻址1541:000AABAAABAAMOV AX, ES:[BX] [DI] 基址变址寻址1542:0005C6C5C6C5MOV AX, [BP] [DI+02H] 基址变址且相对寻址153F:0006B7B6B7B6MOV AX, TABLE 基址变址1541A9A A9A[BP] [DI] 且相对寻址:00088 8MOV AX, ES:[BP] [SI] 基址变址寻址1542:0005C6C5C6C5MOV AX, [BP] [SI+05H] 基址变址且相对寻址153F:000ABBBABBBAMOV AX, 03H [BP] [DI] 基址变址且相对寻址153F:0007B8B7B8B7MOV AX, [BP] [SI] 基址变址寻址153F:0005B6B5B6B5MOV AX, [BP+02H] [DI+03H] 基址变址且相对寻址153F:0009BAB9BAB9MOV AX, TABLE [BP+02H][DI+03H] 基址变址且相对寻址1541:000DAEADAEAD第二次上机一、实验目的1. 熟练掌握汇编语言程序设计的方法及上机步骤。

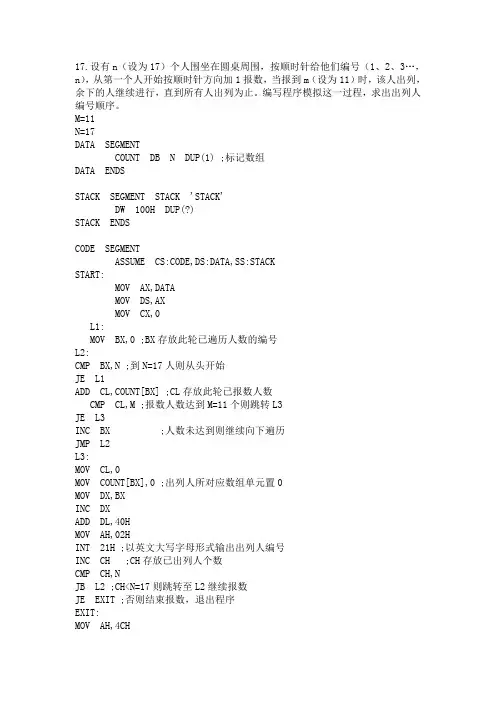

17.设有n(设为17)个人围坐在圆桌周围,按顺时针给他们编号(1、2、3…,n),从第一个人开始按顺时针方向加1报数,当报到m(设为11)时,该人出列,余下的人继续进行,直到所有人出列为止。

编写程序模拟这一过程,求出出列人编号顺序。

M=11N=17DATA SEGMENTCOUNT DB N DUP(1) ;标记数组DATA ENDSSTACK SEGMENT STACK 'STACK'DW 100H DUP(?)STACK ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA,SS:STACKSTART:MOV AX,DATAMOV DS,AXMOV CX,0L1:MOV BX,0 ;BX存放此轮已遍历人数的编号L2:CMP BX,N ;到N=17人则从头开始JE L1ADD CL,COUNT[BX] ;CL存放此轮已报数人数CMP CL,M ;报数人数达到M=11个则跳转L3JE L3INC BX ;人数未达到则继续向下遍历JMP L2L3:MOV CL,0MOV COUNT[BX],0 ;出列人所对应数组单元置0MOV DX,BXINC DXADD DL,40HMOV AH,02HINT 21H ;以英文大写字母形式输出出列人编号INC CH ;CH存放已出列人个数CMP CH,NJB L2 ;CH<N=17则跳转至L2继续报数JE EXIT ;否则结束报数,退出程序EXIT:MOV AH,4CHINT 21HCODE ENDSEND START4.39 (上机题)编写程序实现下列5项功能,通过从键盘输入1~5进行菜单式选择:(1)按数字键“1”,完成将字符串中的小写字母变换成大写字母。

用户输入由英文大小写字母或数字0~9组成的字符串(以回车结束),变换后按下列格式在屏幕上显示: <原字符串>例如:abcdgyt0092<新字符串> ABCDGYT0092按任一键重做;按Esc键返回主菜单。

微机复习题与考点1.CPU子系统包括:运算器、控制器、寄存器(注意不是存储器!)2.若流水线分为6段,每段拍长均为200ps,运行一个有100000条指令的程序,则其延时为__1.2ns__,加速比为_6__、最大吞吐量为__5 GIPS_(不是实际吞吐量!)。

3.CPU响应中断时保护“现场”和“断点”的目的是为了使中断正常返回,这里的“现场”指中断发生前各寄存器的值,“断点”指中断返回地址。

4.超标量结构:微处理器内部含有多条指令流水线和多个执行部件。

5.RISC执行程序的速度优于CISC的主要原因是:RISC的指令平均周期数较少。

6.四级存储器:寄存器、Cache、主存、辅存。

7.微处理器内部CPSR的主要作用:产生影响或控制某些后续指令所需的标志。

8.微码控制器的特点:控制单元的输入和输出之间的关系被视为一个内存单元。

9.Flash:写入速度类似于RAM,掉电后存储内容又不丢失的存储器。

10.CPI(Cycles Per Instruction):执行每条指令的平均周期数。

11.MIPS:每秒百万条指令,即处理器带宽,是衡量CPU运行速度的单位。

MIPS=f(MHz)/CPI。

12.执行时间T(s):(IC * CPI)/f(Hz)13.Bootloader:完成硬件初始化和加载操作系统。

14.设某CPU中一条指令执行过程分为“取指”,“分析”,和“执行”三个阶段,每一段执行时间分别为t、t和2t,则按照顺序方式连续执行n条指令需要时间为__4nt___,若忽略延迟的影响,则采用上述三级流水线时需要的时间为___2(n+1)t_(当n很大时,约为2nt)__,该流水线的加速比为2nn+1(当n很大时,约为2)。

15.流水线性能指标:实际吞吐量 = N/T流水,加速比 =T非流T流水。

16.总线仲裁:合理地控制和管理系统中多个主设备的总线请求,以避免总线冲突。

17.按照ATPCS的规定,ARM系统中子程序的调用可以利用R0~R3 四个寄存器来传递参数,更多的参数传递可利用堆栈来传递。

《微型计算机原理及接口技术》试题一. 单项选择题1. 8086CPU芯片的外部引线中,数据线的条数为○①6条②8条③16条④20条2. 8088CPU上READY信号为下面哪种信号有效?○①上升边②下降边③高电平④低电平3. 8088CPU中的CS寄存器是一个多少位的寄存器?○①8位②16位③24位④32位4. 当8086CPU 读写内存的一个规则(对准)字(16位)时,BHE和A0的状态必须是○①00 ②01 ③10 ④115. 当8086CPU读I/O接口时,信号M/IO和DT/R的状态必须是○①00 ②01 ③10 ④116. 在8088CPU中, 用于寄存器间接寻址输入输出指令的寄存器是○①AX ②BX ③CX ④DX7. ISA总线是一种多少位的内(系统)总线?○①8位②16位③32位④64位8. 属于只读存贮器的芯片是○①SRAM ②DRAM ③EPROM ④SDRAM9. 需要定时刷新的存贮器是○①SRAM ②DRAM ③EPROM ④EEPROM10. 内存从A4000H到CBFFFH,共有○①124K ②160K ③180K ④224K11. 擦除EPROM是用○①+5V电压②+15V电压③+21V电压④紫外光照射12. 采用查询方式来实现输入输出是因为它○①速度最快②CPU可以不介入③实现起来比较容易④在对多个事件查询工作时,能对突发事件做出实时响应13. 实现DMA传送,需要○①CPU通过执行指令来完成②CPU利用中断方式来完成③CPU利用查询方式来完成④不需要CPU参与即可完成14 下面哪种说法不正确○①内存地址也可做为接口地址使用②内存地址不可做为接口地址使用③接口地址不可做为内存地址使用④接口地址也可做为外存地址使用15. 8255工作在方式0时,下面哪种说法正确○①A、B、C三个口输入均有锁存能力②只有A口输入有锁存能力③只有C口输入有锁存能力④A、B、C三个口输入均无锁存能力二. 多项选择(在备选的答案中选出正确的答案,每小题2.5分, 本题共10分)1 . 在构成8 0 88最大模式下构成系统总线时,可用到下列哪些芯片?○①74LS373 ②8288 ③74LS245 ④74LS138 ⑤82892 . 8086CPU一个总线周期可以读(或写)的字节数为○①1个②2个③3个④4个⑤6个3. 当8255的A口工作在方式2,B口工作在方式0时,其C口可用作○①全部用作联络信号②5条用作联络信号③4条用作联络信号④3条用作I/O ⑤8条用作I/O4. 当8086CPU最大模式下读内存时,下列哪些信号的状态是正确的?○①MEMR=0 ②MEMW=0 ③IOW=1 ④IOR=0 ⑤DT/R=0三. 判断题1. 8086CPU的复位启动地址为0FFFFH。

第二章习题答案2.2 完成下列逻辑运算(1)101+1.01 = 110.01(2)1010.001-10.1 = 111.101(3)-1011.0110 1-1.1001 = -1100.1111 1(4)10.1101-1.1001 = 1.01(5)110011/11 = 10001(6)(-101.01)/(-0.1) = 1010.12.3 完成下列逻辑运算(1)1011 0101∨1111 0000 = 1111 0101(2)1101 0001∧1010 1011 = 1000 0001(3)1010 1011⊕0001 1100 = 1011 01112.4 选择题(1)下列无符号数中最小的数是( A )。

A.H(1,1011,0101) (01A5)B.B(3764)C.D(2590)D.O (2)下列无符号数中最大的数是( B )。

A.B(227)(10010101)B.OC.H(143)(96)D.D(3)在机器数( A )中,零的表示形式是唯一的。

A.补码B.原码C.补码和反码D.原码和反码(4)单纯从理论出发,计算机的所有功能都可以交给硬件实现。

而事实上,硬件只实现比较简单的功能,复杂的功能则交给软件完成。

这样做的理由是( BCD )。

A.提高解题速度B.降低成本C.增强计算机的适应性,扩大应用面D.易于制造(5)编译程序和解释程序相比,编译程序的优点是( D ),解释程序的优点是( C )。

A.编译过程(解释并执行过程)花费时间短B.占用内存少C.比较容易发现和排除源程序错误D.编译结果(目标程序)执行速度快2.5通常使用逻辑运算代替数值运算是非常方便的。

例如,逻辑运算AND将两个位组合的方法同乘法运算一样。

哪一种逻辑运算和两个位的加法几乎相同?这样情况下会导致什么错误发生?逻辑运算OR和两个位的加法几乎相同。

问题在于多个bit的乘或加运算无法用AND或OR运算替代,因为逻辑运算没有相应的进位机制。

电子科技大学二零零四至二零零五学年第二学期《微机系统原理与接口技术》课程考试题题号一二三四五六七总分满分15 15 10 24 6 11 19 100 得分评卷教师一、填空题(每空1分,共15分)1.PC/XT微机开机后,第一条执行的指令存放地址为()。

2.当运算结果为0时,状态标志ZF的值为()。

3.8086的INTR端输入一个()电平时,可屏蔽中断获得了中断请求。

4.32位逻辑地址5890H:3200H表示的实际地址值是()。

5.若CPU的地址总线宽度为N ,则可寻址()个存储器单元。

6.ISA总线的AEN信号线为低电平时,表示由()控制地址总线和读/写命令线。

7.8086从I/O端口地址20H输入字节数据的指令是()。

8.当INT 21H中断的功能号为02H时,它的入口参数送寄存器()。

9.响应可屏蔽中断INTR的条件是控制标志IF=()。

10. 若8086的外部中断INTR、NMI同时有中断请求,应先响应()。

11.PC系统中,在可屏蔽中断的第()个INTA响应周期传送中断类型码。

12.串行通信协议分为串行异步通信协议和()。

13.二片可编程中断控制器8259主从连接时最多可供()个中断源。

14.DAC0832有三种工作方式,即直通方式、()方式和双缓冲方式。

15.在串行异步通信时,发送端和接收端的波特率设置应()。

二、单选题(每题1分,共15分)1.计算机中数据总线驱动电路使用的基本逻辑单元是()。

A:非门B:三态门C:触发器D:译码器2.MIPS用来描述计算机的运算速度,含义是()。

A:每秒处理百万个字符B:每分钟处理百万个字符C:每秒执行百万条指令D:每分钟执行百万条指令3.执行指令IRET后弹出堆栈的寄存器先后顺序为()。

A:CS、IP、F B:IP、CS、F C:F、CS、IP D:F、IP、CS4.微机系统中,主机与硬盘的数据交换用()方式。

A:中断控制B:DMA控制C:查询控制D:无条件程序控制5.CPU对存储器访问时,地址线和数据线的有效时间关系为()。

电子科技大学微机原理与接口技术试题库一、问答题1、下列字符表示成相应的ASCII码是多少?(1)换行0AH (2)字母“Q”51H(3)空格20H2、下列各机器数所表示数的范围是多少?(1)8位二进制无符号定点整数;0~255(2)8位二进制无符号定点小数;0.996094(3)16位二进制无符号定点整数;0~65535(4)用补码表示的16位二进制有符号整数;-32768~327673、(111)X=273,基数X=?164、有一个二进制小数X=0.X1X2X3X4X5X6(1)若使X≥1/2,则X1……X6应满足什么条件? X1=1若使X>1/8,则X1……X6应满足什么条件?X1∨X2 ∨X3=1(2)5、有两个二进制数X=01101010,Y=10001100,试比较它们的大小。

(1)X和Y两个数均为无符号数;X>Y(2)X和Y两个数均为有符号的补码数。

X<Y二、填空题1、对于R进制数来说,其基数(能使用的数字符号个数)是R个,能使用的最小数字符号是0 。

1、2、十进制数72转换成八进制数是110Q。

3、与十进制数67等值的十六进制数是43H 。

1、4、二进制数101.011转换成十进制数是 5.375。

2、5、十六进制数0E12转换成二进制数是110000010010B。

三、选择题1、在计算机内部,一切信息的存取、处理和传送都是以 D 形式进行的。

A)EBCDIC码B)ASCII码C)十六进制编码D)二进制编码2、与十进制数56等值的二进制数是 A 。

A)111000 B)111001 C)101111 D)1101103、十进制数59转换成八进制数是 A 。

A)73Q B)37Q C)59Q D)112Q4、与十进制数58.75等值的十六进制数是 B 。

A)A3.CH B)3A.CH C)3A.23H D)C.3AH5、二进制数1101.01转换成十进制数是 C 。

A)17.256 B)13.5 C)13.25 D)17.56、二进制数111010.11转换成十六进制数是 B 。

姓名学号总分任课老师

一.填空题(每空1分,共30分)

1)15的8位二进制补码为,-15的8位二进制补码为。

2)某8位二进制补码为80H,其十进制表示为。

3)字符B的ASCII码为,字符0的ASCII码为。

4)8086CPU总线按功能可分为数据总线,总线和总线。

5)8086CPU数据总线包含条数据线,最多可寻址的存储器容量为。

6)CPU内部用于计算的部分为,用于保存下一条要执行的指令地址的为。

A) 程序状态字B) 程序计数器C) ALU D) 工作寄存器

7)经常用作循环次数的寄存器是,用于I/O端口寻址的寄存器是。

A) AX B) BX C) CX D) DX

8)指令MOV CX, 1000的结果是CH= 。

9)将0D787H和4321H相加后,标志位CF= ,SF= ,ZF= ,

OF= ,AF= ,PF= 。

10)寄存器SI中能够表示的最大有符号数为,最小有符号数为。

11)设(DS)=4000H,(BX)=0100H,(DI)=0002H,(4002)=0A0AH,(40100)=1234H,(40102)

=5678H,求以下指令分别执行后AX寄存器的值。

MOV AX , [2] (AX)= 。

MOV AX , [BX] (AX)= 。

MOV AX , [BX][DI] (AX)= 。

MOV AX , 1[BX] (AX)= 。

12)用一条指令将AX寄存器低四位清零,其余位不变:。

13)用一条指令将AX寄存器高四位取反,其余位不变:。

14)用一条指令将AL中的大写字母变成相应的小写:。

15)用一条指令将AX高8位与低8位交换:。

二.判断题(每题1分,共10分)

对以下语句语法正确的打√,语法错误打×,其中TABLE和TAB为两个字节类型的变量。

1)MOV DS , 1000H

2)MOV DS , TABLE

3)MOV [1200H] , [1300H]

4)ADD AX , BX , CX

5)XCHG AL , CL

6)CALL AL

7)MUL AX , BX

8)JU L1

9)SHR CL , CL

10)CMP AX , CL

三.简答题(共5分)

有以下伪指令,画出存储器分配图(设V AR1的段内偏移地址为0000H)。

V AR1 DB 12 , -12 , 0 , 34H

V AR2 DB ‘A’ , ‘B’

V AR3 DW ‘CD’ , ‘E’

V AR4 DB 3 , 3 DUP ( 1 )

V AR5 DW V AR2, LENGTH V AR4

四.程序分析(每空3分,共21分)

1)下面程序段执行完毕时CX= 。

MOV AX , 100

MOV BX , 10

MOV CX , 5

L1 :

DEC CX

SUB AX , BX

JNC L1

2)下面程序段执行完毕时AX= 。

XOR AX , AX

MOV BX , 100

L1 :

ADD AX , BX

RCR BX,1

JNC L1

3)从键盘读入一个字符串到缓冲区BUF中,请将空缺的指令补上。

若输入12345↙,则指令MOV AL ,

BUF+2执行的结果是AL= 。

MOV BUF, 80

LEA, BUF

MOV AH ,

INT 21H

4)将无符号数字节变量V AR1,V AR2计算平均值,结果四舍五入存放在AL中,请补充完整。

MOV AL,V AR1

XOR AH,AH

ADD AL,V AR2

SHR AX,1

五.综合题(14分)

下面程序对8088最大方式系统中两片6264存储器进行检验,检验通过将DL清0,否则将DL 置0FFH。

1)将程序补充完整(每空3分)

MOV AX , 0000H

MOV DS , AX

MOV BX , 0FFFH

MOV AL , 55H

MOV CX , 16*1024

L1 :

MOV [BX] , AL

CMP AL , [BX]

JNE L2

INC BX

LOOP L1

MOV DL , 0

JMP L3

L2 :

MOV DL , 0FFH

L3 :

2)画出指令MOV [0100H], AL执行时系统总线时序图(5分)

T1

在8086最小方式系统下增加一个8253,I/O地址为100H~107H的偶地址,要求以1MHz信号为时钟,产生周期为1秒,低电平为1毫秒的周期方波。

1)画出电路(5分)

2)编写相应的程序(5分)

七段显示器常用来显示数字0~9,某七段显示器包含7个输入引脚a~g,当某个引脚为高电平时,对应LED为亮,否则为灭。

现要求在8088最大方式系统中设计一个输出接口控制七段显示器,I/O 地址为240H。

1)使用逻辑门电路补充剩余接口电路(4分)。

2)编写完整的程序轮流显示数字0~9(6分)。