移动电源LAYOUT注意事项

- 格式:doc

- 大小:97.00 KB

- 文档页数:1

Layout主要工作注意事项●画之前的准备工作●与电路设计者的沟通●Layout 的金属线尤其是电源线、地线●保护环●衬底噪声●管子的匹配精度一、l ayout 之前的准备工作1、先估算芯片面积先分别计算各个电路模块的面积,然后再加上模块之间走线以及端口引出等的面积,即得到芯片总的面积。

2、Top-Down 设计流程先根据电路规模对版图进行整体布局,整体布局包括:主要单元的大小形状以及位置安排;电源和地线的布局;输入输出引脚的放置等;统计整个芯片的引脚个数,包括测试点也要确定好,严格确定每个模块的引脚属性,位置。

3、模块的方向应该与信号的流向一致每个模块一定按照确定好的引脚位置引出之间的连线4、保证主信号通道简单流畅,连线尽量短,少拐弯等。

5、不同模块的电源,地线分开,以防干扰,电源线的寄生电阻尽可能较小,避免各模块的电源电压不一致。

6、尽可能把电容电阻和大管子放在侧旁,利于提高电路的抗干扰能力。

二、与电路设计者的沟通搞清楚电路的结构和工作原理明确电路设计中对版图有特殊要求的地方包含内容:(1)确保金属线的宽度和引线孔的数目能够满足要求(各通路在典型情况和最坏情况的大小)尤其是电源线盒地线。

(2)差分对管,有源负载,电流镜,电容阵列等要求匹配良好的子模块。

(3)电路中MOS管,电阻电容对精度的要求。

(4)易受干扰的电压传输线,高频信号传输线。

三、layout 的金属线尤其是电源线,地线1、根据电路在最坏情况下的电流值来确定金属线的宽度以及接触孔的排列方式和数目,以避免电迁移。

电迁移效应:是指当传输电流过大时,电子碰撞金属原子,导致原子移位而使金属断线。

在接触孔周围,电流比较集中,电迁移更容易产生。

2、避免天线效应长金属(面积较大的金属)在刻蚀的时候,会吸引大量的电荷,这时如果该金属与管子栅相连,可能会在栅极形成高压,影响栅养化层质量,降低电路的可靠性和寿命。

解决方案:(1)插一个金属跳线来消除(在低层金属上的天线效应可以通过在顶层金属层插入短的跳线来消除)。

移动电源布线注意事项:

1.在SW 和VIN 之间连接电感。

在PCB 布线时尽可能短和粗,以减小EMI 和电路板上的功率损耗。

2.低ESR 输入电容能减小开关噪音和电池流出的峰值电流。

陶瓷电容也是一个好选择,作为输入退耦电容,此电容尽量放置在靠近IC处。

10uF 输入电容已足够所以的应用。

3.选择低ESR (等效串联电阻) 的电容可以使输出电压纹波最小化。

多层陶瓷电容是一种极好的。

选择,因为他们有极低的ESR 和小的封装。

对于大部分应用,一个4.7uF 到20uF 的电容已足

够。

大于22uF 的电容将获得极好的输出电压波形和瞬态响应.输出纹波大时很多的产品将不能充电,如:IPHONE3等。

4.在PCB 布线时,VOUT 到输出滤波电容的PCB 走线应尽量短而粗。

5.电感的选择:有三个重要的电感规格,直流电阻,饱和电流和磁芯损耗。

低直流电阻,具有更好的电源效率。

采用大的电感值的电感可输出更大的电流并能减小输出纹波,电感电流一般设在电感标称的峰值电流(IP)的20%到 40%,电感应选择低内阻的,以减小内阻引起的功率损耗。

为最小化辐射噪音,请使用带屏蔽环的工形绕线电感。

6.电源线、地线及LX脚的走线须尽量短、直、粗,以减少电磁干扰。

7.电阻分压器R1和R2,必须尽可能直接地连接到FB引脚。

8.IC的地、Cin及Cout须在同一个层面紧密连接在一起。

LAYOUT應注意事項:1.如果兩個銲點之間,只走一條線,應儘量走在中間,以減少短路的機會。

2.繞線時,除非不得已的情況下,不要走90度角,容易造成斷裂。

3.繞完線後,儘可能使用淚滴,以增加線與銲點的接觸面,接觸面積愈大則線愈不容易斷裂。

4.繞線距離板邊,最少不要低於0.5MM,以免成型時將線截斷。

5.文字面避免放在銲點上面,將參考位置放在實體物面積之外。

6.注意FPC要折彎或擺動之處,必須儘量設計不要太硬,不要舖太多的銅,使其具有良好的耐折性。

7.導線的寬度:銅導線的寬度關係到耐電流和溫昇,所以盡量使用寬一點的導體較佳)。

通常信號用0.8mm寬,電源用1.5mm以上。

必要時可以加大或減小。

太細的線製作容易導致失敗。

8.焊點不要太小以免脫落,孔徑可以設成0.5mm以利鑽孔時的定位。

如果你技術好,可以直接設成要鑽孔的孔徑,這樣子銅箔比較不容易突起,但是相對鑽孔定位會差一點,要是鑽歪了,焊點內會有留白。

9:零件排列时各部份电路盡可能排列在一起,走线盡可能短。

10:IC地去耦电容应尽可能的靠近IC脚以增加效果。

11:如果两条线路之间的电压差较大时需注意安全间距。

12:要考量每条回路的电流大小,即发热状况来决定铜箔粗细。

13:线路拐角时尽量部要有锐角,直角最好用钝角和圆弧。

14:对高频电路而言,两条线路最好不要平行走太长,以减少分布电容的影响,一般采取顶层底层众项的方式。

15:高频电路须考量地线的高频阻抗,一般采用大面積接地的方式,各点就近接地,减小地线的电感份量,讓各接地点的电位相近。

16:高频电路的走线要粗而短,减小因走线太长而产生的电感及高频阻抗对电路的影响。

17:零件排列时,一般要把同类零件排在一起,盡量整齐,对有极性的元件盡可能的方向一致,降低淺在的生产成本。

18:对RF机种而言,电源部份的零件盡量遠离接收板,以减少干擾。

19:对TF机种而言,发射器应盡可能离PIR远一些,以减少发射时对PIR造成的干扰。

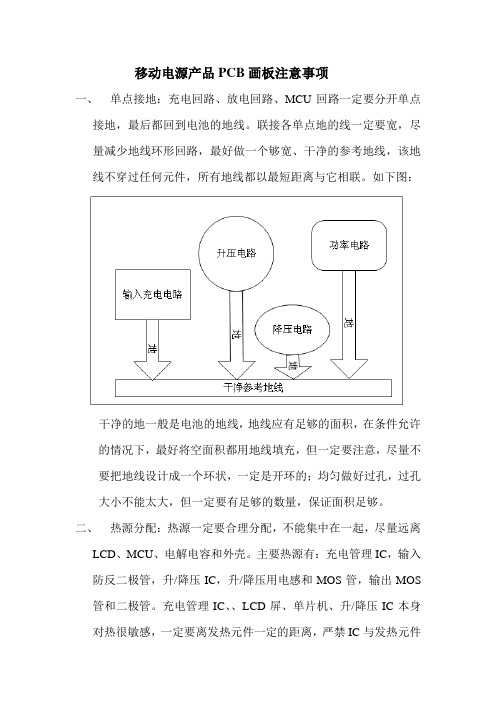

移动电源产品PCB画板注意事项一、单点接地:充电回路、放电回路、MCU回路一定要分开单点接地,最后都回到电池的地线。

联接各单点地的线一定要宽,尽量减少地线环形回路,最好做一个够宽、干净的参考地线,该地线不穿过任何元件,所有地线都以最短距离与它相联。

如下图:干净的地一般是电池的地线,地线应有足够的面积,在条件允许的情况下,最好将空面积都用地线填充,但一定要注意,尽量不要把地线设计成一个环状,一定是开环的;均匀做好过孔,过孔大小不能太大,但一定要有足够的数量,保证面积足够。

二、热源分配:热源一定要合理分配,不能集中在一起,尽量远离LCD、MCU、电解电容和外壳。

主要热源有:充电管理IC,输入防反二极管,升/降压IC,升/降压用电感和MOS管,输出MOS 管和二极管。

充电管理IC、、LCD屏、单片机、升/降压IC本身对热很敏感,一定要离发热元件一定的距离,严禁IC与发热元件背靠背。

贴片发热元件一定要足够的散热面积,最好采用大面积地线作为散热面,否则就选用带散热的插件元件。

三、MCU外围元件:MCU的OSC和REST引脚所接元件尽量紧靠相应引脚,检测元件尽量靠近MCU,走线尽可能短,无法靠近MCU的检测元件,其走线可考虑采用跳线直接与MCU引脚相联,在单片机VCC引脚,一定要接滤波电容(104到105),一定要紧靠在VCC引脚边。

四、升/降压电路布线要求:升/降压用MOS管、二极管、电感三个元件一定紧靠近升/降压IC,MOS管的驱动一定要短,不能转弯;MOS管的驱动信号线尽量短,禁走干扰区。

升/降压反馈电阻也要紧靠近升/降压IC,但不能放在IC、电感和升压MOS管下,走线尽量短、粗,输入、输出滤波电容尽量靠近升/降压IC,严禁通过过孔与IC相联,应直接铜泊相联。

输入、输出滤波电容最好采用多个小容值电容并联,容值采用分布式的,小、中、大都有,电容最好采用无极性电容,以保证良好的滤波效果。

有很多升压IC有上电瞬间会使输出升高现象,设计时一定要注意元件选择,尽量防止该现象。

1.每天须中午时分回传工作档, 如有SW AP DSN,当天须将DSN回传, 回传之档案需分开单个压缩,不能一起压缩.2.对线走线须尽可能保持美观,换层处VIA水平或者垂直方向须对齐,不可有反向的走线(见红圈).并须加一GND VIA.(如图:修改前/后)3.4.5.接口部分USB信号不可从LAN CONN中间穿越, LAN信号须直接拉出,顺序不对则直接拉出打VIA换层.(如图:修改前/后)6.7.8.BOT层SMD零件PIN 边缘与DIP 零件PIN 边缘尽量隔开,120MIL 以上较好,80 MIL以上次之, 而最少须60mil 以上.(如图)9.10.对于封装为SOT23_5的零件须留心,注意走线宽度. 当需要走粗线时,宽度尽量保持20mil 以上.11.12.电源转换处各层所铺铜箔尽可能做到大小一样,不要一层很大,一层很小.13.30mil 和30mil 以上的电源线贯孔要用PWRVIA30, 电源转换处贯孔用PWRVIA30,VCORE部分电源转换贯孔用PWRVIA. 并且须注意VIA的整齐度.14.晶震的GND不能与其它GND相连,包括Shape.(如图)15.16.CLK与USB间距须在50MIL以上.(如图:蓝色----CLK, 紫色----USB)17.18.工厂有规范:一般情况BGA实际大小往外扩大3MM 同层不能摆放贴片零件,(封装有多加一个外框,可见.) 除非有特殊规定,否则一律要避免.(如图)19.20.一些高频信号(USB , LAN , SATA , VGA 等)走线如有经过其他高频信号(如CLK , 晶震)的PIN或VIA(包括相互之间),间距也必须足够.(如图: 假设图中为一对LAN信号与两根CLK信号,则X mil 与Y mil 都须达到安全间距.)21.22.0402 的电阻电容等零件,两PIN连接的SHAPE尽量避免延伸至两PIN中间.(如图:黄色框ok; 蓝色框须避免)23.24.普通信号和电源转换处铜箔或电源PAD, space尽量25mil,最小要求20mil. 所有电源铜箔亦须注意此间距问题.(BGA内部电源铜箔space也要适当空大)25.26.R G B 三条的走线包GND,在走线当中不能有其它的电源或讯号的via打在其中,GNDvia允许例外,并且须尽可能从起点包到终点. 所包之GND 每1000mil的距离内一定要有VIA下内层.27.28.MOS 所在位置的所有层,都尽量避免走线.(如图:黄线区域内其他层都要尽量避免走线)29.30.凡BGA内部的VIA一律要打在四个PIN的正中心位置, (如图) 经确认,确实有难度无法做到时才可例外.31.32.需要等长的每一对线, 尽可能将误差缩小不超过1 MIL.33.切割线维持20MIL的宽度,如有困难可适当缩小宽度,最小宽度不低于10MIL, 过了该处即须将线宽恢复到20MIL.34.+3.3VSB (3V_DUAL)进南桥须50MIL, 其他地方须40MIL. 接PCI的PIN A14须35MIL.35.处理过的地方,VCC & GND PIN的下内层要及时处理好.如果有处理则一定要用适当粗的线处理,不可只用5MIL 先稍作处理.36.绕线不可在BOARD GEOMETRY/ CONSTRAINT_AREA 中处理,不可在CONN中处理.37.DDR和CPU的搭界处需要留20~30MIL的距离38.VCORE部分的MOS铺铜打VIA的时候须注意VIA与PIN之间不要太近.39.同一个SATA插针的两对信号须走同一层进行处理.40.RGB一起的还有两条线*HSYNC*,*VSYNC*需要和RGB走同一层而且间距不能太小41.+12V须整条net保持30MIL以上的宽度,含任何一个分岔的末端也必须在30MIL以上.42.晶震的PIN脚离其他层的走线尽可能空开.43.大面积空旷铺铜箔时,铜箔不能将零散走线和零散零件包裹进来,一定要手工修正或者挖空铜箔.44.改板绕线方式须按修改之前的方式处理.45.LX GX系列,IDE部分,IOW IOR要比DATA短1000MIL. (LX GX 一般为档案名.)46.所有背板的统一要求:四角所有层离半边120MIL,螺絲孔在電源層的隔離以40mil為準,但是不能隔离太大(即超过40MIL),大的贴片电容电源及GND都最少四个PWRVIA30,PCIe Slot 不能在Top層Pin角與GND連接SHAPE。

太有用了,8个开关电源layout经验!其实对于一个开关电源工程师而言PCB的绘制其实是对一款产品的影响至关重要的部分,如果你不能很好的Layout的话,整个电源很有可能不能正常工作,最小问题也是稳波或者EMC过不去这是别人家的成品开关电源,模组,我会以这个电源模组的设计重点给大家讲一些点的。

经验一,安规走线间距这个是写在协议里面的,如果你不按照这个做,耐压测试一定是过不了的,因为高电压,会直接空气击穿。

注意保险丝之前的距离是比较远的,要求3mm以上,这就是为啥保险丝都会放在电路最前端的原因。

第二个要注意的是就算安规没有写,如果两根走线太近,正常工作也依然会击穿的,两根1mm间距的PCB外层耐压是200V 所以一般220v交流或者310V直流的走线距离至少2mm以上,我一般都是在2.5mm以上的。

这些器件都是有安规要求的,说白了,就是两个器件有最小尺寸需求的,太小的器件其实是不可能过安规的,能明白吗?这就是所谓的开关电源PCB工程师实质上是带着镣铐在跳舞的原因。

开关电源变压器的骨架,同样是为了符合安规所以要有严格的把关。

尤其是初级,到次级的距离,小功率变压器是必须飞线的。

飞线的长度也要被管控,如果飞线太短,耐压可能会受到影响,而如果飞线太长,会有可能对外辐射电磁信号,EMC过不了,所以需要在规格书里面详细写清楚,PCB绘制的时候,飞线的焊盘一定要注意,不能太妖孽。

经验二,电流走向这个其实很少有真的被提及,其实原因也很简单。

很多人不注意啊。

看着两个设计,这部分RV1压敏电阻到后面x2电容之间,为啥走线为啥故意这样走,而不是直接覆铜全部短接?注意这里保险丝之后,接压敏电阻VR1再接x2电容的走线,完全是绕了一个弯这是为什么?理由很简单,不让电流在PCB上面有回头路可以走。

电流只走阻抗最小的部分,如果直接覆铜,必经的元器件就有可能会被跳过,所以这样做不可以。

同样的,这里的电解电容,一样是为了避免电流绕过必经的电容,直接流到负载上。

layout 注意事項以減少EMC問題元件的放置PCB 佈局之前應先注意將元件放置(placement)在適當的位置,一方面需考慮電路板外部接線端子的位置,另一方面也需考慮不同性質的電路應予以適當的區隔。

低階類比、高速數位以及雜訊電路(繼電器、高電流開關等等) 應加以分隔以降低子系統間的耦合。

當放置元件時,應同時考慮子系統電路間的內部電路繞線,特別是時序及震盪電路。

為了去除EMI的潛在問題,應該系統化的檢查元件放置與線路佈局,返覆檢視及修正佈線一直到確定所有的EMI風險降低到最低為止,簡而言之,事先的防範是將低EMI干擾問題的首要原則。

下圖說明將不同性質電路的區隔概念。

將PCB上不同性質的電路予以隔離數位電路的雜訊與佈線類比電路的雜訊通常來自於電路板的外部,然而數位電路的雜訊則往往由內部產生,因此如何降低內部雜訊是數位電路板佈線的首要考量因素。

在MCU為主的系統中最敏感的信號是時序、重置和中斷線路,震盪器在開機時尤為敏感。

千萬不要將這些線路與高電流開關線路平行,如此易於被電磁交互耦合信號破壞。

此效應容易破壞MCU經由中斷碼的執行,引起非預期的重置或中斷。

時序信號受到干擾,將造成失相(lose phase)使整個系統失去同步,由於MCU的執行是依據適當的時鐘脈波,因此不要期望它們能在EMI 的干擾下恢復正常操作。

震盪器或陶瓷共振時鐘是一種RF電路,必須繞線以減少它的發射位準及敏感性。

圖15以一個震盪器或陶瓷共振器與DIP包裝的例子來說明,儘量將震盪電路的配置靠近MCU,若是震盪器或陶瓷共振器的本體很長,就放在PCB之下並將包裝接地。

如果震盪器在PCB之外,就將MCU 放在離PCB連接器的附近,不然,就將MCU儘量擺近震盪器以縮短繞線距離。

震盪線路的地線應該連接元件可能使用最短繞線的接地腳位,電源和接地腳應該直接繞線到PCB的電源部分。

圖16 說明PCB 挈b的?/FONT> I/O接地與I/O電纜線的解耦電容佈線方式。

LAYOUT注意事項1.拉線時千萬不能用自動避線的功能(除了BGA IC內),且要在GRID上.2.拉線時一定要預留測點VIA.3.走線時要注意跨切割的問題(切割線可以微調).4.一般在走線時, I/O Port, CLK區域(切割區)不可將不相關的信號線走入.5.CLK IC 要預留衛兵電容,在缺口處兩邊各一個.6.CLK 信號要從電容端拉出不可從電阻端,繞線也必頇過電容之後繞.B,LAN….等等,有+/-的信號必頇平行且儘量等長.8.POWER信號主幹線一定要保持MIN_LINE_WIDTH的寬度,支線頇問過才能變細.9.POWER PIN 打VIA的線要儘量短10.0603的零件中間不能走線..11.走線時不要打太多VIA,也不要有太多無用的轉角,儘量平整走線.12.D ifferential Pair 在走線時要推到最小的Spacing,轉角時也一樣.13.換角位一定要RUN 出BACKANNO.SWP傳回台北重新NETIN.14.微調零件時請用GRID 5.15.走線時為了讓走線順可以微調零件若移動大或頇移動CONNECTOR時一定要先問過.16.走線時若發現零件有重疊時請順便調整好.17.拉完線在做MISSING NET前請記得將NO_RAT的NET OFF掉,並且做VCC,GND PLANE的SHAPE處理(ROUTE/AUTO SPLIT PLANES),以免有POWER PIN沒拉.18.B RD完成的定義:NO DRC, NO MISSING NET.19.加測點時要注意有繞線的NET必頇保持原來的長度範圍(北橋到CPU, 北橋到DDR,IDE,AGP,HUB LINK,CLK)CLK的測點要加在尾端.,BGA內不可加測點20.排零件時要考慮整齊及美觀並注意限高區.21.D IP 電容只能上,下擇一或左,右擇一.22.處理文字面時要注意不能放在VIA及光學點上23.文字面字體一般用2號(密), 3號(疏),而JUMPER,CONN,IC 請用4號以上24.R OUTINR時要ON GRID, SILDE時不能用GRIDLESS(DIFFERENTIAL PAIR除外).。

移动电源LAYOUT注意事项:

1.电流采样电阻的地以及主电路的地尽量集中靠近为主地并且走线尽量加宽,然后MCU部分的地(回路不要与大电流地有叠加情况)单独连到主地;

2.有排针连接过大电流的情况,尽量用直通针连接上下板,不要用公母座接插(会增加接触阻抗);

3.MCU的AD口电容尽量靠近MCU的I/O口,尽量保证先过电容再到I/O的原则,滤波电容的地要与单片机的地共地且单独连接到主地;

4.采样电阻取样端尽量靠近电阻焊盘端取样;

5.电池正连接到电感,升压MOS等升压部分主电流回路走线尽量加宽以降低损耗,输入输出滤波电容尽量靠近升压部分电路。

以下是参与示意图:。