allegro 16.0的区域规则设置笔记

- 格式:doc

- 大小:134.50 KB

- 文档页数:4

1. Allegro中我设置了highlight的颜色为白色,但选中后颜色是白蓝相间的,很不方便查看。

是什么地方需要设置,哪位大虾告诉哈我?答:setup/user preferences/display/display_nohilitefont 这个选项打勾就行了。

2. 不小心按了Highlight Sov后部分线高亮成白色,怎样取消?答:这个是用来检查跨分割的,取消的办法是:如果是4层板的话,在电源层跟地层都铺上地网络,然后再按Highlight Sov刷新即可。

3. 如何更改Highlight高亮默认颜色?答:可以在Display->Color/Visibility->Display->Temporary Highlight里修改即可,临时修改颜色可以点Display->Assign Color来实现。

4. 如实现Highlight高亮部分网络,而背景变暗,就像Altium Designer那样?答:可以在Display->Color/Visibility->Display->Shadow Mode打开该模式,并且选中Dim active layer 即可。

5. 快速切换层快捷键答:可以按数字区里的“-”或“+”来换层。

6. OrCAD跟Allegro交互时,出现WARNING [CAP0072] Could not find component to highlight 错误等?答:OrCAD输出网表,Allegro导入网表,确保两者对的上号,然后在Orcad选中元件,再右键Editor Select,即可在Allegro中选中该元件;反过来,在Allegro中要先Highlight某元件,在Orcad中变会选中该元件。

1.ORcad :首先打开orcad和allegro分别占1/2的窗口界面。

然后orcad中Tools/creatnetlist/PCB Editor中Create PCB Editor Netlist下的Options中设置导出网表的路径。

Spacing规则(约束)Rexdlutarm@2009-07-02 Allegro 16.0以后版本的约束规则设置较之前有很大改变,对于用惯了15.x的人来说,很多不习惯新的约束管理器。

和在对待女人的态度上,恰相反。

80后说90后脑残,15.7说16.2脑残,Xp说Vista脑残。

Vista确实很脑残。

新事物取代旧事物是自然界发展的客观规律。

说明:1本文只介绍了Spacing约束的设置,因为Physical规则通常来说都设置的非常简单。

掌握了Spacing规则Physical规则对你来说一定是小Case。

另外,Physical 规则的设置也写的话,一定显得都是在重复Spacing的设置;2文中所有的规则(约束),如不特殊说明默认情况下均指Spacing规则(约束);3对于Electrical的约束,是另一种约束,本文不作讨论。

约束的设置方式:1直接的:Net中写数值,2 间接的:创建Constraint Set,然后Assign给Net;这两种都很常用,后者管理方便。

在Physical和Spacing设置中用后者比较好,但是在Electrical中,我看到很多很多的人会混合使用。

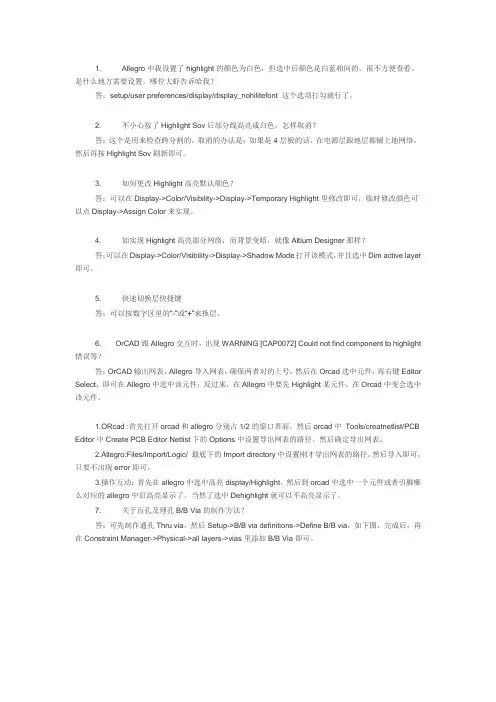

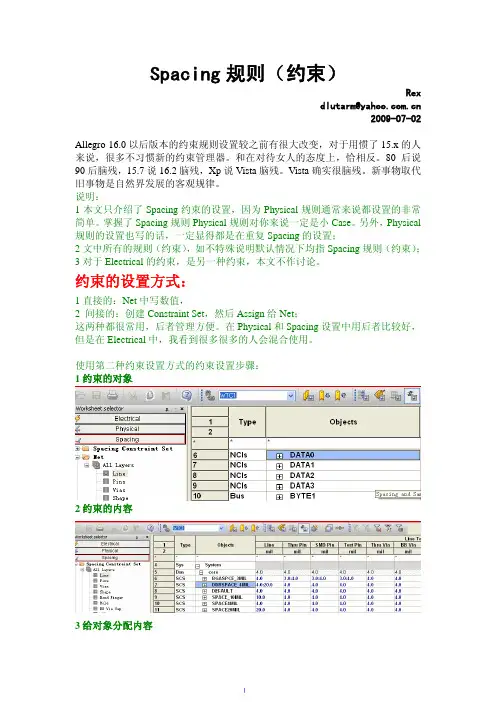

使用第二种约束设置方式的约束设置步骤:1约束的对象2约束的内容3给对象分配内容1这3个步骤默默的引导着所有间接约束的设置。

基本约束预备先理解:Net class2Net class-classRegionRegion-classRegion-class-classBus……现在不理解,想跳过去。

没关系,你早晚都要理解的。

最简单和稍微复杂一点的约束:最简单的就是default的约束,稍微复杂一点的就是修改了一点默认的约束。

再复杂一些的约束:你可能会想让不断变化的CLK(我们不考虑是不是差分)和其他的线离的远一些。

在Constraint Set中Create规则并设置规则的内容:Creat & Set之后3给Net分配规则:更高级的约束:What Can U Think?有了一根线的约束,贪婪的本性会使你你很快上升到两根线(通常是Diff)和更多线的约束。

allegro 遇到的问题汇总避免忘记1、更新封装封装修改后,在allegro下palce--update symbols。

在package symbol下选择要更新的封装。

注意勾选update symbol padstacksIgnore FIXED property。

2、如何批量放置VIA?比方在TOP层铺了一片铜到地,然后想规则的放置一批VIA将表面铺铜区连接到地层,能不能自动完成啊?手动放很麻烦也不均与,影响美观CopyFind勾選ViaOption填寫數量,間距。

别人整理的还不错原文地址/BLOG_ARTICLE_3006536.HTM1. Allegro中我设置了highlight的颜色为白色,但选中后颜色是白蓝相间的,很不方便查看。

是什么地方需要设置,哪位大虾告诉哈我?答:setup/user preferences/display/display_nohilitefont 这个选项打勾就行了。

2. 不小心按了Highlight Sov后部分线高亮成白色,怎样取消?答:这个是用来检查跨分割的,取消的办法是:如果是4层板的话,在电源层跟地层都铺上地网络,然后再按Highlight Sov刷新即可。

3. 如何更改Highlight高亮默认颜色?答:可以在Display->Color/Visibility->Display->Temporary Highlight里修改即可,临时修改颜色可以点Display->Assign Color来实现。

4. 如实现Highlight高亮部分网络,而背景变暗,就像Altium Designer 那样?答:可以在Display->Color/Visibility->Display->Shadow Mode打开该模式,并且选中Dim active layer即可。

5. 快速切换层快捷键答:可以按数字区里的“-”或“+”来换层。

allegro 遇到的问题汇总避免忘记1、更新封装封装修改后,在allegro下palce--update symbols。

在package symbol下选择要更新的封装。

注意勾选update symbol padstacksIgnore FIXED property。

2、如何批量放置VIA?比方在TOP层铺了一片铜到地,然后想规则的放置一批VIA将表面铺铜区连接到地层,能不能自动完成啊?手动放很麻烦也不均与,影响美观CopyFind勾選ViaOption填寫數量,間距。

别人整理的还不错原文地址/BLOG_ARTICLE_3006536.HTM1. Allegro中我设置了highlight的颜色为白色,但选中后颜色是白蓝相间的,很不方便查看。

是什么地方需要设置,哪位大虾告诉哈我?答:setup/user preferences/display/display_nohilitefont 这个选项打勾就行了。

2. 不小心按了Highlight Sov后部分线高亮成白色,怎样取消?答:这个是用来检查跨分割的,取消的办法是:如果是4层板的话,在电源层跟地层都铺上地网络,然后再按Highlight Sov刷新即可。

3. 如何更改Highlight高亮默认颜色?答:可以在Display->Color/Visibility->Display->Temporary Highlight里修改即可,临时修改颜色可以点Display->Assign Color来实现。

4. 如实现Highlight高亮部分网络,而背景变暗,就像Altium Designer 那样?答:可以在Display->Color/Visibility->Display->Shadow Mode打开该模式,并且选中Dim active layer即可。

5. 快速切换层快捷键答:可以按数字区里的“-”或“+”来换层。

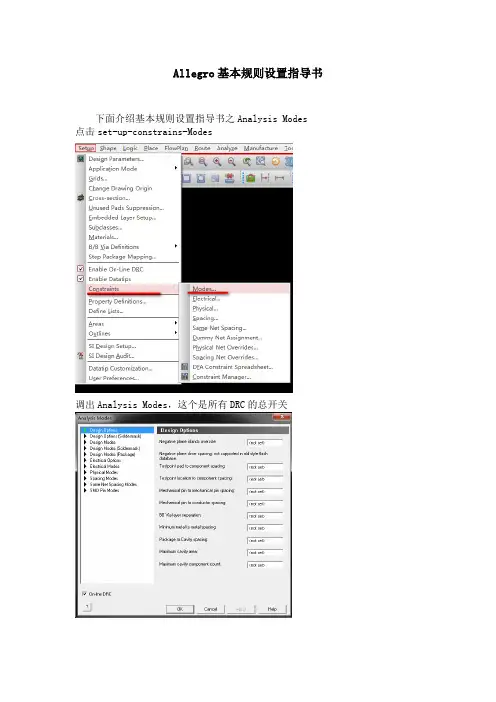

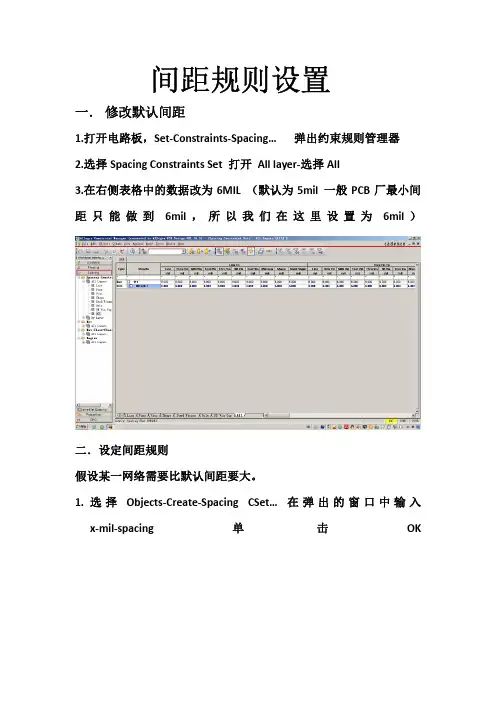

Allegro基本规则设置指导书下面介绍基本规则设置指导书之Analysis Modes 点击set-up-constrains-Modes调出Analysis Modes,这个是所有DRC的总开关下面介绍常用的一些开关设置1.Design Options (Soldermask)从上往下阻焊到阻焊的间距阻焊到pad和走线间距阻焊到shape1的间距钢网到钢网的间距2.Design Mode从上往下测试点Pad到器件DRC开关测试点到器件的DRC开关测试点在器件下方的DRC开关重孔开关3.Design Mode(soldermask)从上往下阻焊到阻焊的DRC开关阻焊到Pad和线的DRC开关阻焊到shape的DRC开关钢网到钢网的DRC开关4.Design Modes(Package)从上到下器件和器件的DRC开关器件超出package keepin的DRC开关器件在器件禁布的DRC开关5.Electric options从上往下开启最短长度延时开启相对长度延时开启pin delay开启Z轴延时6.Electric Modes从上往下绝对长度延时开关相对长度延时开关总长DRC开关差分检查DRC开关7.Physical Mode从上往下走线出现T分支DRC开关Pad和Pad连接的DRC开关过孔使用类型DRC开关8.Spacing Modes默认全部选择所有间距相关的DRC开关都要打开9.Same Net Spacing Modes同名网络DRC开关,默认全部打开10.SMD Pins Modes盘中孔DRC默认是关闭的,可以用来检查孔是否打在SMD的pin上的情况11.开启DRC总开关On-line DRC是需要开启的,否则所有DRC都不起作用Physical规则设置下面介绍规则设置指导书之Physical规则设置点击Set-up-constraints-Constraint Manager打开规则管理器1.设置Physical规则2.打开时默认有个Default规则从左往右Line Width最小线宽最大线宽Neck最小线宽Neck的走线长度3.如果是差分规则,需要额外设以下参数从左往右最小线间距差分对之间的间距Neck走线差分之间的间距正公差负公差4.Pad-Pad connect选择Not Allowed,不允许Pad和Pad直接连接简而言之,就是允许盘中孔Physical规则匹配下面介绍基本规则设置指导书之Physical规则匹配1.在这里给网络匹配上相应的规则2.可以给同一类型的网络建立一个Net Class,匹配规则更方便选中需要的net右击创建Class3.同时如果是差分对的话,需要创建差分对选择需要的两个net,Create Differential PairPhysical Region下面介绍基本规则设置指导书之Physical Region1.空白的地方创建一个Region2.给新建的Region匹配一个规则,所有区域里面的Physical相关的都按照Region的规则来3.当部分网络想按照本身的规则来匹配,可以创建region-Class4.然后匹配回它原来的规则5.后面这些规则一般按照Physical里面设置的规则不修改Spacing规则设置下面介绍基本规则设置指导书之Spacing规则设置1.设置Line到其它的间距规则从左往右线到线,通孔pin,表贴pin,测试pin,通孔Via,盲埋孔,测试孔,微孔,铜皮,Bond finger,hole之间的间距2.设置pin到其它的间距,通孔pin和表贴pin3.设置Via到其它的间距4.设置shape到其它的间距5.设置Bond Finger到其它的间距7.设置盲埋孔之间的间距Spacing规则匹配下面介绍基本规则设置指导书之Spacing规则匹配2.可以把同一类网络创建一个Net Class给Net Class匹配间距规则会更为方便Spacing规则Class to Class 下面介绍基本规则设置指导书之Spacing规则Class to Class1.当我们需要给组和组之间设置一个间距规则时候需要用到这个功能在需要的Net Class地方创建一个Class to Class2.Class to Class匹配一个规则Spacing Region 下面介绍基本规则设置指导书之Spacing Region1.空白的地方创建一个Region2.给创建好的Region 匹配一个规则3.当网络需要在Region中需要按照自身的规则匹配时,可以创建RegionClass来匹配4.Region也支持Class to Class规则,点击ok即可5.设置好的如下图Same Net Spacing规则设置下面介绍基本规则设置指导书之Same Net Spacing规则设置8.设置Line到其它的间距规则从左往右线到线,通孔pin,表贴pin,测试pin,通孔Via,盲埋孔,测试孔,微孔,铜皮,Bond finger,hole之间的间距9.设置pin到其它的间距,通孔pin和表贴pin10.设置Via到其它的间距11.设置shape到其它的间距12.设置Bond Finger到其它的间距13.设置Hole到其它的间距14.打开或者关闭同名网络开关Same Net Spacing规则匹配下面介绍基本规则设置指导书之Same Net Spacing规则匹配3.匹配设置好的Same Net间距规则Same Net Spacing Region下面介绍基本规则设置指导书之Same Net Spacing Region6.空白的地方创建一个Region7.给创建好的Region 匹配一个规则8.当网络需要在Region中需要按照自身的规则匹配时,可以创建RegionClass来匹配Electrical Min Max Propagation Delay下面介绍基本规则设置指导书之Electrical Min Max Propagation Delay在这里可以设置走线的最短和最长的长度,这个过孔和pin delay的长度也会计算进去Electrical Total Etch Length下面介绍Allegro基本规则设置指导书之Electrical Total Etch Length这里可以设置走线的最短和最长的值,这里的值只是走线长度,不包含过孔和pin delay的长度Electrical Differentail Pair下面介绍基本规则设置指导书之 Electrical Differentail Pair这里一般用来设置差分的对内等长,在tolerance这里设置Electrical Relative Propagation Delay下面介绍基本规则设置指导书之 Electrical Relative Propagation Delay1.这里用来设置等长规则2.在创建Match Group之前要创建pin pair3.创建好pin pair之后,选中需要做等长的网络,创建Match Group4.创建好Match Group之后,Scope选择Global, Tolerance 输入公差值5.选择一个网络作为基准。

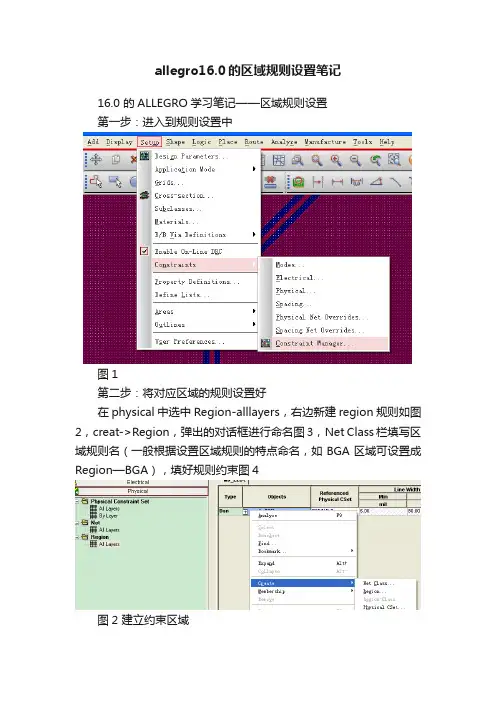

allegro16.0的区域规则设置笔记

16.0 的ALLEGRO学习笔记——区域规则设置

第一步:进入到规则设置中

图1

第二步:将对应区域的规则设置好

在physical中选中Region-alllayers,右边新建region规则如图2,creat->Region,弹出的对话框进行命名图3,Net Class栏填写区域规则名(一般根据设置区域规则的特点命名,如BGA区域可设置成Region—BGA),填好规则约束图4

图2 建立约束区域

图3 约束区域命名

图4 具体的约束数据,线宽,过孔等,也可以再spacing中进行约束

第三步:画出约束的区域

右边Option-下拉菜单到Constraint Region,选好区域规则层top/bottom

图5 选择Constraint Region层

Shape下前3个画区域,第二三个画矩形和圆形区域,第一个画不规则区域,画好一个区域

图5 根据区域的形状选择状态

右边会出现图6 所示信息,Assign to Region下的选择菜单,选择对应的区域规则

图6 区域规则选择

图7 画好要设置的区域

这样就做好了一个区域规则设置,继续努力!!。

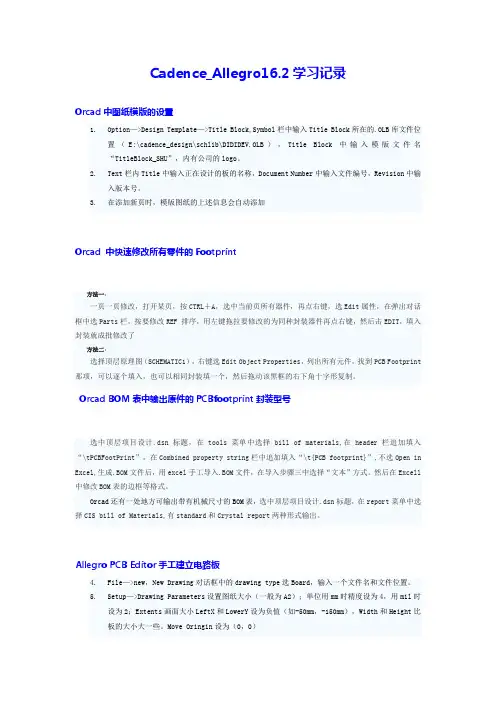

Cadence_Allegro16.2学习记录Orcad中图纸模版的设置1.Option—>Design Template—>Title Block,Symbol栏中输入Title Block所在的.OLB库文件位置(E:\cadence_design\schlib\DIDIDEV.OLB),Title Block中输入模版文件名“TitleBlock_SHU”,内有公司的logo。

2.Text栏内Title中输入正在设计的板的名称,Document Number中输入文件编号,Revision中输入版本号。

3.在添加新页时,模版图纸的上述信息会自动添加Orcad 中快速修改所有零件的Footprint方法一:一页一页修改,打开某页,按CTRL+A,选中当前页所有器件,再点右键,选Edit属性,在弹出对话框中选Parts栏,按要修改REF 排序,用左键拖拉要修改的为同种封装器件再点右键,然后击EDIT,填入封装就成批修改了方法二:选择顶层原理图(SCHEMATIC1),右键选Edit Object Properties,列出所有元件,找到PCB Footprint 那项,可以逐个填入,也可以相同封装填一个,然后拖动该黑框的右下角十字形复制。

Orcad BOM表中输出原件的PCBfootprint封装型号选中顶层项目设计.dsn标题,在tools菜单中选择bill of materials,在header栏追加填入“\tPCBFootPrint”,在Combined property string栏中追加填入“\t{PCB footprint}”,不选Open in Excel,生成.BOM文件后,用excel手工导入.BOM文件,在导入步骤三中选择“文本”方式。

然后在Excell 中修改BOM表的边框等格式。

Orcad还有一处地方可输出带有机械尺寸的BOM表,选中顶层项目设计.dsn标题,在report菜单中选择CIS bill of Materials,有standard和Crystal report两种形式输出。

Allegro约束规则设置随着电子商务的不断发展,大量的交易评台涌现出来。

其中,Allegro 作为东欧最大的电商评台,拥有数百万的用户和商家。

为了保证评台的可持续发展和用户的利益,Allegro评台制定了一系列的约束规则,以规范和管理用户的行为。

本文将详细介绍Allegro评台的约束规则设置。

一、账户注册与使用规定1.1 注册要求在注册Allegro评台账户时,用户需要提供真实尊称、唯一识别信息号码等个人信息,以确保账户的真实性和有效性。

1.2 账户使用规定用户在使用账户进行交易时,需要遵守评台规定的交易流程和规则,不得有任何违反法律法规和评台规定的行为,如欺诈、虚假宣传、侵权等。

二、商品交易规定2.1 商品发布规定商家在发布商品时,需提供详细、真实的商品信息,不得发布违禁品或虚假商品,如有违反将面临相应的处罚。

2.2 交易行为规范买家和卖家在交易过程中应遵守规定的交易流程,如按时付款、按时发货,不得擅自修改订单或逾期交易。

三、评价与投诉规定3.1 评价规定买家在收到商品后,可对交易进行评价,评价内容需客观、真实,不得进行恶意、虚假的评价。

3.2 投诉处理规定对于买家或卖家的投诉,评台将进行核实和处理,如发现违规行为,将给予相应的处罚,并保障投诉方的权益。

四、违规处理规定4.1 违规行为处罚对于违反评台规定的行为,评台将根据情节严重程度给予相应的处罚,如下架商品、冻结账户等。

4.2 申诉机制对于被处罚的用户,可通过评台设立的申诉机制进行申诉,评台将重新审核相关情况,并依据申诉结果做出处理。

五、合作商家规定5.1 合作资格要求Allegro评台对合作商家有一定的资质和经营要求,包括经营年限、信誉度等。

5.2 合作权益合作商家可享受评台提供的一系列增值服务和营销支持,提升业务竞争力。

Allegro评台的约束规则设置是为了维护评台的正常运营秩序,保障用户和商家的合法权益,促进良好的交易环境。

用户在使用评台时,需严格遵守相关规定,如有违规行为,将面临相应的处罚。

allegro设置区域规则以Allegro 设置区域规则为标题,本文将探讨Allegro 平台中设置区域规则的方法和重要性。

区域规则是Allegro 平台中的一项重要功能,它可以帮助卖家更好地管理和展示商品,提供更好的购物体验。

区域规则主要用于控制商品的展示范围和销售限制,使卖家能够根据不同地区的需求和法律法规进行灵活的调整。

设置区域规则可以帮助卖家更好地针对不同地区的需求进行定制化展示。

不同地区的消费者对商品的需求和偏好有所不同,通过设置区域规则,卖家可以根据地区特点进行展示策略的调整。

比如,某些地区对某种商品的需求量较大,卖家可以通过设置区域规则将该商品在该地区的展示位置提前,以便更好地满足消费者需求,提高销售量。

设置区域规则还可以帮助卖家合理控制商品的销售范围和限制。

有些商品可能受到地区法律法规的限制,或者卖家只希望在特定地区销售某些商品。

通过设置区域规则,卖家可以将商品的销售范围限制在特定地区,避免违反法律法规或者销售策略。

同时,卖家也可以根据销售情况进行调整,及时调整销售范围,以便更好地控制库存和销售效果。

设置区域规则还可以帮助卖家更好地管理价格和促销活动。

不同地区的消费能力和购买习惯不同,通过设置区域规则,卖家可以根据地区特点进行灵活的定价和促销策略。

比如,在某些地区消费者对价格敏感,卖家可以通过设置区域规则在该地区进行价格调整或者促销活动,以吸引更多消费者,提高销售额。

设置区域规则还可以帮助卖家更好地管理物流和售后服务。

不同地区的物流能力和售后服务水平有所差异,通过设置区域规则,卖家可以根据地区特点进行灵活的物流和售后服务策略。

比如,在物流能力较强的地区,卖家可以提供更快速的物流服务,提高消费者的满意度和购买意愿。

Allegro 平台中设置区域规则对卖家来说具有重要的意义。

通过合理设置区域规则,卖家可以更好地管理和展示商品,提高销售效果,满足消费者的需求,增强竞争力。

因此,卖家应该充分利用Allegro 平台提供的区域规则功能,根据地区特点进行灵活调整,以获得更大的商机和利润。

allegro精简笔记// 本cadence笔记分为三篇:笔记零,笔记1,笔记2,精简凝练,很好!【笔记零】§1、安装:SPB15.2 CD1~3,安装1、2,第3为库,不安装License安装:设置环境变量lm_license_file D:\Cadence\license.dat修改license中SERVER yyh ANY 5280为SERVER zeng ANY 5280§2、用Design Entry CIS(Capture)设计原理图进入Design Entry CIS Studio设置操作环境\Options\Preferencses:颜色:colors/Print格子:Grid Display杂项:Miscellaneous.........常取默认值配置设计图纸:设定模板:\Options\Design Template:(应用于新图)设定当前图纸\Options\Schematic Page Properities创建新设计创建元件及元件库File\New\Library(...\Labrary1.OLB)Design\New Part...(New Part Properties)Parts per 1/2/..(封装下元件的个数)Pakage Type:(只有一个元件时,不起作用)Homogeneous:复合封装元件中(多个元件图组成时)每个元件图都一样(default适用于标准逻辑)Heterogeneous:复合封装元件(多个元件图组成时)中使用不一样的元件图(较适用于大元件)一个封装下多个元件图,以View\next part(previous part)切换视图Part Numbering:Alphabetic/numericPlace(PIN...Rectangle)建立项目File\New\ProjectSchematic\new page (可以多张图:单层次电路图间,以相同名称的“电路端口连接器”off-page connector连接层次式电路图:以方块图(层次块Hierarchical Block...)来代替实际电路的电路图,以相同名称Port的配对内层电路,内层电路之间可以多张,同单层连接绘制原理图放置元器件:Place元件:Part(来自Libraries,先要添加库)电源和地(power gnd)连接线路wirebus:与wire之间必须以支线连接,并以网标(net alias)对应(wire:D0,D1....D7;bus:D[0..7])数据总线和数据总线的引出线必须定义net alias修改元件序号和元件值创建分级模块(多张电路图)平坦式(单层次)电路:各电路之间信号连接,以相同名称的off-page connector连接层次式电路图:以方块图(层次块Hierarchical Block...)来代替实际电路的电路图,以相同名称Port的配对内层电路,内层电路之间可以多张,同单层连接标题栏处理:一般已有标题栏,添加:Place\Title Block()PCB层预处理元件的属性编辑元件属性在导入PCB之前,必须正确填写元件的封装(PCB Footprint)参数整体赋值(框住多个元件,然后Edit Properties)分类属性编辑Edit Properties\New Column\Class:IC(IC,IO,Discrete三类,在PCB中分类放置)放置定义房间(Room)Edit Properties\New Column\Room添加文本和图像添加文本、位图(Place\...)原理图绘制的后续处理(切换到项目管理器窗口,选中*.DSN文件,然后进行后处理————DRC检查、生成网表及元器件清单)设计规则检查(T ools\Design Rules Check...)Design Rules Checkscope(范围):entire(全部)/selection(所选)Mode(模式):occurences(事件:在同一绘图页内同一实体出现多次的实体电路)instance(实体:绘图页内的元件符号)如一复杂层次电路,某子方块电路重复使用3次,就形成3次事件;子方块电路内本身的元件则是实体。

ALLEGRO约束规则设置步骤[图解]ALLEGRO 约束规则设置步骤[图解]本文是我对约束规则设置方面的一些理解,希望对新手能有所帮助。

由于本人水平有限,错误之处难免,希望大家不吝赐教!在进行高速布线时,一般都需要进行线长匹配,这时我们就需要设置好constraint 规则,并将这些规则分配到各类 net group 上。

下面以 ddr为例,具体说明这些约束设置的具体步骤。

1.布线要求DDR 时钟:线宽 10mil,内部间距 5mil,外部间距30mil,要求差分布线,必需精确匹配差分对走线误差,允许在+20mil 以内DDR 地址、片选及其他控制线:线宽 5mil,内部间距 15mil,外部间距20mil,应走成菊花链状拓扑,可比ddrclk 线长1000-2500mil,绝对不能短DDR 数据线,ddrdqs,ddrdm线:线宽 5mil,内部间距 15mil,外部间距20mil,最好在同一层布线。

数据线与时钟线的线长差控制在 50mil 内。

2.根据上述要求,我们在 allegro 中设置不同的约束针对线宽(physical),我们只需要设置3 个约束:DDR_CLK, DDR_ADDR, DDR_DATA设置好了上述约束之后,我们就可以将这些约束添加到net上了。

点击 physical rule set 中的attac h……,再点击右边控制面板中的more,弹出对话框如上图所示,找到 ckn0和 ckp0,点击 apply,则弹出选中左边列表中的NET_PHYSICAL_TYPE, 在右边空格内输入DDR_CLK, 点击apply,弹出即这两个 net已经添加上了 NET_PHYSICAL_TYPE 属性,且值为DDR_CLK.类似的,可以将DDR 数据线,数据选通线和数据屏蔽线的NET_PHYSICAL_TYPE 设为DDR_DATA, DDR 地址线,片选线,和其他控制线的 NET_PHYSICAL_TYPE 设为DDR_ADDR. 上述步骤完成后,我们就要将已经设好的约束分配到这些 net group 上。

allegro区域规则设置Allegro区域规则设置随着电子商务的快速发展,越来越多的人开始选择在网上购物。

作为波兰最大的在线市场,Allegro平台在该国享有极高的声誉和知名度。

为了确保交易的安全和公平,Allegro平台制定了一系列区域规则,以保护卖家和买家的权益。

本文将介绍Allegro区域规则的设置和相关内容。

Allegro平台根据不同的地理区域和市场需求,制定了不同的区域规则。

这些规则包括但不限于商品发布、交易方式、退款和售后服务等方面。

例如,在某些地区,卖家需要提供更详细的商品信息,包括商品的产地、包装规格等。

这样可以帮助买家更好地了解商品的特性和质量,从而做出更明智的购买决策。

Allegro平台要求卖家必须遵守公平竞争的原则。

卖家不能通过不正当的手段提高自己的商品排名,或者恶意诋毁竞争对手。

平台会定期对卖家的行为进行审核和监督,一旦发现违规行为,将会采取相应的惩罚措施,包括限制商品的展示、暂停账号等。

这样可以保证市场的公平竞争环境,为买家提供更好的购物体验。

Allegro平台还设置了严格的退款和售后服务规则。

卖家需要按照平台规定的退款政策进行操作,确保买家的利益得到保护。

在交易纠纷出现时,平台将会根据双方提供的证据进行仲裁,并给出公正的裁决结果。

这样既保障了买家的权益,也给卖家提供了一个公正公平的交易环境。

为了保证交易的安全,Allegro平台还设置了多种支付方式。

买家可以选择信用卡支付、支付宝、银行转账等多种支付方式,以满足不同用户的需求。

同时,平台也提供了安全的支付通道,保障用户的资金安全。

为了提高用户的购物体验,Allegro平台还设置了评价和评分系统。

买家可以根据购买的商品和卖家的服务进行评价,并给予相应的评分。

这不仅可以帮助其他买家做出更明智的购买决策,也可以激励卖家提供更好的服务,提高整体交易质量。

总结起来,Allegro区域规则的设置旨在保护卖家和买家的权益,维护市场的公平竞争环境,提高用户的购物体验。

Allegro布线规则的设置说明PCB布线经常会要求对重要的信号线进行规则的设置。

布线规则的设置通常包括线宽和线距两大部分。

下面就以一主板Layout guide为例部分说明之。

1. 首先是对整板未定义线规则的设置首先是对整板未定义线规则的设置,如下表所示:Net Name Width Spacing Net GroupNon-special Signal Inner layer:4Outer layer:5Inner layer:4Outer layer:5选择打开set standard values这里规定了Default line 在outer layer(TOP)和inner layer(INT1)中的line width 和pad to pad 的间距。

2. 接下来设置HOST 部分,部分,见下表要求:Net Name Width Spacing Space withothersignalNetGroupFSB Signals Inner layer:4Outer layer:58/1020HOST首先将属于此网络的所有net 定义为同一组,即BUS NAME=HOST选择Edit-Properties 并在右侧的当前命令栏中点击More 打开Find by name or property 窗口,ok这样就可以得到下面的窗口:至此一组HOST 线设置完毕,用同样的方法我们可以继续将DDR 等部分的线设置完3. 重新打开,选择spacing rule set-set value,点击ADD 添加HOST 8:10然后在Subclass 中,顶底层Line To Line 的间距为10,内层为8.4. 选择physical rule set-set value,点击ADD 添加HOST 4/5然后在Subclass 中,顶底层的线宽为5,内层为4.5. 无论是线宽还是线距都需要在assignment table 中进行和其他NET 的匹配。

Allegro163—PCB设计笔记打开PCBEditor。

一般选择第一项操作查看各种层Diplay——Color/Viibility封装的制作在PadDeigner中操作此项首先制作贴片式焊盘的做法Candence制作封装需要先制作焊盘打开制作焊盘的软件开始>程序>candence>releae16.3>PCBEditerUtilitie>PadDeigner 表贴焊盘就不用填写ThemalRelief(散热焊盘)和AntiPad(绝缘层焊盘)了这是建立好的焊盘文件然后打开PCBEditor——File——New——设置图纸大小Setup——DeignParameterEditor——DeignUerUnit (单位)选择E某tent项中Left某和LowerY为原点的坐标定义,Width 和Heigh为做封装时图纸的大小>Type项不变,仍为Package(封装)。

设置表格>Setup>Grid>将Non_Etch和AllEtch和TOP和BUTTOM中的Spacing的某和Y都改为0.0254(最小步进值)开始加入焊盘>Layout>Pin>>Option中如下设置创建一个零件库必须的几个条件:1至少一个引脚。

4要有Place_bound,即安装区,防止元器件之间的叠加。

做通孔类焊盘的时候要求焊盘过孔镀锡后要比元件引脚直径大0.2或0.3毫米最好。

这样有利于波峰焊是焊锡往上走。

同时也利于排气。

如果孔太小,气体跑不出来,会夹杂在焊锡里,孔太大,元件会发生偏斜。

元件孔包括镀层(铜色的约0.1毫米),镀锡1)首先添加Aembly_Top2)然后设置丝印层边框3)放置Add——Rectangle继续放置丝印层,并且放在第一个引脚的边上。

放置完以后保存就可以了这是做一个贴片式封装生成的文件这是生成的元件封装的数据文件元件的绘图文件,可以打开并编辑。

LeeAllegro PCB Editor What's New in Release 16.0Allegro V16.0 新版本拥有全新的操作接口,使用者在人性化的接口上更能有效率地工作,以下为V16.0新增功能及新接口的介绍。

.Date : 2007/07/16.Author : Jonathan .Revision : 1.0.Version : 16.0.备注:PCB Editor User Interface变更的部份为:.ToolbarIcon的更新、及工具群组的变更.Fold-Away Windows使工具窗口最大化,平时不使用时,Control Panel会自动收缩.Cadence Branding在SPB系列产品的左上角多了Cadence 商标Context-sensitive Editing参数设定或可执行之命令,可节省鼠标游标在工具列、control panel 和对象间移动的时间,换下列两种模式。

可执行的相关指令. Etch Edit Application Mode后,就会自动依对象执行如列表之相关指令.新的pre-selection 编辑模式可依被点选对象相关此模式可切A . General Edit Application Mode一般编辑模式,点选对象后会有该对象B Etch 相关应用编辑模式,点选对象entral Location for Design Parameters数设定界面包含 Display 、Design 、Text 、Etch Edit 、Shape and Manufacturing ..C 常用的设计参数集中在同一个控制界面,新的参olor and Visibility Enhancementsllegro Products Now Support OpenGL Standard卡128MB ,系统1GB 以上的RAMCA 支持Open GL 显示,若要最佳效能,基本配备为独立显示odernization of Color/Visibility User Interfaceolor Support Extended to 192二个调色盘,6x16的矩阵,一个调色盘共96色M 新的颜色层面显示界面C 颜色可支援192色,每个调色盘为Transparent Graphics Improve Visibility Through the PCB 可设定对象的透明度,使对象透明化,让重迭的对象更易显示uick Access to Commonly Used Subclasses在同一个画面作层面控制,而这个新的设定会在local Q 可以将常用的层面设定为我的最爱,自设常用的层面可pcbenv 内存一个 myfavorites.txt 储存相关的层面设定。

allegro区域规则Allegro区域规则作为一个拥有大量用户的在线交易平台,Allegro需要一系列规则来保证买家和卖家的权益以及整个平台的安全性。

以下是Allegro区域规则的详细说明。

一、账户管理规则1. 注册账户时需要提供真实姓名、地址和联系方式等信息,并保证信息的准确性和完整性。

2. 用户不得使用虚假身份注册账户或冒用他人身份注册账户。

3. 用户需妥善保管自己的账户密码,不得将其泄露给他人。

若发现账户被盗用,应立即联系客服处理。

4. 用户需遵守平台对于账户使用频率和操作次数等限制。

二、商品发布规则1. 发布商品时必须提供真实商品信息,包括商品名称、描述、价格等,并保证信息真实准确。

2. 禁止发布虚假或欺诈性商品信息,如虚假承诺或虚构优惠活动等。

3. 禁止发布违法或侵权商品信息,如盗版软件、仿冒品等。

4. 发布商品时需遵守平台对于图片大小、格式和水印等要求。

三、交易行为规则1. 交易双方应尽可能详细地了解商品信息和交易条件,如价格、数量、物流方式等。

2. 买家应在购买前仔细核对商品信息,并确认自己的收货地址和联系方式等信息的准确性。

3. 卖家应按照约定时间和方式发货,并提供有效的物流信息。

若出现物流问题需及时与买家沟通并解决。

4. 买卖双方应尽可能保持良好的沟通和合作关系,如有争议应及时联系客服处理。

四、违规处理规则1. 若用户违反上述规则,平台有权采取一定措施进行处理,包括但不限于下架商品、冻结账户、取消订单等。

2. 对于严重违规行为或多次违规行为,平台有权永久禁止用户使用该平台。

3. 若用户因违规行为造成平台或其他用户损失,平台将保留追究法律责任的权利。

五、其他注意事项1. 用户需遵守国家相关法律法规以及平台其他公告和规定。

2. 平台会不断完善和更新相关规则,请用户随时关注并遵守最新的规定。

以上为Allegro区域规则的详细说明。

我们希望所有用户能够遵守这些规则,共同维护一个安全、公正、透明的交易平台。

16.0 的ALLEGRO学习笔记——区域规则设置

第一步:进入到规则设置中

图1

第二步:将对应区域的规则设置好

在physical中选中Region-alllayers,右边新建region规则如图2,creat->Region,弹出的对话框进行命名图3,Net Class栏填写区域规则名(一般根据设置区域规则的特点命名,如BGA区域可设置成Region—BGA),填好规则约束图4

图2 建立约束区域

图3 约束区域命名

图4 具体的约束数据,线宽,过孔等,也可以再spacing中进行约束

第三步:画出约束的区域

右边Option-下拉菜单到Constraint Region,选好区域规则层top/bottom

图5 选择Constraint Region层

Shape下前3个画区域,第二三个画矩形和圆形区域,第一个画不规则区域,画好一个区域

图5 根据区域的形状选择状态

右边会出现图6 所示信息,Assign to Region下的选择菜单,选择对应的区域规则

图6 区域规则选择

图7 画好要设置的区域

这样就做好了一个区域规则设置,继续努力!!。