基于FPGA的实时视频处理平台方案讨论及设计

- 格式:pdf

- 大小:88.47 KB

- 文档页数:4

基于FPGA的视频监控跟踪系统的设计与实现的开题报告一、课题背景和研究意义视频监控技术在实际应用中具有重要意义,广泛用于各种领域,如安防监控、交通监控、环境监控等。

视频监控技术的高效性和实时性对算法和硬件设备的要求都很高,因此利用FPGA实现视频监控跟踪系统,不仅可以提高实时性能,还可以适应不同的监控场景,实现更精确的目标跟踪。

本课题的研究意义在于:1.提高视频监控技术的实时性能和准确性;2.利用FPGA实现视频处理硬件,提高处理效率;3.研究视频跟踪算法,实现目标实时定位和跟踪;4.探索适用于不同场景的监控跟踪方案,提高监控效果。

二、研究内容和研究方法1.研究基于FPGA的视频处理系统设计,包括视频采集、预处理、编码、解码等模块的设计与实现;2.研究基于深度学习的视频目标检测算法,在FPGA硬件平台上实现目标检测,并将结果传输至下一级处理模块;3.研究视频跟踪算法,实现目标的实时定位和跟踪;4.探索不同场景下的视频处理方案,提高监控效果和灵活性。

研究方法:1.对视频采集、处理、传输等模块进行需求分析,设计相应的视频处理系统;2.调查目标检测与跟踪算法,建立相应的模型;3.将开发好的算法和模型应用于FPGA平台上,并进行性能测试;4.根据实验结果和用户反馈,对系统进行优化和改进。

三、研究目标和预期成果1.完成基于FPGA的视频监控跟踪系统设计与实现;2.实现视频的实时采集、处理、传输和存储;3.实现目标检测和跟踪算法,提高监控效果和准确性;4.提高系统的可靠性、实时性和处理效率;5.验证系统在不同场景下的监控能力和应用性。

四、进度计划第一阶段:系统需求分析和设计(2个月)1.对视频监控需求进行分析,确定系统的功能和性能指标;2.设计视频采集、处理、传输和存储模块;3.研究并选择合适的目标检测和跟踪算法。

第二阶段:系统开发与实现(6个月)1.搭建完整的视频监控跟踪系统,实现视频的预处理、编码、解码等模块;2.学习深度学习等相关技术,实现目标检测和跟踪算法;3.进行系统测试和调试,优化系统性能。

基于FPGA的视频处理系统设计与实现随着数字化技术与高清视频的普及,基于FPGA的视频处理系统的应用也越来越广泛。

它们可以满足人们对于视频质量、速度和响应性能的要求。

FPGA作为一种高度可编程的器件,可根据应用需求任意重构电路结构,使得视频处理系统具有高度的扩展性、灵活性和定制性。

本文将从设计目标、系统结构、视频数据流传输、数字信号处理、硬件开发与软件开发等多个方面来介绍基于FPGA的视频处理系统的设计与实现。

一、设计目标在设计基于FPGA的视频处理系统时,我们需要考虑以下几个方面:1.视频质量:在视频的采集、传输和显示过程中需要确保视频的清晰、流畅和无噪音。

2.速度:视频处理系统需要具备高速的处理能力,可以迅速对视频进行处理,以达到实时性和响应性能。

3.低功耗:由于FPGA系统是基于硬件实现的,所以需要考虑低功耗来满足电源限制和延长电池寿命。

4.设计可重用:这就需要设计出可重用的平台,方便进行软件开发和硬件设计。

二、系统结构基于FPGA的视频处理系统的系统结构如图1所示。

它主要由三个部分组成:视频输入模块、视频处理模块和视频输出模块。

1.视频输入模块视频输入模块主要负责从相机或视频文件中采集视频数据,并将其转换成数字信号传输给FPGA。

该模块包括视频采集和视频解码两个部分。

2.视频处理模块视频处理模块主要是对采集到的视频数据进行处理,包括降噪、滤波、缩放、边缘检测、图像增强等操作。

它往往是FPGA设计的重点。

3.视频输出模块视频输出模块主要把处理好的视频数据输出到显示器、硬盘或网络等外设上,并在此过程中再次进行编码技术,使传输数据量减小,加快传输速度。

该模块还需要实现垂直同步、交错、逆交错等技术来保证视频输出的正确性和质量。

图1:基于FPGA的视频处理系统结构图三、视频数据流传输视频数据流传输是视频处理系统中非常重要的一环,它利用高带宽的总线来传输大量数据。

视频数据流传输主要有以下三种方式:1.像素传输像素传输是最常用的一种方式,它将每个像素的RGB值保存在一个字节中,并采用三根数据线分别传输每个像素的R、G、B值。

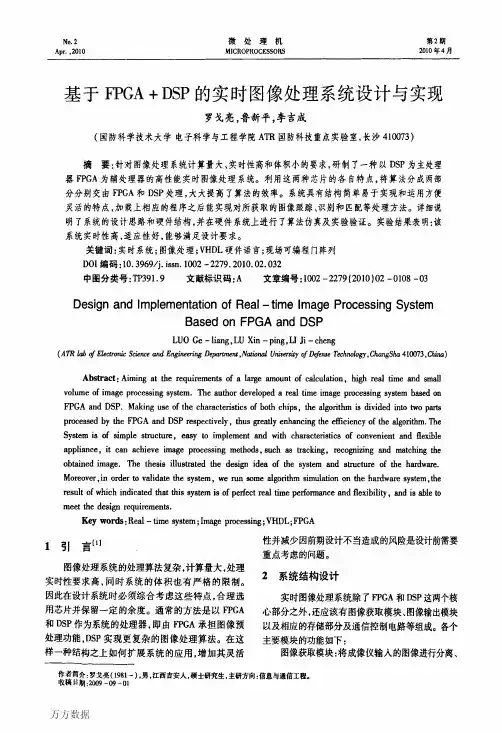

万方数据万方数据·110·微处理机2010年(DPRAM)。

虽然C6416片内集成了高达8M位的片内高速缓存,但考虑到图像处理算法必涉及到对前后几帧图像进行处理,为保证系统运行时存储容量不会成为整个系统的性能瓶颈(chokepoint),在DSP模块中额外扩展存储空间。

由于EMIFA口的数据宽度更大,因此系统在EMIFA的CEl空间内扩展了两片总共128M位的同步存储器。

C6416的引导方式有三种,分别是:不加载,CPU直接开始执行地址0处的存储器中的指令;ROM加载,位于EMIFBCEl空间的ROM中的程序首选通过EDMA被搬人地址O处,ROM加载只支持8位的ROM加载;主机加载,外部主机通过主机接口初始化CPU的存储空间,包括片内配置寄存器。

本系统采用的是ROM加载方式。

C6416片内有三个多通道缓冲串口,经DSP处理的最终结果将通过DSP的多通道缓冲串口传送至FPGA。

3.4图像输出模块该模块的功能是将DSP处理后的图像数据进行数模转换,并与字符信号合成后形成VGA格式的视频信号。

这里选用的数模转换芯片为ADV7125。

这是ADI公司生产的一款三通道(每通道8位)视频数模转换器,其最大数据吞吐率330MSPS,输出信图2原始图像图3FPGA图像增强结果5结论实时图像处理系统以DSP和FPGA为基本结构,并在此结构的基础上进行了优化,增加了视频输入通路。

同时所有的数据交换都通过了FPGA,后期的调试过程证明这样做使得调试非常方便,既可以监视数据的交换又方便修正前期设计的错误。

整个系统结构简单,各个模块功能清晰明了。

经后期大量的系统仿真验证:系统稳定性高,处理速度快,能满足设计要求。

号兼容RS一343A/RS一170。

由FPGA产生的数字视频信号分别进入到ADV7125的三个数据通道,经数模转换后输出模拟视频信号并与原来的同步信号、消隐信号叠加后便可以在显示器上显示处理的结果了。

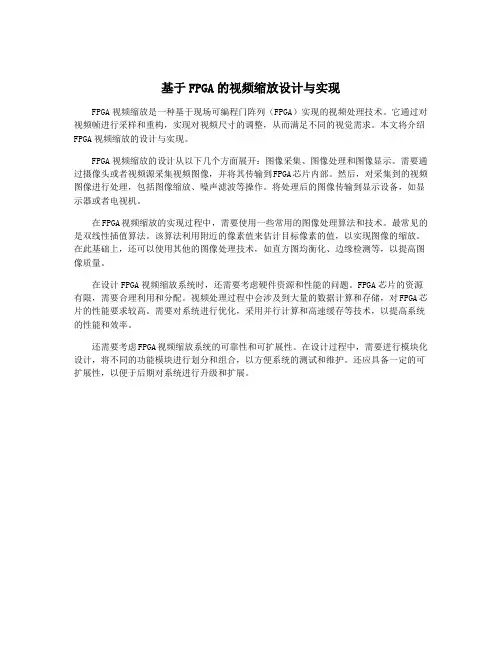

基于FPGA的视频缩放设计与实现

FPGA视频缩放是一种基于现场可编程门阵列(FPGA)实现的视频处理技术。

它通过对视频帧进行采样和重构,实现对视频尺寸的调整,从而满足不同的视觉需求。

本文将介绍FPGA视频缩放的设计与实现。

FPGA视频缩放的设计从以下几个方面展开:图像采集、图像处理和图像显示。

需要通过摄像头或者视频源采集视频图像,并将其传输到FPGA芯片内部。

然后,对采集到的视频图像进行处理,包括图像缩放、噪声滤波等操作。

将处理后的图像传输到显示设备,如显示器或者电视机。

在FPGA视频缩放的实现过程中,需要使用一些常用的图像处理算法和技术。

最常见的是双线性插值算法。

该算法利用附近的像素值来估计目标像素的值,以实现图像的缩放。

在此基础上,还可以使用其他的图像处理技术,如直方图均衡化、边缘检测等,以提高图像质量。

在设计FPGA视频缩放系统时,还需要考虑硬件资源和性能的问题。

FPGA芯片的资源有限,需要合理利用和分配。

视频处理过程中会涉及到大量的数据计算和存储,对FPGA芯片的性能要求较高。

需要对系统进行优化,采用并行计算和高速缓存等技术,以提高系统的性能和效率。

还需要考虑FPGA视频缩放系统的可靠性和可扩展性。

在设计过程中,需要进行模块化设计,将不同的功能模块进行划分和组合,以方便系统的测试和维护。

还应具备一定的可扩展性,以便于后期对系统进行升级和扩展。

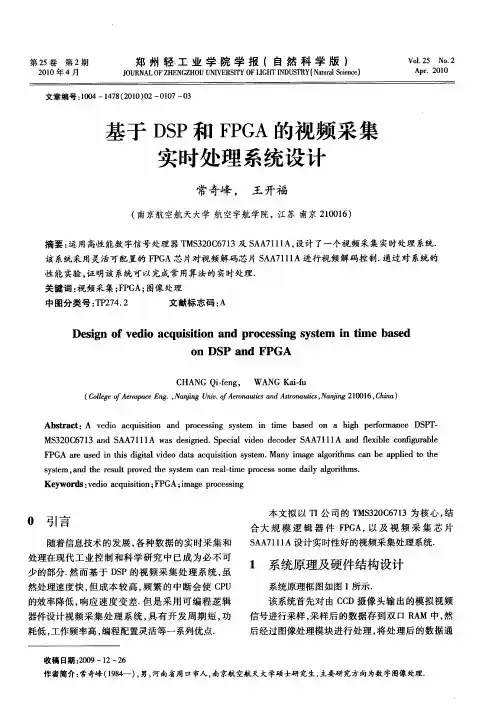

探析基于FPGA的视频采集系统设计视频图像采集是数字图像处理、监控系统等应用的必要组成部分。

图像采集与处理在工农医等领域得到了广泛应用,目前随着科技的不断发展,各种图像采集设备层出不穷,性能和实用性也得到了市场验证。

视频采集系统的实现方法有很多,本文对基于FPGA的视频采集系统设计进行探讨分析。

标签:FPGA;视频采集;系统设计1、FPGA的应用优势(1)逻辑功能强大。

FPGA采用SRAM编程技术实现系统的快速运行,增强其逻辑功能;布线资源丰富,只需擦除更改程序,即可满足系统设计所需的不同逻辑功能;可编程I/O资源丰富,可满足复杂数字逻辑设计。

(2)设计灵活。

FPGA内部的嵌入式RAM支持多种操作模式,异步先入先出(FirstInputFirstOut,FIFO)数据缓冲器可拓展FPGA的设计范围,使设计选择更加灵活;FPGA内部包含的逻辑门数较多,可满足复杂设计要求。

(3)操作简便。

为保证FPGA系统的可靠性,在使用FPGA芯片之前需进行稳定性测试,在此之后设计者只要利用软硬件环境便可设计系统功能;在实现FPGA系统不同逻辑功能时,设计者可通过多次反复编程予以实现,无需更改硬件电路。

2、基于FPGA的视频采集系统方案整体框架(1)视频采集部分:将摄像头采集到的模拟视频数据CVBS转换成数字视频格式YUV4:2:2,包括I2C总线配置,TIU656解码。

(2)视频处理部分:为适应VGA的不同显示,对视频数据做相应预处理,包括彩色VGA数据处理,灰度VGA数据处理,Sobel边沿检测数据处理,Prewitt边沿检测数据处理。

(3)视频存储部分:将视频数据储存在容量为4M×16×4Banks的SDRAM中,主要包括SDRAM控制器设计。

(4)VGA显示部分:将实时的视频数据在显示器上显示出来。

包括色度空间转换,VGA时序产生,ADV7123视频数据编码。

3、系统的具体工作流程系统上电后,由配置芯片重新配置FPGA;配置完成后,FPGA对视频解码芯片进行初始化;视频解码芯片进入工作状态,采集4路模拟视频信号;FPGA 初步处理4路数字视频信号;处理后,将4路视频数据存储到SDRAM中;在TFTLCD上显示所采集的数字化视频信息;利用IO口,可在外部切换采集通道,对系统进行复位操作。

基于FPGA的实时视频图像采集与显示系统的设计与实现作者:贡镇来源:《现代电子技术》2013年第13期摘要:主要针对目前视频图像处理发展的现状,结合FPGA技术,设计了一个基于FPGA的实时视频图像采集与显示系统。

系统采用FPGA作为主控芯片,搭载专用的编码解码芯片进行图像的采集与显示,主要包括解码芯片的初始化、编码芯片的初始化、FPGA图像采集、PLL设置等几个功能模块。

采用FPGA的标准设计流程及一些常用技巧来对整个系统进行编程。

重点在于利用FPFA开发平台对普通相机输出的图像进行采集与显示,最终能在连接的RCA端口显示屏显示。

关键词: FPGA;视频图像采集;编码芯片;解码芯片中图分类号: TN911⁃34 文献标识码: A 文章编号: 1004⁃373X(2013)13⁃0046⁃03Design and Implementation of real⁃time video image captureand display system based on FPGAGONG Zhen(Anhui University of Science and Technology, Huainan 232000, China)Abstract: Based on the current development status of the video image processing and FPGA technology, a FPGA⁃based real⁃time video image capture and display system is designed in this paper. Equipped with dedicated coding and decoding ship for image capture and display, the system adopts FPGA as the main control chip, which are composed of decoding chip initialization module, the encoding chip initialization module, FPGA image acquisition module and PLL setting module. FPGA⁃standard design flow and some commonly used techniques are taken to program the entire system. The focus is to realize the ordinary camera output image acquisition and display via the FPFA development platform, and ultimately connect the RCA port display screen.Keywords: FPGA; video image capture; coding chip; decoding chip0 引言随着时代的发展,人们在图像处理领域取得了相当多的成果,研究出了很多算法,例如中值滤波、高通滤波等。

大连海事大学硕士学位论文基于FPGA的视频图像处理系统姓名:杨宁申请学位级别:硕士专业:电路与系统指导教师:董辉;白桂欣 20080301中文摘要摘要随着电子技术和计算机技术的飞速发展,视频图像处理技术近年来得到极大的重视和长足的发展,其应用范围主要包括数字广播、消费类电子、视频监控、医学成像及文档影像处理等领域。

当前视频图像处理主要问题是当处理的数据量很大时,处理速度慢,执行效率低。

而且视频算法的软件和硬件仿真和验证的灵活性低。

本论文首先根据视频信号的处理过程和典型视频图像处理系统的构成提出了基于FPGA的视频图像处理系统总体框图;其次选择视频转换芯片S丸钾113,完成视频图像采集模块的设计,主要分三步完成:1配置视频转换芯片的工作模式, 完成视频转化芯片SAA7113的初始化:2・通过分析输出数据流的格式标准,来识别奇偶场信号、场消隐信号和有效行数据的开始和结束信号三种控制信号,并根据控制信号,用Verilog.硬件描述语言编程实现图像数据的采集;3分析SRAM 的读写控制时序,采用两块SRAM完成图像数据的存储。

然后编写软件测试文件, 在ISE Simulator仿真环境进行程序测试与运行,并分析仿真结果,验证了数据采集和存储的正确性;最后,对常用视频图像算法的MATI.AB仿真,选择适当的算子,采用工具MATIJLB、System Generator for DSP和ISE,利用模块构建方式, 搭建视频算法平台,实现图像平滑滤波、锐化滤波算法,在Simulink中仿真并自动生成硬件描述语言和网表,对资源的消耗做简要分析。

本论文的创新点是采用新的开发环境System Generator for DSP实现视频图像算法。

这种开发视频图像算法的方式灵活性强、设计周期短、验证方便、是视频图像处理发展的必然趋势。

关键词:视频信号;视频采集;Ver i log;图像算法英文摘要Processing System of Video Image based on FPGAAbstractWith therapid development of electronics and computer technology,video image processing is increasingly being paid more attention and being used in a variety of fields,DMB(Digital Multimedia Broadcasting,consumer electronics,surveillance,medicinalimaging and documentimage processing and SO on.The main challenges for imageprocessing due to both the speed and the low-efficiency when the enormous amount of video data require per frame.The second challenge is dealing with simulation time and test environment.Simulink,they Can automaticallygenerated HDL filesand Netlist.And it can be used inthe ISE.The innovation point of the paper is to develop video image algorithm in System Generator for DSP,It’S the ideal platform and the trend of video image processing,for flexible and convenience.Key Words:Video SignaI:Video sampIe;Ver i Iog;Image aIgor ithm大连海事大学学位论文原创性声明和使用授权说明原创性声明本人郑重声明:本论文是在导师的指导下,独立进行研究工作所取得的成果, 撰写成硕士学位论文==基王壁鱼△的视麴图堡处理丕缠 :。

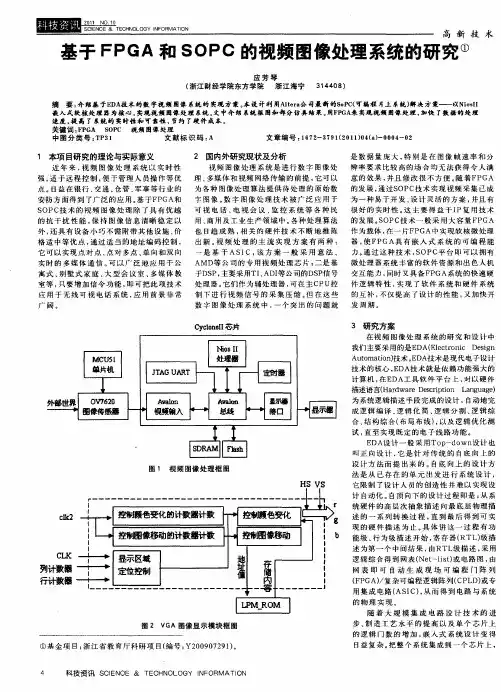

基于FPGA和SOPC的视频图像处理系统的研究摘要:介绍基于EDA技术的数字视频图像系统的实现方案。

本设计利用Altera公司最新的SoPC(可编程片上系统)解决方案——以NiosII嵌入式软核处理器为核心,实现视频图像处理系统。

文中介绍系统框图和部分仿真结果。

用FPGA来实现视频图像处理,加快了数据的处理速度,提高了系统的实时性和可靠性,节约了硬件成本。

关键词:FPGA SOPC 视频图像处理1 本项目研究的理论与实际意义近年来,视频图像处理系统以实时性强,适于远程控制,便于管理人员操作等优点。

日益在银行、交通、仓管、军事等行业的安防方面得到了广泛的应用。

基于FPGA和SOPC技术的视频图像处理除了具有优越的抗干扰性能,保持图像信息清晰稳定以外,还具有设备小巧不需附带其他设施、价格适中等优点,通过适当的地址编码控制,它可以实现点对点、点对多点、单向和双向实时的多媒体通信。

可以广泛地应用于公寓式、别墅式家庭、大型会议室、多媒体教室等,只要增加信令功能,即可把此项技术应用于无线可视电话系统,应用前景非常广阔。

2 国内外研究现状及分析视频图像处理系统是进行数字图像处理、多媒体和视频网络传输的前提,它可以为各种图像处理算法提供待处理的原始数字图像。

数字图像处理技术被广泛应用于可视电话、电视会议、监控系统等各种民用、商用及工业生产领域中。

各种处理算法也日趋成熟,相关的硬件技术不断地推陈出新。

视频处理的主流实现方案有两种: 一是基于ASIC,该方案一般采用意法、AMD等公司的专用视频处理芯片;二是基于DSP,主要采用TI、ADI等公司的DSP信号处理器。

它们作为辅处理器,可在主CPU控制下进行视频信号的采集压缩。

但在这些数字图像处理系统中,一个突出的问题就是数据量庞大,特别是在图像帧速率和分辨率要求比较高的场合均无法获得令人满意的效果,并且修改很不方便。

随着FPGA的发展,通过SOPC技术实现视频采集已成为一种易于开发、设计灵活的方案,并且有很好的实时性。

基于FPGA的实时视频处理平台方案讨论及设计

为了能够实时地采集、处理、显示视频,设计并实现了一种基于双

PowerPC硬核架构的实时视频处理平台;用硬件实现视频的预处理算法,并以用户IP核的形式添加到硬件系统中,上层的视频处理软件程序则

直接从存储器中调用预处理后的图像数据;重点介绍了在FPGA上构建双

PowerPC硬核架构的硬件系统;采用乒乓控制算法缓存一行图像数据;用DMA的方式将图像数据保存在存储器中;以边缘检测作为视频预处理算

法的一个实例,在平台上实现,实验结果表明,用本平台实现仅需

40ms;本平台能够实时处理视频,具有较高的实用价值。

0 引言

目前,视频处理平台大多使用DSP芯片进行图像处理。

实时视频处理对系统性能提出了极高的要求,几乎最简单的功能也超出了单个通用

DSP芯片的处理能力。

一旦达到极限,通常只有增加额外的DSP芯片。

2010年郭春辉提出一种基于多条带、多DSP的并行视频处理系统[1]。

这种采用多处理器并行处理的方法虽然提高了处理速度,但增加了系统开发

的复杂度,例如任务的合理分配,多处理器之间的通信、互斥等。

当然,也

增加了系统的功耗。

DSP在性能方面的局限导致开发更为专用的芯片,如

多媒体处理器,来克服这些问题。

然而,事实证明这些器件除了在范围极窄

的一些应用中,都有不灵活的缺点,同时还存在性能瓶颈。

基于处理器的方。