DSP实验指导书

- 格式:doc

- 大小:1.75 MB

- 文档页数:16

《DSP原理》实验指导书《DSP原理》实验使用XDS510USB Emulator实验箱完成。

该实验箱提供了极其丰富的功能单元电路以及高度灵活的可搭接性, 使其完全能够完成具有复杂性和创造性的综合性实验。

实验装置采用与可编程器件分离设计,可编程器件焊接在独立的下载板上。

通过选择下载板可以选择不同厂家、不同型号、不同规模的可编程器件,既可适应不同教学需要,也使系统的功能和规模扩展变得更为方便。

实验装置提供接线、驱动、扩展集成插座和部分必须的分立元件,留有足够的接线机会,也给实验装置留有足够的机动灵活性。

为了方便实验操作,减少对实验仪器仪表的依赖,在实验装置中配备了一些基本功能模块和实验小工具。

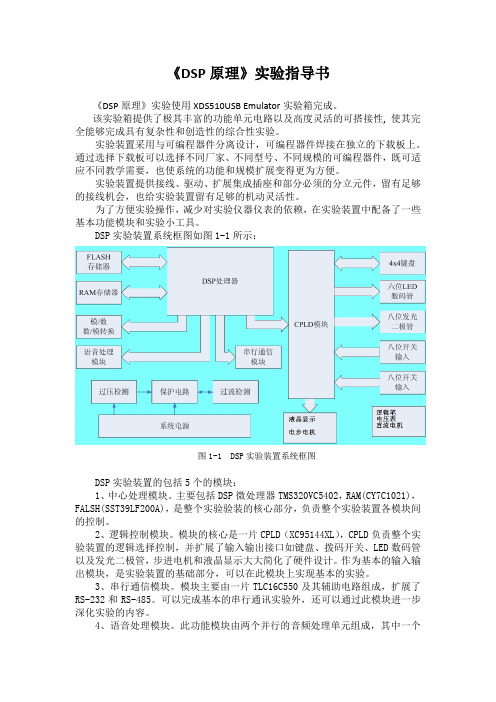

DSP实验装置系统框图如图1-1所示:图1-1 DSP实验装置系统框图DSP实验装置的包括5个的模块:1、中心处理模块。

主要包括DSP微处理器TMS320VC5402,RAM(CY7C1021),FALSH(SST39LF200A),是整个实验验装的核心部分,负责整个实验装置各模块间的控制。

2、逻辑控制模块。

模块的核心是一片CPLD(XC95144XL),CPLD负责整个实验装置的逻辑选择控制,并扩展了输入输出接口如键盘、拨码开关、LED数码管以及发光二极管,步进电机和液晶显示大大简化了硬件设计。

作为基本的输入输出模块,是实验装置的基础部分,可以在此模块上实现基本的实验。

3、串行通信模块。

模块主要由一片TLC16C550及其辅助电路组成,扩展了RS-232和RS-485。

可以完成基本的串行通讯实验外,还可以通过此模块进一步深化实验的内容。

4、语音处理模块。

此功能模块由两个并行的音频处理单元组成,其中一个单元主要是基本的数模、模数转换,另外一个单元是语音处理单元,主要的处理芯片是TLV320AIC10。

后续的章节将给予详细介绍。

5、辅助模块。

辅助模块主要提供的是实验所需的工具,是本实验装置的一个特色所在,也是装置人性化的一面。

实验一:DSP软件集成开发环境CCS一. 实验目的1.了解DSP 软件开发集成环境Code Composer Studio (CCS) 的安装和配置过程;2.熟悉并掌握CCS 的操作环境和基本功能,了解DSP软件开发的一般流程:(1) 学习创建工程和管理工程的方法;(2) 了解工程文件和映像文件的基本内容;(3) 了解基本的编译和调试功能;(4) 学习使用观察窗口。

二. 实验设备计算机、Code Composer Studio 2.2 或以上版本三. 背景知识1.DSP 应用系统开发一般需要借助以下调试工具:―软件集成开发环境(CCS):完成系统的软件开发,进行软件和硬件仿真调试;―硬件开发及测试平台:实现系统的硬件仿真与调试,包括仿真器和评估模块。

S 集成了适用于所有TI 器件的源码编辑、编译链接、代码性能评估、调试仿真等功能,为设计人员提供了一个完整的嵌入式系统软件开发环境。

3.系统软件部分可以通过CCS 建立的工程文件进行管理,工程文件一般包含以下几种文件:―源程序文件:C 语言或汇编语言文件(*.ASM 或*.C)―头文件(*.H)―命令文件(*.CMD)―库文件(*.LIB, *.OBJ)四. 实验步骤1.创建工程文件双击CCStudio 图标,启动CCS,CCS 的初始界面包括工程管理区和工作区两部分。

在菜单中选择“Project—>New…”,弹出“Project Create”窗口:若标题栏显示xxxx Emulator,则需要先运行Setup CCS,选择合适的软件仿真环境在“Project”编辑框内填入项目名称,例如“hello1”;有必要的话,可以更改项目文件夹位置(Location);“Project”下拉框用以确定输出文件类型;目标硬件类型在“Target”下拉框中指定。

点击“完成”后,CCS 自动在指定目录下生成“hello1.pjt”工程文件。

工程文件中保存了对应工程的设置信息和内部文件的引用情况。

DSP原理及应用实验指导书实验一:熟悉CCS,编写一个以C语言为基础的DSP程序一、实验目的1.认识TMS320LF2407 DSP实验开发系统的硬件结构。

2.了解TMS320LF2407 DSP应用程序的开发调试流程。

3.学习使用CCS3.3调试TMS320LF2407 DSP程序。

4.学习用标准C语言编制程序:了解常用的C语言程序设计方法和组成部分。

二、实验设备PC兼容机一台,操作系统为Windows2000(或Windows98,Windows XP,以下默认为Windows2000),CCS3.3编译软件,TMS320LF2407 DSP实验开发板和仿真器。

三、实验原理1.标准C语言程序:CCS支持使用标准C语言开发DSP应用程序。

当使用标准C语言编制程序时,其源文件名的后缀应为.C(如:volume.c)。

CCS在编译标准C语言程序时,首先将其编译成相应汇编语言程序,再进一步编译成目标DSP的可执行代码。

最后生成的是COFF格式的可下载到DSP 中运行的文件,其文件名后缀为.out。

由于使用C语言编制程序,其中调用的标准C的库函数由专门的库提供,在编译链接时编译系统还负责构建C运行环境。

所以用户工程中需要注明使用C 的支持库。

2.命令文件的作用:命令文件(文件后缀为.cmd)为链接程序提供程序和数据在具体DSP硬件中的位置分配信息。

通过编制命令文件,我们可以将某些特定的数据或程序按照我们的意图放置在DSP所管理的内存中。

命令文件也为链接程序提供了DSP外扩存储器的描述。

在程序中使用CMD文件描述硬件存储区,可以只说明使用部分,但只要是说明的,必须和硬件匹配,也就是只要说明的存储区必须是存在的和可使用的。

3.内存映射(map)文件的作用:一般的,我们设计、开发的DSP程序在调试好后,要固化到系统的ROM 中,为了更精确的使用ROM空间,我们就需要知道程序的大小和位置,通过建立目标程序的map文件可以了解DSP代码的确切信息。

DSP实验指导书DSP原理与应⽤实验指导书张卫宁王晓东⼆零⼀零年四⽉⽬录第⼀部分软件仿真(Simulator)实验实验⼀集成开发环境CCS应⽤基础实验⼆寻址⽅式实验三定点定标运算实验四浮点运算实验五汇编程序的优化实验六C语⾔编程与优化(乘法—累加运算程序设计)实验七混合编程实验实验⼋FIR滤波器的实现实验九基于DSP的数字图像处理算法的实现第⼆部分硬件(Emulator)实验实验⼗⽚内定时器实验实验⼗⼀数字I/O⼝的应⽤实验⼗⼆同步串⼝与A/D转换实验⼗三基于DSP的数字⾳频处理系统第三部分部分实验程序参考清单实验⼀参考程序实验⼆参考程序实验三参考程序实验四参考程序实验五参考程序第四部分参考资料⼀、C54xCPU的存储器映像寄存器及其地址⼆、C54xCPU的状态和控制寄存器ST0、ST1三、TMS320C5416DSP的存储区映像四、C54xCPU的处理器模式状态寄存器PMST五、C54x的⽚内定时器控制寄存器TCR六、TMS320C5416的中断⽮量表参考⽂献第⼀部分软件仿真(Simulator)实验实验⼀集成开发环境CCS应⽤基础⼀、⽬的1. 通过创建⼀个简单的应⽤⼯程,初步熟悉Code Composer Studio(简称CCS)的集成开发环境(IDE)及其⼯具的使⽤。

2. 掌握汇编语⾔源程序的基本框架和编写⽅法,了解CCS的⼯程结构以及编译、汇编、连接、运⾏和调试的基本过程。

3. 了解ST0、ST1的控制位对计算过程的控制以及计算结果对状态位的影响。

⼆、内容1. 学习使⽤CCS集成开发环境(IDE)的各种⼯具。

包括下列内容:(1)编辑、汇编和连接。

(2)查看和修改存储器映像寄存器的内容。

(3)查看和修改ST0、ST1及PMST的有关位。

(4)查看和修改程序存储器和数据存储器的内容。

(5)断点操作。

(6)运⾏程序(单步运⾏、连续运⾏和断点运⾏)。

2. 观察并理解COFF段结构的划分及存储空间的分配。

实验一常用指令实验一、实验目的1、了解DSP开发系统的组成和结构;2、掌握DSP开发系统连接过程和DSP的开发界面;3,熟悉LF2407系列的寻址系统及常用LF2407系列指令的用法。

二、实验设备计算机,CCS 2.0版软件,DSP仿真器,EXP3实验箱。

三.实验步骤与内容开发TM S 320C2xxx应用系统一般需要以下几个调试工具来完成:(1)软件集成开发环境(CodeComposer):完成系统的软件开发,进行软件和硬件仿真调试。

它也是硬件调试的辅助乎段。

(2)开发系统:实现硬件仿真调试时与硬件系统的通信,控制和读取硬件系统的状态和数据。

(3)评估模块:提供软件运行和调试的平台和用户系统开发的参照。

(4) CodeComposer4.1卞要完成系统的软件开发和调试。

它提供一整套的程序编制、维打…、编译、调试环境,能将汇编语言和C语言程序编译连接生成COFF(公共目标文件)格式的可执行文件,并能将程序下载到目标DSP上运行调试。

(5)用户系统的软件部分可以由CodeComposer建立的工程文件进行管理,工程文件一般包含以下几种文件:源程序文件:C语言或汇编语言文件(*.ASM或*.C)头文件(*H)命令文件(*.CMD)库文件(*.LIB)中断向量交件(*.ASM)★启动CodeComposer双击桌面上“CC C2000 "启动Code Composer 4.1;可以看到显示出的C2XX CodeComposer窗口;★创建工程(1)创建新的工程文件:选择菜单“Project”的“New...”项;输入工程文件名字并保存;这时建立的是一个空的工程文件;.(2)在工程文件中添加程序文件:选择菜单“Project”的“Add Files to Project...”项;在“Add Files to Project”对话框中改变文件类型为“Asm Source Files(.a*;*.s*)",选择文件“*asm";重复上述各步骤,再添加以下文件到工程中;*.cmd, vector.asm.(3)编译连接工程:选择菜单“Project”的“Rebuild All”项;注意编译过程中CCS卞窗日下部的“Build"提示窗中显示编译信息,最后将给出错误和警告的统计数;编辑修改工程中的文件.(4)查看工程文件展开CCS卞窗日左侧工程管理窗中的工程各分支,可以看到“*.mak*工程中包含"*.asm","*.cmd"和"*.h;,其中“*.h”为程序在编译时根据程序中的“include"语句自动加入的;(5).查看源文件双击工程竹理窗中的“`'`as m”文件,可以查看程序内容;双击工程竹理窗中的“`'`.h”文件,打开此文件显示,可以看到其中有卞程序中要用到的一些寄存器等;" *.cmd”文件定义程序所放置的位置,此例中描述了LF2407的片内存储器资源,指定了程序和数据在内存中的位置;(6)基本调试功能:a)执行File-Load Program,在随后打开的对话框中选择刚刚建立的*.out文件;在项日浏览窗日中,双击`'`.rim激活这个文件,移动光标到start 行上,右击鼠标选择Toggle Breakpoint或按F9设置断点;b)使用观察窗口执行View令Watch window打开观察窗日;在`*asm中,选中任意一个变量,右击鼠标,选择”Quickwatch",CCS将打开quickwatch窗口并显示选中的变量;在`*asm中,选中任意一个变量,右击鼠标,选择”Add to watch window",CCS将把变量添加到观察窗日并显示选中的变量值;在观察窗日中双击变量,则弹出修改变量窗日,此时,可以在这个窗日中改变程序变量的值。

DSP实验指导书-图文数字信号处理E某PIV教学实验系统110实验五离散余弦变换(DCT)算法实验一、实验目的学习DCT算法的实现方法。

二、实验设备计算机,CCS2.0版软件,实验箱,DSP仿真器。

三、实验原理离散余弦变换与离散傅立叶变换紧密相关的,属于正弦类正交变换,由于其优良的去冗余性能及高效快速算法的可实现性,被广泛用于语音及图象的有损和无损压缩。

在开始实验之前,应了解以下基本原理。

1.语音或图象的压缩手段;2.DCT变换在数据压缩中的作用与应用。

四、实验步骤1.阅读本实验所提供的样例子程序;2.运行样例程序,分析结果;3.样例程序实验操作说明A.实验前准备1)正确完成计算机、DSP仿真器和实验箱连接后,开关K9拨到右边,即仿真器选择连接右边的CPU:CPU2;系统上电;2)“A/D转换单元”的拨码开关设置:JP3拨码开关:码位123456备注ON:将“模拟信号源”单元的信号输入到AD7822OFF:OFF:OFF:OFF:OFF:SW2拨码开关:SW21ON2ON3ON4备注码位ONAD7822的采样时钟为250KHZ,且中断给CPU2的中断2数字信号处理E某PIV教学实验系统111S23拨码开关:码位1、2B.实验启动CCS2.0,Project/Open打开“Algorithm”目录中“e某p05_cpu2”子目录下“E某p-DCT-AD.pjt”工程文件;双击“E某p-DCT-AD.pjt”及“Source”可查看各源程序;加载“E某p-DCT-AD.out”;在主程序中,在flag=0处设置断点;单击“Run”运备注OFF,不混频行程序,程序将运行至断点处停止;数字信号处理E某PIV教学实验系统112用View/Graph/Time/Frequency打开两个图形观察窗口;采用双踪观察在启始地址分别为某和y,长度为128的单元中数值的变化,数值类型为32位浮点型,这两个数组分别存放的是经A/D转换的输入信号和对该信号进行DCT变换的结果;再打开一个图形观察窗口,设置观察变量为z;变量z为输入信号的DCT变换及逆DCT变换的结果,长度128,32位浮点型,即输入信号的重构信号;调整各图形观察窗口,观察正变换与逆变换结果;单击“Animate”运行程序,调整各图形观察窗口,动态观察变换结果;改变输入信号的波形、频率、幅值,动态观察变换结果;数字信号处理E某PIV教学实验系统113单击“Halt”暂停程序运行,关闭窗口,实验结束;实验结果:在CCS2.0环境,同步观察输入信号及其DCT变换结果。

第一章.实验系统标准配置SZ-DSP II型模块简介:1、TI主控板(2407、5402、5416)其中任意一种2、ALTERA的CPLD系统模板一块3、高速或者高精度A/D、D/A板可选4、CAN总线接口(2407用)5、USB接口6、同步串行口(5416用)7、232、485异步串口电路8、语音芯片TLC320AD50(5416用)9、I/O 扩展电路10、语音电路11、CPLD电路12、单片机管理单元13、拨码功能选择电路14、键盘、液晶屏电路15、数码管、发光二极管显示电路16、机电控制模块(可选)18、视频模块(可选)实验仪的开关、插座定义及初始状态:1、J28是USB接口2、J24为CAN总线接口3、DB9插座是232异步串行接口4、J3是485接口5、M3是耳机插孔,语音输出用6、M1是麦克风插孔,语音输入用7、J31是可外扩的DSP高16位数据和高位地址线接口(位于主板的最左上方),其具体管脚定义如下:1~8脚是DSP的高位地址线A23~A16;9~24脚是DSP的高16位地址线D31~D16;8、J32是可外扩的DSP低16位地址线和数据线接口,其具体管脚定义如下:1~16脚是DSP的低16位地址线A15~A0;17~32脚为DSP的低16位数据线D0~D15;31脚是电源端+5V,32脚是接地端GND。

9、J43为DSP F2407的16位A/D引出端,其具体管脚分布如下:1~16是DSP 2407的16位A/D ADCIN00~ADCIN15;17脚是模拟地AGND,18脚是模拟电压A3.3V。

10、J33是CPLD或FPGA(以下简称CPLD)的I/O脚用来做控制线的输出端,可做二次开发用,其接口如下:1~10脚是DSP小系统上的CPLD的I/O引出端,可作为信号的输出用;11~20脚是DSP小系统上的CPLD的I/O引出端,可作为信号的输入输出用;21、31脚是空脚;22脚是DSP的时钟引出端;23、24、25脚分别可作为FLASH的写控制、读控制、片选;26、28 脚为DSP小系统上CPLD的全局使能引出端,可作为信号输入也可为全局使能信号;27、30脚为DSP小系统上CPLD的时钟引出端,可作为输入信号也可为时钟输入;29脚是DSP小系统上CPLD的引出端,可作为信号输入;32脚是复位信号RESET。

dsp实验指导书实验一I/O实验实验目的:熟悉SZ—DSPII实验平台的使用了解DSP对I/O口的访问方式熟悉简单的程序设计及指令运用实验设备:计算机;DSP硬件仿真器;DSP实验开发平台实验硬件设置:在做实验以前,需要接通该实验的硬件电路,本实验为:先将实验箱右侧的船型开关往“I”方向打开电源,然后将系统主板的开关S33往下拨接通+/-5V电源,然后将CPLD/FPGA模块上的电源开关S9往下(ON)拨,开关S10往下拨来选通主板上发光二极管等输出指示设备;将系统主板中“MCU/DSP选择档”选中MCU(往下拨),将“功能键7”拨上去,电击键盘中的RST键,MCU将对所有发光二极管进行检测,如果所有的发光二极管正常,则将“MCU/DSP选择挡”选中DSP,将功能键1到7都拨下来。

然后开始做实验,注意在做实验时开始按了RST硬件复位后,实验不要再按RST键,以免由于DSP复位而失败。

如果实验中硬件工作不正常,可按RST对整个系统硬件进行复位。

实验原理:本程序主要是实现将数据往一个I/O端口送,从而显示一种状态,来验证DSP对I/O口的访问。

该实验是由DSP直接编程,往发光二极管送数,运用PORTW指令,观察发光二极管的变化,从而完成基本的I/O实验。

D8-D15高八位数据DSPCPLD锁存8个指示灯指示灯的片选1002H硬件框图实验程序框图DSP送出不同的数据DSP初始化开始输出到1002H实验程序FG_ADDR.et1002HDATADELAY.macroec_tenthloop1STM#09h,AR6loop0STM#19999,AR7BANZ$,某AR7-BANZloop0,某AR6-BANZloop1,某AR5-.endm ;延时ec_tenth/10秒STMec_tenth-1,AR5reet:.et60h;doubleramdata.ect\B_c_int00NOPNOP.pace31某4某16.title\.global_c_int00.mmreg.te某tLD#0h,DPSTM#3000h,SPRSB某INTMSTM#07FFFh,SWWSR;工作在20MHz_c_int00:SSB某某F;某F=1ST#1007h,CLKMDRPT#0FFhNOPSTM#0ffffh,IFRORM#000h,IMRRSB某S某MST#8100H,DATA#10WRDENG:PORTWDATA,FG_ADDRDELAYNOPST#4200H,DATADATA,FG_ADDR#10PORTWDELAYST#2400H,DATAPORTWDELAYST#1800H,DATAPORTWDELAY#10ST#1800H,DATAPORTWDELAYDATA,FG_ADDR#10DATA,FG_ADDRDATA,FG_ADDR#10RPT#10NOPST#2400H,DATAPORTWDELAYRPT#10NOPST#4200H,DATAPORTWDELAYRPT#10NOPST#8100H,DATAPORTWDELAYRPT#10NOPSTM#00H,DATA;;;PORTWDELAYNOPST#100H,DATADATA,FG_ADDR#10PORTWDELAYST#200H,DATAPORTWDELAYST#400H,DATAPORTWDELAY#10DATA,FG_ADDRDATA,FG_ADDR#10DATA,FG_ADDR#10DATA,FG_ADDR#10DATA,FG_ADDR#10DATA,FG_ADDR#10ST#800H,DATAPORTWDELAYRPT#10NOPST#1000H,DATAPORTWDELAY#10RPT#10NOPST#2000H,DATAPORTWDELAYRPT#10NOPST#4000H,DATAPORTWDELAYRPT#10NOPSTM#8000H,DATAPORTWDELAYRPT#10NOP;;;ST#8000H,DATAPORTWDELAYST#4000H,DATADATA,FG_ADDR#10DATA,FG_ADDR#10DATA,FG_ADDR#10DATA,FG_ADDR#10DATA,FG_ADDRDATA,FG_ADDR#10PORTWDELAYDATA,FG_ADDR#10ST#2000H,DATAPORTWDELAY#10ST#1000H,DATAPORTWDELAYRPT#10NOPST#800H,DATAPORTWDELAY#10RPT#10NOPST#400H,DATAPORTWDELAYRPT#10NOPST#200H,DATAPORTWDELAYRPT#10NOPSTM#100H,DATAPORTWDELAYRPT#10NOPST#8100H,DATADATA,FG_ADDR#10DATA,FG_ADDR#10DATA,FG_ADDR#10DATA,FG_ADDRDATA,FG_ADDR#10DATA,FG_ADDRBWRDENGaaanopbaaa.end思考题:有哪三种以上的寻址方式可以完成上述实验?并描述其原理。

DSP技术实验指导书陈军波刘海华编电子信息工程学院信号处理教研室2005年10月目 录第一部分DSP实验教学平台功能介绍 (3)☆结构简介: (3)☆数据流程图 (17)第二部分基础实验 (20)实验一CCS操作与DSP综合外设控制实验 (20)实验二DSP存储器及基本指令实验 (33)实验三快速傅里叶变换(FFT)实现 (38)实验四有限冲击响应滤波器(FIR)实现 (43)实验五无限冲击响应滤波器(IIR)实现 (51)实验六实时语音FIR滤波设计实验 (57)第三部分创新性实验 (60)实验一温度测量实验 (60)实验二YUV彩色图像处理之增强对比度 (62)实验三脉冲幅度相干(PAM)解调实验 (66)实验四MP3音频解码实验 (70)提示:请不要带电拔插仿真器和板卡!第一部分DSP实验教学平台功能介绍☆结构简介:一、主要功能模块:1、主CPU(SZ-5416D)模块:采用TI公司TMS320C5416DSP(以下简称5416)芯片,该模块上的资源有:4mbit flash、256k*16bit SRAM、2500 gate CPLD、电平转换芯片,模块上留有JTAG 插口,用户可以通过仿真器和CCS下载程序和进行实验;2、主CPU(SZ-2407E)模块:采用TI公司TMS320LF2407DSP(以下简称2407)芯片,该模块上的资源有:256k*16bit SRAM、2500 gate CPLD、电平转换芯片,模块上留有JTAG插口,用户可以通过仿真器和CCS下载程序和进行实验;以上两个模块可以通过5416的HPI接口实现双DSP的高速并行数据交换。

在实现对其他对象操作时,在平台的主板采用了CPLD(XC95216)来实现两DSP之间的软切换。

3、图象、语音模块(SZ-DSPFVV板):图象采用高速AD(TLC5510)和高速的DA(TLC5602),同时TLC5510和TLC5602又可做普通的AD、DA实验;语音模块采用专用语音处理芯片TLC320AD50C,最高采样率为22.05KHz,16位串行接口。

第一章实验设备说明一.ICETEK–F28335-A评估板技术指标DSP控制技术实验指导书北京信息科技大学自动化学院2011年4月1 主处理芯片:TMS320F28335,运行速度为150MHz;具有一个浮点内核,处理速度更快,工作速度可达150MIPS;片上RAM 68k*16bit;片上扩展SRAM存贮空间64K*16Bit;最大可扩至512K*16Bit自带16路12bit A/D,最大采样速率1 2.5MSPS,采集电压范围0-3v;其中六路AD硬件调整为可采集+-5v电压信号。

2路的DAC7528转换,10M/S,8Bit;2路UART串行接口,一路为RS232接口;一路为RS232/RS485可选;16路PWM输出;1路CAN接口通讯;片上256K*16bit FLASH,自带128位加密位;设计有用户可以自定义的开关,测试指示灯和复位电路;4组标准扩展连接器,为用户进行二次开发提供条件;兼容ICETEK系列扩展模块;具有IEEE1149.1相兼容的逻辑扫描电路,该电路仅用于测试和仿真;+5V电源输入,内部+3.3V、+1.9 V电源管理;高保真语音接口设计,双路语音采集,每路96K/S;4层板设计工艺,工作稳定可靠;具有自启动功能设计,可以实现脱机工作;可以选配多种应用接口板,包括语音板,网络板等;2三.ICETEK-F28335-A 器件分布图二.ICETEK –F28335-A 评估板实物图ADREFIN扩展插座ADCLO模式跳线F 设置2JTAG仿真插头标准RS-232电源指示灯+5V 电 源插座U3四路用户 D2-D5P3Bootload扩展插座 可控开关 用户可控er 模式选指示灯择开关扩展插座音频插座 J12立体声输出J11耳机输出J10立体声输入 J9 麦克风输入图 1.2 ICETEK –F28335-A 器件分布图CAN 接口四. ICETEK –F28335–A 评估板原理框图J5P1扩展插座复位按扭图 1.1ICETEK-F28335-A 评估板实物图图 1.3 评估板原理框图3 4五.评估板的内存映射图块起始地址片内存储空间(On-Chip)片外存储空间(XINTF)数据空间程序空间数据空间程序空间M0 向量–随机存储器(32*32)0x00 0000(当VMAP = 0时有效)M0 SARAM(单存取随机存储器) 1K*16 0x00 0040M1 SARAM(单存取随机存储器) 1K*16 0x00 0400外设寄存器组00x00 0800(2K*16)保留外设向量(PIE Vector)无效(256*16)0x00 0D00(当VMAP=1,ENPIE=1时有效)外设寄存器组0 0x00 0E00保留0x004000 相当于片外空间0(4K*16 XZCS0)保留TMS320F 0x00 2000(保护,D MA管理)24x/LF240x00 0x数据存5000 储空间外设寄存器组 3相当于相当于TMS320F24x/LF240x程序存储空间块起始地址0x00 E0000x00 F0000x01 00000x30 00000x33 FFF80x34 00000x38 00000x38 04000x38 08000x3F 80000x3F 90000x3F A0000x3F B0000x3F C0000x3F E0000x3F FFC0片内存储空间(On-Chip)L6 SARAM(单存取随机存储器) 4K*16(DMA管理)L7 SARAM(单存取随机存储器) 4K*16(DMA管理)保留FLASH (256K *16,安全块)128-bit 密码保留TI OTP(1K*16,保留)用户OTP(1K*16,安全块)保留L0 SRAM(4K*16,安全块)L1 SRAM(4K*16,安全块)L2 SRAM(4K*16,安全块)L3 SRAM(4K*16,安全块)保留Boot ROM(8K*16)BROM向量,32*32)当VMAP (=1,MP/MC=0,ENPIE=0时有效片外存储空间(XINTF)片外空间6(1M*16 XZCS6)DMA管(0x10理)0000片外空间7(1M*16 XZCS7)DMA管(0x20理)0000保留图1.40x00 5000保护(DMA管理)外设寄存器组 1 0x00 6000保留(4K*16)受保护外设寄存器组 20x00 7000(4K*16受保护)L0 SARAM(单存取随机存储器) 4K*160x00 8000(安全块)保留L1 SARAM(单存取随机存储器) 4K*16 0x00 9000 (安全块)L2 SARAM(单存取随机存储器) 4K*160x00 A000(安全块)L3 SARAM(单存取随机存储器) 4K*160x00 B000(安全块)L4 SARAM(单存取随机存储器) 4K*160x00 C000(DMA 管理)L5 SARAM(单存取随机存储器) 4K*16 0x00 D000(DMA管理)5评估板的内存映射图6六.液晶控制板实物图:第二章实验环境设置一.ICETEK-DSP教学实验箱的硬件连接1. 打开实验箱,取出三相电源连接线(如右图),将电源线的一端插入实验箱外部左恻箱壁上的电源插孔中。

确认实验箱面板上电源总开关(位于实验箱底板左上角)处于“关”的位置,连接电源线的另一端至220V交流供电插座上,保证稳固连接。

随后可以接通电源。

二.设置CCSCCS工作环境分为:软仿真环境(Simulator)和硬仿真环境(Emulator)1.设置CCS 工作在软件仿真环境CCS 可以工作在纯软件仿真(Simulator)环境中,就是由软件在PC 机内存中构造一个虚拟的DSP 环境,可以调试、运行程序。

但一般软件无法构造DSP 中的外设,所以液晶控制板实物图软件仿真通常用于调试纯软件的算法和进行效率分析等。

在使用软件仿真方式工作时,无需连接板卡和仿真器等硬件。

其具体设置步骤如下:(1) 单击桌面上图标:进入CCS 设置窗口。

(2) 在出现的窗口中按标号顺序进行如下设置:7 82.设置 CCS 工作在硬仿真工作环境通过 ICETEK-5100USB 仿真器连接 ICETEK –F28335-A 硬件环境进行调试和开 发。

(1) 单击桌面上图标进入 CCS 设置窗口。

(2) 在出现的窗口中按标号顺序进行如下设置:图 2.1删除掉原有的驱动设置(3) 在出现的窗口中按标号顺序进行如下设置:图 2.3 ①单击选 上图中顺序号的说明:择此项选择硬件仿真 F28335 芯片驱动①:在”Family ”下拉菜单中选择“C28XX ” ②:在“Platform ”下拉菜单中选择“ICETEK emulator ” ③: My System ”下出现“F28335 XDS510 Emulator ”②双击此项(3) 在出现的窗口进行如下设置:③单击此项⑤退出保存图 2.2 ④左单击此 项选择软件仿真F28335芯片驱动9 10图2.5 仿真器复位如果窗口中没有出现“按任意键继续…”USB 电缆从仿真器上拔出,返回第(1)步重试。

图2.4 保存退出(4)双击桌面上图标:以上设置完成后,CCS 已经被设置成Emulator 的方式(用仿真器连接硬件板卡的方式),并且指定通过ICETEK-5100USB 仿真器连接ICETEK–F28335-A 评估板。

如果需要一(5)三.启动CCS启动Emulator 方式(1) 检查ICETEK-5100USB 仿真器的黑色JTAG 插头是否正确连接到ICETEK–F28335-A 评估板的J1 插头上。

注:仿真器的插头中有一个孔加入了封针,与J1 插头上的缺针位置应重合,保证不会插错。

(2) 用仿真器附带的USB 信号线连接仿真器和PC 机的USB 插座,注意ICETEK-5100USB 仿真器上指示灯Power 和Run 灯依次点亮。

图2.6(3) 双击桌面上仿真器初始化图标:未连接到28335芯片显示如果出现下面提示窗口(注意红色圈中的信息)下空格键进入下一步操作。

11芯片进行仿真调试。

12第三章实验内容实验一内容一:一.实验目的CCS 调试环境熟悉以及简单程序的软件调试1.了解F28335简单的浮点运算。

2.熟悉浮点运算的编程。

二.实验原理TMS320F28335是一款32 位浮点通用数字信号处理芯片,等特点。

三.实验要求1.设置Code Composer Studio 3.3在硬件仿真方式下运行2.启动Code Composer Studio 3.33.打开工程文件工程文件为:图2.7 设置连接28335芯片E:_F28335_Aex_examples-float_2833xfpu(7)如图2.8 所示,可以确认CCS 软件和28335 芯片连接在一起了。

图2.8 CCS软件和28335芯片连接13_software.pjt打开源程序Example_2833xFPU.c阅读程序,理解程序内容。

4.编译、下载程序。

5.把y1和y2添加到观察窗。

6.运行程序,观察y1和y2结果。

7. 修改x1和x2值,重新执行程序,观察y1和y2结果。

8.退出CCS四.实验结果分析程序设计实现了简单的浮点乘法和加法运算,y1和y2是实验结果。

记录实验结果。

五.问题与思考如何做复杂的浮点运算。

14实验二内容一:指示灯实验一.实验目的数字量输入与数字量输出内容二:拨码开关控制实验一.实验目的1.了解ICETEK–F28335-A评估板在TMS320F28335DSP外部扩展存储空间上的扩展。

1.了解ICETEK–F28335-A评估板在TMS320F28335DSP外部扩展存储空间上的扩展。

2.了解ICETEK–F28335-A评估板上拨码开关扩展原理。

二.实验设备二.实验设备计算机,ICETEK-F28335-A实验箱。

三.实验原理1.TMS320F28335DSP的存储器扩展接口存储器扩展接口是DSP扩展片外资源的主要接口,它提供了一组控制信号和地址、数据线,可以扩展各类存储器和存储器、寄存器映射的外设。

-ICETEK–F28335-A评估板在扩展接口上除了扩展了片外SRAM外,还扩展了指示灯和DIP开关等设备。

具体扩展地址如下:0x180001:板上DIP开关控制寄存器0x180000:板上指示灯控制寄存器2.指示灯扩展原理图指示灯扩展原理 3.1四.实验要求1.编写程序实现将0-F和F-0十六进制代码送到指示灯显示。

2.编写程序实现小灯从左到右循环显示。

3.编写程序实现小灯从右到左循环显示。

15计算机,ICETEK-F28335-A实验箱。