基于32位超标量处理器的保留站设计

- 格式:pdf

- 大小:902.73 KB

- 文档页数:4

1. 系统概述及项目背景ABB IndustrialIT系统是在ABB原有控制系统基础上发展起来的最新的企业自动化解决方案。

该系统融传统的DCS和PLC优点于一体并支持多种国际现场总线标准,尤其适合于水泥行业的应用,目前在水泥行业应用非常广泛。

2001年安徽海螺集团上了2500 t/d 生产线两条,5000 t/d 生产线四条,全部采用ABB AC800F控制系统,3年来运行良好,在此良好合作的基础上2004年又大规模地上了11条5000 t/d和10000 t/d生产线,全部采用了ABB的控制系统,在2005年还将有6条5000 t/d和10000 t/d 生产线采用ABB的控制系统。

本文以池州2×5000 t/d 生产线项目为重点,从技术角度介绍AC800F系统在海螺的成功应用。

2. DCS系统控制网络系统网络分为现场控制层和中央监控层两层网络。

第一层为现场控制层,ABB S800 远程I/O采用Profibus DP通信标准与AC800F控制器进行通信,通讯速率高达12MB/s,距离远达1200米,根据项目要求,有些站距离比较远,采用光纤作为传输介质;在现场采用了部分现场总线仪表,采用ProfiBus PA通信标准与AC800F 控制器进行通信。

第二层为中央监控层,实现各控制器之间及与操作员站、工程师站的通信,采用基于TCP/IP协议的工业以太网。

由于水泥行业的特点,控制器及操作员站位置分散,且距离较远,现场干扰较大,所以通信网络采用了冗余光纤环网结构。

采用赫斯曼导轨安装型光纤集线器通信模件,该集线器提供双冗余供电,双路光纤接口,可以将光缆接成环形,通信模件内置冗余管理功能,当环路任何一处出现故障可以在30ms内自动切换到另外一条备用线路上,同时可以诊测到故障发生位置。

3. DCS过程控制站3.1 DCS控制站特点描述过程控制级包括多个ControlIT控制站,完成各种控制功能,ControlIT控制站由AC800F现场总线型控制器和下挂的S800分布式智能I/O 站组成。

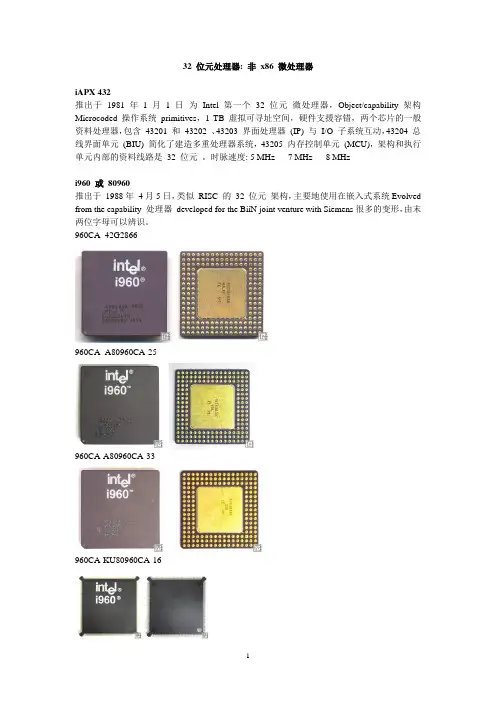

32 位元处理器: 非x86 微处理器iAPX 432推出于1981年1月1日为Intel 第一个32 位元微处理器,Object/capability 架构Microcoded 操作系统primitives,1 TB 虚拟可寻址空间,硬件支援容错,两个芯片的一般资料处理器,包含43201 和43202 、43203 界面处理器(IP) 与I/O 子系统互动,43204 总线界面单元(BIU) 简化了建造多重处理器系统,43205 内存控制单元(MCU),架构和执行单元内部的资料线路是32 位元。

时脉速度: 5 MHz 7 MHz 8 MHzi960 或80960推出于1988年4月5日,类似RISC 的32 位元架构,主要地使用在嵌入式系统Evolved from the capability 处理器developed for the BiiN joint venture with Siemens很多的变形,由末两位字母可以辨识。

960CA -42G2866960CA -A80960CA-25960CA-A80960CA-33960CA-KU80960CA-16960CA-KU80960CA-25960CF-A80960CF-25960CF-KU80960CF-33960FC80960HD66960A80960KA-22960GC80960RN-100960GC80960RS-100960N80960SA16960N80960SA-16960N80960SA20960GC80960RD66960N80960SB16i860 或 80860推出于 1989年 2月27,Intel 的第一个 超标量处理器,RISC 32/64 位元 架构, 管线的特性对于程式设计师而言非常显而易见,使用于 Intel Paragon 巨型平行超级电脑。

A80860XP-50。

Freelance 800F分布式控制系统系统描述术语表过程站:这个术语用于描述AC800F控制器(现场控制器)和机架式控制器。

一个过程站可以设计成冗余配置和非冗余配置。

AC800F:这个术语用于描述AC800F现场控制器这种类型的过程站。

一个冗余的过程站包含了2个AC800F控制器。

机架式过程站:这个术语用于描述机架式类型的过程站。

一个冗余的过程站包含2个机架式CPU。

控制器:这个术语用于描述一个单独的,非冗余的过程站。

目录Freelance 800F:灵活的的过程控制系统页 4系统结构页 6过程级自动化:控制器页 8过程级自动化:远程I/O 页 12过程级自动化:现场设备页 13过程级自动化:Freelance机架式I/O 页 14系统通信页 16操作员级DigiVis软件页 18 Control Builder F组态和调试软件页 28工程与服务页 40 Freelance 800F系统数据页 42ABB4在现代自动化系统投资中,由于硬件设备部分只占用整个系统中较少的成本,则编写工程应用软件的成本就变得越来越重要。

通常来讲,一个自动化项目的工程应用软件费用约占到了整个项目的50%左右,这不难看出,成本结构的迁移给用户创造了优化项目投资的机会,所以,必须从工程编程一开始就要考虑降低费用!这就是我们开发Freelance 800F 系统的目的:保持硬件价格与那些可编程逻辑控制器一致的情况下,通过减少用户工程费用来提高成本效率。

Freelance 800F 过程控制系统如何帮助用户减少工程费用?通过使用一个完整的工程工具(Control Builder F )来配置组态整个控制系统,包括自动化功能、操作员界面显示和记录,以及组态现场总线设备(PROFIBUS ,FOUNDATION Fieldbus ,HART 等等)和设备参数设定。

在过程控制站和操作员站之间自动生成全局的数据通信。

对于现场设备、过程控制站和操作员站,整个控•••制系统采用了一个统一的全局数据库,从而降低了建立数据通信及交互访问的成本和时间投资,并保证整个系统范围内数据的一致性。

基于RISC-V参数化超标量处理器的优化设计

刘有耀;潘宇晨

【期刊名称】《计算机工程与应用》

【年(卷),期】2022(58)5

【摘要】为解决嵌入式领域对处理器不同性能面积的需求,以及对重排序缓冲区阻塞,保留站派遣长短周期指令时导致的吞吐率不平衡及堵塞问题,设计并优化了一种简便配置的参数化流水线超标量处理器。

通过定制化流水线中的分支预测,缓存与运算单元,将RISC-V指令划分5大类处理,对不同周期的执行单元采用级联与并行的混合分布方式,将充当排序缓存中的指令再派遣,达到指令暂存和分类执行的目的,使一条不定周期指令可以携带多条单周期指令提交。

缓存之间以直连方式进行通信,以避免复杂的公共数据总线以降低时序损耗。

实验结果表明,该处理器可以通过配置达到IPC为0.746~1.476之间的性能,平均比同类型处理器IPC提升132.4%。

【总页数】9页(P66-74)

【作者】刘有耀;潘宇晨

【作者单位】西安邮电大学电子工程学院

【正文语种】中文

【中图分类】TP332

【相关文献】

1.基于 MIPS 指令集的超标量和超长指令字混合架构处理器设计

2.基于32位超标量处理器的保留站设计

3.基于RISC-V指令集的超标量处理器设计

4.DMR:兼容

RISC-V架构的乱序超标量通用处理器核5.32位RISC-V处理器中乘法器的优化设计

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的32位整数微处理器的设计与实现冯海涛;王永纲;石江涛;颜天信;王砚方【期刊名称】《小型微型计算机系统》【年(卷),期】2005(26)6【摘要】CPU"软核"可以根据实际应用需要进行剪裁,因而CPU软核设计是SoC 设计实现的重要部分.在FPGA内部设计和调试完全嵌入式的整数微处理器软核,不仅涉及到通常CPU必需的算术逻辑累加器、寄存器堆、指令缓冲、跳转计数、指令集及指令编译等方面的设计实现,还要针对FPGA内部的结构特点对设计进行分析优化,例如流水线结构的选择、关键路径延迟的折衷平衡以及整体调试等.在Virtex1000FG680-4FPGA上设计实现的32位RISC整数微处理器,运行时钟频率可达30MHz,实现150条指令,占用FPGA逻辑资源7%.【总页数】5页(P1113-1117)【作者】冯海涛;王永纲;石江涛;颜天信;王砚方【作者单位】中国科学技术大学,近代物理系,安徽,合肥,230027;中国科学技术大学,近代物理系,安徽,合肥,230027;中国科学技术大学,近代物理系,安徽,合肥,230027;中国科学技术大学,近代物理系,安徽,合肥,230027;中国科学技术大学,近代物理系,安徽,合肥,230027【正文语种】中文【中图分类】TP368.1;TP302.2【相关文献】1.基于FPGA的32位RISC微处理器设计 [J], 刘览;郑步生;施慧彬2.基于FPGA的32位ALU的设计与实现 [J], 孔哲;王伟3.32位RISC微处理器FPGA验证平台设计与实现 [J], 于海;樊晓桠;张盛兵4.基于32位微处理器的液晶显示系统设计与实现 [J], 杜清珍;马超;梁兆宽5.基于FPGA的32位微处理器设计 [J], 归发弟因版权原因,仅展示原文概要,查看原文内容请购买。

第9卷第7期 2010年7月软件导刊Software GuideV01.9No.7 Jul.2010基于32位I ntel CPU的反汇编引擎设计与实现闫培宁1,张戈2,谢状平2(1.河南大学软件学院,河南开封475001;2.河南大学计算机与信.g-工程学院,河南开封475001摘要:通过对Intel IA一32机器指令与中断调试机制等技术的研究,采用动态反汇编技术,设计了基于32位Intel 系列CPU的反汇编引擎.并在此基础上开发动态调试器,以实现应用程序的反汇编与动态调试功能。

关键词:反汇编;动态调试;机器指令;汇编语言中图分类号:TP312文献标识码:A 文章编号:1672—7800(201007-0069-03O 引言反汇编技术在程序优化、数据解密、软件汉化、逆向软件工程和汇编语言教学等领域发挥着重要的作用。

主要是将编译、封装后的应用程序反汇编成为汇编语言代码。

供开发研究人员进行分析优化等。

基于主流的操作系统为32位,且Intel系列及其兼容CPU应用广泛的现状.笔者根据高校在教学科研工作中的实际需要。

采用动态反汇编技术设计了基于32位Intel 系列CPU的反汇编引擎。

并应用此反汇编引擎开发了动态调试器,实现了应用程序的反汇编与动态调试功能.在实际应用和教学过程中起到了良好的作用。

1反汇编引擎概述反汇编引擎主要功能是将可执行的文件中的二进制机器指令经过分析转变为汇编程序。

其分析转变的依据是机器指令格式,也是机器代码和汇编语言格式之间的桥梁。

不同类型的 CPU的指令格式是不同的.本文主要探讨的为常用的Intel系列兼容CPU机器指令格式。

以此为基石设计和开发反汇编引擎。

1.1机器指令Intel机器指令一般分为Intel 64和IA一32,分别是64位指令和32位指令.本文仅讨论32位指令的情况,但其中的很多内容对于intel 64也是同样适用的。

Intel 64及IA一32机器指令格式如图1所示。

(mpc83xx中文翻译,绝对难找)powerpc 第7章 e300处理器内核概述第七章 e300处理器核概述本章概述由原始MPC603e PowerPC微处理器设计派生出的嵌入式e300处理器核的特性。

e300核是PowerPC微处理器系列的一个实现。

在整个文档中,交替使用术语‘e300 核’、‘核’和‘处理器’。

在描述实现特定(implementation-specific)的特性时使用术语e300c1,而在描述属于该处理器系列的特性时使用术语e300。

MPC8349E使用e300c1核。

7.1 概述本节介绍e300核的详细信息,提供显示其主要功能单元的结构图(见e300 PowerPC核参考手册的字节序模式和字节顺序一章),并简要介绍这些单元是如何交互的。

说明e300核与源自MPC603e处理器的先前PowerPC实现的所有不同之处。

更多信息请参见e300 PowerPC核参考手册。

e300核是该精简指令集计算(RISC)微处理器系列中的一个低功耗实现。

该核实现了PowerPC系统结构的32位部分,该部分定义了32位有效地址,8、16和32位整型数据类型,以及32和64位浮点数据类型。

e300核是一个超标量处理器,它每个时钟可以发出和撤回多达3条指令。

指令可以不按程序顺序执行,以提高性能,但该核使指令的执行看起来象顺序执行一样。

e300c1核集成了5个执行单元:整数单元(IU integer unit)、浮点数单元(FPU floating-point unit)、转移处理单元(BPU branch processingunit)、取/存单元(LSU load/store unit)和系统寄存器单元(SRU system register unit)。

并行执行5条指令的能力和具有快速执行时间的简单指令的使用使基于e300核的系统具有很高的效率和吞吐率。

绝大多数整型指令在一个时钟周期内执行完成。

32位RISC中存储管理单元的设计李瑛;高德远;张盛兵;樊晓桠【期刊名称】《西北工业大学学报》【年(卷),期】2004(022)003【摘要】多任务处理要求在处理器中集成片上的存储管理单元(MMU),支持虚拟存储管理,通过硬件MMU把虚地址转换成物理地址.提出了32位超标量RISC微处理器的MMU体系结构,论述了逻辑地址到物理地址转换的3种机制以及相应的存储保护和异常处理;着重讨论TLB(Translation Lookaside Buffer)的设计原则,并对其3种设计结构进行分析比较,优化了TLB的组织结构;给出了MMU的组成、数据通路、控制通路,解决了速度瓶颈,满足了芯片的设计要求.整个芯片用TSMC 0.25 μm工艺实现,芯片面积为5 mm×5 mm,主频为66 MHz.【总页数】5页(P365-369)【作者】李瑛;高德远;张盛兵;樊晓桠【作者单位】西北工业大学,航空微电子中心,陕西,西安,710072;西北工业大学,航空微电子中心,陕西,西安,710072;西北工业大学,航空微电子中心,陕西,西安,710072;西北工业大学,航空微电子中心,陕西,西安,710072【正文语种】中文【中图分类】TP303【相关文献】1.32位RISC处理器中系统控制协处理器的设计与实现 [J], 李奕磊;李东生;李军强2.32位微处理器中存储管理单元的全定制设计 [J], 张志峰3.SPARC V8处理器中存储管理单元的设计 [J], 肖建青;李红桥;张洵颖;龚龙庆4.瑞萨科技发布用于车辆变频控制的带有256B片上快闪存储器的SH7147F 32位RISC微控制器 [J],5.32位RISC处理器中可配置乘法器的设计 [J], 李云;张盛兵因版权原因,仅展示原文概要,查看原文内容请购买。

一种32位双核微处理器的设计与监控章鸣嬛;叶有祥【期刊名称】《微计算机信息》【年(卷),期】2012(000)010【摘要】This paper achieves a 32 dual-core microprocessor system, namely the "ARM CPU" which using the experimental platform ARM9 and "experimental CPU" using pragrammable resource FPGA respectively. We have study on this system about its working mode and system structure, monitoring the working state of "experimental CPU" through "ARM CPU",using serial interface to send the instructions to complete the single-step or continuous operation, and to complete stop operation; transfering the instruction file and modifying memory etc. The results show, as the system has a faster system clock, it can complete a instruction cycle approxi- mately only 0.01 seconds;have high workin~ efficiency, and can have a real-time rabid treatment on si~,nal inducin~ from nutside.%论文实现了一个32位的双核微处理器系统,分别为ARM9实验平台上的32位“ARMCPU”和利用FPGA资源实现的32位“实验CPU”.并对该双核系统的工作方式及体系结构进行了研究。

基于32位Intel CPU的反汇编引擎设计与实现

闫培宁;张戈;谢状平

【期刊名称】《软件导刊》

【年(卷),期】2010(000)007

【摘要】通过对Intel IA-32机器指令与中断调试机制等技术的研究,采用动态反汇编技术,设计了基于32位Intel系列CPU的反汇编引擎,并在此基础上开发动态调试器,以实现应用程序的反汇编与动态调试功能。

【总页数】3页(P69-71)

【作者】闫培宁;张戈;谢状平

【作者单位】

【正文语种】中文

【中图分类】TP312

【相关文献】

1.32位嵌入式CPU中系统控制协处理器的设计与实现 [J], 金钊

2.32位高性能嵌入式CPU中Load Aligner 模块的设计与实现 [J], 张书;王颖;林正浩

3.基于32位Intel CPU的反汇编引擎设计与实现 [J], 闫培宁;张戈;谢状平

4.基于VB引擎反汇编技术的软件破解方法及防范策略 [J], 周显春

5.专用于Intel PXA210和PXA250微处理器的更小巧、完备的电源管理IC—为基于Intel XScale^TM微架构的CPU提供完备的电源方案 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。