一位全减器

- 格式:doc

- 大小:177.00 KB

- 文档页数:2

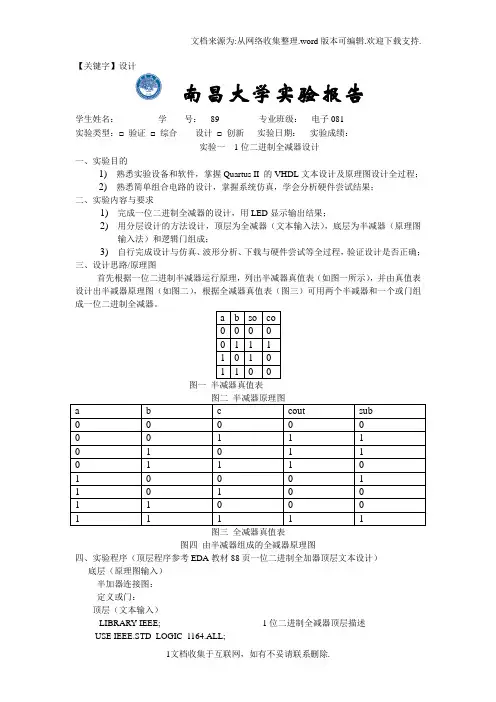

【关键字】设计南昌大学实验报告学生姓名:学号:89 专业班级:电子081实验类型:□ 验证□ 综合设计□ 创新实验日期:实验成绩:实验一1位二进制全减器设计一、实验目的1)熟悉实验设备和软件,掌握Quartus II 的VHDL文本设计及原理图设计全过程;2)熟悉简单组合电路的设计,掌握系统仿真,学会分析硬件尝试结果;二、实验内容与要求1)完成一位二进制全减器的设计,用LED显示输出结果;2)用分层设计的方法设计,顶层为全减器(文本输入法),底层为半减器(原理图输入法)和逻辑门组成;3)自行完成设计与仿真、波形分析、下载与硬件尝试等全过程,验证设计是否正确;三、设计思路/原理图首先根据一位二进制半减器运行原理,列出半减器真值表(如图一所示),并由真值表设计出半减器原理图(如图二),根据全减器真值表(图三)可用两个半减器和一个或门组成一位二进制全减器。

a b so co0 0 0 00 1 1 11 0 1 01 1 0 0图一半减器真值表a b c cout sub0 0 0 0 00 0 1 1 10 1 0 1 10 1 1 1 01 0 0 0 11 0 1 0 01 1 0 0 01 1 1 1 1图三全减器真值表图四由半减器组成的全减器原理图四、实验程序(顶层程序参考EDA教材88页一位二进制全加器顶层文本设计)底层(原理图输入)半加器连接图:定义或门:顶层(文本输入)LIBRARY IEEE; --1位二进制全减器顶层描述USE IEEE.STD_LOGIC_1164.ALL;ENTITY f_m IS --定义f_m实体PORT (ain,bin,cin :IN STD_LOGIC;cout,sub:OUT STD_LOGIC);END ENTITY f_m;ARCHITECTURE one OF f_m IS --描述结构体COMPONENT h_m --定义h_m各引脚PORT ( a,b : IN STD_LOGIC ;co,so : OUT STD_LOGIC) ;END COMPONENT ;COMPONENT or2a --定义or2a各引脚PORT (a,b : IN STD_LOGIC;c : OUT STD_LOGIC) ;END COMPONENT ;SIGNAL d,e,f : STD_LOGIC ; --定义信号d,e,f的类型BEGIN --描述底层各元件的连接u1 : h_m PORT MAP (a=>ain, b=>bin, co=>d, so=>e) ;u2 : h_m PORT MAP (a=>e, b=>cin, co=>f, so=>sub);u3 : or2a PORT MAP (a=>d, b=>f, c=>cout);END ARCHITECTURE one ; --结束结构体描述五、实验步骤1.建立工作库文件夹和编辑设计文件1)在D盘新建立一个文件夹命名为f_m,选择ACEX1K芯片,保存下面的工程文件;2)打开quartus II,选择菜单File→New→Block diagram/schematic file,点击OK,输入半减器原理图,保存为h_m.bdf并选择菜单file→create/update→createVHDL component declaration files for current file2.选择菜单File→New→Block diagram/schematic file,点击OK,定义或门,保存为or2a.bdf并选择菜单file→create/update→create VHDL component declarati on filesfor current file3.选择菜单File→New→VHDL file,点击OK后在打开的界面下输入已设计的程序,保存为f_m.vhd;4.对f_m.vhd进行编译5.创建仿真文件f_m.vwf,将所有引脚拉入仿真文件,设定end time以及ain,bin,cin输入值,进行仿真6.选择assignments→pins 设置各引脚,并编译;7.下载程序,验证实验结果;六、仿真波形分析下图为实验所得的波形图:a b c d e f g h i区间ain bin cin cout sub LED6 LED5 a-b 0 0 0 0 0 灭灭b-c 0 0 1 1 1 亮亮c-d 0 1 0 1 1 亮亮d-e 0 1 1 1 0 亮灭e-f 1 0 0 0 1 灭亮f-g 1 0 1 0 0 灭灭g-h 1 1 0 0 0 灭灭h-i 1 1 1 1 1 亮亮借位情况,cout为本位输出,sub为向上借位的值,由上表可知,仿真结果与理论值(全减器真值表)一致,故仿真成功。

实验一 1位二进制全减器设计一、实验目的1.熟悉Quartes II集成开发软件的使用;2.初步熟悉PH-1V型实验装置的使用;3 . 学习用原理图输入法和文本输入法进行简单的数字电路设计,掌握系统仿真,学会分析硬件测试结果。

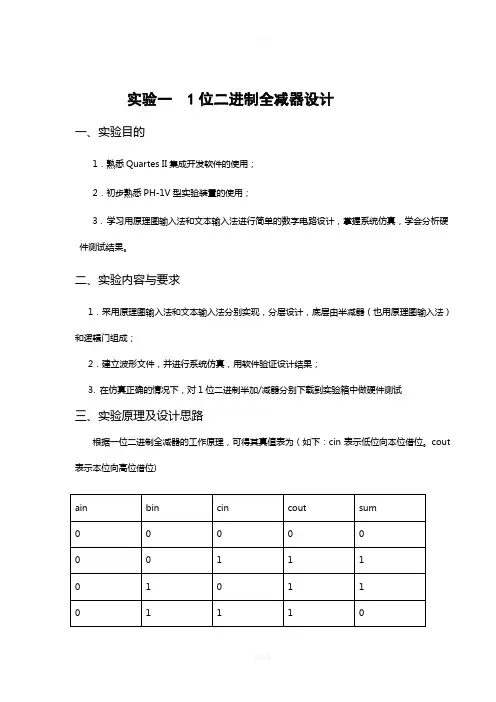

二、实验内容与要求1.采用原理图输入法和文本输入法分别实现,分层设计,底层由半减器(也用原理图输入法)和逻辑门组成;2.建立波形文件,并进行系统仿真,用软件验证设计结果;3. 在仿真正确的情况下,对1位二进制半加/减器分别下载到实验箱中做硬件测试三、实验原理及设计思路根据一位二进制全减器的工作原理,可得其真值表为(如下:cin表示低位向本位借位。

cout 表示本位向高位借位)由EDA教程中全加器的顶层设计描述及半加器调用可类比到全减器的设计,可由先对半减器进行描述,然后进行两次调用。

半减器的工作时的逻辑表达式为:so=a XOR b ;co=(NOT a)AND b 四、实验程序(程序来源:EDA技术实验教程)LIBRARY IEEE ; ——或门逻辑描述USE IEEE.STD_LOGIC_1164.ALL;ENTITY or2a ISPORT (a, b :IN STD_LOGIC;c : OUT STD_LOGIC );END ENTITY or2a;ARCHITECTURE one OF or2a ISBEGINc <= a OR b ;END ARCHITECTURE one;LIBRARY IEEE; ——半减器描述USE IEEE.STD_LOGIC_1164.ALL;ENTITY h_suber ISPORT (a, b : IN STD_LOGIC;co, so : OUT STD_LOGIC);END ENTITY h_suber;ARCHITECTURE fh1 OF h_suber isBEGINso <= a xor b ;co <= (not a )AND b ;END ARCHITECTURE fh1;LIBRARY IEEE; ——1位二进制全减器顶层设计描述USE IEEE.STD_LOGIC_1164.ALL;ENTITY f_suber ISPORT (ain,bin,cin : IN STD_LOGIC;cout,sum : OUT STD_LOGIC );END ENTITY f_suber;ARCHITECTURE fd1 OF f_suber ISCOMPONENT h_suber ——调用半减器声明语句PORT ( a,b : IN STD_LOGIC;co,so : OUT STD_LOGIC);END COMPONENT ;COMPONENT or2a ——调用或门声明语句PORT (a,b : IN STD_LOGIC;c : OUT STD_LOGIC);END COMPONENT;SIGNAL d,e,f : STD_LOGIC; ——定义3个信号作为内部的连接线BEGINu1 : h_suber PORT MAP(a=>ain,b=>bin,co=>d,so=>e); ——例化语句u2 : h_suber PORT MAP(a=>e, b=>cin,co=>f,so=>sum);u3 : or2a PORT MAP(a=>d, b=>f,c=>cout);END ARCHITECTURE fd1 ;五、实验步骤:1.打开Quartes II软件,建立工程文件,注意工程名要与实体名一致:2、打开QuartusII,选择菜单File->New->VHDL.File,建立vhdl文件,将以上程序输入并进行编译;3、建立波形文件,并进行系统仿真,注意设置仿真结束时间以及添加结点;4、输入信号波形Tools->Options->Waveform Editor,进行功能仿真Tools->Simulator Tools,在Simulator Mode选择Functional,仿真表生成后点击Start开始仿真,完成后点击Report结果如下图所示;5、引脚锁定,及设置流程对各管脚进行分配,将ain分配给53,bin分配给54,cin分配给55。

一位全减器课程设计一、课程目标知识目标:1. 学生能理解全减器的基本原理,掌握全减器的电路组成和功能。

2. 学生能运用所学知识,分析全减器的逻辑功能,解释全减器在实际电路中的应用。

3. 学生了解全减器与其他逻辑门的关系,能正确区分全减器与半减器的区别。

技能目标:1. 学生能运用所学知识,设计简单的全减器电路,并进行模拟验证。

2. 学生能通过实际操作,分析全减器电路的故障现象,并提出解决方案。

3. 学生具备一定的电路图识别能力,能读懂并绘制全减器电路图。

情感态度价值观目标:1. 培养学生对电子电路的兴趣,激发他们探索电子世界的热情。

2. 培养学生的团队协作精神,使他们学会在小组合作中共同解决问题。

3. 培养学生具备良好的学习习惯,树立严谨的科学态度,提高他们的自主学习能力。

课程性质:本课程为电子技术基础课程,以理论教学与实践操作相结合的方式进行。

学生特点:学生具备一定的电子技术基础知识,对全减器有一定了解,但对实际应用和电路设计尚不熟练。

教学要求:结合学生特点,注重理论与实践相结合,注重培养学生的动手操作能力和创新能力。

在教学过程中,关注学生的个体差异,因材施教,使学生在掌握全减器知识的基础上,提高综合运用能力。

通过具体的学习成果,对学生的学习效果进行评估,确保课程目标的达成。

二、教学内容1. 全减器的基本原理:包括全减器的定义、作用及其在数字电路中的应用。

- 教材章节:第三章第三节《全减器与加法器》- 内容:全减器的工作原理、逻辑表达式、真值表。

2. 全减器的电路组成:分析全减器电路的各个部分,探讨其功能及相互关系。

- 教材章节:第三章第四节《全减器电路的设计》- 内容:全减器电路的组成部分,如输入端、输出端、借位端等。

3. 全减器与其他逻辑门的关系:介绍全减器与半减器、与非门等逻辑门的联系与区别。

- 教材章节:第三章第五节《各类逻辑门的特性与应用》- 内容:全减器与其他逻辑门的功能对比,应用场景。

1、用3线—8线译码器74LS138和门电路设计1位二进制全减器,输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号(74LS138的逻辑框图如图1.1所示)。

CO---向高位的借位; Y---两位数之差;C I ---来自低位的借位;

故:

Y=m 1+m 2+m 4+m 7;CO=m 3+m 5+m 6+m 7; 其逻辑图如下:

Y

2、试用8选1数据选择器74LS152和必要的门电路设计一个路灯控制电路,要求在四个不同的地方都能独立地开灯和关灯,画出逻辑电路图(74LS152的逻辑框图如图2.1所示)。

i i i m D A A A D A A A D Y ∑

==++⋅⋅=7001270120 图2.1 74LS152的逻辑框图

D3

D2D1

D0

Y A0A1

A2

D7

D6D5D4

74L S 152

m m m

m

其中A3,A2,A1,A0分别代表四个不同的地方;Y代表灯;1代表亮,或是开关闭合;0代表灯灭;

Y=A3(m1+m2+m4+m0)

对照着所给的逻辑表达式可得:

D0=D1=D2=D4=A3

D3=D5=D6=D7=0; A2=A2;A1=A1;A0=A0;

故逻辑图如下所示:

A3

Y

1。

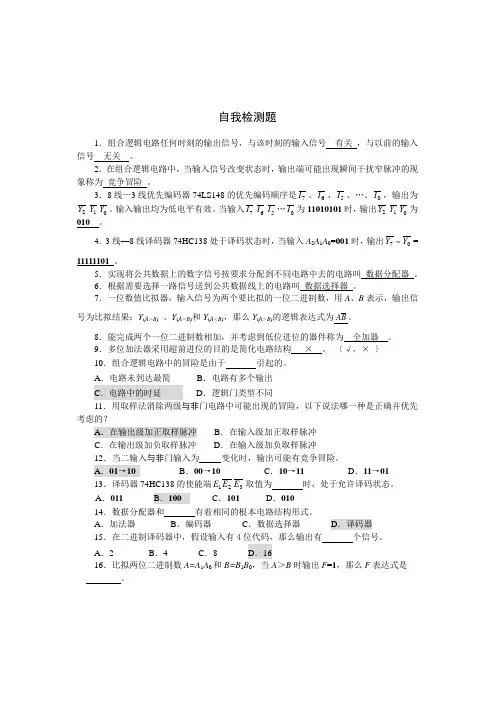

自我检测题1.组合逻辑电路任何时刻的输出信号,与该时刻的输入信号 有关 ,与以前的输入信号 无关 。

2.在组合逻辑电路中,当输入信号改变状态时,输出端可能出现瞬间干扰窄脉冲的现象称为 竞争冒险 。

3.8线—3线优先编码器74LS148的优先编码顺序是7I 、6I 、5I 、…、0I ,输出为2Y 1Y 0Y 。

输入输出均为低电平有效。

当输入7I 6I 5I …0I 为时,输出2Y 1Y 0Y 为 010 。

4.3线—8线译码器74HC138处于译码状态时,当输入A 2A 1A 0=001时,输出07Y ~Y = 。

5.实现将公共数据上的数字信号按要求分配到不同电路中去的电路叫 数据分配器 。

6.根据需要选择一路信号送到公共数据线上的电路叫 数据选择器 。

7.一位数值比较器,输入信号为两个要比较的一位二进制数,用A 、B 表示,输出信号为比较结果:Y (A >B ) 、Y (A =B )和Y (A <B ),则Y (A >B )的逻辑表达式为B A 。

8.能完成两个一位二进制数相加,并考虑到低位进位的器件称为 全加器 。

9.多位加法器采用超前进位的目的是简化电路结构 × 。

(√,× ) 10.组合逻辑电路中的冒险是由于 引起的。

A .电路未达到最简 B .电路有多个输出 C .电路中的时延 D .逻辑门类型不同11.用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并优先考虑的A .在输出级加正取样脉冲B .在输入级加正取样脉冲C .在输出级加负取样脉冲D .在输入级加负取样脉冲 12.当二输入与非门输入为 变化时,输出可能有竞争冒险。

A .01→10B .00→10C .10→11D .11→01 13.译码器74HC138的使能端321E E E 取值为 时,处于允许译码状态。

A .011 B .100 C .101 D .010 14.数据分配器和 有着相同的基本电路结构形式。

全减器原理全减器是数字电路中常见的逻辑门电路,它用于实现两个二进制数的减法运算。

在数字电路中,全减器通常由几个半加器和一个附加的输入引脚组成,用来处理借位。

在本文中,我们将详细介绍全减器的原理和工作方式。

首先,我们来看一下全减器的基本结构。

全减器通常由三个输入引脚和两个输出引脚组成,分别是被减数A、减数B、借位输入Borrow In、差值输出Difference和借位输出Borrow Out。

全减器的原理是通过对被减数和减数进行异或运算来得到差值,同时通过对被减数、减数和借位输入进行与非运算来得到借位输出。

这样,我们就可以实现两个二进制数的减法运算。

接下来,我们来详细介绍全减器的工作原理。

首先,被减数A和减数B的每一位都分别与对应的减数B和借位输入进行异或运算,得到差值和借位输出。

然后,将这些差值和借位输出通过半加器进行处理,得到最终的差值和借位输出。

通过这样的过程,我们就可以实现两个二进制数的减法运算。

在实际应用中,全减器常常被用于数字电路中,例如在计算机的算术逻辑单元(ALU)中。

在ALU中,全减器用来处理减法运算,从而实现计算机的加减法功能。

此外,全减器还可以被用于其他数字系统中,例如在数字信号处理器(DSP)和通信系统中。

总的来说,全减器是数字电路中非常重要的逻辑门电路,它可以实现两个二进制数的减法运算。

通过对被减数和减数进行异或和与非运算,全减器可以得到差值和借位输出,从而实现减法运算。

在实际应用中,全减器被广泛应用于数字电路和计算机系统中,发挥着重要的作用。

以上就是关于全减器原理的详细介绍,希望能够对大家有所帮助。

如果对全减器原理还有疑问或者需要进一步了解,欢迎继续阅读相关资料或者咨询专业人士。

-.自我检测题1.组合逻辑电路任何时刻的输出信号,与该时刻的输入信号 有关 ,与以前的输入信号 无关 。

2.在组合逻辑电路中,当输入信号改变状态时,输出端可能出现瞬间干扰窄脉冲的现象称为 竞争冒险 。

3.8线—3线优先编码器74LS148的优先编码顺序是7I 、6I 、5I 、…、0I ,输出为2Y 1Y 0Y 。

输入输出均为低电平有效。

当输入7I 6I 5I …0I 为11010101时,输出2Y 1Y 0Y 为 010 。

4.3线—8线译码器74HC138处于译码状态时,当输入A 2A 1A 0=001时,输出07Y ~Y = 11111101 。

5.实现将公共数据上的数字信号按要求分配到不同电路中去的电路叫 数据分配器 。

6.根据需要选择一路信号送到公共数据线上的电路叫 数据选择器 。

7.一位数值比拟器,输入信号为两个要比拟的一位二进制数,用A 、B 表示,输出信号为比拟结果:Y (A >B ) 、Y (A =B )和Y (A <B ),那么Y (A >B )的逻辑表达式为B A 。

8.能完成两个一位二进制数相加,并考虑到低位进位的器件称为 全加器 。

9.多位加法器采用超前进位的目的是简化电路构造 × 。

〔√,× 〕 10.组合逻辑电路中的冒险是由于 引起的。

A .电路未到达最简 B .电路有多个输出C .电路中的时延D .逻辑门类型不同11.用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并优先考虑的?A .在输出级加正取样脉冲B .在输入级加正取样脉冲C .在输出级加负取样脉冲D .在输入级加负取样脉冲12.当二输入与非门输入为 变化时,输出可能有竞争冒险。

A .01→10B .00→10C .10→11D .11→0113.译码器74HC138的使能端321E E E 取值为 时,处于允许译码状态。

A .011 B .100 C .101 D .01014.数据分配器和 有着一样的根本电路构造形式。

实验一1位二进制全减器设计一、实验目的1.熟悉QUarteS II集成开发软件的使用;2.初步熟悉PH-1V型实验装置的使用:3.学习用原理图输入法和文本输入法进行简单的数字电路设讣,掌握系统仿真,学会分析硬件测试结果。

二、实验内容与要求1.采用原理图输入法和文本输入法分别实现,分层设计,底层由半减器(也用原理图输入法)和逻辑门组成:2.建立波形文件,并进行系统仿真,用软件验证设计结果;3.在仿真正确的情况下,对1位二进制半加/减器分别下载到实验箱中做硬件测试三、实验原理及设计思路根据一位二进制全减器的工作原理,可得苴真值表为(如下:Cin表示低位向本位借位。

COUt 表示本位向高位借位)由EDA教程中全加器的顶层设计描述及半加器调用可类比到全减器的设汁,可由先对半减器进行描述,然后进行两次调用。

半减器的工作时的逻辑表达式为:SO二a XOR b : CO= (NOT a)AND b四、实验程序(程序来源:EDA技术实验教程)LIBRARY IEEE ; ——或门逻辑描述USE IEEE. STD_LOGlC_1164. ALL;ENTlTY or2a ISPORT (a, b :IN STD_LOGIC;C : OUT STD_LOGIC );END ENinY or2a;ARCHITECTURE One OF or2a ISBEGlNc <= a OR b ;END ARCHITECTURE one;LiBRARY IEEE; ——半减器描述USE IEEE. STD_LOGIC_1164・ ALL;ENTITY h.suber ISPORT (a, b : IN STD.LOGIC;co, So : OUT STD.LOGIC);END ENTITY h_suber;ARCHlTECTURE fhl OF h.suber isBEGINSO <= a XOr b ;CO <= (not a )AND b ;END ARCHliECTURE fhl;LIBR,⅛RY IEEE; —1位二进制全减器顶层设计描述USE IEEE・STD_LOGIC_1164・ALL;ENTITY f.suber ISPORT (ain,bin,cin : IN STD.LOGIC; COUt t SUm : OUT STD-LOGlC ); END ENTITY f.suber;ARCHITECTURE fdl OF f.suber ISCON(PONENT h.suber ——调用半减器声明语句PORi ( a,b : IN STD.LOGIC;co, So : OUT STD.LOGIC);END COMPONENT ;COMPoNENT or2a ——调用或门声明语句PORT Qb : IN STD.LOGIC;C : OUT STD—LOGIC);END COMPONENT;SlGNAL d,e,f : STD.LOGIC;——泄义3个信号作为内部的连接线BEGlN UI : h-suber PORT NfAP(a=>ain, b=>bin, co=>d, so=>e); 例化语句u2 : h-suber PORT N(AP(a=>e, b=>cin, co=>f, so=>sum);u3 : or2a PORi MAP(a=>d, b=>f, c=>cout);END ARCHITECTURE fdl ;五、实验步骤:1•打开QUatteS II软件•建立工程文件,注意工程名要与实体名一致:T«t.41 n<r ∣Φrγ titsTyPe KeεsaσeInfo: Lonacot ∏>d froa source PLn ,,om r, to dcatmatiDn Pin Info: OIlartU 5 II Clocyic TIDIna AnOlTZCtr σas 5uccc3s541 ・ 0Info: OUatrtU 5 II FuLI ConPiLfttIon v05 □ucce35fu 1・ O CrrOt :3,∖ SyClem (2∣ APmCUJSring (39) /CIiliZ^ ∖√a1πr>3X⅜,∣ *∣[L θs⅛m3 Lmg I For Kttlp, press FLIlrW PrCJjrci ViXar <1: Di rrct <>ry # HABrTop LrVr 1 Ent 1 ∙ γ IpMg. . . ×2、打开QUartUSII,选择菜单File->New->VHDL. F 订e,建立VhdI 文件,将以上程序输入并进行编译:©0H 卧H≡3幣肆癒鄴SS^^SB*仔5[Co...二叵区≡SJ ∏CD (⅛& 电73C S ► ¾Φ∣> ∣⅜∣^》OYiAqo* ⅛⅛∙ 5Clιr -nts 讥 V l ^ I ∣]0∣> 巧 W 0 応Ta⅛sFLo* ICO(IPiI a aH g √* S ► Co(IPlI « Ue≡ιcn V ⅜*∙ ► λiι*lyςiς <<ripιlαtt4n Λ4pψrt ⅛ LCg«1 HOti c<号 Γl⅛⅜∙ Sxnn^ry申Flo” S⅛ttiΛg≡rlewSmnrT √* E- ► X:tter √* ⅛- ► ClaSSIC ' S-∙ A IDA Natl: ®PrQcrS IleVi∏w Status QuarLus II V^SJOn JJ⅛vi Ki an W∙Λ*Dp-l<v<l ≡κtd ty Hsu anily e*i ceiniπg NodcISCt tinig reau2rer ∣<nt≡ OtaI IOCJC el*nenls aIftl PinK"sub" 1 errors r __ C ∣ σarr v EllOl XSLPl⅛÷D I —Ide3、建立波形文件,并进行系统仿真,注意设置仿真结束时间以及添加结点;⅛*8r =:3g7q5rn亠・ PoirrecS-n φ=∖≡Γ∙7∙35 盘Staitp t∙u e 久7∙LOEC15Qm7 ∙45 P U4"B >e ct 篙潼 TOOlS I 〉OPtiOnS I 〉WaVefOrln EdiCo r ∙ j (⅛f f⅛n k ^w TOOIS I 〉SimUlatOrTOOls∙* SinlUlatOrMOde ⅛¾5FUnCtiOnai ・SF ⅛t ^H÷¾ΠΓl ^⅛S tart⅛^e M ∙s⅛^ΠΓl !DT E ⅛∙R e p o5、引脚锁定,及设置流程对各管脚进行分配,将Ain 分配给53, bin 分配给54, Cin 分配给55。

自我检测题1.组合逻辑电路任何时刻的输出信号,与该时刻的输入信号 有关 ,与以前的输入信号 无关 。

2.在组合逻辑电路中,当输入信号改变状态时,输出端可能出现瞬间干扰窄脉冲的现象称为 竞争冒险 。

3.8线—3线优先编码器74LS148的优先编码顺序是7I 、6I 、5I 、…、0I ,输出为2Y 1Y 0Y 。

输入输出均为低电平有效。

当输入7I 6I 5I …0I 为11010101时,输出2Y 1Y 0Y 为 010 。

4.3线—8线译码器74HC138处于译码状态时,当输入A 2A 1A 0=001时,输出07Y ~Y = 11111101 。

5.实现将公共数据上的数字信号按要求分配到不同电路中去的电路叫 数据分配器 。

6.根据需要选择一路信号送到公共数据线上的电路叫 数据选择器 。

7.一位数值比拟器,输入信号为两个要比拟的一位二进制数,用A 、B 表示,输出信号为比拟结果:Y (A >B ) 、Y (A =B )和Y (A <B ),那么Y (A >B )的逻辑表达式为B A 。

8.能完成两个一位二进制数相加,并考虑到低位进位的器件称为 全加器 。

9.多位加法器采用超前进位的目的是简化电路结构 × 。

〔√,× 〕 10.组合逻辑电路中的冒险是由于 引起的。

A .电路未到达最简 B .电路有多个输出C .电路中的时延D .逻辑门类型不同11.用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并优先考虑的?A .在输出级加正取样脉冲B .在输入级加正取样脉冲C .在输出级加负取样脉冲D .在输入级加负取样脉冲12.当二输入与非门输入为 变化时,输出可能有竞争冒险。

A .01→10B .00→10C .10→11D .11→0113.译码器74HC138的使能端321E E E 取值为 时,处于允许译码状态。

A .011 B .100 C .101 D .01014.数据分配器和 有着相同的根本电路结构形式。

自我检测题1.组合逻辑电路任何时刻的输出信号,与该时刻的输入信号 有关 ,与以前的输入信号 无关 。

2.在组合逻辑电路中,当输入信号改变状态时,输出端可能出现瞬间干扰窄脉冲的现象称为 竞争冒险 。

3.8线—3线优先编码器74LS148的优先编码顺序是7I 、6I 、5I 、…、0I ,输出为2Y 1Y 0Y 。

输入输出均为低电平有效。

当输入7I 6I 5I …0I 为时,输出2Y 1Y 0Y 为 010 。

4.3线—8线译码器74HC138处于译码状态时,当输入A 2A 1A 0=001时,输出07Y ~Y = 。

5.实现将公共数据上的数字信号按要求分配到不同电路中去的电路叫 数据分配器 。

6.根据需要选择一路信号送到公共数据线上的电路叫 数据选择器 。

7.一位数值比较器,输入信号为两个要比较的一位二进制数,用A 、B 表示,输出信号为比较结果:Y (A >B ) 、Y (A =B )和Y (A <B ),则Y (A >B )的逻辑表达式为B A 。

8.能完成两个一位二进制数相加,并考虑到低位进位的器件称为 全加器 。

9.多位加法器采用超前进位的目的是简化电路结构 × 。

(√,× ) 10.组合逻辑电路中的冒险是由于 引起的。

A .电路未达到最简 B .电路有多个输出 C .电路中的时延 D .逻辑门类型不同11.用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并优先考虑的?A .在输出级加正取样脉冲B .在输入级加正取样脉冲C .在输出级加负取样脉冲D .在输入级加负取样脉冲 12.当二输入与非门输入为 变化时,输出可能有竞争冒险。

A .01→10B .00→10C .10→11D .11→01 13.译码器74HC138的使能端321E E E 取值为 时,处于允许译码状态。

A .011 B .100 C .101 D .010 14.数据分配器和 有着相同的基本电路结构形式。

实验四 全减器一、实验目的设计并实现一个一位减法器 二、实验原理半减器不考虑低位向本位的借位。

一位半减器由两个输入、两个输出。

表1 半减器真值表输入 输出 Bi Ai Di Ci 0 0 0 0 0 1 1 1 1 0 1 0 11由真值表可得到函数表达式:Bi Ai Bi Ai Di += Bi Ai Ci =在下图中,“进位入”Ci -1是指低位的进位输出,“进位出”Ci 即是本位的进位输出。

Ai Bi A BCDDi CiC D 半减器半减器≥Ci-1原理图如下:全减器(被减数)Ai(减数)Bi(差)Di (借位出)Ci真值表:输入输出Ci-1Bi Ai Si Ci 0000000000000000000011111111111111111111根据真值表写出逻辑表达式:111i i i i i i i i i i D A B C A B C A B C ---=++三、实验步骤1、建立工程fullsub,新建VHDL 文件输入以下代码保存为fullsub1.vhdl 。

打开addern.vhdl 文件,选择File → Creat/Update → Creat Symbol Files for Current Files 生成顶层符号文件。

(参考实验一、二)----------------------半减器程序 library ieee;use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity halfsub is port(a,b:in std_logic; d,c:out std_logic); end halfsub;architecture half1 of halfsub is begind<=((a and (not b))or ((not a)and b)); c<=(not a)and b; end half1;-----------------------------------全减器程序 library ieee;use ieee.std_logic_1164.all; entity fullsub1 isport(ai,bi,ci:in std_logic; di,co:out std_logic); end fullsub1;architecture full1 of fullsub1 iscomponent halfsub-----------声明半减器调用 port(a,b:in std_logic;d,c:out std_logic); end component;signal halfsub1_d,halfsub1_c,halfsub2_c:std_logic;begin----------------------------------------------------------调用半减器 halfsub1:halfsub port map (ai,bi,halfsub1_d,halfsub1_c); halfsub2:halfsub port map (halfsub1_d,ci,di,halfsub2_c); co<=(halfsub1_c or ci); end full1;2、新建一个Block Diagramm/Schematic File 原理图文件,,在空白处双击添加生成的顶层原理图,并连接input 、output (输入输出管脚)重命名后如图所示,保存文件fullsub.bdf 。

实验一 1位二进制全减器设计一、实验目的1. 熟悉EDA 技术开发流程;2. 熟悉Quartes II 集成开发软件的使用;3. 学习用原理图输入法和文本输入法进行简单设计;4. 熟悉简单组合电路设计,掌握系统仿真,学会分析硬件测试结果;5. 初步熟悉EDA 实验装置的使用。

二、实验内容与要求1.完成全减器的设计:分别使用原理图输入法和文本输入法设计一位二进制全减器,用分层设计方法,顶层为全减器,底层由半减器(也用原理图输入法)和逻辑门组成;2.进行波形仿真,并分析仿真波形图;3.下载测试减法器是否正确。

三、设计思路/原理图由课本P79:1位二进制全加器的设计可以仿照出1位二进制全减器的设计。

实验框图如真值表画出卡诺图并化简可得: Ca=M N ;Re=(M N)+(M ·N)。

选择相应组合逻辑器件可以构成半减器和全减器。

四、 实验程序:按照实验要求:底层半减器用原理图输入法,顶层为全减器,可知只需写出全减器和或门程序如下:(1)全减器程序:library ieee; --1位二进制全减器顶层设计描述 use ieee.std_logic_1164.all; entity f_suber isport (min, nin, lin : in std_logic; --减数、被减数和低位来的借位 cary, sub : out std_logic); --进位和结果end entity f_suber;architecture fs1 of f_suber iscomponent h_suber--对要调用的元件h_suber的界面端口进行定义port ( m, n: in std_logic;ca, re: out std_logic);end component;component or2a --对要调用的元件or2a的界面端口进行定义port (a, b: in std_logic;c:out std_logic);end component;signal g, h, y: std_logic;begins1 : h_suber port map (m=>min, n=>nin, ca=>g, re=>h);--例化一个1位二进制半减器s2 : h_suber port map (m=>h, n=>lin, ca=>y, re=>sub);--例化一个1位二进制半减器s3 : or2a port map (a=>g, b=>y, c=>cary); --例化一个或门end architecture fs1;(2)或门程序:library ieee;use ieee.std_logic_1164.all;entity or2a isport (a,b :in std_logic;c :out std_logic);end entity or2a;architecture one of or2a isbeginc<=a or b;end architecture one;五、实验步骤1.用原理图输入法设计半减器(1)打开Quartus II软件,进入编辑环境。

实验六 数据选择器及应用一、实验目的1、掌握数据选择器的工作原理及逻辑功能。

2、熟悉74LS153和74LS151的管脚排列和测试方法。

3、学习用数据选择器构成组合逻辑电路的方法。

二、实验任务1、用双四选一数据选择器74LS153实现一位全减器。

2、用双四选一数据选择器74LS153设计一个四位奇偶校验器。

3、用八选一数据选择器74LS151设计一个多数表决电路。

4、用Multisim8进行仿真,并在实验仪器上实现。

三、实验原理数据选择器又称多路转换器或多路开关,其功能是在地址码(或叫选择控制)电位的控制下,从几个数据输入中选择一个并将其送到一个公共输出端。

数据选择器的功能类似一个多掷开关,如图3.6.1所示,图中有四路数据D 0 ~ D 3通过选择控制信号A 1、A 0(地址码)从四路数据中选中某一路数据送至输出端Y 。

一个n 个地址端的数据选择器,具有2n 个数据选择功能。

例如:数据选择器(74LS153),n = 2,可完成四选一的功能;数据选择器(74LS151),n = 3,可完成八选一的功能。

1、双四选一数据选择器74LS153所谓双4选1数据选择器就是在一块集成芯片上有两个4选1数据选择器。

集成芯片引脚排列如图3.6.2,功能如表3.6.1所示。

表3.6.1 74LS153功能表图3.6.2 74LS153引脚排列1 0地址码 D D D D数据输入 Y输出 图3.6.1 四选一数据选择器示意图S1、S2为两个独立的使能端;A1、A0为公用的地址输入端;1D0~1D3和2D0~2D3分别为两个4选1数据选择器的数据输入端;Q1、Q2为两个输出端。

(1)当使能端S1(S2)=1时,多路开关被禁止,无输出,Q=0。

(2)当使能端S1(S2)=0时,多路开关正常工作,根据地址码A1、A0的状态,将相应的数据D0~D3送到输出端Q。

如:A1A0=00 则选择D O数据到输出端,即Q =D0。

数字电路中加法器和减法器逻辑图分析1.加法器,减法器都是从一位的二进制数开始进行例题讲解,逐渐扩展到多位二进制位数之间的运算。

在设计逻辑电路的过程中,根据所描述的功能构建好真值表。

出题者喜欢要求读者用与或门,与或非门构建函数表达式。

它的原因在于依据真值表写函数表达式,最标准的就是最小项表达式。

以下小图的逻辑图来看与或门,我们的头脑中不能老是思维定势,认为输入就是两个,在实际生活中,输入应该非常多,远非两个,在逻辑符号中,要清楚地认识与非门的多输入的画法,将与门分成了好几格,每一格代表一个与门电路。

下小图可以写成AB+CD+EF(不认真考虑前面的输入),由细小的门集成为更大的门,将某一部分单独来看,它们就是一个整体,如(AB+CD+EF),体现在逻辑图中就是一个角。

如果从全图的角度看,在最后一级门电路中,每一个小整体代表着输出。

最后一级的与门中,有两个输入,有三个输入,这都是可以的,最多输入的个数是依照初始的输入的个数来定,不可能超过这个数,只可能少于这个数,因为对于某一输出而言,并非所有的输入对它都是有效的。

从最左边的所有输入,经过逻辑电路图,在最右边得到了所有的输出。

还有一点,这是与或表达式的逻辑图,如果在写逻辑表达式,包括化简变化函数式时,采用了不同于与或形式的表达式,那么最终得到的逻辑图就和下面的与或形式的逻辑图完全不一样。

2.一位的全减器是指,两个一位的二进制数之间进行减法运算。

全减器的特例就是半减器。

多位二进制减法器,是由加法电路构成的;在加法电路的基础上,减法与加法采用同一套电路,实现加减法共用。

3.这里的多位二进制数的减法,是指无符号数,为什么?将减法运算转换为加法运算,采用的是补数的方法完成的。

这就解释了为什么两者能共用一套电路,是不是减法在转换时,我们需要在加法电路的基础上进行一些小的扩展,来进行减法的补码转换?N反是每一位都取反,没有符号位,下式当中,A-B是减法,通过形式转化,将-B化为B反+1-2n,B是正数,A和B均为无符号数,通过补码的转变,我们成功的将-B变为了固定的-2n,但是这还是有减号,该怎么解决?仔细观察下面这张图,A和B是两个四位二进制数相减。

EDA技术实用教程

课题报告

课题名称:一位全减器的设计

院系:

专业:电子信息工程

组员:

设计流程:

一、一位半减器的设计

一位半减器程序如下; 其中x,y 是输入,diff 是输出差,s_out 是借位输出, sub_in 为借位输入。

library ieee;

use ieee.std_logic_1164.all; entity h_suber is

port (x,y : in std_logic; diff,s_out : out std_logic ); end h_suber;

architecture hdlarch of h_suber is begin process(x,y) begin

diff <= x xor y;s_out <= (not x) and y; end process; end hdlarch;

半减器逻辑表达式:

半减器真值表:

输入输出

x y diff s_sout

0000

0111

1010

1100半减器波形图如下:

半减器封装图:

二、一位全减器的设计

一位全减器设计结构图:sub_in为借位输入,clk是输入延迟信号用来消除仿真图中出现的毛刺现象

一位全减器逻辑表达式:

一位全减器真值表:

一位全减器波形图:

一位全减器封装图:。