实验二__三态门和OC门的研究

- 格式:ppt

- 大小:427.50 KB

- 文档页数:12

实验二三态门,OC门的设计与仿真一、实验目的熟悉三态门、OC门的原理,用逻辑图和VHDL语言设计三态门、OC门,并仿真。

二、实验内容1.用逻辑图和VHDL语言设计三态门,三态门的使能端对低电平有效。

2.用逻辑图和VHDL语言设计一个OC门(集电极开路门)。

三、实验原理1.三态门,又名三态缓冲器(Tri-State Buffer)用途:用在总线传输上,有效而又灵活地控制多组数据在总线上通行,起着交通信号灯的作用。

功能:三态逻辑输出三种不同的状态,其中两种状态常见的逻辑1和逻辑0,第三个状态高阻值,称为高阻态,用Hi-Z或者Z或z表示三态缓冲器比普通缓冲器多了一个使能输入EN,即连接到缓冲器符号底部的信号。

从真值表可以看出,如果是EN=1.则OUT等于IN,就像普通缓冲器一样。

但是当EN=0时,无论输入的值什么,输出结果为高阻态(Hi-Z)。

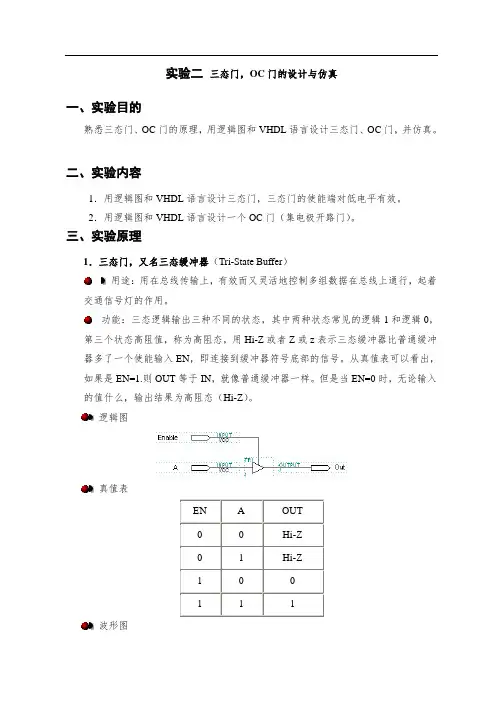

逻辑图真值表EN A OUT0 0 Hi-Z0 1 Hi-Z1 0 01 1 1波形图2.OC门,又名集电极开路门(opndrn)用途:集电极开路门(OC门)是一种用途广泛的门电路。

典型应用是可以实现线与的功能。

逻辑图真值表A B0 01 Hi-Z波形图四、实验方法与步骤实验方法:采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4的FPGA试验箱。

实验步骤:1、编写源代码。

打开QuartusⅡ软件平台,点击File中得New建立一个文件。

编写的文件名与实体名一致,点击File/Save as以“.vhd”为扩展名存盘文件。

VHDL 设计源代码如下:三态门:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY tri_s ISPORT (enable,datain:IN STD_LOGIC;dataout:OUT STD_LOGIC);END tri_s;ARCHITECTURE bhv OF tri_s ISBEGINPROCESS (enable,datain)BEGINIF enable='1' THEN dataout<=datain;ELSE dataout<='Z';END IF;END PROCESS;END bhv;OC门:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY oc ISPORT(datain:IN STD_LOGIC;dataout:OUT STD_LOGIC);END oc;ARCHITECTURE bhv OF oc ISBEGINPROCESS (datain)BEGINIF (datain='0') THEN dataout<='0';ELSE dataout<='Z';END IF;END PROCESS;END bhv;2、按照实验箱上FPGA的芯片名更改编程芯片的设置。

实验三、OC门的研究一、实验目的:了解负载电阻RL对集电极开路门工作状态的影响;掌握集电极开路门的使用方法;二、实验要求:实现OC门的线与功能:a)用四个OC门线与,驱动四个与非门;b)计算负载电阻RL;c)在该阻值条件下,测量V oh与Vol。

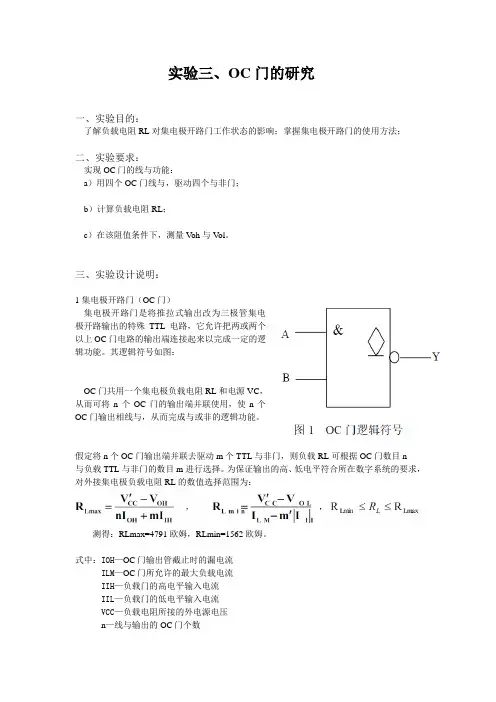

三、实验设计说明:1集电极开路门(OC门)集电极开路门是将推拉式输出改为三极管集电极开路输出的特殊TTL电路,它允许把两或两个以上OC门电路的输出端连接起来以完成一定的逻辑功能。

其逻辑符号如图:OC门共用一个集电极负载电阻RL和电源VC,从而可将n个OC门的输出端并联使用,使n个OC门输出相线与,从而完成与或非的逻辑功能。

假定将n个OC门输出端并联去驱动m个TTL与非门,则负载RL可根据OC门数目n与负载TTL与非门的数目m进行选择。

为保证输出的高、低电平符合所在数字系统的要求,对外接集电极负载电阻RL的数值选择范围为:测得:RLmax=4791欧姆,RLmin=1562欧姆。

式中:IOH—OC门输出管截止时的漏电流ILM—OC门所允许的最大负载电流IIH—负载门的高电平输入电流IIL—负载门的低电平输入电流VCC—负载电阻所接的外电源电压n—线与输出的OC门个数m’—负载门的个数m—接入电路的负载门输入端的总个数本实验74LS01(OC与非门)的电特性如下表四、实验设备与元器件:1.数字电路与系统实验箱1台2.数字万用表1块3.元器件74LS01 1片74LS00 1片电阻变阻器1个五、实验数据及分析实验中测量所得数据如下:电阻R(欧姆)不同状态下的电压值输入端电平电压值VOH/VOL(伏特)A B C D0 0 0 00 0 0 10 0 1 10 1 1 11 1 1 1分析:所得实验数据回代入公式结果符合理论。

且测得的电压值的变化规律随着输入OC门高电平输入端个数增加而减小,且不输入高信号和输入高信号之间电压差距明显,符合理论分析结果。

测得的电阻符合理论计算值的Rmax<R<Rmin,测得的电压值也近似等于按表格里查找所得的电压值。

三态门实验报告三态门实验报告引言:在科学研究中,实验是获取真实数据和验证理论的重要方法之一。

本次实验旨在研究三态门的工作原理和应用。

通过实验,我们能够深入了解三态门的特性,并进一步探究其在现实生活中的应用。

一、实验目的本次实验的目的是通过搭建三态门电路,观察和分析三态门的工作原理,探究其在数字电路中的应用。

二、实验材料和仪器本次实验所需材料和仪器如下:1. 电路板2. 三态门芯片3. 连接线4. 电源5. 开关6. LED灯三、实验步骤1. 将三态门芯片插入电路板中,并用连接线连接芯片和其他元件。

2. 将电源接入电路板,确保电路板正常供电。

3. 通过开关控制输入信号,观察LED灯的亮灭情况。

四、实验结果和分析通过实验观察和数据记录,我们得出以下实验结果和分析:1. 当输入信号为低电平时,LED灯熄灭。

2. 当输入信号为高电平时,LED灯点亮。

3. 当输入信号为无效电平时,LED灯保持上一状态。

根据实验结果,我们可以得出以下结论:三态门是一种数字逻辑门,具有三个输入端和一个输出端。

它的工作原理是根据输入信号的不同状态,输出相应的电平。

当输入信号为低电平时,输出为低电平;当输入信号为高电平时,输出为高电平;当输入信号为无效电平时,输出保持上一状态。

五、三态门的应用三态门在数字电路中有广泛的应用。

以下是一些常见的应用场景:1. 数据总线控制:在计算机系统中,三态门常用于数据总线的控制,实现数据的传输和共享。

2. 内存芯片:三态门可以用于内存芯片的控制线路,实现数据的读取和写入。

3. 多路选择器:三态门可以用于多路选择器的实现,根据输入信号的不同状态,选择不同的输入通路。

4. 缓冲器:三态门可以用作缓冲器,将信号从一个电路传递到另一个电路,保持信号的强度和波形。

六、实验总结通过本次实验,我们深入了解了三态门的工作原理和应用。

三态门作为一种重要的数字逻辑门,在现代电子技术中起着重要的作用。

通过进一步研究和实践,我们可以更好地应用三态门,推动数字电路技术的发展。

东南大学电工电子实验中心实验报告课程名称:数字逻辑电路实验第二次实验实验名称:门电路和组合逻辑院(系):电气工程专业:电气工程及自动化姓名:学号:实验室: 104 实验时间:2013年11月8日评定成绩:审阅教师:一、实验目的(1)掌握TTL和CMOS器件的静态特性和动态特性测量方法及这些特性对数字系统设计的影响;(2)掌握通过数字器件手册查看器件静态和动态特性参数;(3)掌握不同结构的数字器件之间的互连;(4)掌握OC门和三态门的特性和使用方法;(5)加深示波器测量技术的训练;(6)掌握小规模组合逻辑的工程设计方法;(7)了解竞争和冒险的产生原因,消除方法,掌握用示波器和逻辑分析捕捉毛刺的方法。

二、实验器材74LS00 74LS2074LS244 74HC0174LS04三、 必做实验1.(1)用 OC 门实现三路信号分时传送的总线结构a. 用OC 门实现三路信号分时传送的总线结构,框图如图所示,功能如表所示。

(注意OC 门必须外接负载电阻和电源,E C 取5V )待设计电路D 2D 1D 0A 2A 1A 0Y图 三路分时总线原理框图① 查询相关器件的数据手册,计算OC 表 设计要求的逻辑功能控制输入输出 A 2A 1 A 0 Y 01D 0连接电路。

)(107.66105.039.45'36min max Ω⨯=⨯⨯-=⋅+-=-IH CEO OH C C I N nI V E R )(5.911102.526.053max ax min Ω=⨯-=⋅--=-IL OL OLm C C I N I V E R选取Ω=k R C 2。

设计图如右图所示接线图如下② 静态验证:控制输入和数据输入端加高低电平,用电压表测量输出高低电平的电压值,注意测量A 2A 1A 0=000时的输出值。

E c =A 2A1AD2D1D输出Y电压/V001X X00001X X11010X0X0010X1X11000X X01001X X1000X X X1③动态验证:控制输入加高低电平,数据输入端加连续脉冲信号,用示波器双踪显示输入和输出波形,测量波形的峰峰值、高电平电压和低电平电压,对结果进行分析并解释为什么要选择“DC”。

实验二(1)三态门电路设计班级姓名学号一、实验目的熟悉QuartusII仿真软件的基本操作,并用VHDL/Verilog语言设计一个三态门。

二、实验内容1、熟悉QuartusII软件的基本操作,了解各种设计输入方法(原理图设计、文本设计、波形设计)2、用VHDL语言设计一个三态门,最终在FPGA芯片上编程指令译码器,并验证逻辑实现。

三、实验方法1、实验方法:采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4的FPGA试验箱。

2、实验步骤:1、新建,编写源代码。

(1).选择保存项和芯片类型:【File】-【new project wizard】-【next】(设置文件路径+设置project name为stm)-【next】(设置文件名zlym.vhd—在【add】)-【properties】(type=AHDL)-【next】(family=FLEX10K;name=EPF10K10TI144-4)-【next】-【finish】(2).新建:【file】-【new】(第二个AHDL File)-【OK】2、写好源代码,保存文件(stm.vhd)。

3、编译与调试。

确定源代码文件为当前工程文件,点击【processing】-【start compilation】进行文件编译。

编译结果有一个警告,文件编译成功。

4、波形仿真及验证。

新建一个vector waveform file。

按照程序所述插入EN,A以及dataout)四个节点(EN,A为输入节点,dataout为输出节点)。

(操作为:右击-【insert】-【insert node or bus】-【node finder】(pins=all;【list】)-【>>】-【ok】-【ok】)。

任意设置EN,A的输入波形…点击保存按钮保存。

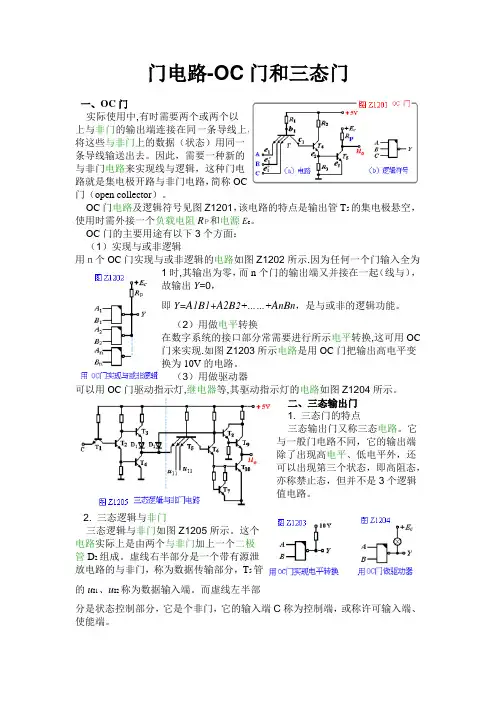

门电路-OC门和三态门一、OC门实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态)用同一条导线输送出去。

因此,需要一种新的与非门电路来实现线与逻辑,这种门电路就是集电极开路与非门电路,简称OC门(open collector)。

OC门电路及逻辑符号见图Z1201,该电路的特点是输出管T5的集电极悬空,使用时需外接一个负载电阻RP和电源E c。

OC门的主要用途有以下3个方面:(1)实现与或非逻辑用n个OC门实现与或非逻辑的电路如图Z1202所示.因为任何一个门输入全为1时,其输出为零,而n个门的输出端又并接在一起(线与),故输出Y=0,即Y=A1B1+A2B2+……+A n B n,是与或非的逻辑功能。

(2)用做电平转换在数字系统的接口部分常需要进行所示电平转换,这可用OC门来实现.如图Z1203所示电路是用OC门把输出高电平变换为10V的电路。

(3)用做驱动器可以用OC门驱动指示灯,继电器等,其驱动指示灯的电路如图Z1204所示。

二、三态输出门1. 三态门的特点三态输出门又称三态电路。

它与一般门电路不同,它的输出端除了出现高电平、低电平外,还可以出现第三个状态,即高阻态,亦称禁止态,但并不是3个逻辑值电路。

2. 三态逻辑与非门三态逻辑与非门如图Z1205所示。

这个电路实际上是由两个与非门加上一个二极管D2组成。

虚线右半部分是一个带有源泄放电路的与非门,称为数据传输部分,T5管的u I1、u I2称为数据输入端。

而虚线左半部分是状态控制部分,它是个非门,它的输入端C称为控制端,或称许可输入端、使能端。

当C端接低电平时,T4输出一个高电平给T5,使虚线右半部分处于工作状态,这样,电路将按与非关系把u I1,u I2接受到的信号传送到输出端,使u0或为高电平,或为低电平。

当C端接高电平时,T4输出低电平给T5,使T6、T7、T10截止。

另一方面,通过D2把T8的基极电位钳在1v左右,使T9截止。

锁存器:输出端的状态不会随输入端的状态变化而变化,只有在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号。

通常只有0和1两个值。

典型的逻辑电路是D触发器。

缓冲器:多用在总线上,提高驱动能力、隔离前后级,缓冲器多半有三态输出功能。

三态缓冲器就是典型的线与逻辑器件,可允许多个器件挂在一条总线上,当然OC输出也可用在线与逻辑应用上。

OC门,又称集电极开路(漏极开路)与非门门电路,Open Collector(Open Drain)。

为什么引入OC门?实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态电平)用同一条导线输送出去。

因此,需要一种新的与非门电路--OC门来实现“线与逻辑”。

OC门主要用于3个方面:实现与或非逻辑,用做电平转换,用做驱动器。

由于OC门电路的输出管的集电极悬空,使用时需外接一个上拉电阻Rp到电源VCC。

OC门使用上拉电阻以输出高电平,此外为了加大输出引脚的驱动能力,上拉电阻阻值的选择原则,从降低功耗及芯片的灌电流能力考虑应当足够大;从确保足够的驱动电流考虑应当足够小。

线与逻辑,即两个输出端(包括两个以上)直接互连就可以实现“AND”的逻辑功能。

在总线传输等实际应用中需要多个门的输出端并联连接使用,而一般TTL门输出端并不能直接并接使用,否则这些门的输出管之间由于低阻抗形成很大的短路电流(灌电流),而烧坏器件。

在硬件上,可用OC门或三态门(ST门)来实现。

用OC门实现线与,应同时在输出端口应加一个上拉电阻。

三态门(ST门),主要用在应用于多个门输出共享数据总线,为避免多个门输出同时占用数据总线,这些门的使能信号(EN)中只允许有一个为有效电平(如高电平),由于三态门的输出是推拉式的低阻输出,且不需接上拉(负载)电阻,所以开关速度比OC门快,常用三态门作为输出缓冲器。

实验二 OC 门和三态门的应用一、实验目的1.能够正确使用数字电路实验系统。

2.掌握TTL 三态门的逻辑应用。

3.掌握TTL OC 门的逻辑应用4.熟悉TTL 三态门、OC 门电路应用的测试方法。

二、实验原理三态门工作时,有三种输出状态0态、1态、高阻态。

当使能端 时三态门正常工作;当使能端 时三态门工作在高阻状态。

适当的利用三态门的控制端可实现单向数据传输总线。

OC 门为集电极开路的与非门,正常工作时要在输出端和电源之间外接电阻R L 才能完成与非功能。

利用多个OC 门输出端“线与”可完成“与或非”功能,从而使OC 门的与非功能得到了扩展。

三、实验内容与步骤1. 74LS125三态门应用测试74LS125三态门外引脚排列为图2.1所示。

利用三态门实现总线传输,实验电路见图2.2所示。

将三个三态门的输入端分别接高电平、地、连续脉冲。

根据三个开关S 1、S 2、S 3的不同状态(S 1、S 2、S 3中每次只允许有一个为低电平),观察输出端指示灯LED 的变化,体会三态门实现总线传输的作用。

切记:要先认清三态门的使能端( ),用逻辑开关使三个三态门的使能端全处于高电平(三态门全处于高阻状态),才允许接通电源。

然后,只能一个门工作,观测总线的逻辑状态。

观测结束,先使工作的三态门转换到高阻状态,再让另一个门开始工作。

否则,将损坏器件。

将测试结果填入表2.1。

表2.1 三态门实现总线传输功能表2.TTLOC门(74LS03)实现线与功能测试OC 门选用芯片74LS03,实验电路如图2.3,此电路构成了线与逻辑。

完成真值表2.2测试,根据真值表判断其逻辑功能。

注意R C 的选择(R=1K Ω,R P =1K Ω)。

输入 使能端(控制端) 输出S1 S2 S3 Y A 1(0V ) A 2(5V ) 连续脉冲 V CC EN 4 A 4 Y 4 EN 3 A 3 Y 374LS125EN 1 A 1 Y 1 EN 2 A 2 Y 2 GND14 813 12 9 10 111EN 1ENS 1 逻辑电平 S 2开 5V×A 1A 2 Y 1 Y 2LED EN , EN=1 EN=0表2.2 OC 门线与功能测试表输入逻辑状态Y 输出A B C D状态 电位(V ) 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 11图2.1 74LS125三态门外引脚排列图 图2. 2 利用三态门实现总线传R P RR CV CC & ◇& ◇A BC DG 1G 2Y 1Y 2}&LED图2. 3 OC 门线与功能测试电路1 0 0 01 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 1四、实验报告要求1.画出实验用各逻辑门的逻辑符号,并写出逻辑表达式。

实验二、三态门实验一、实验目的1、掌握三态门逻辑功能和使用方法。

2、掌握用三态门构成总线的特点和方法。

3、初步学会用示波器测量简单的数字波形。

二、实验所用仪器和芯片1、四二输入与非门74LS00 1片2、三态输出的四总线缓冲门74LS125 1片3、TEC-5实验系统 1台4、示波器 1台三、实验内容1、74LS125三态门的输出负载为74LS00的一个与非门输入端。

74LS00同一个与非门的另一个输入端接低电平,测试74LS125三态门的三态(高阻)输出、高电平输出、低电平输出的电压值。

同时测试74LS125三态输出时74LS00的输出值。

2、74LS125三态门的输出负载为74LS00的一个与非门输入端。

74LS00同一个与非门的另一个输入端接高电平,测试74LS125三态门三态(高阻)输出、高电平输出、低电平输出的电压值。

同时测试74LS125三态输出时74LS00的输出值。

*3、用74LS125两个三态门输出构成一条总线。

使两个控制端一个为低电平,另一个为高电平。

一个三态门的输入接50kHz信号,另一个三态门的输入接500KHz信号。

用示波器观察三态门的输出。

四、实验提示1、三态门74LS125的控制端C为低电平有效。

2、用实验台的电平开关输出作为被测器件的输入。

拨动开关,则改变器件的输入电平。

五、实验报告要求1、画出实验的逻辑电路图。

2、分析每个实验的实验现象。

3、分析实验1和实验2中三态门呈高阻状态时,74LS00输出电压不同的原因。

*4、用三态门74LS125构成总线时,三态门输出应怎样连接?为什么在任何时刻,构成总线的三态门中只允许一个控制端为低电平,其余控制端应为高电平。