一步一步 配置下载xilinx FPGA JTAG

- 格式:pdf

- 大小:4.46 MB

- 文档页数:35

1、WX demo板FPGA代码加载此FPGA的jtag接口为板上的J28接口,对FPGA的各种操作可通过USBblaster线连接到此接口进行识别操作;PS模式下,是通过flash来对FPGA完成配置的,FLASH中的数据是通过jtag下载进去的的,但是JTAG不能直接配置FLASH,需要通过板子上的MAXII(CPLD)芯片进行连接,altera 提供了专用的IP来完成转换,所以需要先准备烧写FLASH之前MAXII的PFL工程。

MAXII芯片的JTAG接口是J27,这个接口可以对CPLD进行编程,也同时是对FLASH进行编程的接口。

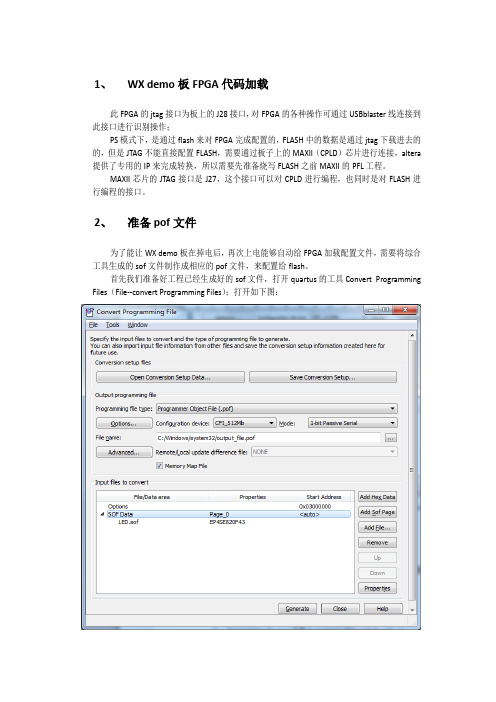

2、准备pof文件为了能让WX demo板在掉电后,再次上电能够自动给FPGA加载配置文件,需要将综合工具生成的sof文件制作成相应的pof文件,来配置给flash。

首先我们准备好工程已经生成好的sof文件,打开quartus的工具Convert Programming Files(File--convert Programming Files);打开如下图:配置步骤如下:1)Programming file type选择Programmer Object File(*.pof);2)Configuration device 选择CFI_512MB ;3)点击Options按钮,Option bit address(32-bit hexadencimal)设置为0x3000000;4)Mode 选择1-bit Passive Serial;5)选择输出的pof文件的路径和文件名;6)点击Advanced按钮,里面所有设置保持默认状态;7)选中”SOF Data Page_ 0 <Auto>”这行,点击Add File,把FPGA对应的sof文件(如LED.sof)添加进来;8)选中LED.sof 这行,点击Properties,把Compress前面的钩打上, 这样便于缩短下载时间;9)最后点击Generate,便会输出我们所需要的pof文件。

1 FPGA的上电启动原理FPGA是基于RAM结构的,当然了,也有基于FLASH结构的,但RAM结构的是主流,也是我们讨论的重点。

而RAM是易失存储器,在掉电后保存在上面的数据就丢失了,重新上电后需要再下载一次才可以。

因此,我们肯定不希望每次重新上电后都用PC去下载一次,工程实现也不允许我们这么做。

所以,通常FPGA旁边都有一颗配置芯片,它通常是一片FLASH,或者是并行或者是串行接口的。

不管是串行还是并行的FLASH,它们的启动加载原理基本相同,后面我们会专门讨论。

FPGA器件有三类配置下载方式:主动配置方式(AS)、被动配置方式(PS)和最常用的基于JTAG的配置方式。

AS和PS模式主要是将bit流下载到配置芯片中;而JTAG模式则既能将代码下载到FPGA中直接在线运行(速度快,调试时优选),也能够通过FPGA将bit流下载到配置芯片中。

由于JTAG方式灵活多用,所以我们的VIP板就只预留了JTAG接口。

AS配置方式:AS配置方式由FPGA器件引导配置操作过程,它控制着外部存储器及其初始化过程,EPCS系列配置芯片如EPCS1,EPCS4,EPCS16等配置器件专供AS模式。

使用Altera串行配置器件来完成,FPGA器件处于主动地位,配置器件处于从属地位。

配置数据通过DATA0引脚送入 FPGA。

配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

PS配置方式:PS配置方式则由外部计算机或其它控制器控制配置过程。

通过加强型配置器件(EPC16,EPC8,EPC4)等配置器件来完成,在PS配置期间,配置数据从外部储存部件,通过DATA0引脚送入FPGA。

配置数据在DCLK上升沿锁存,1个时钟周期传送1位数据。

JTAG配置方式:JTAG接口是一个业界标准,主要用于芯片测试等功能,使用IEEE Std 1149.1联合边界扫描接口引脚,支持JAM STAPL标准,可以使用Altera下载电缆或主控器来完成。

Step by step 学习下载配置Xilinx之FPGA配合Mars-XC2S50-Core FPGA核心板,用图文方式向大家详细讲述如何下载配置Xilinx的FPGA。

FPGA下载模式说明S1为FPGA下载模式选择跳线,断开配置FPGA为JTAG模式,短接则FPGA配置方式为Master Serial Mode下面我们利用Spartan2核心板介绍一下通过JTAG菊花链方式下载FPGA和烧录PROM.硬件跳线选择1. 跳线S1: 此时要求M0 M1 M2 = 100, 断开即可设置FPGA的下载方式为Boundary-scan mode。

2. 将Xilinx下载线和核心板上JTAG mode接口J2相连,连接到计算机并口。

3. 目标板上电。

软件操作一、产生PROM配置文件在烧写PROM之前,需要将ISE生成的*.bit文件转换成prom格式的文件才能下载Xilinx 专用的配置PROM中。

1. 启动iMPACT2. 出现下面画面选择Prepare Configuration Files,点击下一步。

3.出现如下界面,选择PROM File,点击下一步。

4.界面如下,选择PROM类型,和文件格式,填写生成文件名称路径,下一步5.指定使用的PROM类型,并添加,下一步。

6.下一步7点击Add File按钮。

8.选上需要转换的*.bit文件打开。

9.出现如下对话框,提示要不要添加另外的.bit文件。

选择否10界面如下,点击完成11.出现要不要现在生成配置文件,选择是,至此,PROM的文件已经生成。

12.OK.二.菊花链方式下载配置FPGA和PROM 1.打开iMPACT配置2.出现如下界面,选择Configure Device, 下一步。

3.选择Boundary-Scan Mode,下一步。

4.选自动监测扫描链,完成。

5.出现如下界面,检测到两个器件:xc2s50和xcf01s,并提示是否为每个器件添加配置文件。

Gowin FPGA产品JTAG配置手册TN653-1.07, 2019-11-18版权所有© 2019广东高云半导体科技股份有限公司未经本公司书面许可,任何单位和个人都不得擅自摘抄、复制、翻译本文档内容的部分或全部,并不得以任何形式传播。

免责声明本文档并未授予任何知识产权的许可,并未以明示或暗示,或以禁止发言或其它方式授予任何知识产权许可。

除高云半导体在其产品的销售条款和条件中声明的责任之外,高云半导体概不承担任何法律或非法律责任。

高云半导体对高云半导体产品的销售和/或使用不作任何明示或暗示的担保,包括对产品的特定用途适用性、适销性或对任何专利权、版权或其它知识产权的侵权责任等,均不作担保。

高云半导体对文档中包含的文字、图片及其它内容的准确性和完整性不承担任何法律或非法律责任,高云半导体保留修改文档中任何内容的权利,恕不另行通知。

高云半导体不承诺对这些文档进行适时的更新。

目录目录 (i)图目录 (iii)表目录 (iv)1 关于本手册 (1)1.1 手册内容 (1)1.2 适用产品 (1)1.3 相关文档 (1)1.4 术语、缩略语 (2)1.5 技术支持与反馈 (2)2 配置和烧录(Configuration&Programming) (3)2.1 JTAG配置模式 (3)2.2 配置流程 (5)2.2.1 JTAG引脚定义 (5)2.2.2 TAP状态机 (5)2.2.3 TAP复位 (5)2.2.4 指令寄存器和数据寄存器 (6)2.2.5 读取ID CODE实例 (7)2.2.6 配置SRAM流程 (9)2.2.7 读取SRAM的流程 (12)2.2.8 擦除内部Flash (14)2.2.9 编程内部Flash流程 (18)2.2.10 读取内部Flash流程 (22)2.2.11 背景烧录(Background Programming) (25)2.2.12 编程外部Flash (27)2.2.13 读取Status Register 0x41 (31)2.2.14 读取User Code 0x13 (32)2.2.15 重加载0x3C (32)2.2.16 擦除SRAM 0x15 (32)3 例程文件 (33)图目录图2-1 JTAG配置模式连接示意图 (4)图2-2 TAP状态机 (5)图2-3指令寄存器访问时序 (6)图2-4数据寄存器访问时序 (6)图2-5读取ID Code状态机流程图 (8)图2-6读取ID Code指令-0x11访问时序 (8)图2-7读取ID Code数据寄存器访问时序 (8)图2-8配置SRAM流程 (10)图2-9 Tansfer Configuration Data过程示意 (11)图2-10读取SRAM的流程 (13)图2-11擦除GW1N-2(B)/4(B)/6/9,GW1NZ-1内部Flash擦除流程 (15)图2-12擦除GW1N-1(S)内部Flash流程 (17)图2-13编程内部Flash流程图 (19)图2-14 X-page编程流程图 (21)图2-15 Y-page编程流程图 (22)图2-16读取内部Flash流程图 (23)图2-17读取一个Y-page的过程 (24)图2-18 GW1N-4 Background Programming 流程图 (25)图2-19 Transfer JTAG Instrction Sample & Extest 流程图 (26)图2-20 JTAG接口编程外部Flash连接示意图 (27)图2-21采用config-mode[2:0]=011模式编程SPI Flash流程示意图 (28)图2-22 GW2A系列JTAG模拟SPI发送0x06指令时序图 (28)图2-23 GW1N系列JTAG模拟SPI发送0x06指令时序图 (29)图2-24采用Boundary Scan模式编程SPI Flash流程示意图 (30)表目录表目录表1-1术语、缩略语 (2)表2-1 JTAG配置模式管脚定义 (3)表2-2 Gowin FPGA IDCODE (7)表2-3发送指令过程中TDI和TMS的值变化 (7)表2-4器件SRAM地址数量和地址长度 (12)表2-5 JTAG的TCK频率要求 (14)表2-6 Readback-pattern / Autoboot-pattern (18)表2-7管脚状态 (29)表2-8 Status Register含义 (31)1关于本手册 1.1手册内容1关于本手册1.1手册内容本手册主要介绍Gowin FPGA产品的JTAG配置及烧录相关信息,包含JTAG配置模式、配置流程及相关例程文件。

有些人对于FPGA下JTAG的下载方式有些迷惑,为什么出现配置芯片了,为什么要用不同的下载电缆,不同的下载模式?通过在网上查阅相关资料做了总结和整理如下:1 FPGA器件有三类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式。

AS模式(active serial configuration mode):FPGA器件每次上电时作为控制器,由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,从配置器件EPCS主动发出读取数据信号,从而把EPCS的数据读入FPGA中,实现对FPGA的编程配置数据通过DATA0引脚送入 FPGA,配置数据被同步在DCLK 输入上,1个时钟周期传送1位数据。

PS模式(passive serial configuration mode):则由外部计算机或控制器控制配置过程。

通过加强型配置器件(EPC16,EPC8,EPC4)等配置器件来完成,EPCS 作为控制器件,把FPGA当作存储器,把数据写人到FPGA中,实现对FPGA的编程。

该模式可以实现对FPGA在线可编程。

在下载配置的时候对于Cyclone II的器件,如EP2C8,在JTAG下载方式对应.sof,AS下载方式对应.pof。

JTAG:JTAG是直接烧到FPGA里面的由于是SRAM 断电后要重烧,AS 是烧到FPGA的配置芯片里保存的每次上电就写到FPGA里。

一般情况下,Cyclone II开发板上应该有两种下载模式,AS和JTAG。

AS就是下载.pof文件到EPCS中。

而JTAG就是下载.sof文件到FPGA中的RAM中。

关于JTAG的原理,大家可以参考OPEN-JTAG 开发小组写的《ARM JTAG 调试原理》。

JTAG、BDM 都比较类似,实际上是将仿真功能嵌入到芯片内部,接上比较简单的调试工具就可以进行开发了,省掉了高价的仿真器。

JTAG 调试用到了 TCK、TMS、TDI、TDO 和 TRST这几个脚。

JTAG并口下载设计张立强;宋玲;刘宝娟【摘要】JTAG并口下载是FPGA开发流程中重要组成部分.下载过程中状态机的切换和下载后状态信号判断是编程下载的重点.以可编程芯片为下载芯片,采用状态机的思想来实现数据的下载.通过对程序的优化和反复验证,JTAG下载是在速度和数据传输最稳定的情况下进行的,调试结果表明,JTAG下载运行可靠.%JTAG parallel port download is the main composition of the FPGA development. The state machine switching in download and the state signal judging after download are important part of programming download. The programmable chip is taken as the download chip to achieve data download by means of the concept of the state - machine. After optimizing and verifying the procedure, JTAG download performs in the condition of stable speed and data transmission. The debugging result proves that the download is reliable.【期刊名称】《微处理机》【年(卷),期】2013(034)001【总页数】3页(P13-15)【关键词】联合测试行为组织;现场可编程门阵列;状态信号【作者】张立强;宋玲;刘宝娟【作者单位】中国电子科技集团公司第四十七研究所,沈阳110032【正文语种】中文【中图分类】TN41 引言利用并口下载电缆实现JTAG下载,把并口的有效端口和JTAG端口连接起来,实现了数据写入、数据读出、控制器的信号输入、时钟的传输。

[19]中华人民共和国国家知识产权局[12]发明专利申请公布说明书[11]公开号CN 101140315A [43]公开日2008年3月12日[21]申请号200710176308.1[22]申请日2007.10.24[21]申请号200710176308.1[71]申请人中兴通讯股份有限公司地址518057广东省深圳市南山区高新技术产业园科技南路中兴通讯大厦法务部[72]发明人苏宗田 [74]专利代理机构北京银龙知识产权代理有限公司代理人许静[51]Int.CI.G01R 31/3185 (2006.01)H03K 19/173 (2006.01)G06F 9/445 (2006.01)权利要求书 2 页 说明书 5 页 附图 2 页[54]发明名称一种JTAG下载方式下FPGA逻辑代码的下载方法及下载系统[57]摘要本发明提供了一种JTAG下载方式下FPGA逻辑代码的下载方法及下载系统,用于对2片以上的相同FPGA下载相同的逻辑代码。

其中,所述下载方法包括:将JTAG下载信号中的测试模式选择TMS信号、测试时钟输入TCK信号和测试数据输入TDI信号同时输入至各个FPGA对应的管脚,将逻辑代码并行下载到各个FPGA。

按照本发明的下载方法和下载系统,能够减少FPGA逻辑代码下载所需时间,提高FPGA调试效率。

200710176308.1权 利 要 求 书第1/2页 1.一种JTAG下载方式下FPGA逻辑代码的下载方法,用于对2片以上的相同FPGA下载相同的逻辑代码,其特征在于,将JTAG下载信号中的测试模式选择TMS信号、测试时钟输入TCK信号和测试数据输入TDI信号同时输入至各个FPGA对应的管脚,将逻辑代码并行下载到各个FPGA。

2.如权利要求1所述的下载方法,其特征在于,在逻辑代码下载之前还包括:将各个FPGA的片选信号设置为有效状态。

3.如权利要求1或2所述的下载方法,其特征在于,在逻辑代码下载之前还包括:对所有FPGA的配置完成管脚、编程配置管脚和配置状态管脚均进行上拉处理。

关于Xilinx FPGA JTAG下载时菊花链路中的芯片数量当一个系统中含有多片(2片以上)Xilinx FPGA、CPLD或PROM(FLASH)时,可采用单一JTAG口以菊花链(Daisy Chain)形式将所有芯片串联起来实现下载编程,如下图所示。

这样做有两个好处:(1)可以节省多个JTAG口所占用的PCB空间,特别适合空间有限的嵌入式系统,如小型工业摄像机等;(2)嵌入式系统处于封闭环境中,有时需要对系统中的FPGA程序进行在线或远程升级,必须将JTAG口引到机箱外,显然这种单JTAG 口的菊花链结构是最佳选择。

1、关于链路中的芯片数量Xilinx的UG380:“Spartan-6 FPGA Configuration User Guide”的第58页“JTAG Signal Routing”一节有如下描述:The TCK and TMS signals go to all devices in the chain; consequently, their signal qualityis important. For example, TCK should transition monotonically at all receivers to ensureproper JTAG functionality and must be properly terminated. The quality of TCK can limitthe maximum frequency for reliable JTAG configuration.Additionally, if the chain is large (three devices or more), TMS and TCK should be bufferedto ensure that they have sufficient drive strength at all receivers, and the voltage at logicHigh must be compatible with all devices in the chain.由于TCK和TMS两个信号是连接到菊花链中的所有芯片,因此这两个信号的质量(完整性)非常重要!特别是时钟信号TCK,任何毛刺干扰和边沿抖动都会导致下载失败。

使用Flash Loader(JTAG模式)下载EPCS器件的方法一般来说Altera公司Cyclone或者CycloneII系列FPGA相应的配置器件会选择EPCS 系列串行FLASH。

一般使用AS模式下载EPCS系列器件,下面介绍通过JTAG方式下载EPCS系列器件。

如果这种方式进行正确的AS模式的下载的话,可能是EPCS器件本身已经不能正常工作了,此时建议更换配置芯片。

建议使用Quartus II 5.1及以上版本(5.1以下版本在devices中有很多器件不能找到)。

使用JTAG下载模式下载EPCS器件的步骤如下:1.把需要下载的工程文件生成*.sof文件2.点击File菜单,选择Convert Programming Files….如图一所示。

图一:File 选项3.执行完第二步后出现图二所示的界面。

图二3.第一、鼠标左键点击Programming file type 栏目的下拉箭头,选择JTAG Indirect configuration File(.jic)项;第二、Configuration device栏目的下拉箭头,选择EPCS4(本文以EPCS4为例,客户选择自己所用的配置芯片);第三、点击File name栏目后的….,选择输出文件保存的路径以及输入保存文件名,其后缀为*.jc;第四、在Memory Map File前的空格中打钩;4.用鼠标点击一下SOF Date-----Page 05.用鼠标点击Add File…, 出现以下界面,并在Select Input File中选择用户所要转换的*.sof文件(注意选择用户文件的路径)6.完成第5步操作后将出现下图界面7.用鼠标点击一下 Flash Loader,如图8.用鼠标点击Add Device…..,出现下图界面,并且选择用户自己的FPGA芯片(本文以Cyclone II中的EP2C20F256为例)9.点击OK,出现下面界面10.点击Generate,将出现如下界面,然后点击确定,既完成文件的转换11.用生成的文件在JTAG模式下对EPCS器件进行下载12.下载完成后出面的信息本文件说明由CZL提供,联系方式lail247@ QQ: 418046050本人开发的USB BLASTER下载线100%完全兼容Altera原装下载线,其下载图如下:1、AS模式2、JTAG模式。