数电第五版(阎石)第六章课后习题及答案精品PPT课件

- 格式:pptx

- 大小:672.62 KB

- 文档页数:14

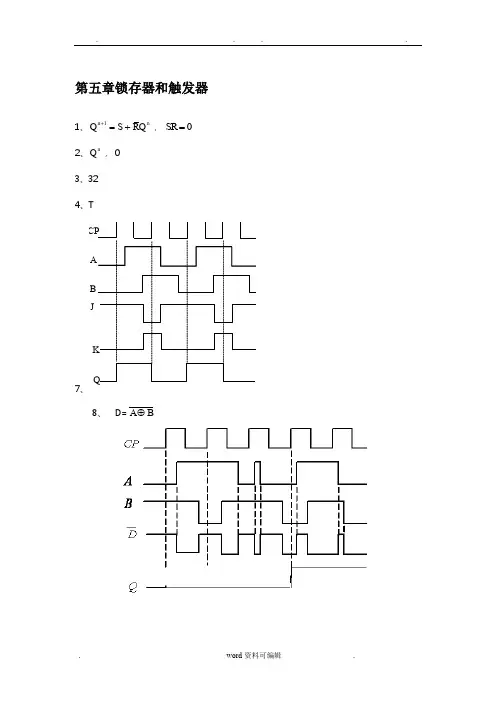

第五章锁存器和触发器

1、1n n Q S RQ +=+, 0SR =

2、n

Q , 0 3、32

4、T

7、

A B

J

4-13题解图

8、

D=B A ⊕

第六章时序逻辑电路

1、输入信号,原来的状态

2、异

3、n

4、4,4

5、反馈清零、反馈置数

6、N

7、状态方程和输出方程:

8、激励方程

状态方程

输出方程

Z=AQ1Q0

根据状态方程组和输出方程可列出状态表,如表题解6.2.4所示,状态图如图题解6。

2.4所示。

14、

15、状态方程为:

24、解:74HC194功能由S1S0控制

00 保持,01右移10 左移11 并行输入

当启动信号端输人一低电平时,使S1=1,这时有S。

=Sl=1,移位寄存器74HC194执行并行输人功能,Q3Q2Q1Q0=D3D2D1D0=1110。

启动信号撤消后,由于Q。

=0,经两级与非门后,使S1=0,这时有

S1S0=01,寄存器开始执行右移操

作。

在移位过程中,因为Q3Q2、

Q1、Q0中总有一个为0,因而能

够维持S1S0=01状态,使右移操作

持续进行下去。

其移位情况如图题

解6,5,1所示。

该电路能按固定的时序输出低电平

脉冲,是一个四相时序脉冲产生电

路。

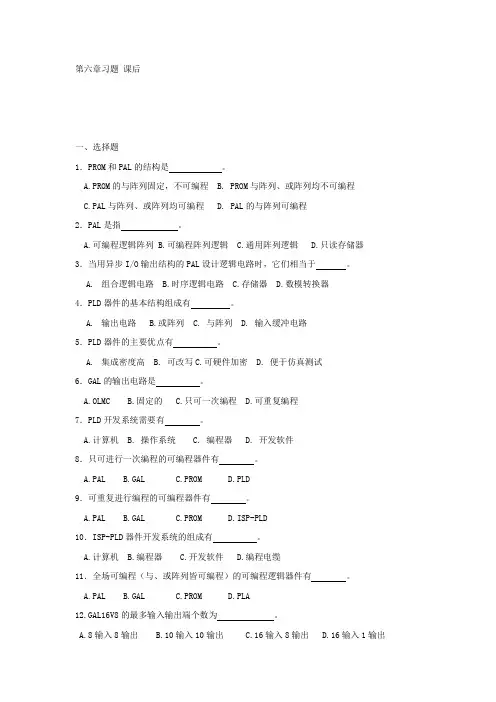

第六章习题课后一、选择题1.PROM和PAL的结构是。

A.PROM的与阵列固定,不可编程B. PROM与阵列、或阵列均不可编程C.PAL与阵列、或阵列均可编程D. PAL的与阵列可编程2.PAL是指。

A.可编程逻辑阵列B.可编程阵列逻辑C.通用阵列逻辑D.只读存储器3.当用异步I/O输出结构的PAL设计逻辑电路时,它们相当于。

A.组合逻辑电路B.时序逻辑电路C.存储器D.数模转换器4.PLD器件的基本结构组成有。

A.输出电路B.或阵列C. 与阵列D. 输入缓冲电路5.PLD器件的主要优点有。

A.集成密度高B. 可改写C.可硬件加密D. 便于仿真测试6.GAL的输出电路是。

A.OLMCB.固定的C.只可一次编程D.可重复编程7.PLD开发系统需要有。

A.计算机B. 操作系统C. 编程器D. 开发软件8.只可进行一次编程的可编程器件有。

A.PALB.GALC.PROMD.PLD9.可重复进行编程的可编程器件有。

A.PALB.GALC.PROMD.ISP-PLD10.ISP-PLD器件开发系统的组成有。

A.计算机B.编程器C.开发软件D.编程电缆11.全场可编程(与、或阵列皆可编程)的可编程逻辑器件有。

A.PALB.GALC.PROMD.PLA12.GAL16V8的最多输入输出端个数为。

A.8输入8输出B.10输入10输出C.16输入8输出D.16输入1输出13一个容量为1K×8的存储器有个存储单元。

A.8B. 8192C.8000D. 8K14.要构成容量为4K×8的RAM,需要片容量为256×4的RAM。

A. 8B.4C. 2D.3215.寻址容量为16K×8的RAM需要根地址线。

A. 8B. 4C.14D.16KE. 1616.RAM的地址码有8位,行、列地址译码器输入端都为4个,则它们的字线加位线共有条。

A.8B.16C.32D.25617.某存储器具有8根地址线和8根双向数据线,则该存储器的容量为。

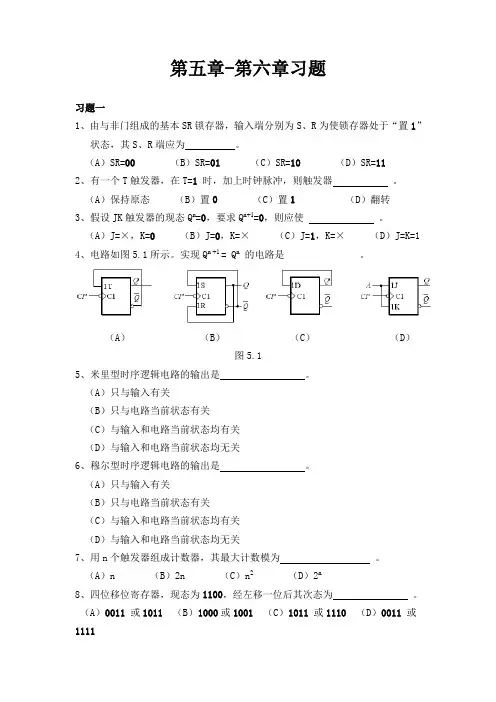

第五章-第六章习题习题一1、由与非门组成的基本SR锁存器,输入端分别为S、R为使锁存器处于“置1”状态,其S、R端应为。

(A)SR=00 (B)SR=01 (C)SR=10 (D)SR=112、有一个T触发器,在T=1 时,加上时钟脉冲,则触发器。

(A)保持原态(B)置0 (C)置1 (D)翻转3、假设JK触发器的现态Q n=0,要求Q n+1=0,则应使。

(A)J=×,K=0 (B)J=0,K=×(C)J=1,K=×(D)J=K=1 4、电路如图5.1所示。

实现Q n +1 = Q n的电路是。

(A)(B)(C)(D)图5.15、米里型时序逻辑电路的输出是。

(A)只与输入有关(B)只与电路当前状态有关(C)与输入和电路当前状态均有关(D)与输入和电路当前状态均无关6、穆尔型时序逻辑电路的输出是。

(A)只与输入有关(B)只与电路当前状态有关(C)与输入和电路当前状态均有关(D)与输入和电路当前状态均无关7、用n个触发器组成计数器,其最大计数模为。

(A)n (B)2n (C)n2(D)2n8、四位移位寄存器,现态为1100,经左移一位后其次态为。

(A)0011 或1011 (B)1000或1001 (C)1011 或1110 (D)0011 或11119、下列电路中,不属于时序逻辑电路的是。

(A)计数器(B)全加器(C)寄存器(D)分频器10、一个5 位的二进制加计数器,由00000 状态开始,经过75个时钟脉冲后,此计数器的状态为:(A)01011 (B)01100 (C)01010 (D)00111 11、图5.2所示为某时序电路的时序图,由此可知该时序电路具有的功能。

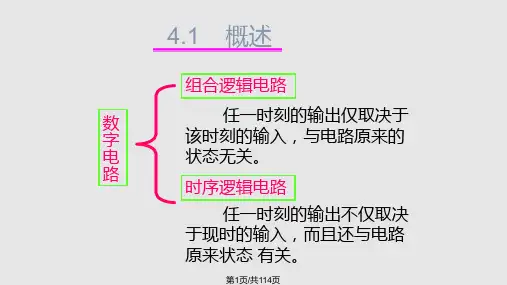

(A)十进制计数器(B)九进制计数器(C)四进制计数器(D)八进制计数器图5.2习题二5-1填空题(1)组合逻辑电路任何时刻的输出信号,与该时刻的输入信号;与电路原来所处的状态;时序逻辑电路任何时刻的输出信号,与该时刻的输入信号;与信号作用前电路原来所处的状态。

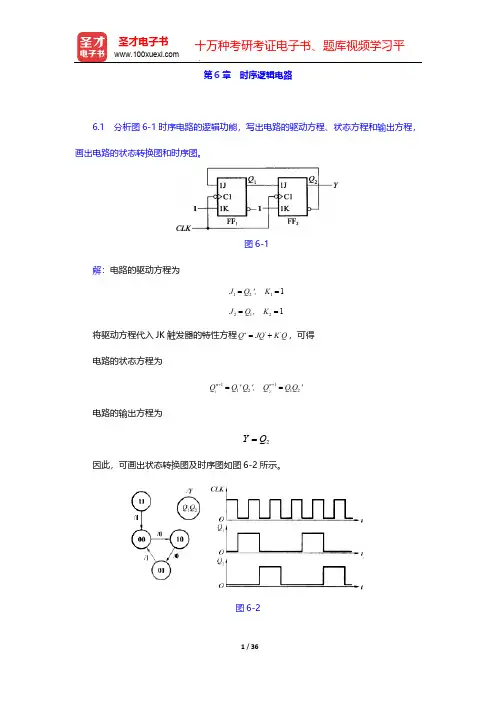

第6章 时序逻辑电路6.1 分析图6-1时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图。

图6-1解:电路的驱动方程为12121211J Q ',K J Q ,K ====将驱动方程代入JK 触发器的特性方程''Q JQ K Q *=+,可得电路的状态方程为12111212n n Q Q 'Q ',Q Q Q '++==电路的输出方程为2Y Q =因此,可画出状态转换图及时序图如图6-2所示。

图6-26.2 分析图6-3时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,并说明该电路能否自启动。

图6-3解:电路的驱动方程为1321312D Q ',D Q D Q Q ===将驱动方程代入D 触发器的特性方程Q D *=,可得电路的状态方程为1231113112n n n Q Q ',Q Q Q Q Q +++===电路的输出方程为()13Y Q 'Q '=因此,可画出状态转换图如图6-4所示,可见电路可以自启动。

图6-46.3 分析图6-5时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。

图6-5解:电路的驱动方程为11322131233J K Q ',J K Q ,J Q Q ,K Q ======将驱动方程代入JK 触发器的特性方程1''n QJQ K Q +=+,可得电路的状态方程为113131n Q Q 'Q 'Q Q +=+=Q 3⊙Q 12311212121123n n Q Q Q 'Q 'Q Q Q Q Q Q Q '++=+=⊕=电路的输出方程为3Y Q =因此,可画出状态转换图如图6-6所示,可见电路可以自启动。

图6-66.4 试分析图6-7时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,检查电路能否自启动。