模拟量采集原理图

- 格式:pdf

- 大小:21.67 KB

- 文档页数:1

TOP700G智能电力测控装置使用说明书珠海拓普智能电气有限公司©版权所有 2008Release 5.21目录第一章概述 (1)1.1 概述 (1)1.2 产品特点 (1)第二章技术指标 (3)2.1 环境要求指标 (3)2.2 技术参数 (3)2.3 精度指标 (3)2.4 接口参数 (4)2.5 绝缘电阻及介质强度 (4)2.6 机械性能 (5)2.7 抗电磁干扰(EMC)性能 (5)2.8 安装方式 (5)第三章产品结构 (6)3.1 硬件结构 (6)3.2 主控单元 (7)第四章产品功能 (10)4.1 装置功能表 (10)4.2 测量功能 (11)4.3 模拟量输出功能 (13)4.4 开关量输入 (13)4.5 开关量输出 (13)4.6 通信接口 (14)4.7 保护功能 (14)4.8 联锁控制功能 (18)4.9 装置告警 (18)4.10 事件记录功能 (19)4.11 PT、CT变比设置 (19)第五章人机界面操作说明 (20)5.1 装置面板布置图 (20)5.2 键盘说明 (20)5.3 信号灯指示说明 (21)5.4 显示菜单说明 (21)第六章用户调试细则 (35)6.1 通电前检查项目 (35)6.2 通电检查项目 (35)6.3 模拟保护试验 (36)第七章定值一览表 (37)附录A TOP700G原理接线图 (42)附录B TOP700G端子接线图 (44)附录C TOP700G外形尺寸 (50)1.1 概述TOP700G智能电力测控装置是一种数字式三相电力测控保护装置,直接针对一回线路设计,能够完成一回线路的测量、控制及辅助保护功能,具有很高的性能价格比。

TOP700G智能电力测控装置集保护、电量测量、电能计量、操作控制、诊断维护、报警输出、模拟量输出等多种功能于一体,同时可选配2个独立的RS485、CANBUS、ProfiBus通讯接口,满足双网(包括冗余)配置,并实现遥测、遥信、遥控等功能。

电力系统监控技术课程设计报告题目:牵引变电所遥信数据采集系统设计班级:姓名:学号:指导教师:设计时间:1 设计原始资料对图1提供的变电所进行远动系统模块的设计。

图1 牵引变电所所主接线1.1 具体题目说明对图1所给的变电站进行遥信数据采集系统的设计。

1.2 要完成的内容(1) 计算机绘制被控站(RTU端:变电所或开闭所或分区亭)的通用系统结构框图。

要求:绘出各种数据点的采集通道(如:模拟量输入、开关量输入、脉冲累计量输入,控制输出通道(模拟量输出、开关量输出、脉宽调制输出)的示意图。

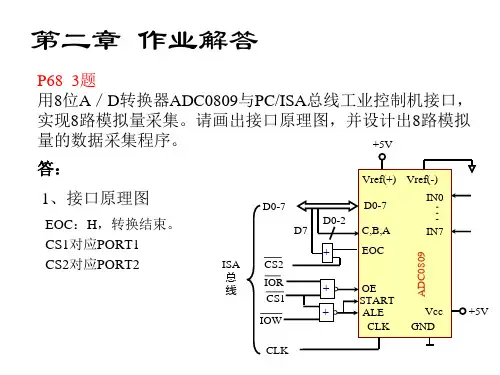

(2) 设计一个具体的MCS-51单片机数据采集最小系统(开关量输入数据,路数为16路),开关量输入数据类型为各断路器、隔离开关的状态信息(经过采集电路后的信息);要求用标准图纸,手工绘制(或专用软件protel等),具体到芯片管脚的连线。

(3) 计算机绘制(A4纸)相应的遥信数据采集程序流程图。

2 硬件设计2.1 各开关元件及数据采集点编号2.1.1 各开关元件编号为了对数量较多的开关元件进行区分以避免误操作,必须对各开关元件进行编号。

各隔离开关编号如表1所示,各断路器编号如表2所示。

表1 断路器编号开关代号开关编号QF9 00HQF10 01HQF11 02HQF12 03HQF13 04HQF14 05HQF15 06HQF16 07H2.2 被控站通用系统结构被控站是受主站监视或受主站监视且控制的站。

计算机技术进入远动技术之后,安装在被控站的远动装置被称为远动终端装置。

RTU对各种电量变送器送来的直流电压分时完成A/D转换,得到对应的二进制数值;对脉冲采集进行计数,得到与脉冲量对应的计数值;把状态量的输入状态转换成逻辑电平“0”或“1”。

将上述各种数字信息按规约编码成遥测信息字和遥信信息字向前置机传送。

被控站通用系统结构图如图1所示。

图1 被控站通用系统结构图2.2.1 数据采集通道在电力系统中,遥信信息可以表示设备的启停、断路器的投切、隔离开关的开合、告警信号的有无、保护动作与否等。

基于网络的高精度数据采集卡设计吕实诚;宋晓波;王晶【摘要】为了实现数据采集卡高精度和网络传输的要求,提出了一种基于网络的高精度数据采集卡的设计方法.硬件方面,采用ARM为主控CPU,扩展了网络接口芯片,实现了数据采集卡的网络接口功能;采用16位高精度AD转换器AD976,实现了高精确度数据采集的要求;采用FPGA内部逻辑控制AD转换器的时序和模拟开关的切换,并辅以扩展FIFO缓存采样数据的方法实现了8路模拟量的扫描测量,保证了模块的采样率;数字量测量采用光电隔离技术,保证了模块工作的可靠性;软件方面,设计了嵌入式Linux数据采集电路驱动程序和网络通信程序.实现了上位机通过网络接口对模拟量和数字量的采集功能.实际测试表明,数据采集卡采集精确度优于0.05%.%In order to achieve the requirements of high-precision and network transmission in data acquisition card,we propose a design of high-precision data acquisition card based on LAN.In terms of hardware,it uses ARM as the host CPU and expands the LAN interface chip.It achieved the features of LAN interface of data acquisition card and high-precision of data acquisition card by high-precision 16-bit AD converter AD976; by using FP-GA internal logic to control ADC for sampling and the channels for switching,supplemented by extended FIFO buffer,it achieved the 8-channels scanning measurement of analog signals and ensured the sampling rate of the module; the measurement of digital signals adopts the photoelectric isolation and ensured the reliability of the module.In terms of software,the embedded Linux driver of data acquisition circuit and the network communications application are designed.It achieved thefunction that a host computer collections analog signals and digital signals through theLAN interface.According to testing,the design of module is reasonable and meets all of the requirements.Acquisition accuracy of the data acquisition card is 0.05%.【期刊名称】《哈尔滨理工大学学报》【年(卷),期】2012(017)002【总页数】5页(P22-26)【关键词】数据采集;高精度;网络接口;FPGA;ARM【作者】吕实诚;宋晓波;王晶【作者单位】哈尔滨理工大学测控技术与通信工程学院,黑龙江哈尔滨150080;哈尔滨理工大学测控技术与通信工程学院,黑龙江哈尔滨150080;哈尔滨理工大学测控技术与通信工程学院,黑龙江哈尔滨150080【正文语种】中文【中图分类】TP274.20 引言随着电子技术的飞速发展,数据采集系统在工业控制、智能化仪器仪表、办公自动化等多领域得到极为广泛的应用.目前发达国家的数据采集系统已经在军事、航空电子设备及宇航技术、工业等领域被广泛应用,并以其高精确度采集和高速远程传输等优点取得了良好的效果[1].而国内的数据采集系统采集精确度不够高,传输方式一般采用RS422、CAN等总线[2],远程传输吞吐率低,已经不能满足发展的需要.数据采集系统正朝着高精确度、多通道、远程传输的方向发展[3-4].同时,网络通信方式以其吞吐率高、可靠性高、传输距离远等优点越来越受到重视[5].因此,研制基于网络的高精确度数据采集系统,采用高精确度ADC和网络传输方式实现数据采集,具有重要的应用价值.1 硬件设计基于网络通信的模拟量和数字量测量模块的技术要求如下:1)数字量测试技术指标:通道数:8路;输入信号幅度范围:0~15 V;输入信号频率范围:0~1 kHz;2)模拟量测试技术指标:通道数:8路;信号形式:单端或差分;满量程精确度:0.05%;最高采样速率:8通道共200 kSa/s.3)网络接口技术指标:10 Mbps以太网接口,实现与上位机通信.该数据采集卡采用模块化设计,主要包括主控CPU和网络接口部分、数据采集电路部分.主控CPU和网络接口部分实现数据采集卡与上位机的网路连接和对数据采集电路部分的管理;数据采集电路部分实现对8通道模拟量的采集功能和8通道数字量的采集功能.数据采集卡的硬件总体框图如图1所示.图1 数据采集卡总体方案1.1 主控CPU和网络接口电路考虑到ARM对网络功能的支持比较好,同时可以运行嵌入式Linux操作系统,有完善的网络协议的支持,经过比较,该数据采集卡选用三星公司的ARM9芯片S3C2410作为主控CPU,实现与上位机的网络连接和对数据采集电路的管理.主控CPU和网络接口电路原理如图2所示.图2 主控CPU和网络接口电路原理图图2中,LAN接口实现与上位机的网络物理连接,在S3C2410外部扩展CS8900网络接口芯片实现网络物理层协议和数据链路层协议;调试串口提供开发阶段嵌入式Linux的调试终端;SDRAM提供操作系统(嵌入式Linux)的运行和数据的缓存;NAND FLASH存储引导程序,Linux内核和文件系统(S3C2410支持NAND FLASH启动);本地总线实现与数据采集电路部分的接口.主控CPU和网络接口电路部分通过本地总线接口实现对数据采集电路部分的管理和控制.1.2 数据采集电路该数据采集卡要求实现8路模拟量采集和8路数字量采集,现在分别对这两部分进行说明.1.2.1 模拟量采集电路模拟量采集要求信号输入范围-15~+15 V,最高采样率100 k/s,采样精确度0.05%.S3C2410片内集成10位ADC模块,不能满足精度要求,需外扩16位A/D转换器AD976[6],配以高速模拟开关(ADG507)进行通道切换实现8通道高精度模拟量采集.为满足采样速度要求,采用FPGA逻辑控制AD转换和通道切换.模拟量采集电路原理框图如图3所示.模拟量测量电路工作原理如下:8路被测模拟量经前端的信号调理,以适应模拟开关的输入电压范围.通过高速模拟开关选出一路,经后端信号调理后送入A/D转换器进行模数转换.通过FPGA内部逻辑协调通道切换和A/D转换器的转换时序,将A/D的采样数据暂存于FPGA内部FIFO缓冲区中,以免每次A/D转换完成后都需ARM读取采样数据,这样可提高采样速率,减轻 ARM 的负担[7].当FIFO 达到一定存储容量时由ARM读出FIFO中数据,通过网络接口发送到上位机.FPGA在模拟量测量中主要完成功能有:地址译码、AD时序控制、通道切换和数据缓冲.图3 模拟量采集电路原理图1.2.1.1 前端信号调理设计模拟量输入信号范围为-15~+15 V,没有超出模拟开关的输入电压范围,故前端信号调理电路只需要实现低通滤波,使ADC采集输入信号时满足采样定理.前端信号调理电路如图4所示.图4 前端信号调理电路图4中,低通滤波电路采用简单的RC滤波,电路简单,成本低,能够满足要求.低通滤波器的截止频率由上式可以得出,输入测量通道的信号A/D采样时满足采样定理,该低通滤波器满足要求.电路中D1、D2、D3、D4为4个16 V的稳压二极管,主要起保护作用,当输入信号超出范围时,四个稳压二极管将输入到后端的电压钳位在-16 V或+16 V,使后端电路免于损坏.1.2.1.2 模拟开关、后端信号调理经前端信号调理电路的处理后,被测信号范围为-15~+15 V.本模块选择AD公司的模拟开关ADG507A切换模拟通道.ADG507A采用+15 V和-15 V双电源供电,输入信号范围-15~+15 V,导通电阻典型值为280 Ω.为达到测量精确度的要求,选用OP275(输入端采用JFET结构,输入电阻10 M以上)做成的电压跟随器来实现阻抗匹配,以拉高多路模拟开关的负载阻抗,削弱串联模拟开关导通电阻分压作用对模块测量精度的影响.本模块选用AD976作为AD转换器.该A/D转换器单端输入,其信号输入范围-10~+10 V.故此部分电路需加入差分转单端电路和信号衰减电路.综合以上分析,后端信号调理电路主要由电压跟随器、差分转单端电路和信号衰减电路三部分组成,具体实现如图5所示.图5中,+VO和-VO是经模拟开关选出的一个测量通道.左侧的运放OP275及其外围电路组成电压跟随器,实现阻抗匹配.右侧的运放OP275及其外围电路组成差分比例运算电路,实现差分变单端和信号衰减;两个15k电阻和两个10k电阻需使用0.05%的精密电阻保证采样精确度,该电路衰减倍数为1.5,将范围为-15~+15 V的被测信号衰减为-10~+10 V,可直接输入到AD976进行采样.图5 后端信号调理电路1.2.1.3 FPGA内部逻辑设计FPGA内部逻辑设计方案如图6所示.图6 FPGA内部逻辑设计方案(模拟量采集部分)FPGA内部逻辑包括以下几个部分:1)地址译码逻辑产生ARM访问FPGA内部各个寄存器地址,主要寄存器如下:ARM-RST信号:FPGA软件复位寄存器;ARM-SET信号:模拟量测量模式寄存器;CNT-CS信号:AD采样率寄存器;STR-CH信号:顺次扫描开始通道寄存器;END-CH信号:顺次扫描结束通道寄存器;FIFO-RD信号:FIFO数据寄存器.2)模拟开关切换时钟和ADC采样控制时钟产当写入到CNT-CS的值为300时,AD976采样率为200 kSa/s,当写入到CNT-CS的值大于300时,AD976采样率小于200 kSa/s.3)模拟开关通道选通逻辑实现在模拟开关切换时钟的控制下,将模拟开关切换到下一个预设通道,为ADC采样下一个通道的数据做好准备.为了增加灵活性,设计了两种模拟开关扫描方式,顺次通道扫描和预设通道扫描.4)FIFO缓冲逻辑实现A/D采样数据的缓冲和ARM对缓冲数据的读取.使用1k×16bit同步FIFO作为AD采样数据的缓冲区,设置FIFO半满为512字,FIFO半满信号作为 ARM 的中断信号,用AD采样完成信号(AD-BUSY)控制AD采样数据写入FIFO,用FIFO读信号(FIFO-RD)控制FIFO数据读出.1.2.2 数字量采集电路数字量采集要求输入信号幅度范围0~+15 V,频率范围:0~1 kHz.采用光电隔离和三态缓冲器配合实现数字量的采集.光电隔离器选择TLP521,该器件的响应时间为4 μs,即响应速度250 kHz>信号频率1 kHz,满足设计要求.三态缓冲器在FPGA内部实现,增加了设计的灵活性.数字量采集电路原理图如图7所示.生逻辑该部分逻辑产生模拟开关的切换时钟和ADC采样控制时钟.时钟周期由A/D采样率寄存器(对应CNT-CS译码信号)设置,时钟周期=A/D采样寄存器值*FPGA时钟周期.由于AD976最高采样率为200 kSa/s,即AD-SAMPLE的最高频率为200 kSa/s,FPGA时钟频率为60 MHz,写入到A/D采样率寄存器的最小值为图7 数字量采集电路原理图8 路待测数字量经过光电隔离,以减小输入端的干扰;将隔离后的数字量输入到FPGA内部三态缓冲器,即数字IO状态寄存器,ARM通过读取数字IO状态寄存器获取输入数字量的状态.2 软件设计2.1 驱动程序设计数据采集卡是以ARM为核心的,其内部运行嵌入式Linux系统.对于嵌入式Linux 系统,对硬件的访问是通过驱动程序实现的.Linux设备主要分为3个基础大类:字符设备,块设备和网络设备[8].ARM访问的数据采集电路属于字符设备,其驱动程序结构如图8所示.图8 本地接口寄存器设备驱动程序该数据采集电路驱动程序可以直接编译进内核,也可以编译成模块通过insmod 命令加载.为了调试方便,将该驱动程序编译为模块,init和exit方法在模块的加载和卸载时被调用.数据采集电路驱动程序在init方法中完成中断的注册和寄存器地址的映射.该驱动程序主要有 open、release、ioctl、fasync方法和中断处理interrupt、open和release方法负责设备的打开和关闭,该驱动程序读写寄存器实现方法在ioctl中完成,对FIFO向ARM申请的中断在中断处理中完成,fasync方法实现驱动程序的异步通知机制.当FIFO中断产生后,在驱动程序的中断处理函数中使用异步通知机制发送SIGIO信号到应用程序,通知应用程序读取FIFO中的数据.ioctl方法实现对各个寄存器的读写,完成对数据采集电路的设置和读取测量结果的功能.2.2 应用程序设计嵌入式Linux网络通信应用程序实现上位机与数据采集卡通过网络接口进行数据交互,采用TCP协议实现保证通信的可靠性.该数据采集卡和上位机使用Server-Client模式通信[9],即在数据采集卡的嵌入式Linux操作系统中运行TCP服务器,在上位机运行TCP客户端.网络通信应用程序流程图如图9所示.图9 嵌入式Linux网络通信应用程序流程图图9网络通信程序中,首先建立TCP服务器并打开数据采集电路设备文件,接着等待上位机客户端的连接,当上位机TCP客户端连接到TCP服务器后,网络通信程序等待接收上位机发送的命令和参数,并根据命令和参数完成相应的数据采集任务.上位机发送的命令主要有两个:命令1实现模拟量的采集,首先设置模拟量采集的参数:采样率、模拟开关扫描方式及扫描参数等,然后启动ADC开始采样.采样数据会缓存于FIFO中,当FIFO中断产生后,网络通信程序会接收到驱动程序发送的信号,在信号处理函数中调用驱动程序中ioctl方法,读取FIFO中的ADC采样数据,并将采样数据通过网络接口发送到上位机.命令2实现数字量的采集,通过读取数字IO状态寄存器得到被测数字量的状态并将测量结果通过网络接口发送到上位机.3 测试为了测试数据采集卡的采样精度指标,在数据采集卡的输入端分别加 -15 V、-5 V、0 V、5 V、15 V电压,通过网络通信将测试数据传输到上位机,测试结果如表1所示.表1 数据采集卡采集精度测试数据输入电压/V 输入方式 8通道的最大误差/V 测试结果-14.999 差分 0.003 6满足要求-5.000 8 差分 0.004 6 满足要求-0.002 单端 0.003 7 满足要求4.998 0 单端 0.004 5 满足要求15.000 差分 0.005 9满足要求模拟量测量满量程精确度要求为0.05%,最大允许误差为30×0.05%=0.015 V.由表1得,数据采集卡满足精确度要求.4 结语本文介绍了基于网络的高精度数据采集卡的设计.采用基于ARM的嵌入式系统技术,设计了数据采集卡的网络接口,开发了网络通信程序,实现了数据采集卡的网络通信功能;采用FPGA逻辑控制高精确度A/D转换和通道切换,实现了8通道高精确度模拟量采集;采用光电隔离技术,实现了8通道数字量采集.实际测试表明,数据采集卡采集精确度0.05%,采样率200kSa/s,满足设计要求.参考文献:【相关文献】[1]邹卫华,尹宁宁.基于LabVIEW的远程数据采集的实现[J].哈尔滨理工大学学报,2008,13(6):87-90.[2]张铭钧,董振刚,张丙良.潜油电泵机组及井下传感器状态监测技术研究[J].电机与控制学报,2009,13(1):28-31.[3]李岩,崔鹏,李晓薇,等.基于uCLinux的嵌入式实时远程数据采集系统[J].哈尔滨理工大学学报,2006,11(3):114-117.[4]庞晓晖,胡修林,张蕴玉,等.高速数据采集系统的设计与实现[J].仪器仪表学报,2000,21(3):297-299.[5]杜中平,林克正,黄凌碧.基于ADuC7026的网络化数据采集系统设计[J].哈尔滨理工大学学报,2006,11(2):80-82.[6]Analog Devices Inc.16Bit,200ksps BiCMOS A/D Converter AD976a[S].USA,Analog Devices Inc.1999.[7]WANG Xu-ying,LU Ying-hua,ZHANG Li-kun.Design and Implementation of High Speed Real-time Data Acquisition System based on FPGA[J].The Journal of China Universities of Posts and Telecommunications,2006,11:61-66.[8]李亚峰,欧文盛.ARM嵌入式Linux系统开发从入门到精通[M].清华大学出版社,2007:110-111.[9]胡冠山,李作纬,刘后毅.嵌入式网络仪器的设计和实现[J].仪表技术与传感器,2006,12:25-27.。

单片机开发与设计工程师考试文档学校:湖南人文科技学院题目:4路模拟信号采集系统学生姓名: 陈自斌易颂文起止日期:2010-6-15~2010-6-25摘要本次设计是建立一个四路模拟信号采集系统,能处理模拟信号(0~5V),同时对信号进行循环采样并通过键盘控制输出。

它主要由A/D转换模块、单片机、显示模块、控制器模块组成。

其中最主要的部分是单片机和A/D转换器,首先被测模拟信号通过A/D转换器转换成数字信号,然后通过单片机的处理,在数码管上不停的显示4路的采样数据,通过的给一个控制信号,可以选择的任意一路信号在数码管上面输出显示。

关键词:A/D转换模块;单片机;控制模块目录设计要求 (1)1、方案 (1)2、单元电路设计 (2)2.1A/D转换模块 (2)2.2单片机 (3)2.3显示模块 (3)2.4控制模块设计 (4)3、系统软件设计 (5)3.1系统工作流程 (5)4、总原理图 (5)5、调试结果及分析 (6)7、详细仪器清单 (7)参考文献 (8)附录 (9)4路模拟信号采集系统设计要求1.4路模拟量输入,范围0-5V;2.对4个通道的模拟量进行巡回采样,再将采集的数据进行工程量转换;3.能通过按键切换所选通道;4.数据在LED显示器上显示,并能够通过键盘操作切换显示不同通道的采样值。

1、方案此方案以单片机STC89C52为核心,对四路模拟信号进行循环采样输出。

首先,信号通过一个A/D转换模块把模拟信号转换成数据信号,在通过STC89C52和8255的控制,由按键控制选择一路信号在LED数码管上显示。

4路模拟信号采集系统原理框图如图1所示:图1 系统方框图2、单元电路设计2.1 A/D转换模块A/D转换模块我们采用的ADC0809芯片,设有一路信号巧(0V~5V)从ADC0809的INo通道输入,地址输人端A、B、C均接地,这时1No的通道地址为OOH。

0809W、RD共同组成是8位ADC,对0V~,5V的信号,其转换精度为20mV/级。

3)I/O端的接线输入接线● 输入接线一般不要太长。

但如果环境干扰较小,电压降不大时,输入接线可适当长些。

● 输入/输出线不能用同一根电缆,输入/输出线要分开。

● 尽可能采用常开触点形式连接到输入端,使编制的梯形图与继电器原理图一致,便于阅读。

输出连接● 输出端接线分为独立输出和公共输出。

在不同组中,可采用不同类型和电压等级的输出电压。

但在同一组中的输出只能用同一类型、同一电压等级的电源。

● 由于PLC的输出元件被封装在印制电路板上,并且连接至端子板,若将连接输出元件的负载短路,将烧毁印制电路板。

● 采用继电器输出时,所承受的电感性负载的大小,会影响到继电器的使用寿命,因此,使用电感性负载时应合理选择,或加隔离继电器。

● PLC的输出负载可能产生干扰,因此要采取措施加以控制,如直流输出的续流管保护,交流输出的阻容吸收电路,晶体管及双向晶闸管输出的旁路电阻保护。

(4)正确选择接地点,完善接地系统良好的接地是保证PLC可靠工作的重要条件,可以避免偶然发生的电压冲击危害。

接地的目的通常有两个,其一为了安全,其二是为了抑制干扰。

完善的接地系统是PLC控制系统抗电磁干扰的重要措施之一。

PLC控制系统的地线包括系统地、屏蔽地、交流地和保护地等。

接地系统混乱对PLC系统的干扰主要是各个接地点电位分布不均,不同接地点间存在地电位差,引起地环路电流,影响系统正常工作。

例如电缆屏蔽层必须一点接地,如果电缆屏蔽层两端A、B都接地,就存在地电位差,有电流流过屏蔽层,当发生异常状态如雷击时,地线电流将更大。

此外,屏蔽层、接地线和大地有可能构成闭合环路,在变化磁场的作用下,屏蔽层内又会出现感应电流,通过屏蔽层与芯线之间的耦合,干扰信号回路。

若系统地与其它接地处理混乱,所产生的地环流就可能在地线上产生不等电位分布,影响PLC内逻辑电路和模拟电路的正常工作。

PLC工作的逻辑电压干扰容限较低,逻辑地电位的分布干扰容易影响PLC的逻辑运算和数据存贮,造成数据混乱、程序跑飞或死机。