[整理]IC项目单6.

- 格式:doc

- 大小:87.50 KB

- 文档页数:8

任务四功率放大电路的安装、调试与检修【学习目标】1.掌握功率放大器的原理。

、2. 掌握PCB电路板的制作2.掌握0TL功率放大器的安装与调试。

【任务导入】功率放大器的作用是对信号进行一个功率放大的作用,主要是将音源器材输入的较微弱信号进行放大后,产生足够大的电流去推动扬声器进行声音的重放。

功放的应用很广泛,例如在体育馆场、影剧场、会议厅或其它公共场所的扩声,家庭、汽车音响等生活中很多地方都有用到。

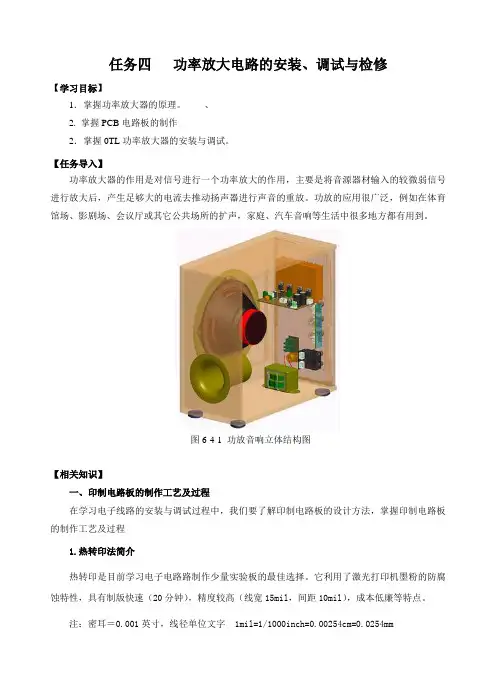

图6-4-1 功放音响立体结构图【相关知识】一、印制电路板的制作工艺及过程在学习电子线路的安装与调试过程中,我们要了解印制电路板的设计方法,掌握印制电路板的制作工艺及过程1.热转印法简介热转印是目前学习电子电路路制作少量实验板的最佳选择。

它利用了激光打印机墨粉的防腐蚀特性,具有制版快速(20分钟),精度较高(线宽15mil,间距10mil),成本低廉等特点。

注:密耳=0.001英寸,线径单位文字 1mil=1/1000inch=0.00254cm=0.0254mm2.设计布线规则由于热转印制版的特点,在布线时要注意以下方面:(1)线宽不小于15mil,线间距不小于10mil。

为确保安全,线宽要在25~30mil,大电流线按照一般布线原则加宽。

导线间距要大于10mil,焊盘间距最好大于15mil。

(2)尽量布成单面板,无法布通时可以考虑跳接线。

仍然无法布通时可以考虑使用双面板,但考虑到焊接时要焊两面的焊盘。

尽量使用手工布线,自动布线往往不能满足要求。

(3)有0.8mm孔的焊盘要在70mil以上,推荐80mil。

否则会由于打孔精度不高使焊盘损坏。

(4)孔的直径可以全部设成10~15mil,不必是实际大小,以利于钻孔时钻头对准。

3.打印打印前先进行排版,把要打的图排满一张A4纸,越多越好。

因为有些图打出来是坏的,我们需要从中选一张好的来转印,然后打印在热转印纸的光面。

(注意:只能用激光打印机打印!不能用喷墨打印机)如果打印出的线路不够黑(在打印选项中若有浓度选项要将之调到最大即最黑)。

二次外协产品清单(原创版)目录1.引言2.产品清单概述3.产品清单详细内容4.结论正文【引言】随着制造业的发展,二次外协产品的需求日益增长。

为了满足生产需要,我们整理了一份二次外协产品清单,以便于进行采购和管理。

本文将对该清单进行详细介绍。

【产品清单概述】二次外协产品是指在生产过程中需要委托外部供应商加工制作的产品。

这些产品通常是半成品或成品,用于满足生产流水线的需求。

二次外协产品清单主要包括以下几类:1.金属制品:包括各种材质的金属板材、管材、型材等;2.塑料制品:如尼龙、ABS、PC 等材质的板材、管材等;3.橡胶制品:如橡胶垫、橡胶管、橡胶 O 型圈等;4.电子元器件:如 IC 芯片、二极管、三极管等;5.标准件:如螺栓、螺母、垫圈等;6.其他辅助材料:如油漆、胶水、润滑油等。

【产品清单详细内容】以下是二次外协产品清单的详细内容:1.金属制品:(1)不锈钢板:304、316 等材质,厚度 0.5-100mm,宽度 100-2000mm;(2)铝板:6061、6063 等材质,厚度 0.5-200mm,宽度 100-3000mm;(3)铜板:黄铜、红铜等材质,厚度 0.5-100mm,宽度 100-2000mm;(4)管材:不锈钢管、铝管、铜管等,规格Φ10-Φ500,壁厚 0.5-20mm;(5)型材:角钢、槽钢、工字钢等,规格 50-500mm,厚度 1-20mm。

2.塑料制品:(1)尼龙板:尼龙 6、尼龙 66 等材质,厚度 0.5-100mm,宽度100-2000mm;(2)ABS 板:厚度 0.5-100mm,宽度 100-2000mm;(3)PC 板:厚度 0.5-100mm,宽度 100-2000mm;(4)管材:尼龙管、ABS 管、PC 管等,规格Φ10-Φ500,壁厚 0.5-20mm;(5)板材:聚四氟乙烯板、酚醛板等,厚度 0.5-100mm,宽度100-2000mm。

TEA2025一.简介1)TEA2025是欧洲生产的双声道功率放大集成电路,该电路具有声道分离度高、电源接通时冲击噪声小、外接元件少,最大电压增益可由外接电阻调节等特点,应用于袖珍式或便携式立体声音响系统中作功率放大。

2)TEA2025的内电路方框图及引脚功能是欧洲生产的双声道功率放大集成电路,该电路具有声道分离度高、电源接通时冲击噪声小、外接元件少,最大电压增益可由外接电阻调节等特点,应用于袖珍式或便携式立体声音响系统中作功率放大。

3)原理图组成TEA2025集成块内部主要由两路功能相同的音频预放、功放、去耦、驱动电路、供电电路等组成,其集成块的内电路方框图及双声道应用电路如图所示。

该IC采用16脚双列直插式封装。

4)TEA2025双声道音频功率放大集成电路,该电路的赋性如下任务电源电压规模为3-一2V,其输出功率由垄断电源电压和负载而定P=0.1W 2VCC=3V RL=4ΩP=一W 2VCC=6V RL=2ΩP=2.3W 2VCC=9V RL=4Ω实用于单声道桥式BTL 或平面声行程两种任务外形。

它还存在外接元件少声道皋牢度高爆破噪声少电压增益可由外接电阻调节等赋性,采纳双列直插一 6 脚塑料封装DIP一6。

二.2025的内电路方框图及引脚功能1.TEA2025主要电参数(1)极限使用条件。

在T.=25 -C时,电源电压Vcc=15 V.输出峰值电流10=1.5A。

(2)主要电参数。

TEA2025集成电路工作电源电压范围为3--12 V.典型工作电压6-9 V。

在Vcc=9 V, RL=8。

Ta=25℃条件下,有以下主要电参数。

.静态电流ICQ 最大值为50 mA,典型值为40 mA。

.电压增益GV 双声道时的最大值为47 dB,最小值为43 dB,典型值为45 dB; BTL时的最大值为53 dB,最小值为49 dB,典型值为51 dB。

.输出功率PO 当THD=10%,P=1 kHz时,双声道时的典型值为1.3 W, BTL时的典型值为4.7 W。

基准收益率的计算KKlo69-0TM243-0LUll 29-G(X)I-FDQS58文稿归稿存档编号JKKUY-基准收益率的计算在按时价计算和收入的情况下,基准的计算可归纳如下:ic = (l +ii)(l +i2)(l +i3)1式中:ic为基准;h为年资金费用率与之高者;乙为年贴现率;h为年。

在i】、狂、L都为小数的情况下,上述可简化为:ic = 11 + 12 + is在按计算和收入的情况下,不用考虑,则:i c = (1 + iι) (1 + i:)1由上可知,基准是由多种因素决定的,是随上述诸因素的变化而变化的,基准收益率的确定具有一定的难度。

但基准的大小则是采用的关键,它决定了的取舍。

因此,作为投资者来讲应慎重确定基准的大小。

项目财务基准收益率(IC)是项目财务内部收益率指标的基准判据,也是项目在财务上是否可行的最低要求,还是用作计算财务净现值的折现率。

因此,财务基准收益确定的是否合理,对决策项目在财务上是否可行至关重要。

如把该值确定过髙,就有可能把一些本来在财务上合理的项目以财务评价不可行而拒之;反过来如果把该值确定过低,又有可能把一些财务上不具备生存能力的项目放行,造成投资的损失和浪费。

对财务基准收益率设立的原则规定:如果有行业发布的本行业基准收益率,即以其作为项目的基准收益率;如果没有行业规定,则由项目评价人员设定。

设定方法:一是参考本行业一定时期的平均收益水平并考虑项目的风险系数确定;二是按项目占用的资金成本加一定的风险系数确定。

推荐确定原则如下:1•对于以国家投入为主,以满足整个国民经济发展需求,社会效益十分显着的大型能源交通、基础设施、社会公益项目,可以仅考虑项目的融资成本,把项目的融资成本作为项目的财务基准收益率的确定依据。

对于以上不以国家投入为主,而其它形式投资的公益项目则应在融资成本加一定的风险系数确定,建议风险系数取1至2个百分点。

2.对于为市场提供产品的一般项目,在确定财务基准收益率时,三个因素都要包括。

Sigma‐Delta Modulator李福乐清华大学微电子所Sigma‐Delta Modulator•Principle•Architecture•Circuit non‐idealities•Sigma‐Delta ConverterExample: DAC Design–AudioPrincipleH ()()()()()()z Q z H z X z H z z Y +++=111312+L M π])()12([log 10⋅+⋅=L S 三部曲☺Sigma‐Delta Modulator•Principle•Architecture•Circuit non‐idealities•Sigma‐Delta ConverterExample: DAC Design–AudioArchitectures for high SNR•Low order, single loop, single bit–高过采样率,稳定,简单•High order, single loop, single bit –稳定性问题,输入信号幅度受限稳定性问题输入信号幅度受限•MASH–稳定,对匹配要求高•Multi bit–D/A线性问题,可校准或DEMSingle ‐loop, single bitg p,g ()()()()z E z z X z z Y 111−−−+=1阶调制器,patterns in spectrum ,不用在第一级2阶、3阶用得比较多阶对稳定性()()()()z E zz X z z Y 2121−−−+=2阶调制器多,4阶对稳定性要仔细考虑,建议用MASH 结构来实现第一个积分器是最重()()()()z E zz X z z Y 3131−−−+=3阶调制器要的,后续积分器误差可被noise shaping()()()()z E zz X z z Y 4141−−−+=4阶调制器vsSNR vs. OSR高阶可用MASH结构考虑电容匹配问题窄带应用可考虑用低阶结构,采用高的OSR第一积分器是最重要的,后续积分器误差可被noise shaping ()请推导传输函数,并分析电容失配效应?vs single Multi‐bit vs. ‐bit‐Full feedforward architecture4th‐Order single‐bit 1 MS/s sigma‐delta ModulatorComparison PerformanceSwing Integrators Output ofCircuit reliazationMeasured resultsSigma‐Delta Modulator•Principle•Architecture•Circuit non‐idealities•Sigma‐Delta ConverterExample: DAC Design–AudioCircuit non‐idealities•Sampling clock jitter•Switch thermal noise•Nonlinear switch Ron•Opamp noisep p•Opamp finite gain•Opamp nonlinearityg1g第一积分器是最重要的,后续积分器误差可被noise shaping第积分器是最重要的后续积分器误差可被i h iIncomplete Charge Transfer (有损积分器))zOpamp settlingNo SR limited:线性建立,no SR limited,With SR limited:建立误差可假设为白噪声若SR limited ,则可能会引入与输入相关的增益误差,表现为失真,主要是HD3,HD5F Medeiro et al –Induced ‐F. Medeiro, et, al. Modeling Opamp Induced Harmonic Distortion for Switched Capacitor Σ‐ΔModulator Design. ISCAS 94.Opamp settling线性建立,no SR limited,建假设为噪声建立误差可假设为白噪声足够的SR可采用Class AB放大器Opamp nonlinearity31Other nonlinearities•电容电压系数–C(v) ~= C0(1+kv*v) kv<<1 for MIM, MOM, PIP–HD2 ~= (1/2)kv*A for single‐end circuitry–HD2 ~= 0 for fully‐differential circuitry–MOS CAP不适合于做高精度工作电容•采样开关非线性Ron–与输入电压相关的导通电阻,带来与输入相关的电荷注入误差–即使低频输入也存在–Solution: bootstrapped sampling switchGAIN–Offset可被积分器DC 抑制–Hysteresis:•Sampling clock jitter考虑第一个积分器;分器都可被过采样系数抑制Sigma‐Delta Modulator•Principle•Architecture•Circuit non‐idealities•Sigma‐Delta ConverterExample: DAC Design–Audio/22oversampling Noise shapingSigma‐Delta ADCSigma‐Delta DAC练习:画出各节点功率谱示意图练习画出各节点功率谱示意图4 Class D DriverFrequency (Normalized Frequency (1116+Z 1-z 1-z -1128fs28128fs MSB 16128fs设计指标SNR, OSR 调制器设计流程SL/MASH 结构选择由噪声指标设计电容值CRFB/CIFF M/B synthesizeNTF kT/C=?%NTF 综合系数映射电路建模仿真y realizeNTF stuffABCD Finite gain Limited BW, SR 动态范围系数标定scaleABCD mapABCD SR, …OTA,系数量化电路设计与仿真根据电容版图要求Comparatoe Input Switch …M t hi 后端设计calculateTF simulateSNR Matching Isolation …行为仿真验证simulateDSM基于MATLAB TOOLBOX developed by Richiard Schreier一个三阶个三阶SDM 例子SPEC:系数:a [249294271]基于MATLABSNR——>90dB OSR——128采用单环单比特三阶调制器a——[2.49, 2.94, 2.71]b——[0.32, 0, 0, 1]g ——[0.0022][032030017]TOOLBOX 的设计三阶低通”CIFF”调制器结构c ——[0.32, 0.30, 0.17]阶低调制结构SDM Testbench3阶调制器电路级模型第一级积分器第级积分器第二级积分器第三级积分器开关电容求和与A/D 开关容求和与/利用开关电容电路进行采样和电荷共享,根据电荷守恒关系可实现比例求和功能根据电荷守恒关系,可实现比例求和功能,省去了一个专门的开关电容比例求和放大器电路运放模型全差分单级结构具备共模反馈跨导可调整增益可调整第一级噪声最关键采样相:121C kT Vni =28ieq kT dVNF df =⋅⋅对folded ‐cascode opa:运放输入端等效噪声:放大相:mn mp g g NF ++=13qmig ⎟⎟⎠⎞⎜⎜⎝⎛++⋅⋅=pi LeffieqC C C C NF C kT V212232mimig g ()pipi po Leff C C C C C C C C ++++=2112输入端总噪声:k ⎛2kT⎞优化噪声优化噪声:1)增大栅面积;2)提高输入跨导。

CH11.按规模划分,集成电路的发展已经经历了哪几代?它的发展遵循了一条业界著名的定律,请说出是什么定律?晶体管-分立元件-SSI-MSI-LSI-VLSI-ULSI-GSI-SOC。

MOORE定律2.什么是无生产线集成电路设计?列出无生产线集成电路设计的特点和环境。

拥有设计人才和技术,但不拥有生产线。

特点:电路设计,工艺制造,封装分立运行。

环境:IC产业生产能力剩余,人们需要更多的功能芯片设计3.多项目晶圆(MPW)技术的特点是什么?对发展集成电路设计有什么意义?MPW:把几到几十种工艺上兼容的芯片拼装到一个宏芯片上,然后以步行的方式排列到一到多个晶圆上。

意义:降低成本。

4.集成电路设计需要哪四个方面的知识?系统,电路,工具,工艺方面的知识CH21.为什么硅材料在集成电路技术中起着举足轻重的作用 ?原材料来源丰富,技术成熟,硅基产品价格低廉2.GaAs和InP材料各有哪些特点? P10,11 3.怎样的条件下金属与半导体形成欧姆接触?怎样的条件下金属与半导体形成肖特基接触?接触区半导体重掺杂可实现欧姆接触,金属与掺杂半导体接触形成肖特基接触4.说出多晶硅在CMOS工艺中的作用。

P13 5.列出你知道的异质半导体材料系统。

GaAs/AlGaAs, InP/ InGaAs, Si/SiGe, 6.SOI材料是怎样形成的,有什么特点?SOI绝缘体上硅,可以通过氧隔离或者晶片粘结技术完成。

特点:电极与衬底之间寄生电容大大减少,器件速度更快,功率更低7. 肖特基接触和欧姆型接触各有什么特点?肖特基接触:阻挡层具有类似PN结的伏安特性。

欧姆型接触:载流子可以容易地利用量子遂穿效应相应自由传输。

8. 简述双极型晶体管和MOS晶体管的工作原理。

P19,21CH31.写出晶体外延的意义,列出三种外延生长方法,并比较各自的优缺点。

意义:用同质材料形成具有不同掺杂种类及浓度而具有不同性能的晶体层。

外延方法:液态生长,气相外延生长,金属有机物气相外延生长2.写出掩膜在IC制造过程中的作用,比较整版掩膜和单片掩膜的区别,列举三种掩膜的制造方法。

光刻三要素光刻三要素】光刻三要素:光刻胶、掩膜版和光刻机光刻胶又叫光致抗蚀剂,它是由光敏化合物、基体树脂和有机溶剂等混合而成的胶状液体光刻胶受到特定波长光线的作用后,导致其化学结构发生变化,使光刻胶在某种特定溶液中的溶解特性改变正胶:分辨率高,在超大规模集成电路工艺中,一般只采用正胶负胶:分辨率差,适于加工线宽≥3微米的线条IC业界名词解释IC业界名词解释芯片我们通常所说的"芯片"是指集成电路,它是微电子技术的主要产品.所谓微电子是相对"强电"、"弱电"等概念而言,指它处理的电子信号极其微小.它是现代信息技术的基础,我们通常所接触的电子产品,包括通讯、电脑、智能化系统、自动控制、空间技术、电台、电视等等都是在微电子技术的基础上发展起来的.我国的信息通讯、电子终端设备产品这些年来有长足发展,但以加工装配、组装工艺、应用工程见长,产品的核心技术自主开发的较少,这里所说的"核心技术"主要就是微电子技术.就好像我们盖房子的水平已经不错了,但是,盖房子所用的砖瓦还不能生产.要命的是,"砖瓦"还很贵.一般来说,"芯片"成本最能影响整机的成本.微电子技术涉及的行业很多,包括化工、光电技术、半导体材料、精密设备制造、软件等,其中又以集成电路技术为核心,包括集成电路的设计、制造.集成电路(IC)常用基本概念有:晶圆,多指单晶硅圆片,由普通硅沙拉制提炼而成,是最常用的半导体材料,按其直径分为4英寸、5英寸、6英寸、8英寸等规格,近来发展出12英寸甚至更大规格.晶圆越大,同一圆片上可生产的IC就多,可降低成本;但要求材料技术和生产技术更高.前、后工序:IC制造过程中, 晶圆光刻的工艺(即所谓流片),被称为前工序,这是IC制造的最要害技术;晶圆流片后,其切割、封装等工序被称为后工序.光刻:IC生产的主要工艺手段,指用光技术在晶圆上刻蚀电路.线宽:4微米/1微米/0.6微未/0.35微米/035微米等,是指IC生产工艺可达到的最小导线宽度,是IC工艺先进水平的主要指标.线宽越小,集成度就高,在同一面积上就集成更多电路单元.封装:指把硅片上的电路管脚,用导线接引到外部接头处,以便与其它器件连接.存储器:专门用于保存数据信息的IC.逻辑电路:以二进制为原理的数字电路。

通用IC进料检验规范1. 目的规范IC类检验标准,为IQC检验IC提供方法和判定依据。

2. 范围适用于IQC对IC进行来料检验。

3. 使用仪器和设备游标卡尺、放大镜、电烙铁;4.抽样方案按MIL-STD-105E LEVEL-II一般正常单次抽样:重0.65、轻微 2.5。

原则上:凡用于真空完全密闭方式包装的IC,由于管理与防护的特殊要求不能现场打开封装的,IQC仅进行包装检验。

对于有特别要求的拆开检查的,其中尺寸检查采用每批抽样N=5,C=0的特检方式进行检查;检查完后,及时真空包装。

5.判定条件5.1:目视距离约30cm,任何角度。

5.2:扫视时间5秒/次左右,自然光或灯光下。

6.检验方法6.1外观:用目测法,将实体与图纸或样品相比较,观察实体的颜色、光洁度等是均能与样品相符。

6.2尺寸:用适当的量具检测其尺寸或通过试装的方法检查。

6.3包装:目测法7.缺陷分类检验项目缺陷内容缺陷分类A B C外观1.IC表面字印与承认规格不符。

2.IC表面字印模糊、脱落,影响识别。

3.IC表面有气泡,凹凸不平。

4.IC表面有裂痕,损伤。

5.IC“第一管脚”标识位置错误或漏标。

图-16.IC“标识缺口”标识错误或漏标。

7.IC引脚断裂。

8.IC引脚弯曲变形。

9.引脚与塑封件之间的粘接不固定,松动。

10.脚与塑封件之间的粘接处有裂口或裂纹。

11.引脚明显氧化发黑。

√√√√√√√√√√√尺寸引脚尺寸与承认样板或规格书不符。

√包装1.无标识(内、外包装都需要标识)2.标识错误(如代码错误或者标识不全)3.产品混装(不同产品混在一起)4.未按指定材料包装5.包装材料破损6. SMD件排列方向需一致。

7.盘装物料不允许有中断少数现象√√√√√√√8.封装图示:第一引脚图-1编制:审核:批准:。

建设投资估算表(概算法)

人民币单位:万元,外币单位:

建设投资估算表(形成资产法)

人民币单位:万元,外币单位:

建设期利息估算表

人民币单位:万元

流动资金估算表

人民币单位:万元

项目总投资估算汇总表

人民币单位:万元,外币单位:

分年投资计划表

人民币单位:万元,外币单位:

营业收入、营业税金及附加和增值税估算表

人民币单位:万元

总成本费用估算表(生产成本加期间费用法)

人民币单位:万元

总成本费用估算表(生产要素法)

人民币单位:万元

借款还本付息计划表

人民币单位:万元

项目投资现金流量表

人民币单位:万元

项目资本金现金流量表

人民币单位:万元

投资各方金现金流量表

人民币单位:万元

利润和利润分配表

人民币单位:万元

资产负债表

人民币单位:万元

财务计划现金流量表人民币单位:万元

THANKS !!!

致力为企业和个人提供合同协议,策划案计划书,学习课件等等

打造全网一站式需求

欢迎您的下载,资料仅供参考。

深圳职业技术学院

Shenzhen Polytechnic

实训(验)项目报告Training Item Report

编制部门:电信学院 编制人:赵杰 审核人 编制日期: 2011-2-20

深 圳 职 业 技 术 学 院

Shenzhen Polytechnic

实 训(验)项 目 单 Training Item

5. 利用L-EDIT设计二输入异或门版图

1)在已经有的工程(project)中,建立一个新的cell,命名为xor2

2)将倒相器inv和传输门tran(两个MOS管)的版图instance到新建cell中,并对其flatten 3)对instance得到的版图进行修改,选择正确MOS管尺寸,并进行正确连接,成为两输入异或门版图,并进行DRC检查修改相应错误

4) 在电路的输入、输出端口,以及Vdd与Gnd

5)进行CMOS异或门版图网表抽取,加入仿真命令,进行瞬时和直流分析

Tool Extract

General选项

Extract Definition File:

c:\Tanner\spr\morbn20.ext

Spice Extract Output File:

d:\design\xor2.spc

Output选项

Comment:

√ Write Node name

٠ Names

√ Write Verbose Spice Statement

Spice Include Statement

. Include c:\tanner\models\ml2_125.md

6)注意各个MOS管尺寸的选取和连接

7)截面观察:TOOLS CROSS-SECTION

8)观察二输入异或门版图设计成果,可单独显示某一图层,或某些特定图层

9)T-SPICE模拟

采用实训4、5的方法,在得到的xor2.spc文件中,插入相应的命令,进行二输入异或门版图的瞬时和直流模拟。

下图为CMOS二输入异或门的参考版图。

最佳二输入异或门电路,应由六个MOS管构成。

整个模块版图的高度。

6.CMOS异或门的LVS(Layout Versus Schematic)

三、注意事项:

1.如果对版图设计的基本规则不熟悉,可以在L-EDIT中,打开SETUP DRC,列出了所有的设计规则,可学习和记忆其中的一些主要和常用的版图设计规则

2.在进行版图设计规则检查时,应选择输出检查文件一项,版图设计中出现的所有错误,都可以在该输出文件中列出,并标明出错的原因,与哪条规则相违背,可打开规则进行对照,并在版图上进行相应的修改。

地点: 信息中心208室 编制人:赵杰 审核人: 编制日期:2011-2-20

深 圳 职 业 技 术 学 院

Shenzhen Polytechnic

实训(验)项目卡。