数字逻辑电路m序列发生器

- 格式:doc

- 大小:28.00 KB

- 文档页数:1

m序列发生器的作用

m序列发生器是一种能够产生伪随机序列的电子设备或算法。

它的主要作用有:

1. 加密通信:m序列发生器可以用于生成加密密钥序列,用于对通信数据进行加密,保护通信内容的安全性。

2. 伪随机数生成:m序列发生器可以用于生成伪随机数序列,可以应用在密码学中的伪随机数生成算法、模拟实验、随机化算法等应用中。

3. 信号处理:m序列发生器可以用于产生具有特定性质的信号序列,如具有较好频谱特性的序列、跳频信号序列等,广泛应用于通信领域、雷达系统、无线电测量等各种信号处理应用中。

4. 探测器测试:m序列发生器可以用于对数字通信中的接收机进行性能测试,通过与已知正常输入进行比较,可以检测接收机的误码率、误比特率、误帧率等性能指标。

总之,m序列发生器的作用主要体现在加密通讯、伪随机数生成、信号处理和探测器测试等方面。

M 序列发生器M 序列(即De Bruijn 序列)又叫做伪随机序列、伪噪声(PN)码或伪随机码。

可以预先确定并且可以重复实现的序列称为确定序列;既不能预先确定又不能重复实现的序列称随机序列;不能预先确定但可以重复产生的序列称伪随机序列。

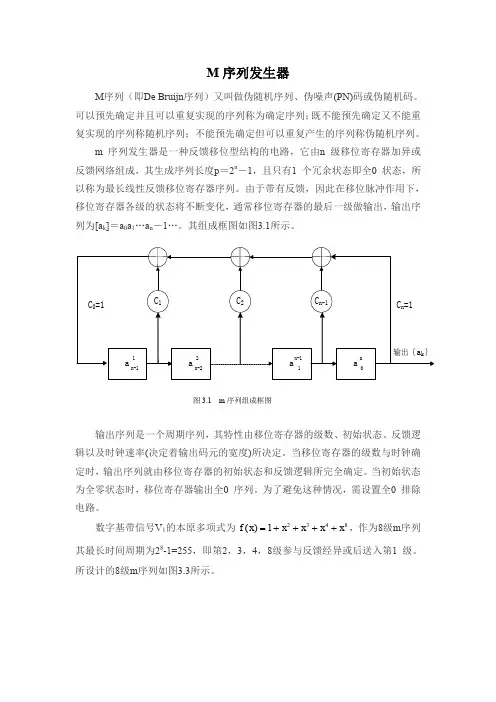

m 序列发生器是一种反馈移位型结构的电路,它由n 级移位寄存器加异或反馈网络组成,其生成序列长度p =2n -1,且只有1 个冗余状态即全0 状态,所以称为最长线性反馈移位寄存器序列。

由于带有反馈,因此在移位脉冲作用下,移位寄存器各级的状态将不断变化,通常移位寄存器的最后一级做输出,输出序列为[a k ]=a 0a 1…a n -1…。

其组成框图如图3.1所示。

输出序列是一个周期序列,其特性由移位寄存器的级数、初始状态、反馈逻辑以及时钟速率(决定着输出码元的宽度)所决定。

当移位寄存器的级数与时钟确定时,输出序列就由移位寄存器的初始状态和反馈逻辑所完全确定。

当初始状态为全零状态时,移位寄存器输出全0 序列。

为了避免这种情况,需设置全0 排除电路。

数字基带信号V 1的本原多项式为84321)(x x x x x f ++++=,作为8级m 序列其最长时间周期为28-1=255,即第2,3,4,8级参与反馈经异或后送入第1 级。

所设计的8级m 序列如图3.3所示。

图3.1 m 序列组成框图a n-11a n-22a 1n-1a 0n C 1C 2C n-1C n =1C 0=1输出{a k }依据上图原理,设计了一种通过手动置数产生M 序列的电路,其电路设计如图3.4所示,该图由Protel SE99绘制,再根据该图搭建硬件电路,图中的单刀开关可以用拨码开关代替。

电路分析:全0状态时,采用此方法设计的m 序列发生器不具有自启动特性。

为了使电路启动,可以断开开关S 1,将74LS194 的工作方式控制端S 1置高电平,这时S 1和S 0均为高电平,即S 1S 0=11,74LS194 处于置数状态,把输入端的初始状态10000000 置到输出端。

成都电子机械高等专科学校毕业设计论文作者姚世刚学号2009111733系部电子与电气工程系专业电子测量技术与仪器题目基于VHDL的m序列伪随机信号发生器的设计指导教师赵茂林评阅教师完成时间:2012年4 月30日毕业设计(论文)中文摘要题目:基于VHDL的m序列发生器的设计摘要:VHDL/CPLD即复杂可编程逻辑器件作为一种大规模集成电路,可根据用户的需要自行构造逻辑功能,可实现较大规模的电路设计,因此被广泛应用于产品的原型设计和产品生产之中。

几乎所有应用中小规模通用数字集成电路的场合均可应用CPLD器件。

本文介绍了基于CPLD的m序列发生器的设计方法。

关键词:CPLD;MAX+PLUS II;伪随机码;m序列发生器毕业设计(论文)外文摘要Title : M—sequence Generator Based CPLDAbstract: VHDL/CPLD Complex Programmable Logic Device that is, as a large scale integrated circuits can be constructed according to the needs of users on their own logic, enabling large-scale circuit design, it is widely used in product design and prototype production into. Almost all applications of small and medium general-purpose digital integrated circuits may be applied CPLD devices occasions. This article describes the m-sequence generator based on CPLD design method.Key words: CPLD;MAX+PLUS II;Pseudorandom Code;m sequence code Generator目录前言 (6)1课题介绍 (7)1.1为什么研究此课题 (7)1.2伪随机序列的应用与意义 (7)1.3伪随机序列的研究现状 (8)1.4研究内容 (8)2设计中使用芯片及VHDL语言介绍 (9)2.1 CPLD芯片介绍 (9)2.1.1概述 (9)2.1.2 MAX7000特点 (9)2.1.3 EPM7128LC84-7 (11)3 伪随机序列介绍 (12)3.1 伪随机序列理论的发展史 (13)3.2 伪随机序列的构造方法 (13)4 序列信号发生器原理 (14)4.1序列信号发生器的设计 (15)4.1.1反馈移位型序列信号发生器 (15)4.1.2计数型序列码发生器 (18)5 移位寄存器 (20)5.1移位寄存器 (20)5.1.1 寄存器 (20)5.1.2移位寄存器 (21)5.2 线性反馈移位寄存器结构 (22)5.2.1 D触发器 (22)5.2.1.1 D触发器工作原理 (22)5.2.1.2 D触发器真值表 (23)5.2.1.3 特征方程 (23)5.2.1.4 状态转移图 (23)5.2.1.5时序图 (24)5.2.1.6 脉冲特性 (24)5.2.2异或门 (25)5.2.2.1 基本原理 (25)5.2.2.2 异或门逻辑符号 (25)5.2.2.3 逻辑表达式 (25)5.2.2.4 真值表 (25)5.3 线性反馈移位寄存器 (26)5.3.1 什么是反馈移位寄存器 (26)5.3.2 线性反馈移位寄存器 (26)5.3.3 性质 (26)6 伪随机信号 (27)6.1 伪随机信号 (27)6.2 m序列码发生器 (30)7 m序列性质 (33)7.1 均衡性 (33)7.2游程特性 (33)7.3 移位相加性 (33)7.4 相关特性 (33)7.5 伪随机特性 (34)8 序列信号发生器的设计和仿真实现 (35)8.1 m序列生成单元的电路设计 (35)8.1.1 系统组成 (35)8.1.2 程序方框图 (36)8.2 m序列发生器 (36)8.3 VHDL语言实现 (37)8.4 仿真数据及结论 (39)结论 (42)致谢 (43)参考文献 (43)前言CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。

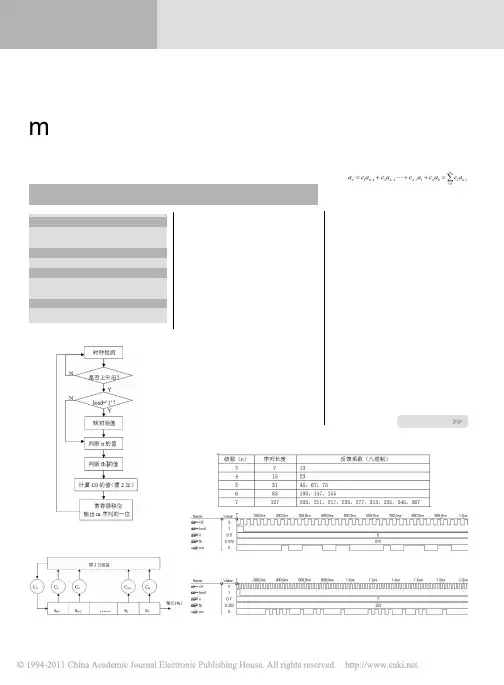

基于FPGA的m序列发生器摘要m序列广泛应用于密码学、通信、雷达、导航等多个领域,本文提出了一种基于FPGA的伪随机序列产生方法,应用移位寄存器理论从序列的本原多项式出发,获得产生该序列的移位寄存器反馈逻辑式,结合FPGA芯片结构特点,在序列算法实现中采用元件例化语句。

算法运用VHDL语言编程,以A1tera的QuartusⅡ软件为开发平台,给出了序列的仿真波形。

序列的统计特性分析表明:该方法产生的序列符合m序列的伪随机特性,验证了算法的正确性。

关键词:m序列;移位寄存器理论;VHDL语言目录摘要 (I)1 m序列 (1)1.1 理论基础 (1)1.1.1 线性反馈移位寄存器 (2)2 m序列的性质 (5)2.1 均衡性 (5)2.2游程特性 (5)2.4 自相关特性 (5)2.5 伪噪声特性 (7)3 m序列的应用 (9)3.1 扩展频谱通信 (9)3.2 通信加密 (10)4 开发工具简介 (11)4.1 Quartus II简介 (11)4.2 数字系统开发流程 (12)4.3 FPGA简介 (12)5 m序列生成器仿真分析 (16)5.1 反馈系数表存储器设计 (16)5.2 移位存储器设计 (17)5.3 仿真分析 (18)参考文献 (20)附录 (22)1 m序列m序列是伪随机序列的一种 ,结构简单 ,实现方便。

在现代工程实践中 , m 序列在通讯、导航、雷达、通信系统性能的测量等领域中有着广泛的应用。

例如 , 在连续波雷达中可用作测距信号 , 在遥控系统中可用作遥控信号 , 在多址通信中可用作地址信号 , 在数字通信中可用作群同步信号 ,还可用作噪声源及在保密通信中起加密作用等。

伪噪声发生器在测距、通信等领域的应用日益受到人们重视。

目前,m序列产生实现方法主要有3种:(1)门电路实现该方法设计简单,但随移位寄存器级数的增长,电路装调困难,且占用的印制板面积较大。

(2)DSP编程实现该方法专业性过强,不适合一般用户。

m序列产生实验一、实验目的1、m序列产生的基本方法;2、m序列0状态消除的基本手段;二、实验仪器1、JH5001型通信原理实验箱一台;2、MaxplusII开发环境一台;3、JTAG下载电缆一根;4、CPLD下载板一块;5、微机一台;6、示波器一台;三、实验原理m序列产生电路在通信电路设计中十分重要,它广泛使用在扩频通信、信号产生、仪器仪表等等电路中。

m序列有时也称伪噪声(PN)或伪随机序列,在一段周期内其自相关性类似于随机二进制序列。

尽管伪噪声序列是确定的,但其具有很多类似随机二进制序列的性质,例如0和1的数目大致相同,将序列平移后和原序列的相关性很小。

PN序列通常由序列逻辑电路产生,一般是由一系列的两状态存储器和反馈逻辑电路构成。

二进制序列在时钟脉冲的作用下在移位寄存器中移动,不同状态的输出逻辑组合起来并反馈回第一级寄存器作为输入。

当反馈由独立的“异或”门组成(通常是这种情况),此时移位寄存器称为线性PN序列发生器。

如果线性移位寄存器在某些时刻到达零状态,它会永远保持零状态不变,因此输出相应地变为全零序列。

因为n阶反馈移位寄存器只有2n-1个非零状态,所以由n阶线性寄存器生成的PN序列不会超过2n-1个。

周期为2n-1的线性反馈寄存器产生的序列称为最大长度(ML)序列——m序列。

m 序列发生器的一般组成m 序列发生器一般组成如上图所示,它用n 级移位寄存器作为主支路,用若干级模2加法器作为各级移位寄存器的抽头形成线性反馈支路。

各抽头的系数hi 称为反馈系数,它必须按照某一个n 次本原多项式:∑==ni i i x h x h 0)(中的二进制系数来取值。

在伪序列发生模块中,可以根据本原多项式的系数,…..h 8、h 7、h 6、h 5、h 4、h 3、h 2、h 1、h 0产生m 序列,这些系数可表示8进制数(1代表相连抽头进入反馈回路,0代表该抽头不进入反馈回路),如:13、23、103、203四、 课题设计要求在输入时钟256KHz 的时钟作用下,可在外部跳线器的控制下改变产生不同的m 序列,在程序中定义的几个变量为:输入: Main_CLK :输入 256KHz 主时钟 M_Sel[1..0]:选择输出不同的m 序列当 Mode[]=0:本原多项式为13(8进制表示); 当 Mode[]=1:本原多项式为23(8进制表示); 当 Mode[]=2:本原多项式为103(8进制表示); 当 Mode[]=3:本原多项式为203(8进制表示);输出: M_Out :m 序列输出 说明:1、 M_Sel[1..0]与复接模块的m_sel0、m_sel1相连; M_Out 在测试点TPB01输出;五、 实验步骤1、将JH5001二次开发光盘内的基本程序m.tdf 及其它相关程序(在光盘的“2th\student_m ”子目录下)拷入机器内。

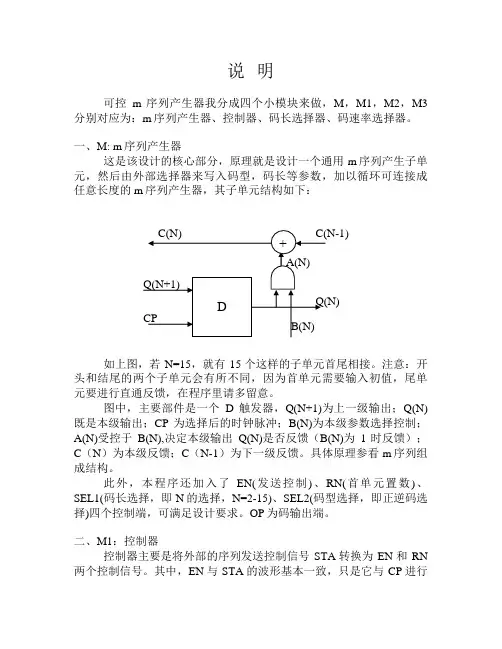

说明可控m序列产生器我分成四个小模块来做,M,M1,M2,M3分别对应为:m序列产生器、控制器、码长选择器、码速率选择器。

一、M: m序列产生器这是该设计的核心部分,原理就是设计一个通用m序列产生子单元,然后由外部选择器来写入码型,码长等参数,加以循环可连接成任意长度的m序列产生器,其子单元结构如下:如上图,若N=15,就有15个这样的子单元首尾相接。

注意:开头和结尾的两个子单元会有所不同,因为首单元需要输入初值,尾单元要进行直通反馈,在程序里请多留意。

图中,主要部件是一个D触发器,Q(N+1)为上一级输出;Q(N)既是本级输出;CP为选择后的时钟脉冲;B(N)为本级参数选择控制;A(N)受控于B(N),决定本级输出Q(N)是否反馈(B(N)为1时反馈);C(N)为本级反馈;C(N-1)为下一级反馈。

具体原理参看m序列组成结构。

此外,本程序还加入了EN(发送控制)、RN(首单元置数)、SEL1(码长选择,即N的选择,N=2-15)、SEL2(码型选择,即正逆码选择)四个控制端,可满足设计要求。

OP为码输出端。

二、M1:控制器控制器主要是将外部的序列发送控制信号STA转换为EN和RN 两个控制信号。

其中,EN与STA的波形基本一致,只是它与CP进行了同步处理;RN在EN为‘1’的头一个脉冲周期里置高电平,以达到为序列发生器的首端置数的目的。

如果不清楚的话可以看一下它的模拟波形。

(注意:STA要采用自锁定开关,高电平有效)三、M2:码长选择序列的码长选择既是N值的选择,码长=2**N-1。

核心就是一个计数器,可从2计到15。

按一次PUSH就可以自动加一(注意:按键建议采用自弹跳按键,如过需要软件清除按键震颤的话,我再做发给你),没有0,1两个状态。

如果需要的话还可以扩展7段数码管的接口,以显示N值。

四、M3:码速率选择器码的传输速率是靠CP来控制的,CP的频率就等于码元速率。

这段程序包含一个倍频器,一个5分频的分频器,可把5MHZ的脉冲源CLK扩展成1MHZ和10MHZ。

基于FPGA的m序列发生器摘要m序列广泛应用于密码学、通信、雷达、导航等多个领域,本文提出了一种基于FPGA的伪随机序列产生方法,应用移位寄存器理论从序列的本原多项式出发,获得产生该序列的移位寄存器反馈逻辑式,结合FPGA芯片结构特点,在序列算法实现中采用元件例化语句。

算法运用VHDL语言编程,以A1tera的QuartusⅡ软件为开发平台,给出了序列的仿真波形。

序列的统计特性分析表明:该方法产生的序列符合m序列的伪随机特性,验证了算法的正确性。

关键词:m序列;移位寄存器理论;VHDL语言目录摘要 (I)1 m序列 (1)1.1 理论基础 (1)1.1.1 线性反馈移位寄存器 (2)2 m序列的性质 (5)2.1 均衡性 (5)2.2游程特性 (5)2.4 自相关特性 (5)2.5 伪噪声特性 (7)3 m序列的应用 (9)3.1 扩展频谱通信 (9)3.2 通信加密 (10)4 开发工具简介 (11)4.1 Quartus II简介 (11)4.2 数字系统开发流程 (12)4.3 FPGA简介 (12)5 m序列生成器仿真分析 (16)5.1 反馈系数表存储器设计 (16)5.2 移位存储器设计 (17)5.3 仿真分析 (18)参考文献 (20)附录 (22)1 m序列m序列是伪随机序列的一种 ,结构简单 ,实现方便。

在现代工程实践中 , m 序列在通讯、导航、雷达、通信系统性能的测量等领域中有着广泛的应用。

例如 , 在连续波雷达中可用作测距信号 , 在遥控系统中可用作遥控信号 , 在多址通信中可用作地址信号 , 在数字通信中可用作群同步信号 ,还可用作噪声源及在保密通信中起加密作用等。

伪噪声发生器在测距、通信等领域的应用日益受到人们重视。

目前,m序列产生实现方法主要有3种:(1)门电路实现该方法设计简单,但随移位寄存器级数的增长,电路装调困难,且占用的印制板面积较大。

(2)DSP编程实现该方法专业性过强,不适合一般用户。

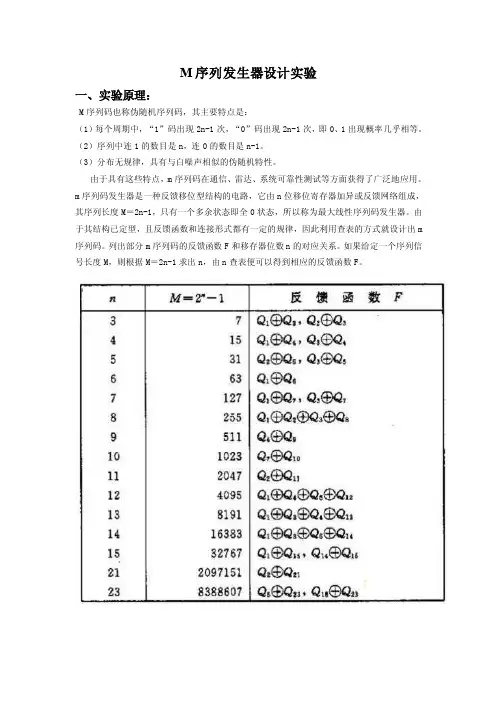

M序列发生器设计实验一、实验原理:M序列码也称伪随机序列码,其主要特点是:(1)每个周期中,“1”码出现2n-1次,“0”码出现2n-1次,即0、1出现概率几乎相等。

(2)序列中连1的数目是n,连0的数目是n-1。

(3)分布无规律,具有与白噪声相似的伪随机特性。

由于具有这些特点,m序列码在通信、雷达、系统可靠性测试等方面获得了广泛地应用。

m序列码发生器是一种反馈移位型结构的电路,它由n位移位寄存器加异或反馈网络组成,其序列长度M=2n-1,只有一个多余状态即全0状态,所以称为最大线性序列码发生器。

由于其结构已定型,且反馈函数和连接形式都有一定的规律,因此利用查表的方式就设计出m 序列码。

列出部分m序列码的反馈函数F和移存器位数n的对应关系。

如果给定一个序列信号长度M,则根据M=2n-1求出n,由n查表便可以得到相应的反馈函数F。

二、基于DSP Builder 的设计M 序列发生器可由线性反馈寄存器(Linear Feedback Shift Registers,LFSR )来产生,如图1所示。

图1 线性反馈移位寄存器的构成其特征多项式可表示为:∑==ni i i x C x F 1)(在图1中涉及的乘法和加法都是指模二运算的乘法和加法,即逻辑与和逻辑或。

要产生最长的线性反馈移位寄存器序列的n 级移位寄存器,其特征多项式必须是n 次本原多项式。

例如n=5,可以生成M 序列的5级LFSR 的特征多项式,即:125++x x ,此式可生成的M 序列的周期为:125-。

下面以M 序列发生器模型125++x x 为例,利用DSP Builder 构建一个伪随机序列发生器。

图2显示了上式的DSP Builder 模型表述,这里采用相连的延时单元级作为移位寄存器,用异或(XOR )完成模二加运算,输出为Output 。

图2 M 序列发生器模型但应注意,图2所示的电路一般无法正常工作。

这是由于在DSP Builder 默认的延时单元在开始工作时,存储内容为0,而对于M 序列来说,起始序列为全0,那么根据多项式,输出序列也将为0.全0序列不是正常的M 序列。

实验九 m 序列产生及其特性实验一、实验目的通过本实验掌握m 序列的特性、产生方法及应用。

二、实验内容1、观察m 序列,识别其特征。

2、观察m 序列的自相关特性。

三、基本原理m 序列是有n 级线性移位寄存器产生的周期为21n -的码序列,是最长线性移位寄存器序列的简称。

码分多址系统主要采用两种长度的m 序列:一种是周期为1521-的m 序列,又称短PN 序列;另一种是周期为4221-的m 序列,又称为长PN 码序列。

m 序列主要有两个功能:①扩展调制信号的带宽到更大的传输带宽,即所谓的扩展频谱;②区分通过多址接入方式使用同一传输频带的不同用户的信号。

1、产生原理图9-1示出的是由n 级移位寄存器构成的码序列发生器。

寄存器的状态决定于时钟控制下输入的信息(“0”或“1”),例如第I 级移位寄存器状态决定于前一时钟脉冲后的第i -1级移位寄存器的状态。

图中C 0,C 1,…,C n 均为反馈线,其中C 0=C n =1,表示反馈连接。

因为m 序列是由循环序列发生器产生的,因此C 0和C n 肯定为1,即参与反馈。

而反馈系数C 1,C 2,…,C n-1若为1,参与反馈;若为0,则表示断开反馈线,即开路,无反馈连线。

图9-1 n 级循环序列发生器的模型一个线性反馈移动寄存器能否产生m 序列,决定于它的反馈系数(0,1,2,,)i c i n =,下表中列出了部分m 序列的反馈系数i c ,按照下表中的系数来构造移位寄存器,就能产生相应的m 序列。

表9-1 部分m 序列的反馈系数表根据表9-1中的八进制的反馈系数,可以确定m 序列发生器的结构。

以7级m 序列反馈系数8(211)i C =为例,首先将八进制的系数转化为二进制的系数即2(010001001)i C =,由此我们可以得到各级反馈系数分别为:01C =、10C =、30C =、41C =、50C =、60C =、71C =,由此就很容易地构造出相应的m 序列发生器。

常见m序列什么是m序列?m序列(m-sequence)是一种特殊的二进制序列,也被称为最大长度线性反馈移位寄存器(maximum length linear feedback shift register, LFSR)序列。

它具有伪随机性质,广泛应用于通信、密码学、编码等领域。

m序列由一个线性反馈移位寄存器(LFSR)产生,LFSR是一种在数字电路中常见的寄存器,用于生成伪随机序列。

LFSR由一组触发器和逻辑门组成,触发器的输出通过逻辑门反馈到寄存器的输入,形成一个闭环。

m序列的长度为2^m - 1,其中m是LFSR的阶数,也是寄存器中触发器的数量。

m 序列具有良好的统计特性,其周期为2^m - 1,即在一个周期内,m序列的输出不会重复。

m序列的生成原理m序列的生成原理基于LFSR的工作原理。

LFSR由m个触发器组成,每个触发器可以存储一个二进制位。

触发器的输出通过逻辑门反馈到寄存器的输入,形成一个闭环。

LFSR的工作过程如下: 1. 初始化寄存器的状态,即给每个触发器赋初始值。

2. 在每个时钟周期内,寄存器中的位向右移动一位,最右边的位被丢弃,最左边的位由逻辑门计算得出,并存储在寄存器的最右边。

3. 重复第2步,直到寄存器的状态回到初始状态。

m序列的输出是寄存器中的位,通常取最右边的位作为序列的输出。

m序列的性质m序列具有以下性质: 1. 周期性:m序列的周期为2^m - 1,即在一个周期内,m 序列的输出不会重复。

2. 均匀性:m序列的输出0和1的个数相等,且相邻的位之间是独立的。

3. 自相关性:m序列的自相关函数在除了原点外都为0,即m序列与其自身进行位移后,相邻位之间的相关性很低。

4. 互相关性:m序列与另一个m序列进行互相关,结果为0,即不同的m序列之间没有相关性。

这些性质使得m序列在通信、密码学、编码等领域有着广泛的应用。

m序列的应用通信领域在通信领域,m序列被用于信号的调制和解调。

第1章绪论1.1 课题背景在信息化社会,通信系统担负着信息传输、交换和处理的重要任务。

通信技术的发展代表了一个国家科学技术的发展现状,也成为国家经济发展的一个重要推动力。

扩展频谱通信是通信的一个重要分支和发展方向,它是扩展频谱技术和通信技术相结合的产物。

由于扩展频谱即使具有抗干扰能力强、截获率低、多址能力强、抗多径、保密性好及测距能力强等一系列的优点,使得扩展频谱通信越来越受到人们的重视。

随着大规模或超大规模集成电路技术、微电子技术、为处理技术的迅猛发展以及一些新型器件的广泛应用,扩展频谱通信的发展迈上了一个新的台阶,它不仅在军事通信中占有重要地位,而且正迅速地渗透到民用通信中。

可以毫不夸张地讲,在现代通信系统,特别是无线通信系统,没有扩展频谱技术,这些系统想生存都是比较困难的。

在扩展频谱系统中,伪随机序列起着重要的作用。

在直扩系统中,用伪随机序列将传输信息扩展,在接收时又用它将信息压缩,并使干扰信息功率扩展,提高了系统的抗干扰能力;在跳频系统中,用伪随机序列控制频率合成器产生的频率随机地跳变,躲避干扰;在跳时系统中,用伪随机序列控制脉冲发送的时间和持续时间。

由此可见,伪随机序列性能的好坏,直接关系到整个系统性能的好坏,是一个至关重要的问题。

m序列是最长线性移位寄存器序列,是伪随机序列中最重要的序列中的一种,这种序列易于产生,有优良的自相关特性。

在直扩系统中m序列用于扩展要传递的信号,在跳频系统中m序列用来控制跳频系统的频率合成器,组成随机跳频图案。

电子设计技术由于计算机技术的发展而产生了巨大变化。

本设计是利用电子设计方法,用电路图表示设计思想,用实验电路板搭载实验电路,进行模拟、仿真,用电子测试仪器进行功能、性能测试。

20世纪80年代,计算机辅助设计(CAD)技术开始发展,许多CAD工具软件开始流行。

在信息学科领域也和其他学科一样,计算机辅助设计技术步入了发展轨道。

由于电子科学是计算机科学的基础,计算机学科的发展离不开电子学科的支持,但是计算机科学又反作用于电子科学,加速了电子学科的发展。

基于EWB的序列信号发生器分析和设计前言在当今电子设计领域,EDA设计和仿真是一个十分重要的设计环节。

在众多的EDA设计和仿真软件中,EWB软件以其强大的仿真设计应用功能,在各高校电信类专业电子电路的仿真和设计中得到了较广泛的应用。

EWB软件及其相关库包的应用对提高学生的仿真设计能力,更新设计理念有较大的好处。

EWB(电子工作平台)软件,最突出的特点是用户界面友好,各类器件和集成芯片丰富,尤其是其直观的虚拟仪表是EWB软件的一大特色。

它采用直观的图形界面创建电路:在计算机屏幕上模仿真实实验室的工作台,绘制电路图需要的元器件、电路仿真需要的测试仪器均可直接从屏幕上选取。

EWB软件所包含的虚拟仪表有:示波器,万用表,函数发生器,波特图图示仪,失真度分析仪,频谱分析仪,逻辑分析仪,网络分析仪等。

这些仪器的使用使仿真分析的操作更符合平时实验的习惯。

本次毕业设计主要是利用EWB软件来设计和仿真序列信号发生器,并结合理论进一步验证序列信号发生器的实际作用。

1 EWB软件的简介1.1 EWB软件的概述随着电子技术和计算机技术的发展,电子产品已与计算机紧密相连,电子产品的智能化日益完善,电路的集成度越来越高,而产品的更新周期却越来越短。

电子设计自动化(EDA)技术,使得电子线路的设计人员能在计算机上完成电路的功能设计、逻辑设计、性能分析、时序测试直至印刷电路板的自动设计。

EDA是在计算机辅助设计(CAD)技术的基础上发展起来的计算机设计软件系统。

与早期的CAD软件相比,EDA软件的自动化程度更高、功能更完善、运行速度更快,而且操作界面友善,有良好的数据开放性和互换性。

电子工作平台Electronics Workbench (EWB)(现称为MultiSim) 软件是加拿大Interactive Image Technologies公司于八十年代末、九十年代初推出的电子电路仿真的虚拟电子工作台软件,它具有这样一些特点:(1)软件仪器的控制面板外形和操作方式都与实物相似,可以实时显示测量结果。

基于 VHDL 可编程 m 序列发生器的研制赵林军(陕西理工学院 电子与信息工程系 陕西 汉中 723003)摘 要: 提出一种可实现周期ƒ初相位编程控制的 m 序列发生器逻辑电路的设计方案。

给出了 V HDL 与 C P L D 的实现 方 案。

程序经编译、仿真、测试后, 可以实现设计要求。

该器件在M C S 51 的控制下, 实现m 序列的周期、初相位的编程变关键词: m 序列发生器; V HDL ; 逻辑电路; C P L D中图分类号: TN 914142文献标识码: B文章编号: 1004 373X (2004) 14 033 02Re s ea r ch an d D eve lop m en t of Programm a b le m Sequen ce Gen e ra tor Ba sed on VHDLZHA O L in jun(D ep a r t m en t o f E lec t ro n i c & Info rm a t i o n E ng inee r ing , Shaanx i U n i ve r s ity o f T echno lo gy , H anzho ng , 723003, C h ina )A b stra c t : T h e a r t i c l e in t r o d uce s o n e o f m sequ en ce gen e r a t o r s , w h ich deve l op ed ba s in g o n V HDL lan guage an d can beenp ro g r am m ab le o n p e r i o d s f r om 22 - 1 to 232- 11 W e exp lica t ed m ak in g p r i n c i p le an d w o rk i n g co u r s e , fu r t h e r m o re , gave th e h a r d w ir ec i rcu it o f th e i m p lem en t th a t h a s g r ea t l y p rac t i ca l and refe r en t i a l va l ue 1Keywords : m sequ en ce gen e r a t o r ; V HDL ; lo g i ca l c i rcu it ; C P L Dm 序列广泛应用于数字基带信号进行加扰, 改善数字 序列的位定时质量与帧同步和自适应时域均衡性能, 同时 也是构造平衡 G OL D 码的基础。