设计示例1存储器设计

- 格式:doc

- 大小:228.00 KB

- 文档页数:6

Vivado 差分信号类型1. 引言差分信号是一种常见的电信号传输方式,可以有效地抗干扰和提高传输速率。

Vivado是赛灵思(Xilinx)公司开发的集成电路设计工具,用于FPGA(Field-Programmable Gate Array)和SoC(System-on-Chip)设计。

在Vivado中,差分信号类型是设计中重要的一部分,本文将详细介绍Vivado中的差分信号类型及其相关知识。

2. 差分信号的定义和特点差分信号是指由两个相互反向的信号组成的信号对。

在差分信号中,一个信号被称为正信号(P),另一个信号被称为负信号(N)。

正负信号之间的差异是由于信号的相位相反而产生的。

差分信号的特点如下:•抗干扰能力强:差分信号可以通过比较正负信号的差异来识别和抵消噪声和干扰,因此具有较强的抗干扰能力。

•传输速率高:由于差分信号可以利用信号的相位差来传输信息,因此可以提高传输速率。

•电压幅度较小:差分信号的电压幅度通常较小,这有助于减少功耗和电磁辐射。

3. Vivado中的差分信号类型在Vivado中,差分信号类型主要有以下几种:3.1 差分输入/输出(Differential I/O)差分输入/输出(Differential I/O)是Vivado中常见的差分信号类型。

差分I/O接口通常用于高速数据传输和抗干扰设计。

在FPGA设计中,常使用差分I/O来连接外部器件,如DDR(Double Data Rate)存储器、高速ADC(Analog-to-Digital Converter)和DAC(Digital-to-Analog Converter)等。

差分I/O接口通常由两个引脚组成,分别为正引脚和负引脚。

在Vivado中,可以使用语法I和N来表示差分I/O引脚,例如<signal_name>_I和<signal_name>_N。

3.2 差分信号约束(Differential Constraint)在Vivado中,差分信号约束用于定义差分信号的时序和电气特性。

verilog fifo原理FIFO(FirstInFirstOut)是一种常用的存储器结构,用于在数据传输过程中暂存数据。

在数字电路和系统设计中,FIFO被广泛应用于数据缓存、接口通信等领域。

本文将介绍VerilogFIFO的基本原理和设计方法。

一、FIFO的结构FIFO通常由输入端、输出端和存储器组成。

输入端和输出端分别对应数据的输入和输出,而存储器则用于暂存数据。

FIFO的读写操作遵循FIFO的先进先出(FIFO)原则,即最早进入FIFO的数据最先被读取。

在Verilog中,可以使用模块(module)和语句(statement)来实现FIFO。

常见的VerilogFIFO结构包括数据寄存器(dataregister)、读写指针(read/writepointer)、存储器单元(memorycell)和控制逻辑(controllogic)等部分。

二、FIFO的工作原理1.读写操作FIFO的读写操作遵循FIFO的基本原则。

在写操作时,新数据被写入存储器;在读操作时,最早进入FIFO的数据最先被读取。

控制逻辑负责管理读写指针,以确保正确的读写操作顺序。

2.缓冲作用FIFO的主要作用是缓冲数据,即在数据传输过程中,将输入端的数据存储到FIFO中,待FIFO满后再从输出端输出数据。

这样可以在一定程度上缓解数据传输的时序问题,提高数据传输的可靠性和效率。

3.溢出和欠流控制当FIFO满时,控制逻辑会停止新的写操作,以避免数据溢出。

同样地,当FIFO空时,控制逻辑会暂停新的读操作,以防止欠流(underflow)现象的发生。

这些控制逻辑的实现通常需要借助状态机(statemachine)和条件语句(conditionstatement)等Verilog语言特性。

以下是一个简单的VerilogFIFO设计示例:modulefifo(inputwireclk,reset,en_write,en_read,outputwire [7:0]data_out);reg[7:0]data_reg[15:0];//数据寄存器regread_pointer,write_pointer;//读写指针integeri;parameterSIZE=16;//FIFO容量//控制逻辑和状态机always@(posedgeclkorposedgereset)beginif(reset)beginread_pointer<=0;//复位时读写指针都归零write_pointer<=0;for(i=0;i<SIZE;i=i+1)begindata_reg[i]<=8'h00;//清空FIFOendendelseif(en_write)begindata_reg[write_pointer]<={data_reg[write_pointer],data_in };//新数据写入FIFOwrite_pointer<=write_pointer+1;//写指针加一if(write_pointer==SIZE)write_pointer<=0;//FIFO满时归零写指针endelseif(en_read)begindata_out<=data_reg[read_pointer];//读出最早进入FIFO的数据read_pointer<=read_pointer+1;//读指针加一if(read_pointer==SIZE)read_pointer<=0;//FIFO空时归零读指针endelsebegin//其他情况不做处理endendendmodule以上示例中,我们使用了一个16位的数据寄存器和两个指针(read_pointer和write_pointer)来管理FIFO的读写操作。

sram的设计与实现

SRAM(静态随机存取存储器)是一种常见的计算机内存类型,它使用电容器来存储数据,并且不需要周期性地刷新数据。

SRAM的设计和实现是计算机硬件工程师必须掌握的技能。

本文将介绍SRAM的设计和实现的基本原理和过程,包括SRAM的存储单元、读写模式、地址解码和控制信号处理,以及SRAM的布局和布线技术。

我们将详细讨论SRAM的各个方面,并提供实现SRAM所需的基本电路和模块的示例。

此外,我们还将介绍一些SRAM的优化技术,如数据压缩、位线预充电和动态电源管理,以提高SRAM的性能和功率效率。

最后,我们将讨论SRAM的应用和未来发展趋势,包括SRAM在处理器、图形处理器、网络交换机和物联网设备中的应用。

本文旨在为读者提供SRAM设计和实现的全面指南,以帮助他们在硬件工程领域取得更好的成绩。

- 1 -。

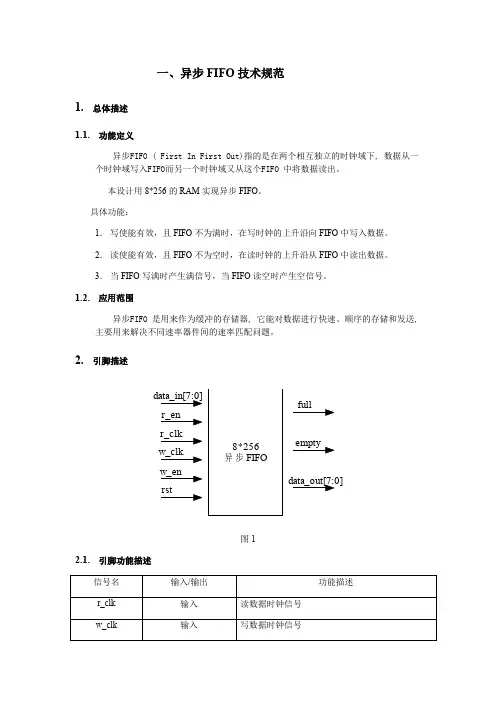

一、异步FIFO 技术规范1. 总体描述1.1. 功能定义异步FIFO ( First In First Out)指的是在两个相互独立的时钟域下, 数据从一个时钟域写入FIFO 而另一个时钟域又从这个FIFO 中将数据读出。

本设计用8*256的RAM 实现异步FIFO 。

具体功能:1. 写使能有效,且FIFO 不为满时,在写时钟的上升沿向FIFO 中写入数据。

2. 读使能有效,且FIFO 不为空时,在读时钟的上升沿从FIFO 中读出数据。

3. 当FIFO 写满时产生满信号,当FIFO 读空时产生空信号。

1.2. 应用范围异步FIFO 是用来作为缓冲的存储器, 它能对数据进行快速、顺序的存储和发送, 主要用来解决不同速率器件间的速率匹配问题。

2. 引脚描述8*256异步FIFO rst r_clkr_en data_in[7:0]full empty w_clkw_endata_out[7:0]图12.1. 引脚功能描述 信号名输入/输出 功能描述r_clk输入 读数据时钟信号 w_clk 输入 写数据时钟信号data_in[7:0] 输入8位的输入数据r_en 输入读使能,高电平有效,在FIFO非空时,clk上升沿读入数据;w_en 输入写使能,高电平有效,在FIFO非满时,clk上升沿写入数据;rst 输入异步清零,低电平有效,低电平时读地址,写地址,计数器都清零。

empty 输出空信号,高电平有效,当FIFO读空时其值为1full 输出满信号,高电平有效,当FIFO写满时其值为1 data_out[7:0] 输出8位的输出数据2.2.引脚时序描述当写满时full由低变高,当读空时empty由低变高。

只要不为满full就为低,不为空empty就为低。

3.顶层模块划分。

一、概述w9825g6kh 读写例程是针对 w9825g6kh 存储器的读写操作所设计的一套程序示例。

w9825g6kh 存储器是一种非易失性存储器,其读写示例程序可以帮助开发者更好地理解和应用该存储器。

二、读操作示例1. 设置 CS 信号为低电平,选中存储器;2. 发送读取命令和位置区域;3. 发送 DUMMY 数据,以便存储器准备好数据并输出;4. 读取存储器输出的数据;5. 设置 CS 信号为高电平,取消选中存储器。

三、写操作示例1. 设置 CS 信号为低电平,选中存储器;2. 发送写入命令和位置区域;3. 发送需要写入的数据;4. 设置 CS 信号为高电平,取消选中存储器。

四、注意事项1. 在进行读写操作时,需要根据 w9825g6kh 存储器的时序要求,确保信号的时序及稳定性;2. 在使用示例程序时,需要根据具体的开发板、MCU 等硬件评台进行适当的适配;3. 读写操作示例仅供参考,开发者在实际应用中需要根据具体需求进行定制和优化。

五、结语w9825g6kh 存储器的读写例程为开发者提供了一个基本的框架,帮助开发者快速上手并实现对该存储器的操作。

但在实际应用中,开发者仍需要根据具体需求进行进一步的开发和优化,以实现更复杂的功能和更高效的性能。

六、参考资料1. w9825g6kh 存储器的数据手册;2. 相关硬件评台的开发指南;3. 相关 MCU 的技术资料。

w9825g6kh 读写例程是一项非常重要的技术内容,针对该存储器的读写操作,我们需要深入了解其详细的实现方式以及在实际应用中可能遇到的问题和解决方案。

接下来,我们将继续探讨 w9825g6kh 存储器的读写例程,希望可以帮助开发者更深入地理解和应用该存储器。

1. 详细解析读操作示例在实际的读操作中,第一步是设置 CS 信号为低电平,这样可以选中存储器,使其处于可读取状态。

接下来,我们需要发送读取命令和位置区域。

在发送完命令和位置区域后,需要发送 DUMMY 数据,以便存储器准备好数据并输出。

xc9536编写逻辑解释说明以及概述1. 引言1.1 概述本文旨在介绍xc9536 编写逻辑的概念、原理和应用领域,以及该技术的特点和优势。

xc9536 是一种常用的可编程逻辑器件,在数字电路设计和逻辑控制系统中扮演着重要角色。

通过编写逻辑,我们可以灵活地定义和实现不同电路功能,提高系统效率和性能。

1.2 文章结构本文主要分为五个部分来阐述xc9536 编写逻辑的相关内容。

首先是引言部分,对于文章的目的、结构和背景进行简要介绍。

其次是xc9536 编写逻辑的基本原理、编程语言支持以及应用领域等方面的阐述。

然后将深入解释说明逻辑设计概念,详细解析xc9536 的工作原理,并给出相应示例与应用案例分析。

接下来是对xc9536 的特点与优势进行概述,包括即时可编程性能优势、设计灵活性与扩展性优势,以及低功耗和高集成度优势等方面。

最后,在结论部分对文章内容进行总结,并提出进一步研究和应用的建议。

1.3 目的本文的目的是为读者提供关于xc9536 编写逻辑的全面了解和必要的指引。

通过阅读本文,读者将了解到xc9536 编写逻辑的基本原理、工作原理以及其在不同应用领域中的实际应用案例。

同时,读者还能够清楚地认识到xc9536 的特点与优势,并能对其进行综合分析和评估。

最终,希望本文能够为进一步研究和应用xc9536 编写逻辑提供有价值的参考和启示。

2. xc9536编写逻辑2.1 基本原理xc9536是一种可编程逻辑器件,它基于XC9500系列的FPGA芯片。

它通过配置细胞阵列中的逻辑门和触发器来实现各种逻辑功能。

在编写逻辑时,我们需要了解其基本原理。

2.2 编程语言支持xc9536可以使用硬件描述语言(HDL)来进行编程。

常见的HDL包括VHDL (Very High-Speed Integrated Circuit Hardware Description Language)和Verilog。

这些语言可以描述逻辑电路的结构和行为,从而实现对xc9536的编程。

锁存电路的简单实现全文共四篇示例,供读者参考第一篇示例:锁存电路(Latch Circuit)是一种基础的数字电路,用来存储电信号。

它能够在特定条件下,将输入的信号固定在输出端,从而实现对数据的存储和传输。

锁存电路常用于存储器、寄存器、触发器等数字逻辑电路中。

在本文中,我们将介绍锁存电路的工作原理和简单实现方法。

锁存电路的工作原理如下:当控制信号为高电平时,锁存电路处于"打开"状态,可以接收输入信号。

当控制信号为低电平时,锁存电路处于"关闭"状态,输出信号被固定在输出端口。

锁存电路有两种常见的工作方式:RS锁存电路和D锁存电路。

RS锁存电路由两个输入端口(R和S)和两个输出端口(Q和Q')组成。

当R=0、S=1时,Q=0、Q'=1;当R=1、S=0时,Q=1、Q'=0;当R=S=0时,锁存电路保持上一次的状态。

RS锁存电路的特点是简单而实用,常用于数字系统中的存储器和触发器。

D锁存电路由一个数据输入端口(D)、一个时钟输入端口(CLK)和一个输出端口(Q)组成。

当CLK的上升沿到来时,如果D=1,则Q=1;如果D=0,则Q=0。

D锁存电路能够在时钟脉冲信号下,实现数据的锁存和传输,常用于存储器、寄存器等数字系统中。

下面我们将介绍一个简单的RS锁存电路的实现方法。

这个RS锁存电路使用两个门电路(与门和非门)来构建。

输入端口分别接入R、S信号,输出端口分别接入Q、Q'信号。

电路图如下:```_____| |R-----| |--------Q| S ||_____| _| | Q'| ||------------```代码实现如下(使用Verilog语言):```module latch (input R, S,output reg Q, Q');always @(R, S)beginif(R==0 && S==1)beginQ = 0;Q' = 1;endelse if(R==1 && S==0)beginQ = 1;Q' = 0;endendendmodule```以上代码将输入的R、S信号进行逻辑判断,根据不同的组合输出不同的Q、Q'信号。

nana flash中的原始误码率和擦写次数的关系计算全文共四篇示例,供读者参考第一篇示例:在nana flash存储器中,误码率是一个很关键的参数,它直接影响到存储器的可靠性和稳定性。

原始误码率指的是在存储器读取数据时,由于存储单元电荷泄漏或者噪声干扰导致的读取错误的情况。

而擦写次数则是指存储单元在使用过程中可以被擦写的次数。

研究原始误码率和擦写次数之间的关系,可以帮助我们更好地了解存储器的工作原理,并且优化存储器的设计和使用。

为了更好地理解原始误码率和擦写次数之间的关系,我们可以通过数学模型进行计算和分析。

我们需要了解存储单元的擦写次数与其损耗程度之间的关系。

一般来说,存储单元的损耗程度可以通过擦写次数的平方根来表示。

即存储单元的损耗程度P与擦写次数N之间满足P = sqrt(N)。

根据这个关系,我们可以推导出原始误码率与擦写次数之间的关系。

假设存储器中有n个存储单元,每个存储单元在使用过程中的原始误码率为Pe,擦写次数为Ni,则存储器整体的误码率可以表示为:P = sum(Pe * sqrt(Ni), i = 1 to n)。

通过对上述公式进行数学推导和计算,我们可以得到存储器的整体误码率与擦写次数之间的关系。

在实际应用中,我们可以根据这个关系来优化存储器的设计和使用,降低原始误码率,提高存储器的可靠性和稳定性。

第二篇示例:在nana flash中,原始误码率(BER)和擦写次数之间的关系是一个重要的研究方向,这对于nana flash的设计和性能优化具有重要意义。

在nana flash中,随着擦写次数的增加,存储单元(如存储单元,块或页)的性能会发生变化,其中包括原始误码率的变化。

了解原始误码率和擦写次数之间的关系可以帮助我们更好地设计nana flash,并减少存储器的故障率。

原始误码率(BER)是在数据传输过程中发生误码的概率。

在nana flash中,存储单元的原始误码率是指在读取数据时,正确的比特值与实际存储的比特值之间的不匹配情况。

丙酮存储器设计引言本文档描述了丙酮存储器的设计要求和指导原则。

丙酮是一种常用的有机溶剂,常用于实验室和工业生产中。

为了确保安全和有效使用丙酮,需要设计合适的存储器。

存储器选择选择适当的丙酮存储器非常重要,以避免泄漏和火灾等安全风险。

以下是一些常见的存储器选择:1. 包装:可以使用丙酮专用的密封金属或塑料瓶作为初级。

确保选择耐化学腐蚀的材料,并遵循生产商的建议。

2. 存储柜:将丙酮储存在一个专用的存储柜中,以提供额外的安全措施。

存储柜应具备以下特点:- 防火性能:选用金属制或耐火材料制的柜体,以提供有效的防火保护。

- 通风系统:确保存储柜内的通风系统良好,以防止丙酮蒸汽积聚。

- 标识和警告:柜体上应标识丙酮存储区域,并设置警告标签,提醒使用人员注意安全。

3. 存储位置:将丙酮存储于远离明火和点燃源的地方。

避免阳光直射和高温环境,确保存储地点通风良好,远离可燃物。

4. 防护措施:在存储和使用丙酮时,需要采取一些额外的防护措施,包括:- 佩戴个人防护装备:包括化学手套、护目镜和防护服等。

- 防护设施:在存储区域安装适当的灭火设备,并确保有易于接近的洗眼器和紧急淋浴。

紧急应对措施在丙酮存储和使用过程中,必须准备应对紧急情况的措施,以确保人员安全。

以下是必要的紧急应对措施:1. 灭火器:确保存储区域配备适当类型和容量的灭火器。

了解如何正确使用灭火器以及不同类型的火灾应对方法。

2. 紧急疏散计划:制定并培训紧急疏散计划,以确保人员能够迅速安全地离开存储区域。

3. 呼救程序:在存储区域安装紧急呼叫设备,并流程化呼救程序。

4. 急救培训:为存储区域的工作人员提供基本的急救培训,以应对意外情况。

结论丙酮存储器设计应符合安全要求,保证丙酮的储存和使用安全可靠。

选择适当的存储器、采取防护措施并做好紧急应对准备是确保丙酮安全使用的关键步骤。

使用本文档提供的指导原则,可以设计出一个合适的丙酮存储器。

设计示例1:存储器设计

1、 存储器模块定义:

存储器用于存放CPU 运算的程序指令和数据等,采用单端口存储器设计,设计最大为64个存储单元,每个存储单元数据宽度为32bit 。

下图为指令存储器的模块框图。

module ExtMem

图1 模块框图

2、 结构框图:

3、 接口说明:

表1: 存储器接口信号说明表

4、 时序说明:

ExtMem_CLK ExtMem_WR ExtMem_RD ExtMem_Adr Valid

Valid

ExtMem_Din

ExtMem_CS

图2 存储器接口读时序框图

ExtMem_CLK ExtMem_WR ExtMem_RD ExtMem_Adr Valid Valid

ExtMem_Dout

ExtMem_CS

图3 存储器接口写时序框图

Valid ExtMem_Dout

ExtMem_CLK ExtMem_WR ExtMem_RD ExtMem_Adr

Valid Valid

ExtMem_Din ExtMem_CS Valid

图4 存储器接口读写时序框图

5、 设计电路源代码

Module Mem ( input CLK,

input CSn, input [5:0] Addr, input WRn, input RDn, input [31:0] Din, output [31:0] Dout );

reg [31:0] Memory [0: 63] ; //---存储器写操作

always @( posedge CLK) begin

if (~CSn & ~WRn ) Memory[Addr]<= Din; end

//---存储器读操作方式1 always @( posedge CLK )

begin

if (~CSn & ~RDn ) Dout<= Memory[Addr];

end

//---存储器读操作方式2

always @( * )

begin

if (~CSn & ~RDn ) Dout<= Memory[Addr];

end

endmodule

问题讨论:

//------方式1与方式2的区别?

//------ altera公司的FPGA芯片,使用其内部存储器IP必须采用方式1设计

//------ xilinx公司的FPGA芯片,使用其内部存储器IP可以采用方式1或方式2设计

6、指令存储器初始化值设计

在仿真环境下,在设计电路中添加如下初始化存储器值电路:

initial

begin

#0 Memory[6'h0]<=32'h10; Memory[1]=32'h11; Memory[2]=32'h12;

Memory[63]=32'h63;

end

问题讨论:在硬件设计实现方式下,如何给存储器赋初值?

7、设计电路仿真

所设计的存储器模块电路,采用xxxx仿真器工具进行了设计仿真验证,如图5所示。

验证结果表明存储器功能以及接口时序完全正确。

附件1是仿真激励源代码。

图5 存储器电路读写仿真波形图

8、存在问题及解决方式方法,设计讨论等

XXXXXXXXX YYYY ZZZZZZZZZZZ

附件1:

//----------------------------------------------------------//

//Desc:

//----------------------------------------------------------//

//

`timescale 10ps/10ps

module Mem_testbench ( );

//---测试信号定义

reg fpga_clk, mem_cs, mem_wr, men_rd;

reg [5:0] mem_addr;

reg [31:0] mem_din;

wire [31:0] mem_dout;

//---存储器模块实例化调用

Mem mem_inst( .CLK(fpga_clk),

.CSn(mem_cs),

.Addr(mem_addr),

.WRn(mem_wr),

.RDn(men_rd),

.Din(mem_din),

.Dout(mem_dout) );

//-------------------------------

always #50 fpga_clk<= ~fpga_clk;

initial

begin

#0 fpga_clk=1'h0; mem_cs=1'h1; mem_wr=1'h1; men_rd=1'h1;

mem_addr=6'h00; mem_din=32'h00;

end

initial

begin

#510 mem_cs=1'h0; mem_wr=1'h0; mem_addr=6'h01; mem_din=32'h01;

#100 mem_addr=6'h02; mem_din=32'h02;

#100 mem_cs=1'h1; mem_wr=1'h1;

#100 mem_addr=6'h03; mem_din=32'h03;

#100 mem_cs=1'h0; mem_wr=1'h0;

#100 mem_cs=1'h1; mem_wr=1'h1; mem_addr=6'h04; mem_din=32'h04;

#200 mem_cs=1'h0; men_rd=1'h0; mem_addr=6'h02; mem_din=32'hzz;

#100 mem_addr=6'h03;

#100 mem_cs=1'h1; men_rd=1'h1;

#200 mem_cs=1'h0; men_rd=1'h0; mem_addr=6'h01;

#200 mem_cs=1'h1; men_rd=1'h1;

#100 mem_addr=6'hzz;

end

//----------------------------------------------------//

endmodule。