启动dc_shell工具的.synopsys.setup文档

- 格式:doc

- 大小:31.50 KB

- 文档页数:6

微电子学实验室实验教程ASIC综合器软件——Design Compiler实验2006-7Design Compiler实验前言Design Compiler(简称DC)是synopsys公司的ASIC综合器产品,它可以完成将硬件描述语言所做的RTL级描述自动转换成优化的门级网表。

DC得到全球60多个半导体厂商、380多个工艺库的支持。

Synopsys的逻辑综合工具DC占据91%的市场份额。

DC是工业界标准的逻辑综合工具,也是Synopsys最核心的产品。

它使IC设计者在最短的时间内最佳的利用硅片完成设计。

它根据设计描述和约束条件并针对特定的工艺库将输入的VHDL或者Verilog的RTL描述自动综合出一个优化的门级电路。

它可以接受多种输入格式,如硬件描述语言、原理图和网表等,并产生多种性能报告,在缩短设计时间的同时提高设计性能。

本实验对DC软件的使用进行简单的介绍,熟悉和掌握综合器软件使用中的基本概念和术语,了解如何对数字电路施加约束,掌握同步数字电路设计、约束和优化的方法,了解时钟的概念,理解同步电路静态时序分析(STA)的方法和时序报告。

西安交通大学微电子学实验室实验1setup和synthesis流程实验准备有两种界面可以运行Design Compiler:1)命令行界面,dc_shell-xg-t;2)图形用户界面(GUI),Design Vision。

本次实验主要运用GUI模式。

图1.1给出了RTL逻辑综合的直观概念和简要流程。

图1.1 RTL逻辑综合的直观概念和简要流程。

在DC中,总共有8种设计对象:z设计(Design):一种能完成一定逻辑功能的电路。

设计中可以包含下一层的子设计。

z单元(Cell):设计中包含的子设计的实例。

z参考(Reference):单元的参考对象,即单元是参考的实例。

z端口(Port):设计的基本输入输出口。

z管脚(Pin):单元的输入输出口。

z连线(Net):端口间及管脚间的互连线。

d c使用教程-CAL-FENGHAI.-(YICAI)-Company One1DC使用说明文件说明:在进行下面的演示时需要用到两个文件,一个是,它是描述一个电路的verilog代码,我们的目标就是用DC综合这个代码得到满足约束条件的电路网表;另一个是,它是综合的脚本文件。

这两个文件都在/home/student1000目录下,大家把它们拷贝到自己的目录下,以备使用。

DC既可使用图形界面,也可不使用图形界面而直接运行脚本来综合电路。

一、DC图形界面的使用。

1.DC图形界面的启动打开一个终端窗口,写入命令 dv –db_mode,敲入回车。

则DC图形界面启动,如下图所示红框处是DC的命令输入框,以下在图形界面上的操作都可以在命令输入框中输入相应的命令来完成。

选择Help-----Man Pages可以查看DC的联机帮助。

相应指令:man。

例:man man表示查看man命令的帮助。

man create_clock表示查看creat_clock命令的帮助。

2.设置库文件选择File----Setup需要设置以下库文件,如下图。

相应指令:set search_path [list /tools/lib/smic25/feview_s/version1/STD/Synopsys \ /tools/lib/smic25/feview_s/version1/STD/Symbol/synopsys]set target_library { }set link_library { }set symbol_library { }点OK,设置完成。

3.读入verilog文件选择File---Read在打开文件对话框中选中要打开的文件,在这里我们选中文件。

在Log框中出现successfully字样表明读入文件成功。

相应命令:read_file点击红色箭头所指的按钮可以查看该电路的symbol图。

4.设置约束条件4.1设置时钟约束在symbol图上选中clk端口选择Attributes-----Specify Clock出来设置时钟约束的对话框,按下图设置,给时钟取名为clock,周期20ns,上升沿0ns,下降沿10ns。

设置启动dc_shell-t工具的.synopsys.setup文件Author:周建伟Company:西安邮电大学SOC组Date:2013.10.30摘要:若你在读不进你的库,即在你的运行报告中总是有:warning:Can‟t read link_library file …your_library.db‟,这边文档会对你有一定的帮助逻辑综合环境启动文件启动文件用来指定综合工具所需要的一些初始化信息。

DC使用名为“.synopsys_dc.setup”的启动文件(位置:inst_dir/admin/setup/.synopsys_dc.setup)。

启动时,DC会以下述顺序搜索并装载相应目录下的启动文件:DC安装目录($DC_PATH/admin/setup)用户主目录工具启动目录注意:后装载的启动文件中的设置将覆盖先装载的启动文件中的相同设置本文档重在讲述怎么设置工具启动目录1、把inst_dir/admin/setup/.synopsys_dc.setup文件拷贝到你DC脚本目录下(也就是和你脚本在同个目录下)2、在.synopsys_dc.setup文件的第92行,即set link_force_case “check_reference”命令下修改内容如下:A、set lib_path /library/smic18/feview~2/version2.2(注:lib_path为你smic18库安装目录,不同于DC安装目录)B、set link_library [list * $lib_path/STD/Synopsys/smic18_ss.db \$lib_path/IO/Synopsys/smic18IO_line_ss.db \$lib_path/IO/Synopsys/smic18IO_stagger_ss.db ]C、set search_path [list . ${synopsys_root}/libraries/syn ${synopsys_root}/dw/syn_ver \${synopsys_root}/dw/sim_ver \$lib_path/STD/Synopsys $lib_path/IO/Synopsys ]D、set target_library [list $lib_path/STD/Synopsys/smic18_ss.db \$lib_path/IO/Synopsys/smic18IO_line_ss.db \$lib_path/IO/Synopsys/smic18IO_stagger_ss.db ]E、set synthetic_library “”set command_log_file “./command.log”set designer “zjw”set company “soc of xupt”set find_converts_name_lists “false”F、set symbol_library $lib_path/STD/Symbol/synopsys/smic18.sdb。

d c使用教程-CAL-FENGHAI.-(YICAI)-Company One1DC使用说明文件说明:在进行下面的演示时需要用到两个文件,一个是,它是描述一个电路的verilog代码,我们的目标就是用DC综合这个代码得到满足约束条件的电路网表;另一个是,它是综合的脚本文件。

这两个文件都在/home/student1000目录下,大家把它们拷贝到自己的目录下,以备使用。

DC既可使用图形界面,也可不使用图形界面而直接运行脚本来综合电路。

一、DC图形界面的使用。

1.DC图形界面的启动打开一个终端窗口,写入命令 dv –db_mode,敲入回车。

则DC图形界面启动,如下图所示红框处是DC的命令输入框,以下在图形界面上的操作都可以在命令输入框中输入相应的命令来完成。

选择Help-----Man Pages可以查看DC的联机帮助。

相应指令:man。

例:man man表示查看man命令的帮助。

man create_clock表示查看creat_clock命令的帮助。

2.设置库文件选择File----Setup需要设置以下库文件,如下图。

相应指令:set search_path [list /tools/lib/smic25/feview_s/version1/STD/Synopsys \ /tools/lib/smic25/feview_s/version1/STD/Symbol/synopsys]set target_library { }set link_library { }set symbol_library { }点OK,设置完成。

3.读入verilog文件选择File---Read在打开文件对话框中选中要打开的文件,在这里我们选中文件。

在Log框中出现successfully字样表明读入文件成功。

相应命令:read_file点击红色箭头所指的按钮可以查看该电路的symbol图。

4.设置约束条件4.1设置时钟约束在symbol图上选中clk端口选择Attributes-----Specify Clock出来设置时钟约束的对话框,按下图设置,给时钟取名为clock,周期20ns,上升沿0ns,下降沿10ns。

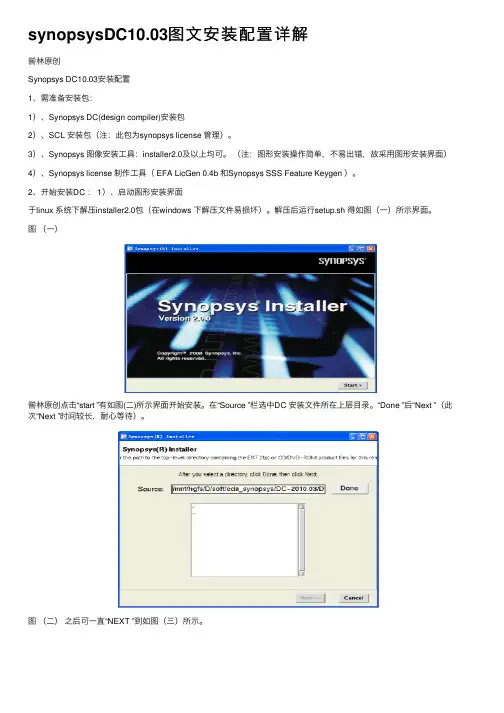

synopsysDC10.03图⽂安装配置详解喾林原创Synopsys DC10.03安装配置1、需准备安装包:1)、Synopsys DC(design compiler)安装包2)、SCL 安装包(注:此包为synopsys license 管理)。

3)、Synopsys 图像安装⼯具:installer2.0及以上均可。

(注:图形安装操作简单,不易出错,故采⽤图形安装界⾯)4)、Synopsys license 制作⼯具( EFA LicGen 0.4b 和Synopsys SSS Feature Keygen )。

2、开始安装DC : 1)、启动图形安装界⾯于linux 系统下解压installer2.0包(在windows 下解压⽂件易损坏)。

解压后运⾏setup.sh 得如图(⼀)所⽰界⾯。

图(⼀)喾林原创点击“start ”有如图(⼆)所⽰界⾯开始安装。

在“Source ”栏选中DC 安装⽂件所在上层⽬录。

“Done ”后“Next ”(此次“Next ”时间较长,耐⼼等待)。

图(⼆)之后可⼀直“NEXT ”到如图(三)所⽰。

图(三)在该界⾯勾选linux选项即可,继续下⼀步到如图(四)所⽰。

选择安装路径后继续下⼀步直到结束。

喾林原创图(四)⾄此DC安装结束。

3、开始安装SCL:此安装与DC安装步骤⼀直,⼏乎没有差别,唯⼀不同的就是安装路径不同。

4、license的制作:License的制作是在windows下制作的。

1)、打开EFA LicGen 0.4b⽂件夹运⾏LicGen.exe程序出现如图(五)所⽰界⾯。

喾林原创图(五)点击“OPEN”选择Synopsys.lpd⽂件,“打开”。

回到图(五)所⽰界⾯。

勾选上Custon、Use Daemon及最后⼀个Custon。

喾林原创在两个“Custon ”后输⼊Linux 系统的MAC 。

注:Linux MAC 获取命令。

A :lmhostid 下图(六)红线处即为 MAC 。

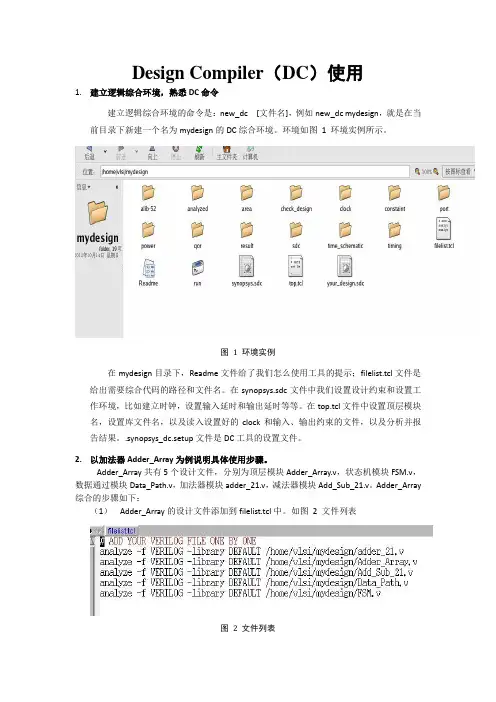

Design Compiler(DC)使用1.建立逻辑综合环境,熟悉DC命令建立逻辑综合环境的命令是:new_dc [文件名],例如new_dc mydesign,就是在当前目录下新建一个名为mydesign的DC综合环境。

环境如图1 环境实例所示。

图1 环境实例在mydesign目录下,Readme文件给了我们怎么使用工具的提示;filelist.tcl文件是给出需要综合代码的路径和文件名。

在synopsys.sdc文件中我们设置设计约束和设置工作环境,比如建立时钟,设置输入延时和输出延时等等。

在top.tcl文件中设置顶层模块名,设置库文件名,以及读入设置好的clock和输入、输出约束的文件,以及分析并报告结果。

.synopsys_dc.setup文件是DC工具的设置文件。

2.以加法器Adder_Array为例说明具体使用步骤。

Adder_Array共有5个设计文件,分别为顶层模块Adder_Array.v,状态机模块FSM.v,数据通过模块Data_Path.v,加法器模块adder_21.v,减法器模块Add_Sub_21.v。

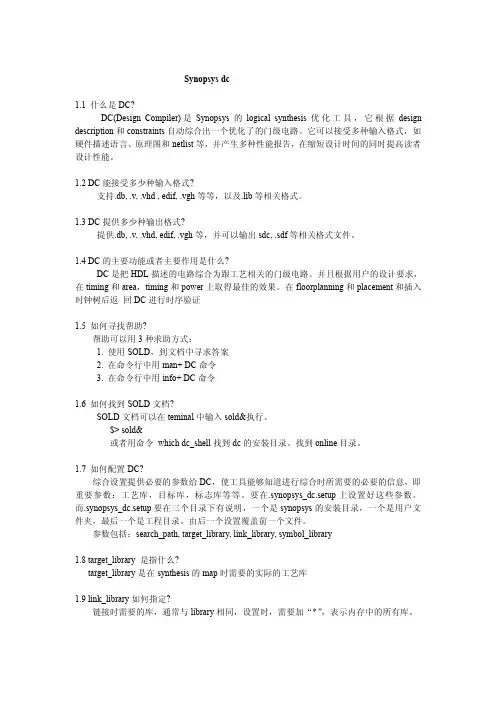

Adder_Array 综合的步骤如下:(1)Adder_Array的设计文件添加到filelist.tcl中。

如图2 文件列表图2 文件列表(2)在top.tcl中将顶层模块设置为Adder_Array。

如图3修改顶层模块名图3 修改顶层模块名(3)修改synopsys.sdc实现以下设计约束:时钟周期1.2ns,input_delay设置为0.5ns,output_delay设置为0.5ns。

如果使用者想增加其他的设计约束可以在此文件中增添。

(4)进入刚才建好的综合环境,在终端中执行run命令,调用Design Compiler执行逻辑综合。

打开终端:cd [建好的环境路径],进入后输入run,即可。

(5)等逻辑综合执行完毕后,查看123.log,对其中的error和warning进行确认,如果有问题修改设计或综合脚本后重新综合,直至没有问题。

DC学习----第一章基本概念作者:未知时间:2010-08-15 15:02:50 来自:网络转载1.1 启动文件启动文件用来指定综合工具所需要的一些初始化信息。

DC使用名为“.synopsys_dc.setup”的启动文件,启动时,DC会以下述顺序搜索并装载相应目录下的启动文件:1)、DC的安装目录;2)、用户的home目录;3)、当前启动目录。

注意:后装载的启动文件中的设置将覆盖先装载的启动文件中的相同设置。

下面是一个DC启动文件的实例,它包含了几乎所有重要的设置,下文将结合该实例解释启动文件中各项设置的具体含义。

例1-1(一个DC启动文件):search_path= search_path + {“.”, synopsys_root + “/dw/sim_ver” }search_path= search_path + { “~/risc32/synthesis/libraries” }target_library={ tcb773stc.db }synthetic_library={dw_foundation.sldb}link_library = { “*”, dw_foundation.sldb, tcb773stc.db }symbol_library = { tcb773s.sdb }synlib_wait_for_design_license = {"DesignWare-Foundation"}alias rt “report_timing”designer= XXXXXcompany= “ASIC Lab, Fudan Univ.”search_path指定了综合工具的搜索路径。

target_library为综合的目标库,它一般是由生产线提供的工艺相关的库。

synthetic_library是综合库,它包含了一些可综合的与工艺无关的IP。

dw_foundation.sldb是Synopsys提供的名为Design Ware的综合库,它包含了基本的算术运算逻辑、控制逻辑、可综合存储器等IP,在综合是调用这些IP有助于提高电路性能和减少综合时间。

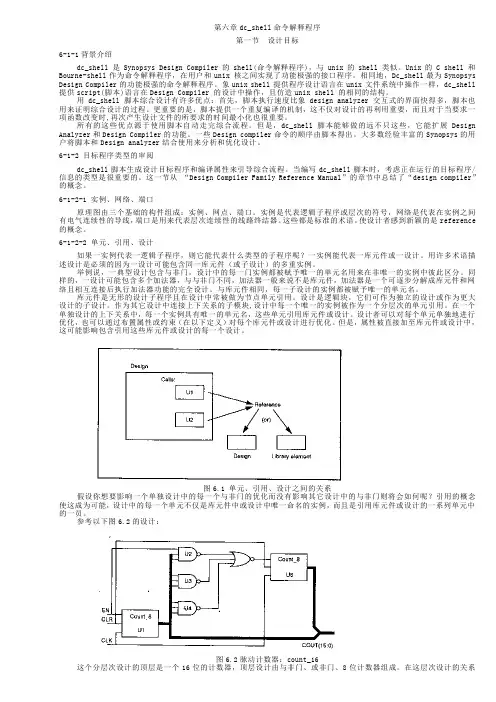

第六章dc_shell命令解释程序第一节设计目标6-1-1背景介绍dc_shell 是Synopsys Design Compiler的shell(命令解释程序),与unix的shell 类似。

Unix的C shell 和Bourne-shell作为命令解释程序,在用户和unix 核之间实现了功能极强的接口程序。

相同地,Dc_shell最为Synopsys Design Compiler的功能极强的命令解释程序。

象unix shell 提供程序设计语言在unix 文件系统中操作一样,dc_shell 提供script(脚本)语言在Design Compiler 的设计中操作,且仿造unix shell 的相同的结构。

用dc_shell 脚本综合设计有许多优点:首先,脚本执行速度比象design analyzer 交互式的界面快得多,脚本也用来证明综合设计的过程。

更重要的是,脚本提供一个重复编译的机制,这不仅对设计的再利用重要,而且对于当要求一项函数改变时,再次产生设计文件的所要求的时间最小化也很重要。

所有的这些优点源于使用脚本自动走完综合流程。

但是,dc_shell 脚本能够做的远不只这些,它能扩展Design Analyzer和Design Compiler的功能。

一些Design compiler命令的顺序由脚本得出。

大多数经验丰富的Synopsys的用户将脚本和Design analyzer结合使用来分析和优化设计。

6-1-2 目标程序类型的审阅dc_shell脚本生成设计目标程序和编译属性来引导综合流程。

当编写dc_shell脚本时,考虑正在运行的目标程序/信息的类型是很重要的。

这一节从“Design Compiler Family Reference Manual”的章节中总结了“design compiler”的概念。

6-1-2-1 实例、网络、端口原理图由三个基础的构件组成:实例、网点、端口。

Design Compiler使用说明一.软件说明Design Compiler是synopsys的综合软件,它的功能是把RTL级的代码转化为门级网表。

综合包括转译(Translation),优化(Opitimization),映射(Mapping)三个过程。

在转译的过程中,软件自动将源代码翻译成每条语句所对应的功能模块以及模块之间的拓扑结构,这一过程是在综合器内部生成电路的布尔函数的表达,不做任何的逻辑重组和优化。

优化:基于所施加的一定时序和面积的约束条件,综合器按照一定的算法对转译结果作逻辑优化和重组。

在映射过程中,根据所施加的一定的时序和面积的约束条件,综合器从目标工艺库中搜索符合条件的单元来构成实际电路。

DC有两种界面,图形界面通过敲入design vision&调用出来,另一种命令行界面通过dc_shell-t调用。

建议初学者使用图形界面,因为图形界面比较容易上手;业界的人士比较青睐命令行界面,因为其所耗的资源少,并且将所用的命令写成综合脚本的形式,便于查阅。

因为门级和代码级不同,代码级考虑的是理想情况,但是实际电路不是这样的,它有门级的延时,线的延时,信号的转换时间,甚至时钟信号到达各个触发器的时间不相等。

基于这些考虑,DC通过施加约束,模拟实际环境,根据实际情况得出门级网表。

因此如何适当的施加约束是DC的关键所在。

二.库的配置通过上述说明可知,DC需要通用库和工艺库的支持,DC用到的工艺库是.db或者是.lib格式的,其中.lib格式的文件是可读得,通过此文件可以了解库的详细信息,比如说工作电压,操作温度,工艺偏差等等。

.db格式的库是二进制的,不可读。

.db格式的库由.lib格式的库通过命令read_lib生成。

目标工艺库(Target_library):是指将RTL级的HDL描述到门级时所需的标准单元综合库,它是由芯片制造商(Foundry)提供的,包含了物理信息的单元模型。

第六章dc_shell命令解释程序第一节设计目标6-1-1背景介绍dc_shell 是Synopsys Design Compiler的shell(命令解释程序),与unix的shell 类似。

Unix的C shell 和Bourne-shell作为命令解释程序,在用户和unix 核之间实现了功能极强的接口程序。

相同地,Dc_shell最为Synopsys Design Compiler的功能极强的命令解释程序。

象unix shell 提供程序设计语言在unix 文件系统中操作一样,dc_shell 提供script(脚本)语言在Design Compiler 的设计中操作,且仿造unix shell 的相同的结构。

用dc_shell 脚本综合设计有许多优点:首先,脚本执行速度比象design analyzer 交互式的界面快得多,脚本也用来证明综合设计的过程。

更重要的是,脚本提供一个重复编译的机制,这不仅对设计的再利用重要,而且对于当要求一项函数改变时,再次产生设计文件的所要求的时间最小化也很重要。

所有的这些优点源于使用脚本自动走完综合流程。

但是,dc_shell 脚本能够做的远不只这些,它能扩展Design Analyzer和Design Compiler的功能。

一些Design compiler命令的顺序由脚本得出。

大多数经验丰富的Synopsys的用户将脚本和Design analyzer结合使用来分析和优化设计。

6-1-2 目标程序类型的审阅dc_shell脚本生成设计目标程序和编译属性来引导综合流程。

当编写dc_shell脚本时,考虑正在运行的目标程序/信息的类型是很重要的。

这一节从“Design Compiler Family Reference Manual”的章节中总结了“design compiler”的概念。

6-1-2-1 实例、网络、端口原理图由三个基础的构件组成:实例、网点、端口。

前言:这是本人经过两个星期的奋斗,从对linux命令的生涩到熟练,对后端工具的陌生到熟悉的一段战斗史!!!下面我把我的操作过程详细写下,供大家学习参考!!一:准备工作所需平台1、vmware92、RHEL(红帽企业版)6。

3Synopsys 工具1、installer_v3。

0(安装synopsys EDA tools 的图形界面的安装工具)2、scl_10.9。

3(synopsys license 管理工具,用于启动tools 的features)3、dc_2009。

06(逻辑综合工具)4、icc_2009。

06(布局布线工具)5、pt_2012。

12(时序分析工具)License生成工具1、EFA LicGen 0.4b2、Synopsys SSS Feature Keygen3、Synposys。

src(最新的据我所知是40kb大小,有比较全的features)二:搭建RHEL1、安装vmware:本章节详见另一个文档.文档名为“vmware安装手册”.还有一份汉化包,需要可自行下载。

2、安装RHEL:本章详见另一个文档.文档名为“RHEL6。

3安装手册”。

Ps:有一个页面会让你选择安装的软件包,这个时候人工勾上所有的软件包,不然启eda 工具的时候会发现很多系统库找不到。

三:vmware tools安装1、以root用户进入linux,找到左上角的VM选项,下拉之后选择安装wmwaretools.过一会儿会弹出来一个框框,显示vmwaretools—9。

2。

2-893683.tar.gz然后新开一个终端,输入cd /media 你会看到vmwaretools—9。

2。

2—893683.tar。

gz就在那里。

然后把他拷贝出来,后解压安装。

具体命令可以网上搜索。

四:license制作License制作要用到上述的材料,具体详见另一个文档。

文档名为“license制作”.将license文件,即synopsys。

Synopsys 综合工具Design Compiler(DC)简介一.约束的基本概念:约束就是对用户的设计中可度量的电路参数(如时序、面积以及电容等)进行声明。

没有约束,工具(本文为DC)就不能有效地优化电路,以满足要求。

当DC对设计进行优化时,使用了两类约束:1)设计规则约束(Design Rule Constraints,DRC):此类约束是工具固有的,由工艺库(technology library)来定义。

此类约束是设计功能正确的必要条件,通过库应用于所有设计上。

当然,你可以将它们定义的更紧。

2)优化约束(Optimization Constraints):它们是由用户定义的,前提是可实现的。

用户在使用DC时,可以通过命令行或编写约束文件(.scr)来定义约束。

下图给出DC 主要的DRC及优化约束,以及相关的DC命令(dc_shell接口命令)。

DRC:最大转换时间(Max Transition Time):对于一条连线(net)来说,是其驱动pin逻辑值转化的最长时间。

最大扇出(Max Fanout):对于驱动pin来讲。

最大/最小电容(Max/Min Capacitance):用来控制连线的电容值。

器件退化(Cell Degradation):某些工艺库包括器件退化表,它列举了某一器件可驱动的最大电容,是该器件输入pin最大转换时间的函数。

优化约束:时序约束:包括输入/输出延迟(Input/Output Delay):同步路径最大/最小延迟(Minimum/Maximum Delay):异步路径最大面积(门数):最小孔隙度(Min porosity):可布线性二.约束报告约束报告提供了设计规则和优化约束的信息。

可采用如下命令产生相应报告:report_constraintreport_portreport_clockreport_attributereport_timing_requirements用户可通过输出相应报告,来分析设计是否满足了约束。

逻辑综合工具Design Compiler使用教程编者:适用专业:电子科学与技术沈阳理工大学信息学院2010年6月图形界面design vision操作示例逻辑综合主要是将HDL语言描述的电路转换为工艺库器件构成的网表的过程。

综合工具目前比较主流的是synopsys公司Design Compiler,我们在设计实践过程中采用这一工具。

Design compiler有两种工作模式,一种是tcl模式,另一种为图形模式。

在设计中为增强直观性,采用图形界面design vision。

TCL命令行模式可在设计过程中摸索熟悉,并使之成为习惯。

tcl模式在启动工具之前,准备工作有四项:设计的HDL源文件、采用的工艺库文件、设计的约束文件、工具的启动文件。

图形界面模式最少需要前两项,这里不作多说明。

1. 启动工具登陆Linux之后进入的目录即是用户的家目录,在家目录下建立dcLab作为本次实验dc的操作主目录。

在dcLab目录下,建立设计存放目录如source、约束文件目录如constrn、输出网表文件目录ntlst、报告输出目录rpt、log文件目录log、dc启动目录work,等等。

实验室中的工作站存放有umc公司和tsmc公司的0.18um标准单元库的所有文件,存放在目录:/usr/eda/designKit/下面,设计过程中需要查找的话注意路径与示例中的图片上所示路径稍有不同。

Design compiler工具在工作站中已经安装完毕,且用户的环境变量和license 也已设置完成,登录之后直接启动工具即可。

如果打开终端之后无法启动工具,可能就是license没有启动,需要首先采用命令:start_slic启动license,然后design vision才能正常开启与工作。

建立相关的工程目录之后,进入本次实验的工作目录:~/dcLab/work后,采用启动命令:design_vision&,启动工具后相应的界面如下图1所示。

ICC_lab1:数据设置和基本流程最近在学习后端的流程,做lab是最好不过了。

但是有时候做过了lab,过了一段时间之后就会忘记,因此需要自己总结一下,加强印象。

ICC_lab1:数据设置和基本流程数据设置:一、数据准备:在启动ICC之前,需要准备好下面的文件:(1)非库文件①ICC启动的环境设置文件:.synopsys_dc.setup文件,这个以后是需要我们书写的。

主要的设置内容有:·禁止显示一些警告,比如创建库、布局布线过程中的一些警告;·设置一些有用的功能操作(ICC中没有的),需要相应的设置文件·设置一些变量开关状态(开或者关)·设置允许记录shell的命令信息·设置一些关联命令·逻辑库设置(设置search_path ,target_libr,link_library,设置min库:包括标准单元库、IO库、ram库),这就需要库了·定义一些变量,这些变量内容是不同路径下一些文件的名称②设计的verilog门级网表:.v文件,这个文件可以通过综合完成,不需要我们生成。

③设计的平面布局图:.def文件,这个文件在本次实验中用到,这个通过布局规划得到,以后需要我们自己生成。

④时序约束文件:.sdc文件,主要是时序的约束,这个文件可以从.sdc(标准设计约束)文件得到,不需要我们书写。

⑤时序和优化控制文件:opt_ctrl.tcl文件,主要是对设计进行优化的设置,这个以后是需要我们自己书写的。

⑥检查零互联时的时序约束文件:zic_timing.tcl文件,主要是检查设计在0负载的时候,时序的情况。

这个以后需要我们自己书写。

⑦创建电源和地的逻辑连接文件:derive_pg.tcl文件。

顾名思义就是创建电源和地的逻辑连接;以后这个文件需要我们自己书写。

(2)参考库文件(ref文件夹),主要有:(参考库不需要我们书写,但是需要我们熟悉,因为在上面的设置中,需要用到这些库)·普通的库文件(db):里面有标准单元库、IO单元库、RAM宏单元库等·参考的milkyway物理库(mw_lib):里面有各种单元库(IO单元、标准单元等)文件夹·工艺库文件夹(tech):主要是.tf工艺库文件·寄生参数库(tlup):主要是RC参数(.tluplus库文件),用来提取寄生参数用。

启动dc_shell工具的.synopsys.setup文档

设置启动dc_shell-t工具

的

.synopsys.setup文件

Author:周建伟

Company:西安邮电大学SOC组

Date:2013.10.30

摘要:若你在读不进你的库,即在你的运行报告

中总是有:warning:Can’t read link_library file ‘your_library.db’,这边文档会对你有一定的帮助

逻辑综合环境

启动文件

启动文件用来指定综合工具所需要的一些初始化信息。

DC使用名为“.synopsys_dc.setup”的启动文件(位置:inst_dir/admin/setup/.synopsys_dc.setup)。

启动时,DC会以下述顺序搜索并装载相应目录下的启动文件:

DC安装目录($DC_PATH/admin/setup)

用户主目录

工具启动目录

注意:后装载的启动文件中的设置将覆盖先装载的启动文件中的相同设置

本文档重在讲述怎么设置工具启动目录

1、把inst_dir/admin/setup/.synopsys_dc.setup

文件拷贝到你DC脚本目录下(也就是和你脚本在同个目录下)

2、在.synopsys_dc.setup文件的第92行,即set

link_force_case “check_reference”命令下修

改内容如下:

A、s et lib_path

/library/smic18/feview~2/version2.2(注:

lib_path为你smic18库安装目录,不同于

DC安装目录)

B、set link_library [list *

$lib_path/STD/Synopsys/smic18_ss.db \

$lib_path/IO/Synopsys/smic18IO_line_ss.db \

$lib_path/IO/Synopsys/smic18IO_stagger_ss. db ]

C、s et search_path [list .

${synopsys_root}/libraries/syn

${synopsys_root}/dw/syn_ver \

${synopsys_roo t}/dw/sim_ver \

$lib_path/STD/ Synopsys $lib_path/IO/Synopsys ]

D、s et target_library [list

$lib_path/STD/Synopsys/smic18_ss.db \

$lib_path/IO/Synopsys/smic18IO_line_ss.db \

$lib_path/IO/Synopsys/smic18IO_stagger_ss. db ]

E、set synthetic_library “”

set command_log_file “./command.log”

set designer “zjw”

set company “soc of xupt”

set find_converts_name_lists “false”

F、set symbol_library $lib_path/STD/Symbol/synopsys/smic18.sdb。