systemverilog面试

- 格式:doc

- 大小:22.00 KB

- 文档页数:10

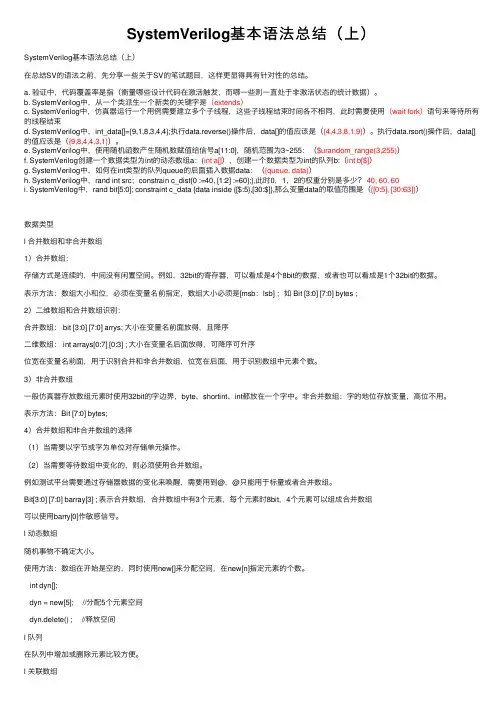

SystemVerilog基本语法总结(上)SystemVerilog基本语法总结(上)在总结SV的语法之前,先分享⼀些关于SV的笔试题⽬,这样更显得具有针对性的总结。

a. 验证中,代码覆盖率是指(衡量哪些设计代码在激活触发,⽽哪⼀些则⼀直处于⾮激活状态的统计数据)。

b. SystemVerilog中,从⼀个类派⽣⼀个新类的关键字是(extends)c. SystemVerilog中,仿真器运⾏⼀个⽤例需要建⽴多个⼦线程,这些⼦线程结束时间各不相同,此时需要使⽤(wait fork)语句来等待所有的线程结束d. SystemVerilog中,int_data[]={9,1,8,3,4,4};执⾏data.reverse()操作后,data[]的值应该是({4,4,3,8,1,9})。

执⾏data.rsort()操作后,data[]的值应该是({9,8,4,4,3,1})。

e. SystemVerilog中,使⽤随机函数产⽣随机数赋值给信号a[11:0],随机范围为3~255:($urandom_range(3,255))f. SystemVerilog创建⼀个数据类型为int的动态数组a:(int a[]),创建⼀个数据类型为int的队列b:(int b[$])g. SystemVerilog中,如何在int类型的队列queue的后⾯插⼊数据data:({queue, data})h. SystemVerilog中,rand int src;constrain c_dist{0 :=40, [1:2] :=60};},此时0,1,2的权重分别是多少? 40, 60, 60i. SystemVerilog中,rand bit[5:0]; constraint c_data {data inside {[$:5},[30:$]},那么变量data的取值范围是({[0:5], [30:63]})数据类型l 合并数组和⾮合并数组1)合并数组:存储⽅式是连续的,中间没有闲置空间。

低功耗验证解决方案August 20, 2010林雪梅linxuemei@王凤海wangfenghai@王欣 wangxin@中星微电子有限公司摘要随着便携性要求的提高,低功耗设计的需求推动了低功耗设计技术在多电压,电压内部管理等技术上的突破。

以MTCMOS/ AVS等一系列技术为代表的设计方案越来越多的应用,让传统的数字电路验证技术受到了越来越大的挑战。

本文通过对现有解决方案的应用,将介绍如何引入业界标准的UPF流程完成多项低功耗设计的验证,以确保电源管理的正确实现。

ABSTRACTAs the requirements of portal devices keep increasing, new design techniques, including multi-voltage, MTCMOS, AVS, etc., are adopted in many low power devices. These design techniques further brings new verification challenges, which are new but critical. This paper, by applying existing solutions, introduces how to apply UPF flow, an industry standard, to verify low power designs. So the management of power supplies can be verified.1.0 简介嵌入式应用是目前SOC芯片最重要的应用之一。

在嵌入式应用,尤其是便携设备的应用中,功耗成为设计者越来越关注的因素。

20世纪80年代,大规模集成电路的发展导致了硬件描述语言(Verilog和VHDL)和综合工具的出现;到了90年代,设计复用以及IP的利用成为了IC设计经常采用的技术。

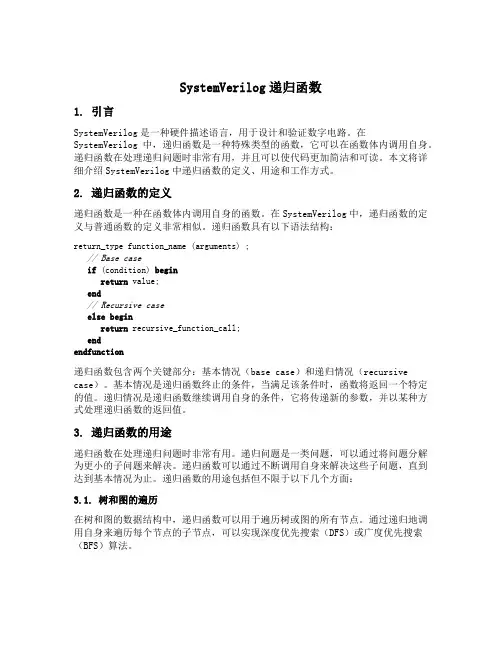

SystemVerilog递归函数1. 引言SystemVerilog是一种硬件描述语言,用于设计和验证数字电路。

在SystemVerilog中,递归函数是一种特殊类型的函数,它可以在函数体内调用自身。

递归函数在处理递归问题时非常有用,并且可以使代码更加简洁和可读。

本文将详细介绍SystemVerilog中递归函数的定义、用途和工作方式。

2. 递归函数的定义递归函数是一种在函数体内调用自身的函数。

在SystemVerilog中,递归函数的定义与普通函数的定义非常相似。

递归函数具有以下语法结构:return_type function_name (arguments) ;// Base caseif (condition) beginreturn value;end// Recursive caseelse beginreturn recursive_function_call;endendfunction递归函数包含两个关键部分:基本情况(base case)和递归情况(recursive case)。

基本情况是递归函数终止的条件,当满足该条件时,函数将返回一个特定的值。

递归情况是递归函数继续调用自身的条件,它将传递新的参数,并以某种方式处理递归函数的返回值。

3. 递归函数的用途递归函数在处理递归问题时非常有用。

递归问题是一类问题,可以通过将问题分解为更小的子问题来解决。

递归函数可以通过不断调用自身来解决这些子问题,直到达到基本情况为止。

递归函数的用途包括但不限于以下几个方面:3.1. 树和图的遍历在树和图的数据结构中,递归函数可以用于遍历树或图的所有节点。

通过递归地调用自身来遍历每个节点的子节点,可以实现深度优先搜索(DFS)或广度优先搜索(BFS)算法。

3.2. 排列和组合递归函数可以用于生成排列和组合。

通过递归地调用自身,并在每次调用中选择不同的元素,可以生成所有可能的排列和组合。

3.3. 数字运算递归函数可以用于处理数字运算,例如计算阶乘、斐波那契数列等。

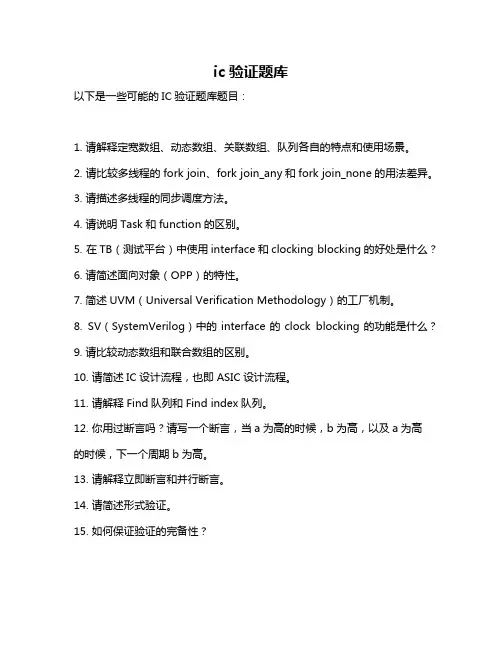

ic验证题库

以下是一些可能的IC验证题库题目:

1. 请解释定宽数组、动态数组、关联数组、队列各自的特点和使用场景。

2. 请比较多线程的fork join、fork join_any和fork join_none的用法差异。

3. 请描述多线程的同步调度方法。

4. 请说明Task和function的区别。

5. 在TB(测试平台)中使用interface和clocking blocking的好处是什么?

6. 请简述面向对象(OPP)的特性。

7. 简述UVM(Universal Verification Methodology)的工厂机制。

8. SV(SystemVerilog)中的interface的clock blocking的功能是什么?

9. 请比较动态数组和联合数组的区别。

10. 请简述IC设计流程,也即ASIC设计流程。

11. 请解释Find队列和Find index队列。

12. 你用过断言吗?请写一个断言,当a为高的时候,b为高,以及a为高

的时候,下一个周期b为高。

13. 请解释立即断言和并行断言。

14. 请简述形式验证。

15. 如何保证验证的完备性?

以上题目主要涉及到了SystemVerilog数据类型、Verilog时序电路、SV 线程通信、覆盖率等方面的知识,仅供参考,建议查阅专业书籍或咨询专业人士获取更准确的信息。

uvm system verilog总结### UVM System Verilog 总结#### 导语UVM(Universal Verification Methodology)与System Verilog的结合,为芯片设计验证领域带来了革新。

这种方法论不仅提高了验证效率,还增强了验证的可重用性和覆盖率。

本文将全面总结UVM与System Verilog的相关概念、特点以及应用。

---#### 一、UVM与System Verilog概述**1.1 UVM简介**UVM是建立在System Verilog基础上的一个标准化验证方法论,旨在提供一种通用的、模块化的验证平台。

它通过将验证环境分层,实现了环境的可重用性和易于维护性。

**1.2 System Verilog简介**System Verilog是一种硬件描述和验证语言,结合了Verilog和VHDL的优点,并增加了面向对象编程的特性。

它在芯片设计和验证中广泛应用。

---#### 二、UVM的核心特点**2.1 面向对象**UVM采用面向对象的设计思想,将验证环境分为不同的类和层次,便于管理和重用。

**2.2 模块化**UVM的模块化设计使得验证环境可以根据不同的测试需求灵活组合和配置。

**2.3 自动化**UVM支持自动化测试,包括自动生成测试序列、自动检查和报告错误等。

---#### 三、System Verilog在UVM中的应用**3.1 非阻塞赋值**System Verilog的非阻塞赋值在UVM中用于描述硬件行为。

**3.2 面向对象编程**System Verilog的面向对象编程特性使得UVM可以定义基类和派生类,实现代码的复用。

**3.3 功能覆盖**利用System Verilog的功能覆盖(Functional Coverage)特性,UVM 可以全面检查设计功能的覆盖率。

---#### 四、UVM与System Verilog的结合优势**4.1 提高验证效率**UVM与System Verilog的结合使得验证人员可以快速搭建验证环境,提高验证效率。

system verilog 中randc用法-回复System Verilog中的randc用法System Verilog是一种硬件描述语言,用于设计和验证现代集成电路。

其中一个非常有用的特性是randc(random count)关键字,它可以在随机数生成过程中控制出现次数。

在本文中,我们将详细介绍randc关键字的用法,并提供一些具体的示例和注意事项。

一、randc简介randc是System Verilog中的一个关键字,它用于控制随机数生成的次数。

一般来说,当我们使用关键字rand时,系统会根据约束条件生成随机数。

然而,有时我们希望某些随机数只出现有限次数,而不是无限次数。

这时,我们可以使用randc关键字来限制生成随机数的次数。

二、randc语法randc关键字的语法如下所示:randc expression;其中,expression是一个任意类型的表达式,用于指定控制随机数次数的条件。

expression必须是一个非负整数,表示randc关键字所生成随机数的最大生成次数。

当生成的随机数达到expression指定的次数后,randc关键字将不再生成随机数。

三、randc示例下面我们将提供一些使用randc关键字的具体示例,以帮助读者更好地理解其用法。

1. 随机生成一个10位二进制数,其中1的个数最多为5。

randc bit [9:0] random_num;constraint count_ones {random_num.countones() <= 5;}......在上面的示例中,我们使用了randc关键字和countones()方法来生成一个10位的二进制数random_num,并设置了一个约束条件count_ones,限制该二进制数中1的个数不超过5个。

这样,我们就能够生成多个满足约束条件的随机数。

2. 随机生成一个8位十进制数,其中奇数的个数最多为3。

randc int unsigned [7:0] random_num;constraint count_odds {random_num.count() with (item 2 == 1)<= 3;}......在上面的示例中,我们定义了一个8位无符号十进制数random_num,并设置了一个约束条件count_odds,限制该十进制数中奇数的个数不超过3个。

systemverilog 结构体使用注意事项-回复SystemVerilog是一种硬件描述语言,结构体(struct)是SystemVerilog中的一种复合数据类型,用于将多个不同类型的变量组合在一起。

结构体的使用可以提高代码的可读性、可维护性和重用性。

然而,在使用结构体时,我们需要注意一些细节,以确保代码的正确性和性能。

首先,让我们来了解一下什么是SystemVerilog中的结构体。

结构体是一种用户自定义的数据类型,它由多个字段(field)组成,每个字段可以有不同的类型。

结构体可以用来表示一个复杂的对象,这个对象由不同类型的数据组成。

在SystemVerilog中,结构体的定义和使用非常灵活,可以满足多种设计需求。

以下是一些使用结构体时需要注意的事项:1. 结构体的定义在定义一个结构体时,需要指定结构体的名称和字段的名称以及对应的数据类型。

例如,我们可以定义一个结构体来表示一个学生的信息:typedef struct {string name;int age;float gpa;} student_t;在上面的例子中,我们定义了一个名为student_t的结构体,它有三个字段,分别为name(字符串类型)、age(整数类型)和gpa(浮点数类型)。

2. 结构体的声明和初始化在使用结构体之前,需要声明一个结构体变量,并对其进行初始化。

可以使用普通的声明方式或者使用结构体的构造函数对结构体进行初始化。

例如,我们可以声明一个名为student的结构体变量,并对其进行初始化:student_t student;student = new; = "Alice";student.age = 20;student.gpa = 3.5;在上面的例子中,我们声明了一个名为student的结构体变量,然后使用结构体的构造函数对其进行初始化,并设置其字段的值。

3. 结构体作为参数传递结构体可以作为函数的参数传递,可以通过引用或者值传递的方式传递结构体。

电子信息、通信、电类专业将会遇到的面试题大全!精!看了让人大吃一惊...模拟电路1、基尔霍夫定理的内容是什么?(仕兰微电子)基尔霍夫电流定律是一个电荷守恒定律,即在一个电路中流入一个节点的电荷与流出同一个节点的电荷相等.基尔霍夫电压定律是一个能量守恒定律,即在一个回路中回路电压之和为零.2、平板电容公式(C=εS/4πkd)。

(未知)3、最基本的如三极管曲线特性。

(未知)4、描述反馈电路的概念,列举他们的应用。

(仕兰微电子)5、负反馈种类(电压并联反馈,电流串联反馈,电压串联反馈和电流并联反馈);负反馈的优点(降低放大器的增益灵敏度,改变输入电阻和输出电阻,改善放大器的线性和非线性失真,有效地扩展放大器的通频带,自动调节作用)(未知)6、放大电路的频率补偿的目的是什么,有哪些方法?(仕兰微电子)7、频率响应,如:怎么才算是稳定的,如何改变频响曲线的几个方法。

(未知)8、给出一个查分运放,如何相位补偿,并画补偿后的波特图。

(凹凸)9、基本放大电路种类(电压放大器,电流放大器,互导放大器和互阻放大器),优缺点,特别是广泛采用差分结构的原因。

(未知)10、给出一差分电路,告诉其输出电压Y+和Y-,求共模分量和差模分量。

(未知)11、画差放的两个输入管。

(凹凸)12、画出由运放构成加法、减法、微分、积分运算的电路原理图。

并画出一个晶体管级的运放电路。

(仕兰微电子)13、用运算放大器组成一个10倍的放大器。

(未知)14、给出一个简单电路,让你分析输出电压的特性(就是个积分电路),并求输出端某点的rise/fall时间。

(Infineon笔试试题)15、电阻R和电容C 串联,输入电压为R和C之间的电压,输出电压分别为C上电压和R 上电压,要求制这两种电路输入电压的频谱,判断这两种电路何为高通滤波器,何为低通滤波器。

当RC<< period - setup ? hold16、时钟周期为T,触发器D1的建立时间最大为T1max,最小为T1min。

ic验证工程师面试题一、背景介绍IC验证工程师是集成电路(IC)设计领域中的重要职业,主要负责验证和测试设计的可行性、正确性以及功能性。

他们需要具备扎实的电子工程知识和熟练的验证技能,以确保IC设计符合设计要求并可以正常运行。

IC验证工程师的面试题目通常涉及各个方面的知识与技巧,下面是一些常见的面试题目。

二、面试题目1. 请简要介绍一下你的背景和经验,特别是在IC验证领域的工作经历。

2. 在IC验证过程中,你是如何确保设计的正确性和一致性的?3. 请解释一下什么是仿真和验证,以及它们在IC设计过程中的作用。

4. 如果你在验证过程中发现设计存在错误,你会如何解决和修复这些问题?5. 在IC验证中,你经常使用哪些工具和软件?请列举并简要介绍它们的功能。

6. 你是否熟悉基本的验证语言和工具,例如Verilog、SystemVerilog 和UVM?请详细说明你的经验。

7. 请解释一下Constrained Random Verification(约束随机验证)的概念,并说明其优势和应用场景。

8. 在验证过程中,你是否遇到过时间和资源限制的挑战?请分享并解决这些挑战的方法。

9. 在IC验证中,测试计划和测试用例的编写对于验证的成功至关重要。

请描述一下你编写测试计划和测试用例的方法或流程。

10. 在项目进展紧张的情况下,你是如何管理时间和任务的分配的?请分享你的时间管理和组织能力。

三、结束语以上是一些常见的IC验证工程师面试题目,通过回答这些问题,你可以展示出你在IC验证领域的知识和技能,体现你的经验和能力。

同时,你的回答也需要结合实际工作和项目经历,给面试官展示你的应变能力和解决问题的能力。

祝你在面试中取得成功!。

FPGA面试问题集锦制作者:曹飞制作日期:2013-12-091:时序约束的概念和基本策略?时序约束主要包括周期约束,偏移约束,静态时序路径约束三种。

通过附加时序约束可以综合布线工具调整映射和布局布线,使设计达到时序要求。

2、为什么一个标准的倒相器中P管的宽长比要比N管的宽长比大?(仕兰微电子)和载流子有关,P管是空穴导电,N管电子导电,电子的迁移率大于空穴,同样的电场下,N管的电流大于P管,因此要增大P管的宽长比,使之对称,这样才能使得两者上升时间下降时间相等、高低电平的噪声容限一样、充电放电的时间相等3:什么是时钟抖动?(jitter)时钟抖动是指芯片的某一个给定点上时钟周期发生暂时性变化,也就是说时钟周期在不同的周期上可能加长或缩短。

它是一个平均值为0的平均变量。

4:什么是同步逻辑和异步逻辑?同步逻辑是时钟之间有固定的因果关系。

异步逻辑是各时钟之间没有固定的因果关系。

同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变。

改变后的状态将一直保持到下一个时钟脉冲的到来,此时无论外部输入 x 有无变化,状态表中的每个状态都是稳定的。

异步时序逻辑电路的特点:电路中除可以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件,电路中没有统一的时钟,电路状态的改变由外部输入的变化直接引起。

5:同步电路和异步电路的区别:同步电路:存储电路中所有触发器的时钟输入端都接同一个时钟脉冲源,因而所有触发器的状态的变化都与所加的时钟脉冲信号同步。

异步电路:电路没有统一的时钟,有些触发器的时钟输入端与时钟脉冲源相连,只有这些触发器的状态变化与时钟脉冲同步,而其他的触发器的状态变化不与时钟脉冲同步。

6:时序设计的实质:时序设计的实质就是满足每一个触发器的建立/保持时间的要求。

7:建立时间与保持时间的概念?建立时间:触发器在时钟上升沿到来之前,其数据输入端的数据必须保持不变的最小时间。

system_verilog 验证小技巧与案例在SystemVerilog中,验证是非常重要的一步,可以帮助我们检查设计的正确性并确保其按预期工作。

以下是一些SystemVerilog验证的小技巧和案例。

1.使用断言(assertions)进行验证:断言是一种在代码中插入的逻辑语句,用于在运行时检查特定条件。

它们可以帮助我们捕捉设计中的错误和问题。

例如,对于一个FIFO设计,我们可以编写一个断言来检查写入和读取操作是否按照预期进行。

`assert (wr_en === (rd_en === 0));`这个断言会在写使能和读使能同时为1时进行验证,以确保读写操作不会同时进行。

2.使用模拟环境进行验证:在验证过程中,我们通常需要创建一个模拟环境来模拟设计的行为。

这个环境通常包括一个测试程序和设计的驱动程序、监听器和功能模型等。

测试程序主要用于生成输入和验证输出,而驱动程序则负责将测试向设计输入,监听器则用于捕获设计的输出并与期望值进行比较,功能模型则用于模拟设计的行为。

例如,对于一个简单的计数器设计,我们可以编写一个测试程序来递增计数器的值,并验证计数器的值是否按预期递增。

3.使用覆盖率分析:覆盖率分析是一种用于确定设计代码是否已被完全测试的方法。

SystemVerilog提供了覆盖率分析的功能,可以帮助我们确定代码的覆盖率,并找出未被完全测试的部分。

覆盖率分析可以使用covergroup和coverpoints来实现。

covergroup提供了用于组织和管理覆盖率数据的方法,而coverpoints则用于指定要测试的代码的特定部分。

例如,对于一个模块,我们可以使用covergroup来收集每个输入组合的覆盖率,并确定哪些输入组合尚未被测试到。

4.使用随机化测试:SystemVerilog提供了一些功能,例如randomize()和randomize_with(),可用于生成随机输入并对设计进行测试。

systemverilog bit 类型赋值-回复SystemVerilog是一种常用于硬件描述语言的编程语言,具有丰富的数据类型用于描述和操作硬件信号。

其中,bit类型是SystemVerilog中最基本的数据类型之一。

本文将逐步回答"SystemVerilog bit 类型赋值"这一主题,详细介绍bit类型的定义、赋值方式及使用。

I. 什么是bit类型bit是SystemVerilog中用于表示单个二进制位的数据类型。

它仅包含两个取值,即0和1,用于表示逻辑低和逻辑高。

在硬件描述中,bit类型常用于表示时钟信号、控制信号等数字信号。

II. 定义bit类型在SystemVerilog中,可以使用关键字"bit"来定义bit类型变量。

例如,以下代码片段定义了一个名为"signal_bit"的bit类型变量:bit signal_bit;定义后的bit类型变量默认值为逻辑低(0)。

III. bit类型的赋值方式有多种方式可以对bit类型进行赋值,例如直接赋值、位选择赋值和位切片赋值。

1. 直接赋值直接赋值是最简单的一种赋值方式,即将一个常量或变量的值赋给bit类型变量。

例如,signal_bit = 1;将bit类型变量signal_bit的值设置为逻辑高(1)。

2. 位选择赋值位选择赋值用于选择变量的特定位,并将特定位的值赋给bit类型变量。

语法形式为:bit_var = variable[index];其中,variable是一个bit向量或一个bit类型的变量,index表示待选择的位索引。

例如,bit [7:0] data = 8'b10101010;signal_bit = data[0];将bit向量data的第0位的值赋给bit类型变量signal_bit。

3. 位切片赋值位切片赋值用于选择变量的一个范围的位,并将该范围内的值赋给bit类型变量。

s y s t e m v e r i l o g面试Qi1)What is callback ?(Qi2)What is factory pattern ?(Qi3)Explain the difference between data types logic and reg and wire .(Qi4)What is the need of clocking blocks ?(Qi5)What are the ways to avoid race condition between testbench and RTL using SystemVerilog?(Qi6)Explain Event regions in SV.(Qi7)What are the types of coverages available in SV ?(Qi8)What is OOPS?(Qi9)What is inheritance and polymorphism?(Qi10)What is the need of virtual interfaces ?(Qi11)Explain about the virtual task and methods .(Qi12)What is the use of the abstract class?(Qi13)What is the difference between mailbox and queue?(Qi14)What data structure you used to build scoreboard?(Qi15)What are the advantages of linkedlist over the queue ?(Qi16)How parallel case and full cases problems are avoided in SV ?(Qi17)What is the difference between pure function and cordinary function ?(Qi18)What is the difference between $random and $urandom?(Qi19)What is scope randomization ?(Qi20)List the predefined randomization methods.(Qi21)What is the dfference between always_combo and always@(*)c?(Qi22)What is the use of packagess?(Qi23)What is the use of $cast?(Qi24)How to call the task which is defined in parent object into derived class ?(Qi25)What is the difference between rand and randc?(Qi26)What is $root?(Qi27)What is $unit?(Qi28)What are bi-directional constraints?(Qi29)What is solve...before constraint ?(Qi30)Without using randomize method or rand,generate an array of unique values? (Qi31)Explain about pass by ref and pass by value?(Qi32)What is the difference betweenbit[7:0] sig_1;byte sig_2;(Qi33)What is the difference between program block and module ?(Qi34)What is final block ?(Qi35)How to implement always block logic in program block ?(Qi36)What is the difference between fork/joins, fork/join_none fork/join_any ?(Qi37)What is the use of modports ?(Qi38)Write a clock generator without using always block.(Qi39)What is forward referencing and how to avoid this problem?(Qi40)What is circular dependency and how to avoid this problem ?(Qi41)What is cross coverage ?(Qi42)Describe the difference between Code Coverage and Functional Coverage Which is more important and Why we need them(Qi43)How to kill a process in fork/join?(Qi44)Difference between Associative array and Dynamic array ?(Qi45)Difference b/wProcedural and Concarent Assertions?(Qi46)What are the advantages of SystemVerilog DPI?(Qi47)how to randomize dynamic arrays of objects?(Qi48)What is randsequence and what is its use?(Qi49)What is bin?(Qi50)Initialwait_order(a,b,c);Which from below initial process will cause that above wait order will pass.a)ig initial begin#1;->a;->b;->c;endb)initial begin#1;->a;endalways @a->b;always@b-> c;c)initial begin#1;->a;#0 ->b;->>c;endinitial begin#1 ->a;#1 ->b;#1 ->c;end(Qi51)Why always block is not allowed in program block?(Qi52)Which is best to use to model transaction? Struct or class ?(Qi53)How SV is more random stable then Verilog?(Qi54)Difference between assert and expect statements?(Qi55)How to add a new processs with out disturbing the random number generator state ? (Qi56)What is the need of alias in SV?(Qi57)What would be the output of the following code and how to avoid it?for(int i=0; i<N;i++)beginforkint j = i;begin#10 $display(" value is 0",j);endjoin_noneendalways N,By using automatic Key word, This problem can be avoided .fori(int i=0; i<N;i++)beginforkautomatic int j =i;begin#10 $display(" value is 0",j);endjoin_noneend(Qi58)Is it possible for functions to return a array( memory) ?(Qi59) How to check weather randomization is ssuccessful or not?(Qi60)Do we need to call super.new() when extending a class ? What happens if we don't call?(Qi61)Equivalent construct to |-> 1?Ans:=>(Qi62)What is the need to implement explicitly a copy() method inside a transaction , whenwe can simple assign one object to other ?(Qi63)How different is the implementation of a struct can union in SV.(Qi64)What is "this"?(Qi65)What is tagged union ?(Qi66)What is "scope resolution operator"?(Qi67)What is the difference between Verilog Parameterized Macros and SystemVerilog Parameterized Macros?(Qi68)What is the difference betweenlogic data_1;var logic data_2;wire logic data_3j;bit data_4;var bit data_5;(Qi69)What is the difference between bits and logic?(Qi70)Write a Statemechine in SV styles.(Qi71)What is the difference between $rose and posedgec?(Qi72)What is advantage of program block over clockcblock w.r.t race condition?(Qi73)How to avoid the race condition between programblock ?(Qi74)What is the difference between assumes and assert?(Qi75)What is coverage driven verification?(Qi76)What is layered architecture ?(Qi77)What are the simulation phases in your verification environment?(Qi78)How to pick a element which is in queue from random index?(Qi79)What data structure is used to store data in your environment and why ?(Qi80)What is casting? Explain about the various types of casting available in SV.(Qi81)How to importuall the items declared inside a package ?(Qi82)Explain how the timescale unit and precision are taken when a module does not have any timescalerdeclaration in RTL?(Qi83)What is streaming operator and what is its use?(Qi84)What are void functions ?(Qi85)How to make sure that a function argument passed has ref is not changed by the function?(Qi86)What is the use of "extern"?(Qi87)What is the difference between initial block and final block?Ans:You can't schedule an event or have delays in final block.(Qi88)How to check weather a handles is holding object or not ?(Qi89)How to disable multiple threads which are spawned by fork...join。

仕兰微面试题目电子类说明:1、笔试共分两部分:第一部分为基础篇(必答题);第二部分为专业篇(选答题)。

2、应聘芯片设计岗位的同学请以书面形式回答问题并附简历参加应聘面试。

3、如不能参加现场招聘的同学,请将简历和答卷邮寄或发e-mail的形式(请注明应聘标题)给我们,以便我们对您作出客观、全面的评价。

第一部分:基础篇(该部分共有试题8题,为必答题,每位应聘者按自己对问题的理解去回答,尽可能多回答你所知道的内容。

若不清楚就写不清楚)。

1、我们公司的产品是集成电路,请描述一下你对集成电路的认识,列举一些与集成电路相关的内容(如讲清楚模拟、数字、双极型、CMOS、MCU、RISC、CISC、DSP、ASIC、FPGA等的概念)。

2、你认为你从事研发工作有哪些特点?3、基尔霍夫定理的内容是什么?4、描述你对集成电路设计流程的认识5、描述你对集成电路工艺的认识。

6、你知道的集成电路设计的表达方式有哪几种?7、描述一个交通信号灯的设计。

8、我们将研发人员分为若干研究方向,对协议和算法理解(主要应用在网络通信、图象语音压缩方面)、电子系统方案的研究、用MCU、DSP编程实现电路功能、用ASIC设计技术设计电路(包括MCU、DSP 本身)、电路功能模块设计(包括模拟电路和数字电路)、集成电路后端设计(主要是指综合及自动布局布线技术)、集成电路设计与工艺接口的研究。

你希望从事哪方面的研究?(可以选择多个方向。

另外,已经从事过相关研发的人员可以详细描述你的研发经历)。

第二部分:专业篇(根据你选择的方向回答以下你认为相关的专业篇的问题。

一般情况)下你只需要回答五道题以上,但请尽可能多回答你所知道的,以便我们了解你的知识结构及技术特点。

1、请谈谈对一个系统设计的总体思路。

针对这个思路,你觉得应该具备哪些方面的知识?2、现有一用户需要一种集成电路产品,要求该产品能够实现如下功能:y=lnx,其中,x为4位二进制整数输入信号。

SystemVerilog断言语法指的是在SystemVerilog中使用断言进行验证和调试设计的语法规则。

断言是一种在设计过程中用来描述期望行为或者不期望行为的一种语言工具,通过断言可以对设计进行形式验证,帮助设计人员及时发现设计缺陷,提高设计的可靠性和稳定性。

在SystemVerilog中,断言语法的使用对于提高设计的质量和可维护性非常重要。

一、assert语句在SystemVerilog中,使用assert语句来定义断言。

assert语句是一种在设计中用来描述预期行为或不期望行为的语句。

它采用布尔表达式来描述期望的行为,如果这个布尔表达式为真,则断言通过,如果为假,则会触发一个错误。

assert语句的基本语法如下:assert(property_expression) else $error ("message");其中,property_expression是一个布尔表达式,用来描述预期的行为;message是在断言失败时会打印的错误信息。

二、sequence语句在SystemVerilog中,还可以使用sequence语句来定义一系列时序逻辑,并通过assert语句使用这些时序逻辑来进行断言验证。

sequence语句的基本语法如下:sequence sequence_name;statement1;statement2;...endsequence其中,sequence_name为时序逻辑的名称,statement1、statement2等为时序逻辑的具体内容。

三、property语句property语句用于定义属性,描述一系列信号之间的关系。

它可以用来描述一些复杂的时序逻辑,例如时序关系、状态机转移等。

property语句的基本语法如下:property property_name;(expression1 |-> expression2);endproperty其中,property_name为属性的名称,expression1和expression2为属性的具体描述。

Verilog 常见必备面试题1、Use verilog hdl to implement a flip-flop with synchronous RESET and SET, a Flip-flop with asynchronous RESET and SET. always@(posedge clk or negedge reset or posedge set)beginif(set)Q<>else if(!reset)Q<>elseQ<>endalways@(posedge clk) beginif(set)Q<>else if(!reset)Q<>elseQ<>end异步reset 和set 同步reset 和set2、Use verilog hdl to implement a latch with asynchronous RESET and SET.always @(clk or reset or set)beginif(set)Q=1;else if(!reset)Q=0;elseQ=D;end3、Use Verilog hdl to implement a 2-to-1multiplexer.assign Y=(SEL==1'b0)?A:B;4、Use AND gate, OR gate and Inverter toimplement a 2-to-1 multiplexer.module MUX21(A, B, SEL, Y);input A,B,SEL;output Y;net SEL_NOT, A_AND, B_AND;not u0(SEL_NOT, SEL);and u1(A_AND, SEL_NOT, A);and u2(B_AND, SEL, B);or u3(Y, A_AND, B_AND);endmodule5、Use a 2-to-1 multiplexer to implement a two input OR gate.module or2(A, B, Y);input A, B;output Y;MUX21 u0(Y, A, B, B );endmodulemodule MUX21(Y, A ,B, SEL)input A,B,SEL;output Y;assign Y=(SEL==1’b0):A:B;endmoduleassign Y=A?A:B;6、Use a tri-state buffer to implement Open-Drain buffer.assign Y=EN?DataIn:1'bz;7、To divide one input clock by3, Written by verilog hdl.module clk_div_3(clk, reset, clk_out);input reset,clk;output clk_out;reg clk_out;reg [1:0] cnt;always@(posedge clk or negedge reset)beginif(!reset)begin cnt<>clk_out<>else if(cnt==2'b01) begin clk_out<>cnt<=cnt+1'b1;>=cnt+1'b1;>else if(cnt==2'b10) begin clk_out<>cnt<>else cnt<>endendmodule,占空比1/38、To divide one input clock by3, 50% dutycycle is required. Written by verilog hdl.module clk_div_3(clk, reset, clk_out);input reset,clk;output clk_out;reg clk_out1, clk_out2;reg [1:0] cnt1,cnt2;assign clk_out = clk_out1 | clk_out2;always@(posedge clk or negedge reset) beginif(!reset)begin cnt1<>clk_out1<>else if(cnt1==2'b01) begin clk_out1<> cnt1<=cnt1+1'b1;>=cnt1+1'b1;>else if(cnt1==2'b10) begin clk_out1<> cnt1<>else cnt1<>endalways@(negedge clk or negedge reset) beginif(!reset)begin cnt2<>clk_out2<>else if(cnt2==2'b01) begin clk_out2<> cnt2<=cnt2+1'b1;>=cnt2+1'b1;>else if(cnt2==2'b10) begin clk_out2<> cnt2<>else cnt2<>endendmodulemodule clk_div_3(clk, reset, clk_out); input reset,clk;output clk_out;reg [1:0] cnt;reg clk_out1, clk_out2;always@(posedge clk)beginif(!reset)cnt<>else if(cnt=='d2)cnt<>elsecnt<>endalways @(posedge clk or negedge reset) beginif(!reset)clk_out1<>else if(cnt=='d2)clk_out1<>else if(cnt == 'd1)clk_out1<>endalways @(negedge clk or negedge reset) beginif(!reset)clk_out2<>else if(cnt=='d2)clk_out2<>else if(cnt == 'd1)clk_out2<>endassign clk_out = clk_out1 | clk_out2; endmodule(来源:EDN电子技术设计)。

system verilog中求位宽的函数-回复SystemVerilog中有很多用于位宽计算的函数和操作符,这些函数和操作符可以帮助我们在设计和验证中自动计算信号和数据类型的位宽。

本文将详细介绍一些常用的SystemVerilog位宽计算函数和操作符,希望能为读者提供一些帮助。

1. sizeof()函数SystemVerilog中的sizeof()函数可以用来计算信号或数据类型的位宽。

这个函数可以用于任何信号或数据类型,包括整型、浮点型、数组等。

sizeof()函数的语法如下:int sizeof(type_name);其中,type_name表示要计算位宽的信号或数据类型的名称或实例。

例如,对于一个16位的整型变量var,我们可以使用sizeof()函数来计算其位宽:int size_var;size_var = sizeof(var);2. bits()函数bits()函数是SystemVerilog的一个内置函数,可以用于计算信号、数据类型或表达式的位宽。

bits()函数的语法如下:int bits(data);其中,data表示要计算位宽的信号、数据类型或表达式。

与sizeof()函数不同,bits()函数在编译时进行位宽计算,并返回一个常量。

这一特性使得bits()函数非常适合在SystemVerilog代码中使用。

例如,对于一个16位的整型变量var,我们可以使用bits()函数来计算其位宽:int size_var;size_var = bits(var);3. `定义符SystemVerilog中的`定义符可以用于定义和访问常量值。

我们可以使用一个`定义符来定义信号或数据类型的位宽,并在其他地方使用它。

这种定义符通常用于编写可重配置的代码。

假设我们要定义一个16位的常量位宽:`define WIDTH 16然后,我们可以在代码的其他地方使用`WIDTH来引用这个位宽:int [ `WIDTH - 1 : 0 ] data;4. *操作符在SystemVerilog中,*操作符可以用于计算数据类型或信号的位宽。

Qi1)What is callback(Qi2)What is factory pattern(Qi3)Explain the difference between data types logic and reg and wire .(Qi4)What is the need of clocking blocks(Qi5)What are the ways to avoid race condition between testbench and RTL using SystemVerilog(Qi6)Explain Event regions in SV.(Qi7)What are the types of coverages available in SV(Qi8)What is OOPS(Qi9)What is inheritance and polymorphism(Qi10)What is the need of virtual interfaces(Qi11)Explain about the virtual task and methods .(Qi12)What is the use of the abstract class(Qi13)What is the difference between mailbox and queue(Qi14)What data structure you used to build scoreboard(Qi15)What are the advantages of linkedlist over the queue(Qi16)How parallel case and full cases problems are avoided in SV(Qi17)What is the difference between pure function and cordinary function(Qi18)What is the difference between $random and $urandom(Qi19)What is scope randomization(Qi20)List the predefined randomization methods.(Qi21)What is the dfference between always_combo and always@(*)c(Qi22)What is the use of packagess(Qi23)What is the use of $cast(Qi24)How to call the task which is defined in parent object into derived class (Qi25)What is the difference between rand and randc(Qi26)What is $root(Qi27)What is $unit(Qi28)What are bi-directional constraints(Qi29)What is solve...before constraint(Qi30)Without using randomize method or rand,generate an array of unique values (Qi31)Explain about pass by ref and pass by value(Qi32)What is the difference betweenbit[7:0] sig_1;byte sig_2;(Qi33)What is the difference between program block and module(Qi34)What is final block(Qi35)How to implement always block logic in program block(Qi36)What is the difference between fork/joins, fork/join_none fork/join_any (Qi37)What is the use of modports(Qi38)Write a clock generator without using always block.(Qi39)What is forward referencing and how to avoid this problem(Qi40)What is circular dependency and how to avoid this problem(Qi41)What is cross coverage(Qi42)Describe the difference between Code Coverage and Functional Coverage Which is more important and Why we need them(Qi43)How to kill a process in fork/join(Qi44)Difference between Associative array and Dynamic array(Qi45)Difference b/wProcedural and Concarent Assertions(Qi46)What are the advantages of SystemVerilog DPI(Qi47)how to randomize dynamic arrays of objects(Qi48)What is randsequence and what is its use(Qi49)What is bin(Qi50)Initialwait_order(a,b,c);Which from below initial process will cause that above wait order will pass.a)ig initial begin #1;->a;->b;->c;endb)initial begin#1;->a;endalways @a->b; always@b-> c;c)initial begin#1;->a;#0 ->b;->>c;endd)initial begin#1 ->a;#1 ->b;#1 ->c;end(Qi51)Why always block is not allowed in program block(Qi52)Which is best to use to model transaction Struct or class(Qi53)How SV is more random stable then Verilog(Qi54)Difference between assert and expect statements(Qi55)How to add a new processs with out disturbing the random number generator state (Qi56)What is the need of alias in SV(Qi57)What would be the output of the following code and how to avoid itfor(int i=0; i<N;i++)beginforkint j = i;begin#10 $display(" value is 0",j);endjoin_noneendalways N,By using automatic Key word, This problem can be avoided .fori(int i=0; i<N;i++)beginforkautomatic int j =i;begin#10 $display(" value is 0",j);endjoin_noneend(Qi58)Is it possible for functions to return a array( memory)(Qi59) How to check weather randomization is ssuccessful or not(Qi60)Do we need to call () when extending a class What happens if we don't call(Qi61)Equivalent construct to |-> 1Ans:=>(Qi62)What is the need to implement explicitly a copy() method inside a transaction , when we can simple assign one object to other(Qi63)How different is the implementation of a struct can union in SV.(Qi64)What is "this"(Qi65)What is tagged union(Qi66)What is "scope resolution operator"(Qi67)What is the difference between Verilog Parameterized Macros and SystemVerilog Parameterized Macros(Qi68)What is the difference betweenlogic data_1;var logic data_2;wire logic data_3j;bit data_4;var bit data_5;(Qi69)What is the difference between bits and logic(Qi70)Write a Statemechine in SV styles.(Qi71)What is the difference between $rose and posedgec(Qi72)What is advantage of program block over clockcblock race condition(Qi73)How to avoid the race condition between programblock(Qi74)What is the difference between assumes and assert(Qi75)What is coverage driven verification(Qi76)What is layered architecture(Qi77)What are the simulation phases in your verification environment(Qi78)How to pick a element which is in queue from random index(Qi79)What data structure is used to store data in your environment and why(Qi80)What is casting Explain about the various types of casting available in SV.(Qi81)How to importuall the items declared inside a package(Qi82)Explain how the timescale unit and precision are taken when a module does not have any timescalerdeclaration in RTL(Qi83)What is streaming operator and what is its use(Qi84)What are void functions(Qi85)How to make sure that a function argument passed has ref is not changed by the function(Qi86)What is the use of "extern"(Qi87)What is the difference between initial block and final block Ans:You can't schedule an event or have delays in final block.(Qi88)How to check weather a handles is holding object or not(Qi89)How to disable multiple threads which are spawned by fork...join。