ADC入门 基础知识资料讲解

- 格式:ppt

- 大小:975.00 KB

- 文档页数:34

adc 基本概念、逻辑概念和物理概念ADC是模拟数字转换器(Analog to Digital Converter)的英文简称,它是一种将模拟信号转换为数字信号的设备或模块。

ADC在现代电子系统中起着非常重要的作用,它可以将来自传感器、麦克风、摄像头等模拟信号转换为数字信号,以便数字处理器进行处理和分析。

在本文中,我们将从基本概念、逻辑概念和物理概念三个方面来探讨ADC的工作原理和应用。

首先,我们来看一下ADC的基本概念。

ADC的基本原理是根据一定的采样频率对模拟信号进行采样,并将采样值按照一定的编码规则转换为数字信号。

其中,采样频率表示每秒钟采集模拟信号的次数,而编码规则则决定了数字信号的精度和范围。

通常来说,ADC的输出是一个n位的二进制数,其取值范围为0到2的n次方减1。

因此,ADC的精度可以通过比特数来表示,比如8位ADC的输出精度为256个离散值。

其次,我们来谈一下ADC的逻辑概念。

在数字系统中,ADC通常作为一个独立的模块,负责将模拟信号转换为数字信号。

它可以通过串行接口(如SPI、I2C)或并行接口(如并行总线)与其他数字器件进行通信。

在实际应用中,ADC的转换结果可以直接用于数字信号处理器(DSP)、微控制器(MCU)或FPGA进行进一步处理。

此外,为了提高系统的灵敏度和精度,可能还会使用ADC前置放大器、数字滤波器等辅助器件。

最后,我们来探讨ADC的物理概念。

ADC通常由模拟前端、数字处理器和接口电路等部分组成。

其中,模拟前端用于对模拟信号进行采样、滤波和放大,以保证转换的准确性和稳定性;数字处理器负责将模拟信号转换为数字信号,并进行存储、加工和输出;而接口电路用于与其他数字设备之间进行通信和数据传输。

此外,ADC的性能参数还包括转换速率、信噪比、非线性度等,这些参数直接影响了其在实际应用中的性能和稳定性。

综上所述,ADC作为一种重要的模拟数字转换设备,在现代电子系统中具有广泛的应用。

ADC采样的相关基础知识(网上摘录)1 MSPS - 模拟混合信号转换速率(Conversion Rate)是指完成一次从模拟转换到数字的AD转换所需的时间的倒数。

积分型AD的转换时间是毫秒级属低速AD,逐次比较型AD是微秒级属中速AD,全并行/串并行型AD可达到纳秒级。

采样时间则是另外一个概念,是指两次转换的间隔。

为了保证转换的正确完成,采样速率(Sample Rate)必须小于或等于转换速率。

因此有人习惯上将转换速率在数值上等同于采样速率也是可以接受的。

常用单位是ksps和Msps,表示每秒采样千/百万次(kilo / Million Samples per Second)。

1msps=1000 ksps2 kspskilo Samples per Second 表示每秒采样千次,是转化速率的单位。

所谓的转换速率(Conversion Rate)是指完成一次从模拟转换到数字的AD转换所需的时间的倒数。

积分型AD的转换时间是毫秒级属低速AD,逐次比较型AD是微秒级属中速AD,全并行/串并行型AD可达到纳秒级。

采样时间则是另外一个概念,是指两次转换的间隔。

为了保证转换的正确完成,采样速率(Sample Rate)必须小于或等于转换速率。

因此有人习惯上将转换速率在数值上等同于采样速率也是可以接受的。

常用单位是ksps和Msps,表示每秒采样千/百万次(kilo / Million Samples per Second)。

1msps=1000ksps3 数据采集中的采样率、缓冲区大小以及,每通道采样数之间的关系采样率,主要取决于你需要分析信号的带宽。

根据采样定理,采样率至少是带宽的两倍。

一般取2.56倍或者更高。

每通道采样数,指的是每次从通道读取的数据长度,其实是从通道的buffer里面读取的。

如果每次读得太少,而且读的间隔过长,那么buffer里面的数据就会堆积,最后导致buffer溢出。

所以buffer size应该大于数据读取间隔*采样率,否则一个间隔的数据就足以把buffer填满了,同时读取的长度也应该保证buffer不会溢出。

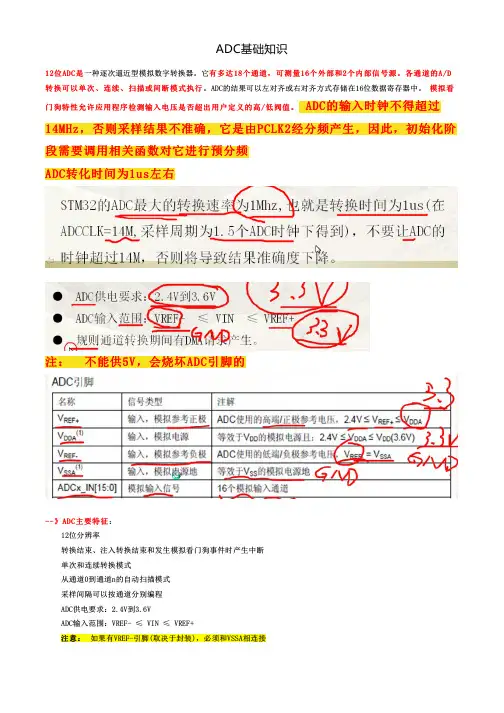

ADC基础知识

12位ADC是一种逐次逼近型模拟数字转换器。

它有多达18个通道,可测量16个外部和2个内部信号源。

各通道的A/D 转换可以单次、连续、扫描或间断模式执行。

ADC的结果可以左对齐或右对齐方式存储在16位数据寄存器中。

模拟看门狗特性允许应用程序检测输入电压是否超出用户定义的高/低阀值。

ADC的输入时钟不得超过14MHz,否则采样结果不准确,它是由PCLK2经分频产生,因此,初始化阶段需要调用相关函数对它进行预分频

ADC转化时间为1us左右

注: 不能供5V,会烧坏ADC引脚的

--》ADC主要特征:

12位分辨率

转换结束、注入转换结束和发生模拟看门狗事件时产生中断

单次和连续转换模式

从通道0到通道n的自动扫描模式

采样间隔可以按通道分别编程

ADC供电要求:2.4V到3.6V

ADC输入范围:VREF- ≤ VIN ≤ VREF+

注意: 如果有VREF-引脚(取决于封装),必须和VSSA相连接

注意:

注: 单次转换只转换一次就停止了

不可能同时使用自动注入和间断模式

下面是: 慢速交叉模式。

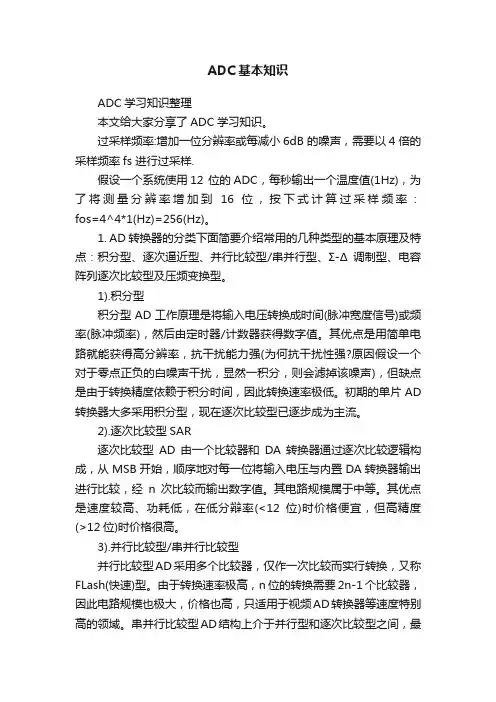

ADC基本知识ADC学习知识整理本文给大家分享了ADC学习知识。

过采样频率:增加一位分辨率或每减小6dB 的噪声,需要以4 倍的采样频率fs 进行过采样.假设一个系统使用12 位的ADC,每秒输出一个温度值(1Hz),为了将测量分辨率增加到16 位,按下式计算过采样频率:fos=4^4*1(Hz)=256(Hz)。

1. AD转换器的分类下面简要介绍常用的几种类型的基本原理及特点:积分型、逐次逼近型、并行比较型/串并行型、Σ-Δ调制型、电容阵列逐次比较型及压频变换型。

1).积分型积分型AD工作原理是将输入电压转换成时间(脉冲宽度信号)或频率(脉冲频率),然后由定时器/计数器获得数字值。

其优点是用简单电路就能获得高分辨率,抗干扰能力强(为何抗干扰性强?原因假设一个对于零点正负的白噪声干扰,显然一积分,则会滤掉该噪声),但缺点是由于转换精度依赖于积分时间,因此转换速率极低。

初期的单片AD 转换器大多采用积分型,现在逐次比较型已逐步成为主流。

2).逐次比较型SAR逐次比较型AD由一个比较器和DA转换器通过逐次比较逻辑构成,从MSB开始,顺序地对每一位将输入电压与内置DA转换器输出进行比较,经n次比较而输出数字值。

其电路规模属于中等。

其优点是速度较高、功耗低,在低分辩率(<12位)时价格便宜,但高精度(>12位)时价格很高。

3).并行比较型/串并行比较型并行比较型AD采用多个比较器,仅作一次比较而实行转换,又称FLash(快速)型。

由于转换速率极高,n位的转换需要2n-1个比较器,因此电路规模也极大,价格也高,只适用于视频AD转换器等速度特别高的领域。

串并行比较型AD结构上介于并行型和逐次比较型之间,最典型的是由2个n/2位的并行型AD转换器配合DA转换器组成,用两次比较实行转换,所以称为Half flash(半快速)型。

还有分成三步或多步实现AD转换的叫做分级(Multistep/Subrangling)型AD,而从转换时序角度又可称为流水线(Pipelined)型AD,现代的分级型AD中还加入了对多次转换结果作数字运算而修正特性等功能。

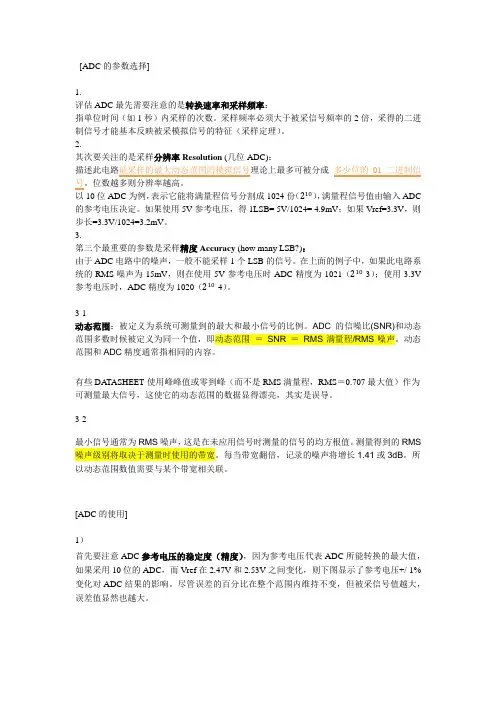

[ADC的参数选择]1.评估ADC最先需要注意的是转换速率和采样频率:指单位时间(如1秒)内采样的次数。

采样频率必须大于被采信号频率的2倍,采得的二进制信号才能基本反映被采模拟信号的特征(采样定理)。

2.其次要关注的是采样分辨率Resolution (几位ADC):描述此电路能采样的最大动态范围的模拟信号理论上最多可被分成多少位的01二进制信号。

位数越多则分辨率越高。

以10位ADC为例,表示它能将满量程信号分割成1024份(210),满量程信号值由输入ADC 的参考电压决定。

如果使用5V参考电压,得1LSB= 5V/1024= 4.9mV;如果Vref=3.3V,则步长=3.3V/1024=3.2mV。

3.第三个最重要的参数是采样精度Accuracy (how many LSB?):由于ADC电路中的噪声,一般不能采样1个LSB的信号。

在上面的例子中,如果此电路系统的RMS噪声为15mV,则在使用5V参考电压时ADC精度为1021(210-3);使用3.3V 参考电压时,ADC精度为1020(210-4)。

3-1动态范围:被定义为系统可测量到的最大和最小信号的比例。

ADC的信噪比(SNR)和动态范围多数时候被定义为同一个值,即动态范围=SNR =RMS满量程/RMS噪声。

动态范围和ADC精度通常指相同的内容。

有些DATASHEET使用峰峰值或零到峰(而不是RMS满量程,RMS=0.707最大值)作为可测量最大信号,这使它的动态范围的数据显得漂亮,其实是误导。

3-2最小信号通常为RMS噪声,这是在未应用信号时测量的信号的均方根值。

测量得到的RMS 噪声级别将取决于测量时使用的带宽。

每当带宽翻倍,记录的噪声将增长1.41或3dB。

所以动态范围数值需要与某个带宽相关联。

[ADC的使用]1)首先要注意ADC参考电压的稳定度(精度),因为参考电压代表ADC所能转换的最大值,如果采用10位的ADC,而Vref在2.47V和2.53V之间变化,则下图显示了参考电压+/-1%变化对ADC结果的影响。

STM32】ADC的基本原理、寄存器(超基础、详细版)ADC的基本介绍ADC的基本定义Analog-to-Digital Converter的缩写。

指模/数转换器或者模拟/数字转换器。

是指将连续变量的模拟信号转换为离散的数字信号的器件。

典型的模拟数字转换器将模拟信号转换为表示一定比例电压值的数字信号。

ADC的主要特征•12位逐次逼近型的模拟数字转换器;•最多带3个ADC控制器,可以单独使用,也可以使用双重模式提高采样率;•最多支持23个通道,可最多测量21个外部和2个内部信号源;•支持单次和连续转换模式;•转换结束,注入转换结束,和发生模拟看门狗事件时产生中断;•通道0到通道n的自动扫描模式;•自动校准;•采样间隔可以按通道编程;•规则通道和注入通道均有外部触发选项;•转换结果支持左对齐或右对齐方式存储在16位数据寄存器;•ADC转换时间:最大转换速率1us(最大转换速度为1MHz,在ADCCLK=14M,采样周期为1.5个ADC时钟下得到);•ADC供电要求:2.4V-3.6V;•ADC输入范围:VREF- ≤ VIN ≤ VREF+。

STM32F10x系列芯片ADC通道和引脚对应关系由上图中可以看出,STM32F103ZET6带3个ADC控制器,一共支持23个通道,包括21个外部和2个内部信号源;但是每个ADC控制器最多只可以有18个通道,包括16个外部和2个内部信号源。

ADC的基本原理ADC的工作框图ADC模块的框图看起来比较复杂,接下来会一点一点地对它进行分析。

ADC引脚在框图中最左边的一列是ADC的各个引脚,它们的名称、信号类型和作用见下图:一般情况下,VDD是3.3V,VSS接地,相对应的,VDDA是3.3V,VSSA也接地,模拟输入信号不要超过VDD(3.3V)。

ADC时钟配置框图中标注的来自ADC预分频器的ADCCLK是ADC模块的时钟来源。

通常,由时钟控制器提供的ADCCLK时钟和PCLK2(APB2时钟)同步。

∑∆模数转换器概述过采样∑∆ADC 的基本结构包括抗混迭滤波器、调制器及降采样低通滤波器,如图3.1所示。

抗混迭滤波器将输入信号限制在一定的带宽之内,对于过采样ADC ,由于输入信号带宽0f 远小于采样频率sf 的一半,抗混迭滤波的通带到阻带之间的过渡带(2s f f -)较宽,缓解了其设计要求,可用低阶模拟滤波器实现。

调制器将过采样信号转化为高速、低精度的数字信号。

然后降采样滤波器将其转变为Nyquist 频率的高精度信号。

调制器可以抑制过采样率ADC 电路引入的噪声,非线性等误差,这样缓解了它对模拟电路的精度要求。

另外,对于开关电容电路实现的过采样ADC ,无需采用采样保持电路。

图3.1 ∑∆过采样ADC 的结构图本章首先介绍了∑∆ADC 的一些主要性能指标、调制器的工作原理、基本结构,然后介绍了调制器的非理想因素与误差来源,最后介绍了未深入研究的问题与宽带∑∆ADC 研究现状。

3.1 ∑∆ADC 的一些主要性能指标∑∆ADC 的主要性能指标为:动态范围(DR)、信噪比(SNR)、信噪失真比(SNDR)、有效位数(ENOB)以及过载度(OL)。

如图3.2所示,图中横轴为输入信号的归一化值,即/in refV V ,纵轴为SNR 或SNDR ,二者均用dB 表示。

从图3.2中可以看出,当输入信号幅度较小时,SNR 和SNDR 大小是相等的;随着输入幅度的增加,失真将会降低调制器的性能,因而在输入幅度较大时,SNDR 会比SNR 小一些。

图3.2显示了非理想调制器的性能比理想调制器的性能差一些:一方面是由于实际调制器的有限增益引起性能成呈线性下降;另一方面是由于实际调制器过载而造成的性能下降。

图3.2 典型的∑∆转换器的性能图调制器各相主要性能指标[60]介绍如下:1.信噪比(SNR):是指在一定的输入幅度时,转换器输出信号能量与噪声能量的比值。

转换器能获得的最大信噪比为峰值信噪比(PSNR)。