以太网控制器芯片的设计及实现.

- 格式:doc

- 大小:27.50 KB

- 文档页数:3

以太网设计FAQ:以太网MAC和PHY问:如何实现单片以太网微控制器?答:诀窍是将微控制器、以太网媒体接入控制器(MAC)和物理接口收发器(PHY)整合进同一芯片,这样能去掉许多外接元器件。

这种方案可使MAC和PHY实现很好的匹配,同时还可减小引脚数、缩小芯片面积。

单片以太网微控制器还降低了功耗,特别是在采用掉电模式的情况下。

问:以太网MAC是什么?答:MAC就是媒体接入控制器。

以太网MAC由IEEE-802.3以太网标准定义。

它实现了一个数据链路层。

最新的MA C同时支持10Mbps和100Mbps两种速率。

通常情况下,它实现MII接口。

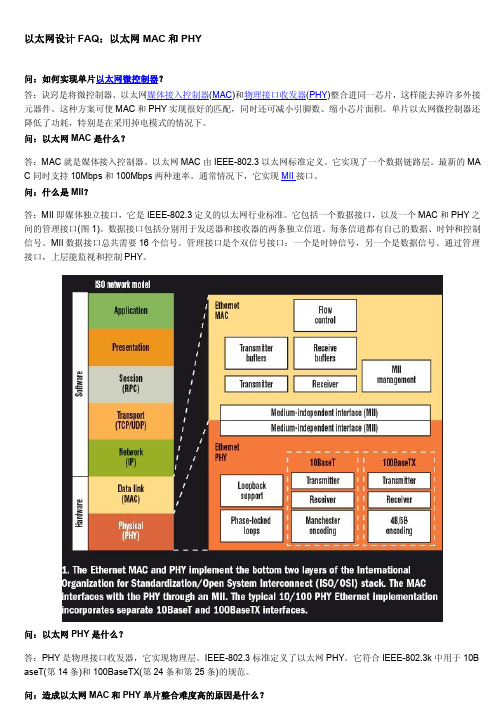

问:什么是MII?答:MII即媒体独立接口,它是IEEE-802.3定义的以太网行业标准。

它包括一个数据接口,以及一个MAC和PHY之间的管理接口(图1)。

数据接口包括分别用于发送器和接收器的两条独立信道。

每条信道都有自己的数据、时钟和控制信号。

MII数据接口总共需要16个信号。

管理接口是个双信号接口:一个是时钟信号,另一个是数据信号。

通过管理接口,上层能监视和控制PHY。

问:以太网PHY是什么?答:PHY是物理接口收发器,它实现物理层。

IEEE-802.3标准定义了以太网PHY。

它符合IEEE-802.3k中用于10B aseT(第14条)和100BaseTX(第24条和第25条)的规范。

问:造成以太网MAC和PHY单片整合难度高的原因是什么?答:PHY整合了大量模拟硬件,而MAC是典型的全数字器件。

芯片面积及模拟/数字混合架构是为什么先将MAC集成进微控制器而将PHY留在片外的原因。

更灵活、密度更高的芯片技术已经可以实现MAC和PHY的单芯片整合。

问:除RJ-45接口外,还需要其它元件吗?答:需要其它元件。

虽然PHY提供绝大多数模拟支持,但在一个典型实现中,仍需外接6、7只分立元件及一个局域网绝缘模块。

绝缘模块一般采用一个1:1的变压器。

这些部件的主要功能是为了保护PHY免遭由于电气失误而引起的损坏。

dm9051硬件设计方法DM9051是一款具有高度集成性的、低功耗的以太网控制器芯片。

它广泛应用于各种嵌入式系统中,包括智能家居、工业控制、智能仪器仪表等。

本文将介绍DM9051的硬件设计方法,以帮助开发人员更好地应用这款芯片。

DM9051芯片的硬件设计主要包括电源设计、时钟设计、接口设计以及外围电路设计等方面。

1.电源设计:DM9051的电源设计需要满足芯片的工作电压和电流需求。

一般来说,DM9051的工作电压为3.3V,电流在100mA左右。

在设计电源时,需要选择合适的电源芯片和滤波电容,以满足芯片工作的可靠性和稳定性。

2.时钟设计:DM9051芯片需要外部提供时钟信号,用于同步其内部的数据传输和处理。

时钟信号可以选择使用外部晶振或者外部时钟源提供。

在选择时钟源时,应考虑到时钟信号的精度、稳定性和抗干扰性等因素。

3.接口设计:DM9051芯片提供了丰富的接口,包括以太网接口、SPI接口、中断接口等。

在接口设计时,需要根据实际应用需求确定接口类型和引脚分配,并考虑信号线的布局和阻抗匹配等问题。

4.外围电路设计:DM9051芯片的外围电路设计主要涉及PHY芯片、RJ-45接口、磁鼓等。

PHY芯片负责将芯片内部的数据转换成与以太网标准兼容的信号,RJ-45接口用于连接以太网电缆,而磁鼓则用于滤除电磁干扰。

在设计外围电路时,需要合理布局各个电路模块,以减少干扰和提高系统的抗干扰性。

此外,DM9051芯片还有一些特殊的硬件设计需求,如电源管理、时钟信号的同步和检测等。

在进行这些特殊设计时,需要根据DM9051的应用手册和数据手册进行详细的了解和分析,并结合实际需求进行设计和调试。

总之,DM9051的硬件设计方法需要考虑多个方面的因素,包括电源设计、时钟设计、接口设计以及外围电路设计等。

在进行设计时,应充分了解芯片的功能和特性,并进行合理的方案选择和布局,以确保系统的可靠性和稳定性。

以太网控制器设计方案以太网控制器是计算机网络中常用的一种网络适配器。

在计算机与网络之间起着桥梁的作用,提供物理层和数据链路层的功能。

以太网控制器设计方案需要考虑到多个方面,如适配器的速度、功能、可靠性等,同时也需要考虑到成本和实际应用。

下面我们将从几个方面介绍一种以太网控制器设计方案。

一、硬件设计:以太网控制器主要由网卡芯片、网卡电路板、光电整流器、集线器等组成。

在硬件设计上,需要考虑到适配器的速度,目前以太网适配器的速率有10Mbps、100Mbps和1Gbps等不同规格。

此外,还需要考虑到适配器的实际应用,如需要在恶劣环境下使用的,需要考虑防水、防尘、防雷等设计。

同时,在适配器距离远离主机的情况下,还需要添加信号放大器或者中继器。

二、软件设计:软件设计主要包括适配器的驱动程序和控制程序。

驱动程序负责将数据从主机传输到适配器,并将适配器接收到的数据传输回主机。

控制程序则负责适配器的操作,如初始化、发送、接收、错误处理等。

在软件设计上,需要考虑到适应不同操作系统的要求。

同时,需要考虑到对于高速数据传输的处理和优化。

三、接口设计:适配器的接口设计非常重要,它决定了适配器与主机之间的通信速度和可靠性。

在接口设计上,需要考虑到信号传输的速率、时序、可靠性和稳定性等。

此外,还需要考虑到接口类型的选择,如PCI、POT、USB等不同的接口类型。

四、错误处理:适配器的错误处理是设计中不可忽视的一个方面。

在适配器操作过程中,可能会出现各种错误,如传输错误、接收错误、缓存错误等。

为了确保网络的正常运行,需要对这些错误进行及时、有效的处理。

在设计中,需要考虑到错误处理的机制和处理过程的优化。

五、成本控制:在以太网控制器设计方案中,成本控制是不可忽视的一个方面。

适配器的成本不仅取决于硬件和软件成本,还取决于适配器的生产和使用成本。

在设计中,需要考虑到成本的可控性,努力达到成本和性能的平衡。

综上所述,以太网控制器设计方案需要从硬件、软件、接口、错误处理、成本等方面考虑。

以太网控制器设计方案在当今数字化的时代,以太网作为一种广泛应用的网络技术,其控制器的设计至关重要。

以太网控制器是实现以太网通信的核心组件,它负责处理数据的发送和接收,以及与上层软件和硬件的交互。

接下来,让我们深入探讨一种以太网控制器的设计方案。

一、设计需求分析在开始设计以太网控制器之前,我们需要明确其功能需求和性能指标。

首先,它应支持常见的以太网协议标准,如 IEEE 8023 ,能够在不同的网络环境中稳定工作。

其次,要具备高速的数据传输能力,以满足现代应用对带宽的要求。

此外,还应具备低功耗、小尺寸、高可靠性等特点,以适应各种嵌入式系统和移动设备的需求。

在接口方面,以太网控制器需要与主机系统(如 CPU )进行有效的通信。

常见的接口包括 PCIe 、 USB 等。

同时,它还应提供多个以太网端口,以支持多设备连接和网络扩展。

二、硬件架构设计以太网控制器的硬件架构主要包括以下几个部分:1、物理层接口( PHY )PHY 负责将数字信号转换为模拟信号,通过以太网电缆进行传输,并将接收到的模拟信号转换回数字信号。

它与以太网介质直接连接,实现物理层的通信功能。

2、媒体访问控制层( MAC )MAC 是以太网控制器的核心部分,负责数据帧的封装和解封装、地址识别、冲突检测与避免等功能。

它遵循以太网协议标准,对数据进行处理和控制。

3、数据缓冲区用于存储发送和接收的数据,以提高数据传输的效率和稳定性。

缓冲区的大小和管理策略会直接影响控制器的性能。

4、控制逻辑单元负责协调各个模块的工作,处理中断信号,与主机系统进行通信等。

5、时钟管理单元提供稳定的时钟信号,确保各个模块的同步工作。

为了实现高性能和低功耗,硬件架构的设计需要采用先进的集成电路工艺和优化的电路设计技术。

例如,使用低功耗的晶体管、动态电压频率调整( DVFS )技术等。

三、软件驱动设计软件驱动是以太网控制器与上层操作系统和应用程序之间的桥梁。

它主要包括以下功能:1、设备初始化在系统启动时,对以太网控制器进行初始化设置,包括配置工作模式、设置 MAC 地址、分配缓冲区等。

基于FPGA的以太网MAC控制器的设计与实现丁世勇;谭文文;李桂英【摘要】The design of Ehernet MAC controller based on FPGA is described. The controller realizes the CSMA/CD (Carrier Sense MultipleAccess/Collision Detection)protocol in half duplex mode and the transmitting and receiving of Pause frame in full duplex mode, and it can access the register in the physical chip. The whole design is described in a way of top-down design flow with Verilog hardware description language. We simulated the design with Modelsim and verified it with FPGA board. The test result shows that the design can satisfy the requirement of 802.3 standard.%介绍了基于FPGA的以太网MAC控制器的设计,主要实现了半双工模式下CSMA/CD协议、全双工模式下Pause帧的收发,以及对物理层芯片中寄存器的读写访问。

设计采用Verilog硬件描述语,按照自顶向下的设计流程描述了以太网的主要功能模块,该控制器通过Modelsim进行了仿真并进行了FPGA板级验证,验证其能够满足802.3标准的要求。

【期刊名称】《电子设计工程》【年(卷),期】2011(019)021【总页数】4页(P163-165,169)【关键词】以太网;FPGA;Verilog;HDL;Modelsim;MAC控制器【作者】丁世勇;谭文文;李桂英【作者单位】山东科技大学信息与电气工程学院,山东青岛266510;山东科技大学信息与电气工程学院,山东青岛266510;山东科技大学理学院,山东青岛266510【正文语种】中文【中图分类】TN492随着网络的飞速发展,因特网(Internet)在人们的生活中占据着越来越重要的地位。

图1 GMII接口信号图2 以太网控制器的结构设计框图6774ELECTRONIC ENGINEERING & PRODUCT WORLD2018.6指示接口、MAC层和物理层的控制和状态信息接口(MDIO)。

具体的信号说明如表1所示。

2 设计方案X i l i n x提供的千兆以太网开发套件为Vi rt e x-5 ML505/ML506开发板,该开发板支持10/100 M、1/10 G以太网,是学习和研发高速连接设备的理想平台。

Xilinx提供了可参数化的10/1 Gbps以太网物理层控制据送出去。

接收数据则与之相反2.1 电路架构该以太网控制器主要进行层协议的接口以及MAC计,总体结构框图如图据的产生模块、发送模块层编解码模块、接收及校验模块分。

发送模块和接收模块主要提供图3 CRC8编码的串行实现图4 GMII的传输格式图5 MAC控制器中的状态转移图3 电路实现与仿真3.1 MAC发送端-数据成帧号,与主机接口从外部存储单元获取的发送数据按照标准协议进行封装,空闲时发送给PHY 层转换发送到网络中去在物理层部分BASE-X PCS/PMA IP CORE 核支持内部或外部链接。

IP 核内的主要组成部分为为物理层的媒介层,图6 接收端数据提取时序图图7 电路的仿真波形图信号I/O 描述TX_ER O 发送器错误信号TX_EN O 发送器使能信号GTX_CLK O 吉比特发送信号的时钟(125 M )TXD O 被发送的数据RX_ER I 接收数据出错指示RX_DV I 接收数据有效指示RXD I 接收数据RX_CLK I 接收时钟信号CRS I 载体感应,仅用于半双工COL I 冲突检测,仅用于半双工表1 CMII接口信号描述[2]王春华.Xilinx可编程逻辑器件设计与开发(基础篇).[M]北京:人民邮电出版社,2011.[5]王长清.基于FPGA的千兆以太网通信板卡的设计与实现[D].河南:河南师范学报,2011.[1]Jeff Watson,Gustavo Castro.高温电子设备对设计和可靠性带来挑战[J].模拟对话,2012,4.[2]Jeff Watson,Maithil Pachchigar.面向高温应用的低功耗数据采集解决方案[J].模拟对话,2015,8.[3]CN-0365:面向高温环境的16位、600 kSPS、低功耗数据采集系统,ADI公司,2015,6.[4]Alan Walsh.面向精密SAR模数转换器的前端放大器和RC滤波器设计[J]模拟对话,2012,12.[5]John L. Evans,James R.Thompson,Mark Christopher,etc.不断变化的汽车环境:高温电子设备。

《面向ZYNQ嵌入式平台的EtherCAT通信协议栈设计与实现》一、引言随着工业自动化和智能制造的快速发展,EtherCAT (Ethernet for Control Automation Technology)通信协议以其高速、实时、高效率的特性,在嵌入式系统领域得到了广泛应用。

ZYNQ嵌入式平台作为一款高性能、低功耗的SoC(System on a Chip)芯片,为EtherCAT通信协议的实现提供了理想的硬件基础。

本文将详细介绍面向ZYNQ嵌入式平台的EtherCAT通信协议栈的设计与实现。

二、EtherCAT通信协议概述EtherCAT是一种基于以太网的实时通信协议,主要用于工业自动化控制领域。

它通过优化数据传输和同步机制,实现了高速、实时、高效率的通信。

EtherCAT协议栈包括物理层、数据链路层、网络层和应用层等多个层次,其中物理层和数据链路层由硬件实现,应用层则由软件实现。

三、ZYNQ嵌入式平台简介ZYNQ嵌入式平台是一款基于Xilinx FPGA和ARM Cortex-A9处理器的SoC芯片,具有高性能、低功耗、可扩展等优点。

其硬件架构包括可编程逻辑(FPGA)和处理器系统(PS),为EtherCAT通信协议的实现提供了良好的硬件基础。

四、EtherCAT通信协议栈设计在ZYNQ嵌入式平台上实现EtherCAT通信协议栈,需要从硬件和软件两个方面进行设计。

1. 硬件设计:(1)选择合适的以太网控制器芯片,与ZYNQ嵌入式平台的处理器系统(PS)进行连接,实现物理层和数据链路层的通信。

(2)设计可编程逻辑(FPGA)电路,实现EtherCAT协议的编码和解码功能。

2. 软件设计:(1)设计应用层软件,实现EtherCAT协议的报文处理、数据传输和同步等功能。

(2)设计驱动程序,与硬件进行交互,实现数据的收发和通信功能的控制。

五、EtherCAT通信协议栈实现在实现EtherCAT通信协议栈时,需要遵循以下步骤:1. 配置以太网控制器芯片的参数,如IP地址、子网掩码等,建立与ZYNQ嵌入式平台的连接。

以太网控制器芯片的设计及实现

网络控制器芯片的功能与设计实现

IEEE 802.3协议是针对以太网CSMA/CD标准的传输介质物理层(PHY)和介质访问控制协议(MAC、Media Access Control)来定义的。

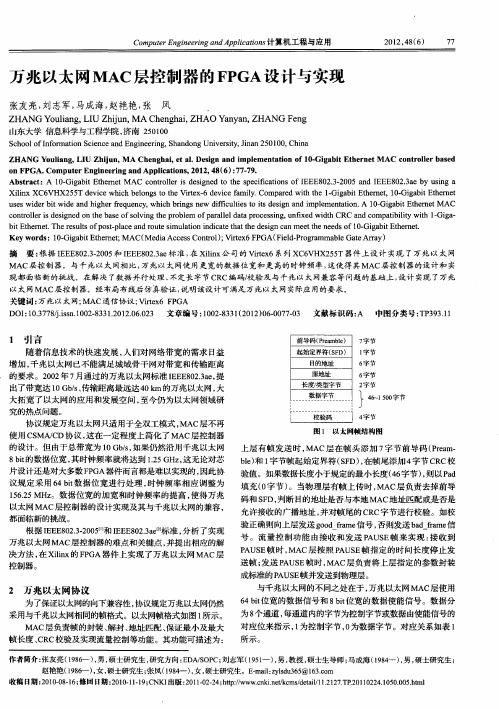

芯片由PHY、发送模块、接收模块、FIFO、控制模块组成,其中控制模块包括寄存器堆、DMA (Direct Memory Access)模块、流量控制模块、接收缓冲区和发送缓冲区组成。

网络控制器芯片的功能框图如图1所示。

图1 以太网控制器芯片的功能框图

1 IEEE 802.3以太网MAC数据帧结构

在发送数据时,发送模块自动在待传数据前加上7字节的前导码和1字节的帧起始定界符,紧随的是6字节的目的地址和6字节的源地址,然后长度/类型为2字节,接着是数据区,然后是46~1500字节的数据。

若发送时,数据长度小于最短长度46字节,发送模块自动填补,以达到最小长度,最后是4个字节的循环冗余校验码。

2 发送模块

发送模块的作用就是按照CSMA/CD协议发送数据包。

发送模块状态机控制协调各个发送子模块的时序,发送模块状态机如图2所示。

图2 发送模块状态转换图

S_defer状态表示网络忙,若网络空闲了,经过最小的帧间隙时间,进入网络空闲状态S_idle。

若需要发送数据包,经过S_pre,S_data,S_pad,S_crc等状态发送,在这当中若检测到冲突信号,就进入S_jam状态。

在S_jam状态判断是local collision还是late collision,若是local collision就进入

S_back状态,按照退避算法重发当前数据帧,否则直接进入网络忙状态,放弃该帧的发送。

3 接收模块

接收模块的任务就是接收数据帧。

物理接口收发器PHY将收到的网络数据变成二进制数据送给接收模块,接收模块再把正确的数据经过接收FIFO和DMA的控制送给接收缓冲区。

接收模块的功能还包括移除接收到帧的前导码/帧分隔符;比较目的地址,判断是否丢弃当前数据帧;对接收到的数据包做CRC校验,判断传输过程中数据是否出错。

接收模块状态机是接收模块的核心,控制协调接收模块的各个子模块的工作与时序。

接收模块状态机如图3所示。

图3 接收模块状态转换图

复位后,状态机进入S_idle状态,若数据是无效的,就停留在S_idle状态,否则进入S_pre状态。

S_pre状态和S_sdf状态的作用就是去掉前导码和帧间隔符。

当帧间隔符全部检测到,进入S_data状态,在S_data状态使用字节计数器,记录所收到数据的字节个数,用于比较目的地址。

若目的地址匹配则将接收到的数据写入到接收FIFO,否则丢弃该帧,不写入到FIFO。

字节计数器的作用还有判断接收到的数据包是否超过帧的最大长度。

若在S_pre状态、S_sdf 状态或S_data状态出现数据有效信号无效的情况,都进入到S_drop状态。

图4 核心模块的功能仿真

4 控制模块

控制模块包含DMA(direct memory access)模块、流量控制模块、缓冲区模块、寄存器堆模块和总线接口模块。

DMA模块的功能是将接收FIFO的数据搬运到接收缓冲区,以及发送缓冲区的数据搬运到发送FIFO。

流量控制模块端口阻塞的情况下丢帧,这种方法是当接收缓冲区开始溢出时,通过将阻塞信号发送回源地址实现的。

流量控制可以有效地防止由于网络中瞬间的大量数据对网络带来的冲击,保证用户网络高效而稳定地运行。

两种控制流量的方式:(1)在半双工方式下,流量控制是通过反向压力(backpressure),即我们通常说的背压计数实现的,这种计数是通过向发送源发送jamming信号使得信息源降低发送速度。

(2)在全双工方式下,流量控制一般遵循IEEE 802.3X标准,是由交换机向信息源发送“pause”帧令其暂停发送。

缓冲区模块由一块32KB的SRAM组成,分为接收缓冲区和发送缓冲区,接收缓冲区和发送缓冲区的大小可以由用户编程决定。

缓冲区以分页的方式来管理,256B为一页。

主机通过总线接口与芯片交换数据,通过读写寄存器堆来控制芯片的工作。

设计验证

本文给出核心功能的验证过程。

把这些核心功能模块连接成一个环路(发送模块直接与接收模块相连接),发送模块按照802.3协议发出数据包,接收模块按照802.3协议处理这些数据包,符合要求的数据包送到(接收缓冲区),这些模块在Mentor公司的ModelsimSe5.8里面功能仿真波形如图5所示。

图5 芯片的实现流程

图中,clk为系统时钟;rst为复位信号;tx_req为发送FIFO请求信号,让DMA从发送缓冲区搬运数据到发送FIFO;tx_fifo_data_out是从发送FIFO里面出来的8数据,发送模块封装这些数据,发送给PHY;这里没有对PHY进行验证,把发送模块发出的数据TXD和数据使能TXEN直接与接收模块数据端和数据有效信号分别相连接;接收模块把TXD进行串并转换,得到8为rx_data;byte_cnt为接收到rx_data的个数。

功能仿真通过之后,把核心模块连接成一个整体(SRAM直接调用Quartus II 的IP Core),通过Quartus II综合以后,下载到FPGA开发板里面。

用FPGA 模拟网络控制器芯片,与计算机进行通信。

FPGA与PC通过RJ-45相连。

应用软件发一数据包给FPGA,接收模块接收到数据包后,通过DMA将数据从FIFO 搬运到接收缓冲区。

一包数据接收完成后,通过附加逻辑,让FPGA发送出刚刚接收到的数据包,附加逻辑还完成了把接收到的数据按位取反的功能。

应用软件显示PC收到的数据包,通过比较PC发给FPGA的数据包和FPGA发送给PC的数据包,验证了核心模块的功能正确(FPGA的附加逻辑将接收到的数据包进行了按位取反操作)。

芯片实现

设计验证通过以后,经过图5所示的流程,得到整个芯片的版图。

本次流片采用华虹NEC 0.35μm CMOS工艺,芯片面积为5640μm×5480μm (不计划片槽和缓冲区),芯片有100个管脚。

芯片的右上部分是实现MAC层的数字区,左下区域是华虹NEC提供的IP Core--32KB的SRAM,用作缓冲区,右下区域完成PHY功能,周围是管脚。