可编程串行通信接口芯片8251A

- 格式:ppt

- 大小:3.35 MB

- 文档页数:19

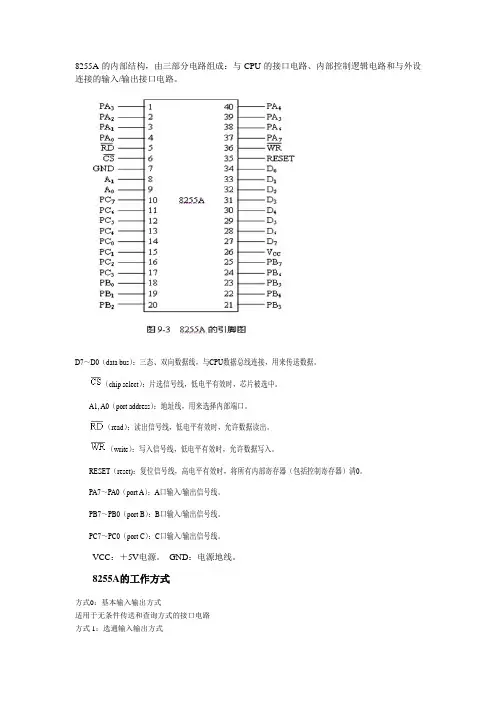

8255A的内部结构,由三部分电路组成:与CPU的接口电路、内部控制逻辑电路和与外设连接的输入/输出接口电路。

D7~D0(data bus):三态、双向数据线,与CPU数据总线连接,用来传送数据。

(chip select):片选信号线,低电平有效时,芯片被选中。

A1, A0(port address):地址线,用来选择内部端口。

(read):读出信号线,低电平有效时,允许数据读出。

(write):写入信号线,低电平有效时,允许数据写入。

RESET(reset):复位信号线,高电平有效时,将所有内部寄存器(包括控制寄存器)清0。

PA7~PA0(port A):A口输入/输出信号线。

PB7~PB0(port B):B口输入/输出信号线。

PC7~PC0(port C):C口输入/输出信号线。

VCC:+5V电源。

GND:电源地线。

8255A的工作方式方式0:基本输入输出方式适用于无条件传送和查询方式的接口电路方式1:选通输入输出方式适用于查询和中断方式的接口电路方式2:双向选通传送方式适用于与双向传送数据的外设适用于查询和中断方式的接口电路8255A初始化编程8255A的A,B,C三个端口的工作方式是在初始化编程时,通过向8255A的控制端口写入控制字来设定的。

8255A由编程写入的控制字有两个:方式控制字和置位/复位控制字。

方式控制字用于设置端口A, B, C的工作方式和数据传送方向;置位/复位控制字用于设置C口的PC7~PC0中某一条口线PC i(i=0~7)的电平。

两个控制字公用一个端口地址,由控制字的最高位作为区分这两个控制字的标志位。

(1)方式控制字的格式8255A工作方式控制字的格式如图7.11所示。

D0:设置PC3~PC0的数据传送方向。

D0=1为输入;D0=0为输出。

D1:设置B口的数据传送方向。

D1=1为输入;D1=0为输出.D2:设置B口的工作方式。

D2=1为方式1;D2=0为方式0。

可编程串行通信接口芯片8251A可编程串行通信接口芯片8251A2010-05-25 15:058251 A是一个通用串行输入/输出接口,可用来将86系列CPU以同步或异步方式与外部设备进行串行通信。

它能将主机以并行方式输入的8位数据变换成逐位输出的串行信号;也能将串行输入数据变换成并行数据传送给处理机。

由于由接口芯片硬件完成串行通信的基本过程,从而大大减轻了CPU的负担,被广泛应用于长距离通信系统及计算机网络。

8251A是一个功能很强的全双工可编程串行通信接口,具有独立的双缓冲结构的接收和发送器,通过编程可以选择同步方式或者异步方式。

在同步方式下,既可以设定为内同步方式也可以设定为外同步方式,并可以在内同步方式时自动插入一个到两个同步字符。

传送字符的数据位可以定义为5~8位,波特率0~64K可选择。

在异步方式下,可以自动产生起始和停止位,并可以编程选择传送字符为5~8位之间的数据位以及1、1/2位之中的停止位,波特率0~19.2K可选择。

同步和异步方式都具有对奇偶错、覆盖错以及帧错误的检测能力。

一、8251A内部结构及功能图8.5.1为8251A结构框图。

作为常用的通信接口,和8255A类似,8251A 的结构也可以归纳为以下三个部分:第一部分是和CPU或者总线的接口部分,其中包括数据总线缓冲器、读/写控制逻辑。

数据总线缓冲器用来把8251A和系统数据总线相连,在CPU执行输入/输出指令期间,由数据总线缓冲器发送和接收数据,此外,控制字,命令字和状态信息也通过数据总线缓冲器传输,读/写控制逻辑电路用来配合数据总线缓冲器工作。

CPU通过数据总线缓冲器和读写控制逻辑向8251A写入工作方式和控制命令字,对芯片初始化;向8251A写入要发送字符的数据代码,送到发送缓冲器进行并行到串行的转换,并且将接收的、已转换成并行代码的接收缓冲器中的字符数据读入CPU。

第二部分是数据格式转换部分,包括发送缓冲器、并行数据到串行数据转换的发送移位器,接收缓冲器和串行数据到并行数据转换的接收移位器,以及发送控制电路和接收控制电路。

可编程通信接口8251A(USART)1.8251A的基本结构8251A的基本结构包括5个功能模块(1)数据总线缓冲器——用于暂存接收,发送数据,CPU发来的命令及8251的工作状态。

(2)读/写控制逻辑——接收来自CPU控制总线的控制信号,控制数据的传送方向。

(3)接收器——从接收数据线RXD上接收串行数据,按指定方式将其转换成并行数据。

(4)发送器——接收CPU送来的并行数据,按指定方式将其转换成串行数据通过发送数据线TXD发送出去。

(5)调制解调器控制电路——提供4个通用的控制信号,即(数据终端准备好),(数据设备准备好),(请求发送)和(准许发送),以备8251A与外设联络。

2.8251A的工作过程(1)8251A发送数据的过程①当发送缓冲器为空时,信号TXRDY有效(或状态字的D0=1),以示发送器准备好,等待CPU送入数据。

②CPU将要发送的数据写入8251A的发送缓冲器;③发送的数据进行“并→串”转换;④插入起始位、奇/偶位和停止位或同步字符等,数据一位一位从TXD端串行输出。

(2)8251A接收数据的过程①在RXD端检测到起始位或同步字符;②开始在RXD线上采集数据;③将接收到的数据“串→并”转换,并进行奇偶校验和检查错误;④将采样到的、经过变换的8位数据由接收缓冲器送入数据总线缓冲器;⑤信号RXRDY有效(或状态字的D1=1),以示8251A已接收到一个数据,待CPU读取。

3.8251A的初始化在如前面已经强调过的,在使用可编程接口之前必须进行初始化,即在使用8251A进行数据传输前,对其进行编程,将相关方式指令字、命令指令字写入8251A。

8251A初始化的具体步骤如图7-3所示。

图7-3 8251A 初始化流程图4. CPU 对8251A 的操作和控制8251A 有两个端口地址,偶地址为输入/输出数据端口地址,奇地址为控制/状态端口地址。

引脚线C/与A 0连接:A 0=0,访问输入/输出数据端口A 0=1,访问控制/状态端口控制信号:、、C/、合成对8251A 的操作如表7-1所示。

8251a有几个端口地址_对8251a进行初始化及流程

8251a内部结构框图8251A是一种可编程的通用同步/异步接收发送器,通常作为串行通信接口使用,被广泛应用Intel80X86为CPU的微型计算机中。

8251a有几个端口地址8251a有两个连续的端口地址,数据输入端口和数据输出端口合用同一个偶地址,而状态端口和控制端口合用同一个奇地址。

8251A初始化编程流程及程序例:8251A工作于异步方式,方式选择控制字为11111011B,工作命令控制字为00010001B。

其初始化程序为:

…

MOV AL,0FBH ;8251A方式选择字

OUT CONTR,AL

MOV AL,11H ;8251A操作命令字

OUT CONTR,AL

…

8251A的应用举例例:微机系统中两台微机之间进行双机串行通信的硬件连接和软件编程。

(1)要求

在甲乙两台微机之间进行串行通信,甲机发送,乙机接收。

要求把甲机上开发的应用程序(其长度为2DH)传送到乙机中去。

双方采用起止式异步方式,通信的数据格式为,字符长度为8位,2位停止位,波特率因子为64,无校验,波特率为4800。

CPU与8251A之间用查询方式交换数据,8251A的端口地址分配是:309H为命令/状态口,308H为数据口。

(2)分析

由于是近距离传输,因此可以不设MODEM,两台微机之间直接通过RS-232标准接口连接即可。

同时是采用查询I/O方式,故收/发程序中只需检查发/收准备好的状态是否置位,即可收发l个字节。

8251a有何特点?在串行通信中作用_8251a的工作方式

8251A的内部结构(1)接收器接收器包括接收缓冲器和接收控制逻辑两部分。

接收器的功能是接收在RXD引脚上的串行数据,并按规定的格式把它转换成并行数据,存放在数据总线缓冲器中。

①接收缓冲器

接收缓冲器主要由移位寄存器和数码寄存器组成。

接收器接收传送到RXD(接收数据输入端)引脚上的串行数据,并对串行数据流的特殊位(奇偶位,停止位等)和字符(同步字符)进行检查、处理,按规定的格式将串行数据转换为并行数据存放在缓冲器中。

接收移位寄存器和接收数据缓冲器组成了双缓冲器结构。

②接收控制逻辑

这一部分控制串行数据的接收,包括三条控制线:

RXRDY(Receiver Ready)接收器准备好,输出,高电平有效。

RXC(Receiver Clock)接收时钟,输入。

SYNDET/BRKDET(SYNchronous DETect/BreaK DETect)同步检测/断点检测,输出/输入,高电平有效。

(2)发送器发送器包括发送缓冲器和发送控制逻辑两部分。

①发送缓冲器和发送过程

发送数据缓冲器接收由CPU送来的并行数据,按初始化编程指定的数据格式转换成串行数据流送至发送移位寄存器,在TXC的下降沿从TXD引脚发送出去。

发送数据缓冲器和发送移位寄存器组成了发送的双缓冲器结构。

②发送控制逻辑

该部分控制串行数据的发送操作,包括3条控制线:

TXRDY(Transmitter ReaDy)发送器准备好,输出,高电平有效。

TXE(Transmitter Empty)发送器空,输出,高电平有效。

第七章终结篇——8251A的总结总算把这个第七章复习完了,我把剩下⼀点关于8251A的发上来吧本来在讲解8251A书本上还有关于RS232和串⼝通信的讲解,但是太浅了,就不放了,有兴趣的朋友可以⾃⾏参考其他⽂章串⾏通信芯⽚8251A有以下特点1. 可以⽤于同步或者异步传输,同步0-64kbps,异步0-19.2kpbs2. 同步传送的时候,5-8位/字符,可以⽤于内同步或者外同步,可⾃动插⼊同步字符3. 异步传送的时候,5-8位/字符,有1,2,1.5个停⽌位4. 完全双⼯,双缓冲发送和接受数据5. 具有出错检查,奇偶校验、溢出、和帧错误等检测电路好吧,为啥要这个8251A因为计算机内部都是并⾏传输数据的,但是长距离通信都是⽤的串⾏通信的(这些概念不太明⽩的不懂的朋友可以⾃⾏百度⼀下概念或者看看书)必须要个东西来转化⼀下82518251的内部结构内部结构包括接收器,发送器,读/写控制逻辑,数据总线缓冲器和调制解调控制电路五⼤部分接收器包括接收缓冲器,并⾏转换逻辑和接受控制电路三个部分接收缓冲器对外引脚为RxD,功能是从此引脚上接收串⾏数据,然后转换成并⾏数据,是由接受移位寄存器和接收数据缓冲器组成双缓冲结构接受控制电路是配合缓冲器⼯作的,作⽤如下1 .在异步⽅式下,芯⽚复位后,先检测输⼊信号中的有效1,⼀旦检测到到,就接着寻找有效的低电平来确定启动位2 消除假启动⼲扰3 对接收到的信息进⾏奇偶校验,并根据校验结果建⽴相应的状态位4 检测停⽌位,并按检测结构建⽴状态位发送器和接收器差不多,也是有发送缓冲器,发送控制电路和并串转换逻辑3个部分发送缓冲器上⾯接的是TxD脚,发送数据缓冲器和发送移位寄存器组成了发送的双缓冲结构,发送控制电路也是辅助发送缓冲器的,但是和接受的功能不⼀样发送控制电路作⽤如下1. 在异步⽅式下插⼊起始位,校验位和停⽌位2. 在同步⽅式下,插⼊同步字符,在数据中插⼊校验位数据总线缓冲器提供与8251A和CPU系统总线相连,在CPU执⾏输⼊输出操作的时候,进⾏数据交换或者读写命令读/写控制逻辑电路⽤来配合总线缓冲器⼯作1. 写信号WR#,把数据总线的信号(数据/控制字)写⼊8251A2. 读信号RD#,将状态/数据字发送到CPU(发到数据总线)3. 接收控制/数据信号C/D#,与读。

串行接口芯片8251A8251A基本功能⏹可用于同步和异步通信方式(通信方式通过对方式字编程实现):☐同步方式:波特率0-64Kbps,每个字符可为5~8位,可使用内部同步检测和外部同步检测,能自动插入同步字符。

☐异步方式:波特率0-19.2Kbps,每个字符可为5~8位,自动增加起始位、停止位和校验位。

时钟TxC,RxC的时钟频率为传输波特率的1,16和64倍。

⏹全双工,具有双缓冲器接收器和发送器;⏹出错检测,具有奇偶、溢出和帧错等检测电路。

8251A的内部结构8251A的内部结构主要包括:数据总线缓冲器、接收缓冲器、接收控制电路、发送缓冲器、发送控制电路、调制/解调控制电路、读/写控制逻辑电路等数据总线缓冲器发送缓冲器发送控制电路接收缓冲器接收控制电路D0~D7SYNDETRxDRxRDY读写控制电路C / DCLKRESETRDWRCSDSRCTSDTRRTSRxCTxCTxETxRDYTxD调制解调控制电路内部总线8251A的内部结构⏹发送器:包括发送缓冲器和发送控制电路☐采用异步方式时,则由发送控制电路自动在其首尾加上起始位、奇偶校验位和停止位,然后从起始位开始,经移位寄存器从数据输出线TxD逐位串行输出。

发送速率取决于TxC接收的发送时钟频率,可以编程定义是发送速率的1、16、64倍。

8251A的内部结构☐采用同步方式,则在发送数据之前,发送器将自动送出1个或2个同步字符,然后才逐位串行输出数据。

◆如果CPU与8251A之间采用中断方式交换信息,那么TxRDY可作为向CPU发出的中断请求信号,表示发送缓冲器已空,可以接收CPU下一个数据。

◆当发送器中的8位数据串行发送完毕时,由发送控制电路向CPU发出TxE有效信号,表示发送器中移位寄存器已空。

8251A的内部结构⏹接收器:包括接收缓冲器和接收控制电路从RxD引脚上接收串行数据转换成并行数据后存入接收缓冲器。

☐异步方式:在RxD线上检测低电平,将检测到的低电平作为起始位,8251A开始进行采样,完成字符装配,并进行奇偶校验和去掉停止位,变成了并行数据后,送到数据输入寄存器,同时发出RxRDY信号送CPU,表示已经收到一个可用的数据。

8251芯片8251芯片是一种通讯接口芯片,主要用于计算机之间或计算机与外设之间的数据传输。

该芯片通过串行和并行数据传输的方式,实现了计算机之间的数据传输和通信功能。

8251芯片提供了串行和并行两种模式的通信接口。

在串行模式下,数据以位的形式传输,适用于长距离传输和低速传输场景。

在并行模式下,数据以字节或字的形式传输,适用于短距离传输和高速传输场景。

8251芯片具有以下主要功能:1. 数据格式控制:8251芯片支持多种数据格式,包括异步串行传输、同步传输和标准格式传输等。

用户可以根据需要选择合适的数据传输格式。

2. 时钟控制:8251芯片提供了多个时钟源,可以根据需要选择不同的时钟源。

同时,芯片还支持外部时钟源的输入。

3. 数据传输控制:芯片可以根据指令进行数据传输的启动、停止和暂停等控制操作。

同时,芯片还支持自动重整、自动请求和自动调整等功能,可以提高数据传输的效率。

4. 错误检测:8251芯片提供了丰富的错误检测和纠错功能,包括奇偶校验、帧错误检测等。

可以有效减少数据传输过程中的错误和丢失。

5. 缓冲区管理:芯片内置了数据缓冲区,可以存储待传输的数据。

通过合理调整缓冲区大小和设置触发阈值,可以实现高效的数据传输。

8251芯片广泛应用于计算机和外设之间的数据传输和通信领域。

它可以与各种外设进行通信,包括打印机、调制解调器、终端设备等。

它不仅提供了稳定可靠的数据传输功能,还具备丰富的扩展接口,可实现更多的功能拓展。

总结来说,8251芯片是一种功能强大的通讯接口芯片,通过串行和并行的数据传输方式,实现了计算机之间或计算机与外设之间的数据传输和通信功能。

它具有多种数据格式控制、时钟控制、数据传输控制、错误检测和缓冲区管理等功能,广泛应用于计算机和外设之间的通信领域。