基于FPGA_DSP的高速基带信号处理平台的设计_谭左红

- 格式:pdf

- 大小:620.32 KB

- 文档页数:5

基于FPGA+DSP的高速数据采集系统设计

杨永东;曾庆立

【期刊名称】《吉首大学学报(自然科学版)》

【年(卷),期】2009(030)004

【摘要】介绍了1种基于FPGA和DSP的高速数据采集系统的设计和实现,其FPGA采用Altera公司ACEX 1K系列的EPIK50TC144_3器件,DSP芯片采用TI 公司TMs320系列的TMS320C6713器件.该系统将A/D采样的数据送往FP-GA,经过FPGA预处理后送到DSP,最终通过USB接口送到主控台,其系统的数据采集的实时速度最高可达到100 MB/s,适用于大部分的高速数据采集场合.

【总页数】4页(P65-68)

【作者】杨永东;曾庆立

【作者单位】吉首大学物理科学与信息工程学院,湖南,吉首,416000;吉首大学物理科学与信息工程学院,湖南,吉首,416000

【正文语种】中文

【中图分类】TP29

【相关文献】

1.基于FPGA+DSP的USB高速数据采集系统设计与实现 [J], 李冬冬;吴玉斌;郝永平;王磊

2.基于FPGA+DSP弹载SAR信号处理系统设计 [J], 陈勇

3.基于FPGA+DSP的高速视频实时处理系统设计 [J], 张小永

4.基于FPGA+DSP的弹载组合导航系统设计 [J], 李炳臻;李杰;胡陈君;张泽宇;纪

志敏

5.基于FPGA+DSP的高速视频实时处理系统设计 [J], 张小永

因版权原因,仅展示原文概要,查看原文内容请购买。

5.DSP技术的开发应用1325.7一种基于高性能DSP和FPGA的DRFM信号处理模块的设计与应用李云杰张庆兴高梅国北京理工大学信息科学技术学院电子工程系北京10009l摘要;本文介绍了一种基于高性能DSP和FP(:A的DRFRI信号处理模块的设计方案,时谊模块的总体设计方案、主要电路单元设计、通用性设计和信号完整性设计等内容做了详细讨论.最后列举了谊DRFM信号处理模块的具休应用.关键词:FPGADSPDRFM一、引言数字射频储存器(DRFM)是现代电子干扰机的关键部件,它能高保真的存储和复制信号加上移频、时延等调制,产生高逼真度的欺骗信号,实现对威胁目标的欺骗干扰[1】。

传统的数字储频系统是在中频或基带进行信号采集存储的,处理带宽和处理能力均有限.随着半导体技术的飞速发展,AI)C和DAC的转换速率和精度不断提高,DSP和FPGA的信号处理能力越来越强。

这些高性能集成电路Ic的出现为更高速的DRFM信号处理模块的研制提供了保障。

本文的主要内容即是一种基于高性能DSP和FPGA的DRFM信号处理模块的设计和应用。

二、DRFM信号处理模块的设计1.模块设计思路和总体框图选用CPCI总线标准,基于高性能的器件.尽量满足灵括性、通用性、可靠性及可扩展性是本DRFM信号处理模块设计的总体思路.其总体框图如图I所示。

2.主要电路单元的设计(1)ADC单元该部分电踌的核心芯片可选ATMEL公司的AT84AD001BSmartADC.该芯片的主要特点包括:①单片集成双同道.8bit分辨率:@每个通道采用率可达1GHz,双同道交织采集模式采用率可达2GHz;③数字输出可设置为1:1或者1:2分路输出;④数字输出为100f/端接的LVDS信号#⑤3线串行编程接口,可以对ADC芯片进行灵活设置.通过设置,ADC芯片的熹成双通道可以工作在正常摸式,或者交织模辛i分别可以实现取通道1GHz的转换·或者单通圈lDRFM信号处理模块的总体框圉道2GHz的转换.模拟输入信号由前级送入进行500端接匹配后,经过高频变压器TPIOI变换为差分形式送入ADC芯片,转换信号的最大带宽可达lGHz。

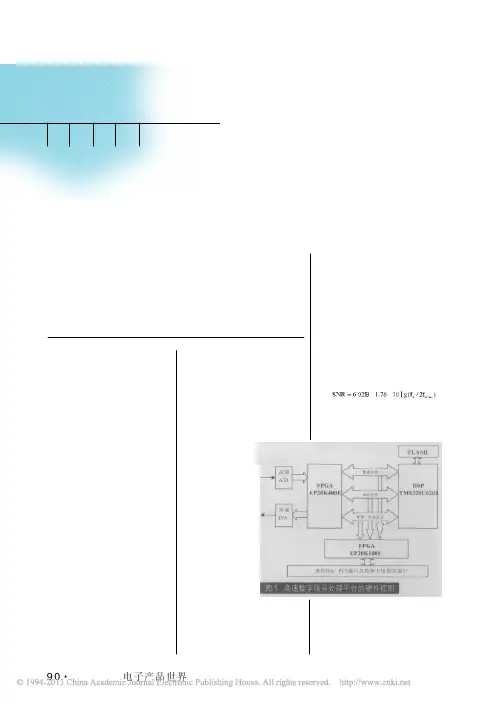

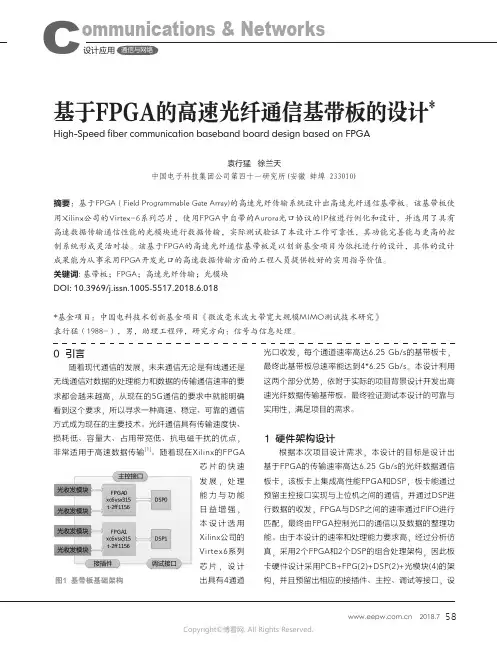

图1 基带板基础架构计的基础架构如图1所示,详细设计的架构如图2所示。

在板卡设计中选取的F P G A是X i l i n x公司的XC6VSX315T-2FF1156型号作为主控芯片用来控制光纤接口的主要功能,主要完成光收发模块的使能控制、光传输的链路管理以及数据的传输。

XC6VSX315T包含49200个Slices和25344 Block RAM,18个用户I/O,可以满足FPGA外围电路设计和后期扩展与增强功能的设计[2]。

设计中要求的光口传输速率是6.25 Gb/s,XC6VSX315T共有5组20个GTX数据收发接口,GTX通道的传输速率最快可达6.6 Gb/s,满足技术指标中的信号传输速率的要求[3]。

光收发模块选用标准的成熟光收发模块,该模块最高传输速度可达4*6.25 Gb/s。

整个板卡选用特定芯片完成主控与基带板之间的数据交互,从而来控制板卡的主要功能。

2 软件架构设计本次设计基于FPGA的高速光纤通信基带板卡时就块、数据控制与整理模块和Aurora 8B10B IP核的调用模块。

本次光口数据传输过程中使用的协议是Xilinx公司提供的一种免费的数据链路层协议——Aurora协议,该协议已经验证是稳定可靠的传输协议,已得到实际应用,该协议核内部封装了高速串行数据接口硬核,可编程逻辑器件通过绑定GTX通道进行数据的收发交互。

单个GTX通道的数据传输速率可达G bit级别,根据不同的需求可以实现多个通道的组合使用,从而可实现几十G bit,甚至上百G bit速率的数据传输。

因此,本次设计图2 基带板详细架构图3 FPGA功能实现代码lane又能实现数据的双工传输。

所以本设计中的Aurora 协议接口就在Xilinx公司的Virtex-6芯片上实现。

Aurora 8B/10B顶层模块例化了Aurora 8B/10B通道模块、TX和RX本地链路模块、全局逻辑模块以及GTP/GTX收发器。

结合FPGA与DSP实现对高速中频采样信号处理平台的设计详解现代社会正向数字化、信息化方向高速发展,在这一过程中,往往需要高速信号的实时性数字化处理。

例如,随着科技的进步,现代雷达等应用信号的数字化处理上有了长足的发展,但也带来了新的问题,这些应用的数字信号处理具有海量运行需求的应用背景,如巡航导弹末制导雷达地形匹配、合成孔径雷达的成像处理、相控阵雷达的时空二维滤波处理等领域。

目前,单片DSP难以胜任许多信号处理系统的要求。

而常见的解决方案也是高速A/D采样与信号处理功能是在多块不同的板卡上实现,这给实际应用带来很多不便。

鉴于上述现有技术所存在的问题,本设计平台的目的是:

(1)实现高速中频信号(如雷达信号)的数字化处理并进行实时传输数据或进行数据的实时计算,并能通过输出电路进行结果显示;

(2)自定义控制总线可以实现对高速中频信号处理板进行灵活控制,具有较强的可配置性和丰富的灵活性;

(3)高速A/D采样与D/A回放及数据处理单元集成在一块板上,在集成度高的同时也降低了高速信号在传输过程中出现差错的概率。

1 平台设计方案高速中频采样信号处理平台由主控制电路、高速A/D与D/A电路、信号处理单元电路、光纤通道电路、时钟管理电路、存储单元和外部接口电路组成,其总体框图如图1所示。

在实际应用过程中,四路A/D通道可以接收不同的信号源的信号,D/A通路可以对外进行数据显示等多种功能,时钟管理电路管理内外时钟的使用及对板上系统供给工作时钟,两路光纤通道可以与其他高速设备相连接,自定义总线可以与CPU或主控制器相连接对平台进行有效灵活的控制。

1.1 高速A/D与D/A设计

四路高速A/D采样通道采用两片NS公司的ADC081000实现,每片有两个A/D通道,。

基于DSP和FPGA的通用数字信号处理系统设计作者:孙靖舒来源:《电脑知识与技术》2020年第20期摘要:随着科学技术的不断发展,如今社会对于电子设备的结构与功能要求也在日益提升。

为此,该文将设计出一种体积小、能耗低的通用数字信号处理系统,并在系统中采用FPGA为系统的硬件加工,以DSP为数字处理核心,最终对其他硬件没备进行有效控制。

关键词:DSP;FPDA;通用数字信号处理;系统设计中图分类号:TP311文献标识码:A文章编号:1009-3044(2020)20-0221-02随着信息技术和电子技术的不断发展,如今数字信号处理已经被广泛地运用到各行各业中,并发挥出良好的应用效果。

但随着人们对于电子设备功能需求的日益增加,如今电子没备的结構也越来越复杂,其不仅极大地增加电子设备的体积和运行能耗,还有可能影响到没备的实际运行效果。

为此,本文将没计出一种能耗低,体积小的通用数字信号处理系统,以期能够为业内人士提供理论参考。

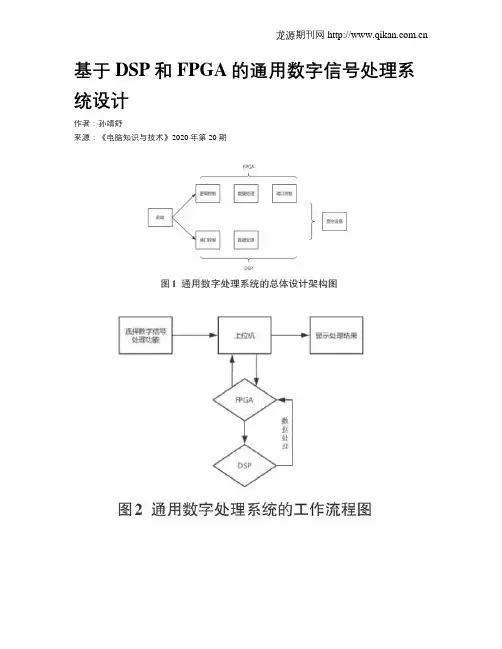

1系统总体设计本文所没计的基于DSP和FPGA的通用数字信号处理系统,其实际总体没计架构如图1所示。

整个系统有前端、FPGA、DSP以及显控设备四部分共同组成,其中前端设备在系统中用于数字模拟信号的输工作;FPGA则是用于控制ADC和DAC部分,其中ADC主要是对前端所输出的信号进行数据采集、滤波、变频、抽取、处理以及对系统外部端口电路进行实时逻辑控制,而DAC则是负责与DSP接口相互连接,然后通过输出基带信号来对DSP部分进行逻辑控制;DSP部分是本系统设计中数字核心处理部分,该部分是本系统没计中的核心部分主要负责通过核心算法对FPGA所传递出的模拟信号进行进一步的分析和处理,并在处理完成后,得到的数据传递给显控没备进行实际显示。

在实际运行过程中,本文所没计的通用数字处理系统的工作流程如图2所示。

操作者可以通过上位机的人机交互界面来选择实际数字信号处理功能,并通过USB接口来将上位机的控制命令传递给FPGA,之后FPGA又会将命令指令传递给DSP,DSP将会根据上位机所发布的指令来对数据进行实际处理,并在完成处理后,将经过处理的数据传回给FPGA,最终FP-GA 则又会通过USB接口将处理后的数据传递给上位机,再由上位机的显示程序和人机交互界面进行显示[1]。

(19)中华人民共和国国家知识产权局(12)发明专利申请(10)申请公布号 (43)申请公布日 (21)申请号 202010346578.8(22)申请日 2020.04.27(71)申请人 湖北三江航天红峰控制有限公司地址 432000 湖北省孝感市北京路特8号(72)发明人 潘玥 郑磊 潘静 (74)专利代理机构 武汉东喻专利代理事务所(普通合伙) 42224代理人 李佑宏(51)Int.Cl.G06F 8/654(2018.01)G06F 5/06(2006.01)(54)发明名称一种基于DSP+FPGA的程序在线升级方法及系统(57)摘要本发明公开了一种基于DSP+FPGA的程序在线升级方法及系统,其中上位机配套软件解析DSP在线升级固件信息,依据预设的通讯协议将在线升级数据和在线升级指令发送给FPGA,FPGA将在线升级数据和在线升级指令通过FIFO传输至DSP;DSP读取并解析FIFO的缓存数据,将解析后的在线升级数据缓存于可读写存储单元;DSP依据解析后的在线升级指令获取所述可读写存储单元的升级数据,以实现待升级硬件设备的在线升级操作,从而提高了程序运行速率,节省了DSP处理器资源,保障程序升级的正确率与可靠性。

权利要求书2页 说明书5页 附图1页CN 111506335 A 2020.08.07C N 111506335A1.一种基于DSP+FPGA的程序在线升级方法,其特征在于,该方法包括如下步骤:上位机获取DSP在线升级固件信息,并依据预设的通讯协议将在线升级数据和在线升级指令发送给FPGA,FPGA将在线升级数据和在线升级指令通过FIFO传输至DSP;DSP读取并解析FIFO的缓存数据,将解析后的在线升级数据缓存于可读写存储单元;所述DSP依据解析后的在线升级指令获取所述可读写存储单元的升级数据,载入非易失性存储单元以实现待升级硬件设备的在线升级操作。

2.根据权利要求1所述的一种基于DSP+FPGA的程序在线升级方法,其特征在于,所述DSP依据解析后的在线升级指令获取所述可读写存储单元的升级数据具体为:所述DSP将解析后的在线升级数据存储于可读写存储单元,DSP的用户程序依据解析后的在线升级指令调用程序升级功能静态库,以获取在线升级数据。

基于DSP/FPGA的超高速跳频系统基带设计跳频通信系统作为扩频通信体制中的一种重要类型,以其出色的抗远近效应、抗干扰能力,在军用、民用通信领域得到了广泛应用。

跳频通信方式是指载波受一伪随机码的控制, 不断地、随机地跳变,可看成载波按照一定规律变化的多频频移键控(MFSK)。

跳频通信的频率受伪随机码控制不断跳变,跳频图案可以设置几千乃至上万个,收发两端只要跳频图案一致,跳频时间同步,就可在信息传输过程中不断跳变空间频率信道,实现跳频通信。

近年来随着半导体工艺和计算机技术的发展,DSP(Digital Signal Processor)、FPGA(Field Programmable Gates Array)等现代信号处理芯片越来越成熟和普遍使用,以前只能理论研究的跳频技术有了实现的可能。

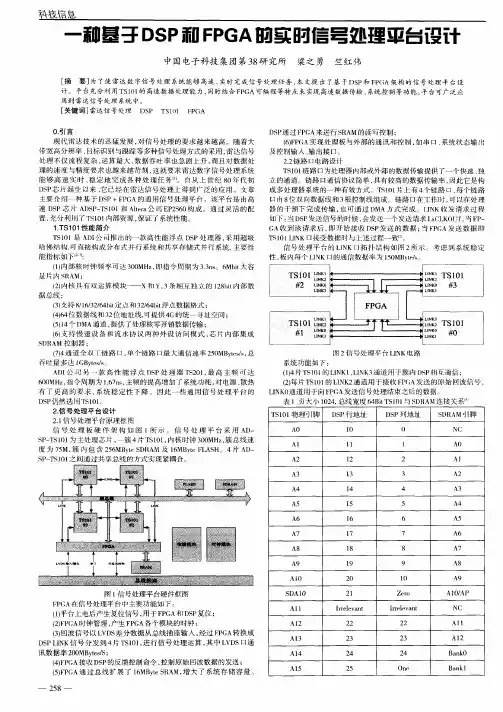

1 基于FPGA/DSP 的跳频系统硬件架构本跳频通信系统的发射系统如图1。

信源信息进入DSP 进行信道编码;随后DSP 根据编码结果使能FPGA 控制DDS 在中频段产生跳频信号;最后混频器把信号频率搬移到射频上,经过高频放大器放大后发射。

接收系统如图2。

天线将接收到的信号经过高频放大器放大后,与第一本振混频,产生第一中频信号;DDS 受DSP 控制,作为第二本振,与接收到的跳频信号按相同规律跳频(但频率相差一个中频),至此得到了固定中频,完成解跳;随后,对信号进行中频采样,在数字域中利用正交NCO(NCO 位于FPGA 中,受DSP 控制)实现数字解调;得到的结果在DSP 中进行信道解码,恢复原始信息,送到信宿。

可以看到本跳频系统中,FPGA 是硬件逻辑的载体,完成基带信号采样后的混频、滤波等操作及对DDS、ADC 等外部逻辑的控制;DSP 控制FPGA内部逻辑以及DDS、ADC 等逻辑单元完成跳频通信系统基带部分的发射与接。

基于DSP和FPGA的信号处理平台

王延昭

【期刊名称】《数字通信世界》

【年(卷),期】2008(000)005

【摘要】本文介绍了一种基于DSP和FPGA高速数字信号处理平台的实现方案,草点研究了试验平台的硬件实现结构,软件实现结构以及不同模式之间的切换,充分体现了软件无线电系统的灵活性,开放性和兼容性的特点.

【总页数】3页(P46-48)

【作者】王延昭

【作者单位】西安电子科技大学信息科学研究所

【正文语种】中文

【中图分类】TN91

【相关文献】

1.一种基于DSP和FPGA的实时信号处理平台设计 [J], 梁之勇;竺红伟

2.一种基于DSP+FPGA架构的InSAR实时信号处理平台设计 [J], 王光;索志勇

3.基于DSP+FPGA的高速通用实时信号处理平台设计 [J], 曹政才;赵应涛;王光国

4.基于FPGA+DSP的高速中频采样信号处理平台的实现 [J], 苏永芝;耿玉玲

5.基于FPGA+DSP的高速基带信号处理平台的设计 [J], 谭左红;田增山

因版权原因,仅展示原文概要,查看原文内容请购买。