多层PCB的Prepreg和core

- 格式:pdf

- 大小:110.30 KB

- 文档页数:3

PCB阻抗设计与阻抗设计软件Polar的使用 随着 PCB 信号切换速度不断增长,当今的 PCB 设计厂商需要理解和控制 PCB 迹线的阻抗。

相应于现代数字电路较短的信号传输时间和较高的时钟速率,PCB 迹线不再是简单的连接,而是传输线。

在实际情况中,需要在数字边际速度高于1ns 或模拟频率超过300Mhz时控制迹线阻抗。

PCB 迹线的关键参数之一是其特性阻抗(即波沿信号传输线路传送时电压与电流的比值)。

印制电路板上导线的特性阻抗是电路板设计的一个重要指标,特别是在高频电路的PCB设计中,必须考虑导线的特性阻抗和器件或信号所要求的特性阻抗是否一致,是否匹配。

这就涉及到两个概念:阻抗控制与阻抗匹配,本文重点讨论阻抗控制和叠层设计的问题。

阻抗控制阻抗控制(eImpedance Controling),线路板中的导体中会有各种信号的传递,为提高其传输速率而必须提高其频率,线路本身若因蚀刻,叠层厚度,导线宽度等不同因素,将会造成阻抗值得变化,使其信号失真。

故在高速线路板上的导体,其阻抗值应控制在某一范围之内,称为―阻抗控制‖。

PCB 迹线的阻抗将由其感应和电容性电感、电阻和电导系数确定。

影响PCB走线的阻抗的因素主要有: 铜线的宽度、铜线的厚度、介质的介电常数、介质的厚度、焊盘的厚度、地线的路径、走线周边的走线等。

PCB 阻抗的范围是 25 至120 欧姆。

在实际情况下,PCB 传输线路通常由一个导线迹线、一个或多个参考层和绝缘材质组成。

迹线和板层构成了控制阻抗。

PCB 将常常采用多层结构,并且控制阻抗也可以采用各种方式来构建。

但是,无论使用什么方式,阻抗值都将由其物理结构和绝缘材料的电子特性决定:●信号迹线的宽度和厚度●迹线两侧的内核或预填材质的高度●迹线和板层的配置●内核和预填材质的绝缘常数PCB传输线主要有两种形式:微带线(Microstrip)与带状线(Stripline)。

微带线(Microstrip):微带线是一根带状导线,指只有一边存在参考平面的传输线,顶部和侧边都曝置于空气中(也可上敷涂覆层),位于绝缘常数 Er 线路板的表面之上,以电源或接地层为参考。

叠层与阻抗(SI9000)的学习笔记一.材质知识,规格1.材料的分类1)铜箔:导电图形构成的基本材料2)芯板(CORE):线路板的骨架,双面敷铜的板子,即可用于内层制作的双面板。

3)半固化片(prepreg):芯板与芯板之间的粘合剂,同时起到绝缘的作用。

4)阻焊油墨:对板子起到阻焊、绝缘、防腐蚀等作用。

5)字符油墨:标示作用。

6)表面处理材料:包括铅锡合金、镍金合金、银、OSP等等。

2.名词说明带状线:走在内层(stripline/double stripline),埋在PCB内部的带状走线。

微带线:是走在表面层(microstrip),附在PCB表面的带状走线。

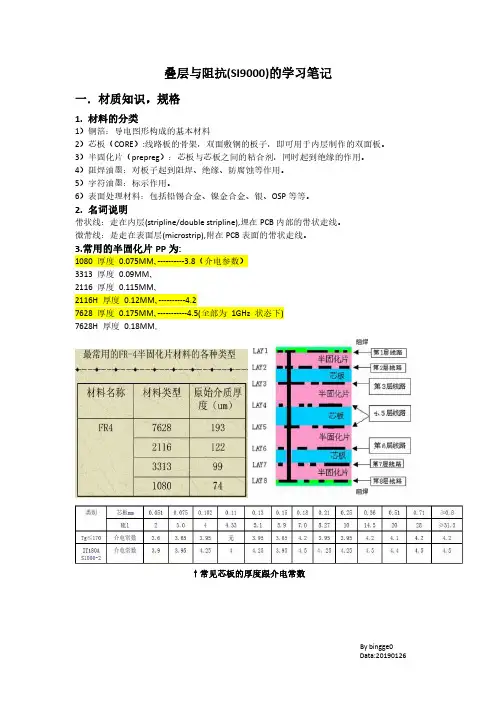

3.常用的半固化片PP为:1080厚度0.075MM、----------3.8(介电参数)3313厚度0.09MM、2116厚度0.115MM、2116H厚度0.12MM、----------4.27628厚度0.175MM、-----------4.5(全部为1GHz状态下)7628H厚度0.18MM。↑常见芯板的厚度跟介电常数↑常见半固化片类型厚度与介电常数标称基铜厚度(um)18(0.5oz)35(1oz)70(2oz)内层计算铜厚(mil)0.65 1.25 2.56外层计算铜厚(mil)2.2 2.9 4.2↑PCB板实际铜厚表格对照表3.特性阻抗的计算1)影响特性阻抗的因素有:介电常数、介质厚度、线宽、铜箔厚度。

一般,介质厚度、线距越大阻抗值越大;介电常数、铜厚、线宽、阻焊厚度越大阻抗值越小。

2)阻抗匹配在高频设计中是很重要的,阻抗匹配与否关系到信号的质量优劣。

而阻抗匹配的目的主要在于传输线上所有高频的微波信号皆能到达负载点,不会有信号反射回源点。

3)铜厚:一般的设计是:表面铜厚做0.5OZ+plating,内层做1OZ。

4介电常数不同板材其介电常数不一样,其与所用的树脂材料有关:FR4板材其介电常数为3.9—4.5,其会随使用的频率增加减小,聚四氟乙烯板材其介电常数为2.2—3.9间要获得高的信号传输要求高的阻抗值。

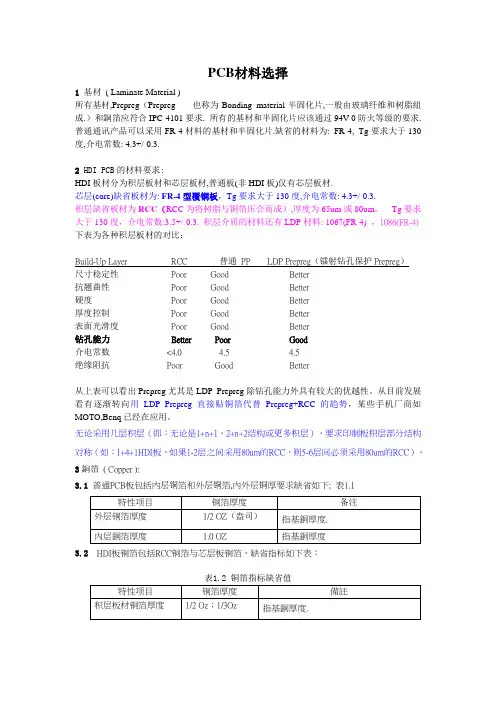

PCB材料选择1基材( Laminate Material )所有基材,Prepreg(Prepreg------也称为Bonding material半固化片,一般由玻璃纤维和树脂組成.)和銅箔应符合IPC-4101要求. 所有的基材和半固化片应该通过94V-0防火等级的要求.普通通讯产品可以采用FR-4材料的基材和半固化片.缺省的材料为: FR-4, Tg要求大于130度,介电常数: 4.3+/-0.3.2 HDI PCB的材料要求:HDI板材分为积层板材和芯层板材,普通板(非HDI板)仅有芯层板材.芯层(core)缺省板材为: FR-4型覆铜板,Tg要求大于130度,介电常数: 4.3+/-0.3.积层缺省板材为RCC(RCC为将树脂与铜箔压合而成),厚度为65um或80um,Tg要求大于130度,介电常数:3.5+/-0.3. 积层介质的材料还有LDP材料: 1067(FR-4),1086(FR-4)下表为各种积层板材的对比:Build-Up Layer RCC 普通PP LDP Prepreg(镭射钻孔保护Prepreg)尺寸稳定性Poor Good Better抗翘曲性Poor Good Better硬度Poor Good Better厚度控制Poor Good Better表面光滑度Poor Good Better钻孔能力Better Poor Good介电常数<4.0 4.5 4.5绝缘阻抗Poor Good Better从上表可以看出Prepreg尤其是LDP Prepreg除钻孔能力外具有较大的优越性。

从目前发展看有逐渐转向用LDP Prepreg直接贴铜箔代替Prepreg+RCC的趋势,某些手机厂商如MOTO,Benq已经在应用。

无论采用几层积层(即:无论是1+n+1、2+n+2结构或更多积层),要求印制板积层部分结构对称(如:1+4+1HDI板,如果1-2层之间采用80um的RCC,则5-6层间必须采用80um的RCC)。

PCB线路板阻抗计算公式现在关于PCB线路板的阻抗计算方式有很多种,相关的软件也能够直接帮您计算阻抗值,今天通过polar si9000来和大家说明下阻抗是怎么计算的。

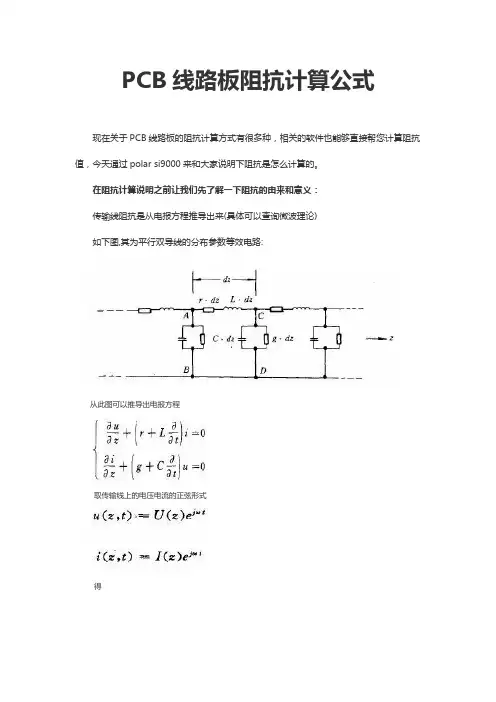

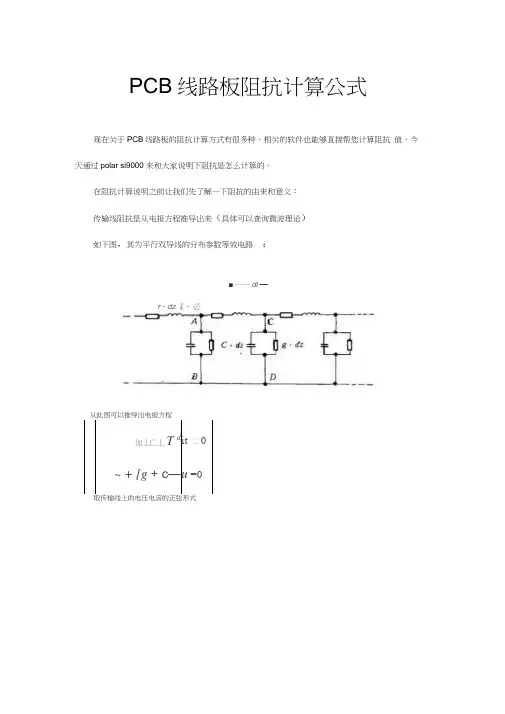

在阻抗计算说明之前让我们先了解一下阻抗的由来和意义:传输线阻抗是从电报方程推导出来(具体可以查询微波理论)如下图,其为平行双导线的分布参数等效电路:从此图可以推导出电报方程取传输线上的电压电流的正弦形式得推出通解定义出特性阻抗无耗线下r=0, g=0 得注意,此特性阻抗和波阻抗的概念上的差异(具体查看平面波的波阻抗定义)特性阻抗与波阻抗之间关系可从此关系式推出.Ok,理解特性阻抗理论上是怎么回事情,看看实际上的意义,当电压电流在传输线传播的时候,如果特性阻抗不一致所求出的电报方程的解不一致,就造成所谓的反射现象等等.在信号完整性领域里,比如反射,串扰,电源平面切割等问题都可以归类为阻抗不连续问题,因此匹配的重要性在此展现出来.叠层(stackup)的定义我们来看如下一种stackup,主板常用的8 层板(4 层power/ground 以及4 层走线层,sggssggs,分别定义为L1, L2…L8)因此要计算的阻抗为L1,L4,L5,L8下面熟悉下在叠层里面的一些基本概念,和厂家打交道经常会使用的Oz 的概念Oz 本来是重量的单位Oz(盎司)=28.3 g(克)在叠层里面是这么定义的,在一平方英尺的面积上铺一盎司的铜的厚度为1Oz,对应的单位如下介电常数(DK)的概念电容器极板间有电介质存在时的电容量Cx 与同样形状和尺寸的真空电容量Co之比为介电常数:ε = Cx/Co = ε'-ε"Prepreg/Core 的概念pp 是种介质材料,由玻璃纤维和环氧树脂组成,core 其实也是pp 类型介质,只不过他两面都覆有铜箔,而pp 没有.传输线特性阻抗的计算首先,我们来看下传输线的基本类型,在计算阻抗的时候通常有如下类型: 微带线和带状线,对于他们的区分,最简单的理解是,微带线只有1 个参考地,而带状线有2个参考地,如下图所示对照上面常用的8 层主板,只有top 和bottom 走线层才是微带线类型,其他的走线层都是带状线类型在计算传输线特性阻抗的时候, 主板阻抗要求基本上是:单线阻抗要求55 或者60Ohm,差分线阻抗要求是70~110Ohm,厚度要求一般是1~2mm,根据板厚要求来分层得到各厚度高度.在此假设板厚为1.6mm,也就是63mil 左右, 单端阻抗要求60Ohm,差分阻抗要求100Ohm,我们假设以如下的叠层来走线。

PCB线路板阻抗计算公式现在关于PCB线路板得阻抗计算方式有很多种,相关得软件也能够直接帮您计算阻抗值,今天通过polar si9000来与大家说明下阻抗就是怎么计算得。

在阻抗计算说明之前让我们先了解一下阻抗得由来与意义:传输线阻抗就是从电报方程推导出来(具体可以查询微波理论)如下图,其为平行双导线得分布参数等效电路:从此图可以推导出电报方程取传输线上得电压电流得正弦形式得推出通解ﻫ定义出特性阻抗ﻫ无耗线下r=0,g=0 得ﻫﻫ注意,此特性阻抗与波阻抗得概念上得差异(具体查瞧平面波得波阻抗定义)特性阻抗与波阻抗之间关系可从此关系式推出、Ok,理解特性阻抗理论上就是怎么回事情,瞧瞧实际上得意义,当电压电流在传输线传播得时候,如果特性阻抗不一致所求出得电报方程得解不一致,就造成所谓得反射现象等等、在信号完整性领域里,比如反射,串扰,电源平面切割等问题都可以归类为阻抗不连续问题,因此匹配得重要性在此展现出来、叠层(stackup)得定义我们来瞧如下一种stackup,主板常用得8 层板(4 层power/ground以及4 层走线层,sggssggs,分别定义为L1,L2…L8)因此要计算得阻抗为L1,L4,L5,L8下面熟悉下在叠层里面得一些基本概念,与厂家打交道经常会使用得Oz 得概念Oz本来就是重量得单位Oz(盎司)=28、3 g(克)在叠层里面就是这么定义得,在一平方英尺得面积上铺一盎司得铜得厚度为1Oz,对应得单位如下介电常数(DK)得概念电容器极板间有电介质存在时得电容量Cx与同样形状与尺寸得真空电容量Co之比为介电常数:ﻫε =Cx/Co=ε'-ε”ﻫPrepreg/Core 得概念pp就是种介质材料,由玻璃纤维与环氧树脂组成,core其实也就是pp类型介质,只不过她两面都覆有铜箔,而pp没有、传输线特性阻抗得计算首先,我们来瞧下传输线得基本类型,在计算阻抗得时候通常有如下类型:微带线与带状线,对于她们得区分,最简单得理解就是,微带线只有1个参考地,而带状线有2个参考地,如下图所示对照上面常用得8 层主板,只有top 与bottom走线层才就是微带线类型,其她得走线层都就是带状线类型在计算传输线特性阻抗得时候, 主板阻抗要求基本上就是:单线阻抗要求55 或者60O hm,差分线阻抗要求就是70~110Ohm,厚度要求一般就是1~2mm,根据板厚要求来分层得到各厚度高度、在此假设板厚为1、6mm,也就就是63mil 左右, 单端阻抗要求60Ohm,差分阻抗要求100Ohm,我们假设以如下得叠层来走线。

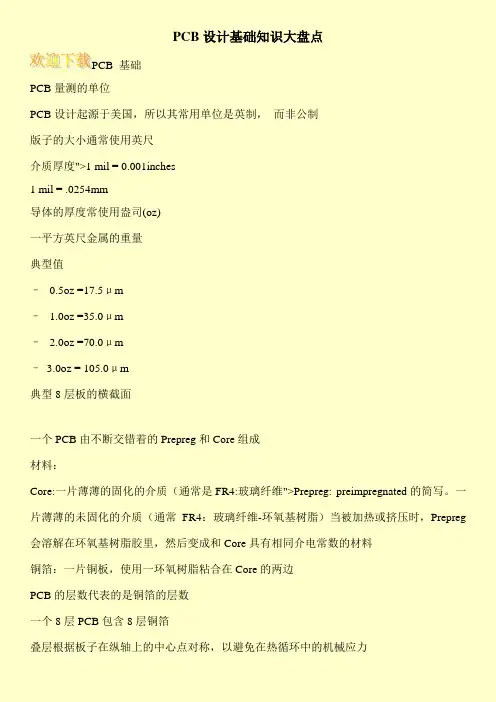

PCB设计基础知识大盘点

PCB 基础

PCB量测的单位

PCB设计起源于美国,所以其常用单位是英制,而非公制

版子的大小通常使用英尺

介质厚度">1 mil = 0.001inches

1 mil = .0254mm

导体的厚度常使用盎司(oz)

一平方英尺金属的重量

典型值

– 0.5oz =17.5μm

– 1.0oz =35.0μm

– 2.0oz =70.0μm

–3.0oz = 105.0μm

典型8层板的横截面

一个PCB由不断交错着的Prepreg和Core组成

材料:

Core:一片薄薄的固化的介质(通常是FR4:玻璃纤维">Prepreg: preimpregnated的简写。

一片薄薄的未固化的介质(通常FR4:玻璃纤维-环氧基树脂)当被加热或挤压时,Prepreg 会溶解在环氧基树脂胶里,然后变成和Core具有相同介电常数的材料

铜箔:一片铜板,使用一环氧树脂粘合在Core的两边

PCB的层数代表的是铜箔的层数

一个8层PCB包含8层铜箔

叠层根据板子在纵轴上的中心点对称,以避免在热循环中的机械应力。

PCB线路板阻抗计算公式现在关于PCB线路板的阻抗计算方式有很多种,相关的软件也能够直接帮您计算阻抗值,今天通过polar si9000 来和大家说明下阻抗是怎么计算的。

在阻抗计算说明之前让我们先了解一下阻抗的由来和意义:传输线阻抗是从电报方程推导出来(具体可以查询微波理论)如下图,其为平行双导线的分布参数等效电路:■------ di —r - dz£・必从此图可以推导出电报方程加丄匚丄T d ~ + [g+ c—it 二0 u=0取传输线上的电压电流的正弦形式劣==一+ j如oc= - -f*推岀通解辽/『+ jy g + J^c定义岀特性阻抗无耗线下r=0, g=0 得7 -区%、注意,此特性阻抗和波阻抗的概念上的差异(具体查看平面波的波阻抗定义)|£C = Ep特性阻抗与波阻抗之间关系可从厂此关系式推岀.Ok,理解特性阻抗理论上是怎么回事情,看看实际上的意义,当电压电流在传输线传播的时候,如果特性阻抗不一致所求出的电报方程的解不一致,就造成所谓的反射现象等等•在信号完整性领域里,比如反射,串扰,电源平面切割等问题都可以归类为阻抗不连续问题,因此匹配的重要性在此展现出来•叠层(stackup)的定义我们来看如下一种 stackup,主板常用的8层板(4层power/ground 以及4层走线 层,sggssggs,分别定义为L1, L2…L8)因此要计算的阻抗为L1,L4,L5,L8Oz 的概念 Oz 本来是重量的单位 0z (盎司)=28.3 g (克)在叠层里面是这么定义的,在一平方英尺的面积上铺一盎司的铜的厚度为 1Oz,对应的单位如下介电常数(DK )的概念电容器极板间有电介质存在时的电容量Cx 与同样形状和尺寸的真空电容量 Co 之比为介电常数:e = Cx/Co = - ee"'Prepreg/Core 的概念pp 是种介质材料,由玻璃纤维和环氧树脂组成,core 其实也是pp 类型介质,只不过他两面都覆有铜 箔,而pp 没有.外匚走线L1F 面熟悉下在叠层里面的一些基本概念 ,和厂家打交道经常会使用的TQP L2L3L4L5 L6 L7CORFCORE .005"f 9 OZ(QiitAr l^yer+Pl^t ng)1 OZ(GMD)1 OZ1 OZ (VCC) I OZ (S1GMAL) 1 OZ(SIGNAL) 1 OZ(GrJD)F'repreo 丄 rril传输线特性阻抗的计算首先,我们来看下传输线的基本类型,在计算阻抗的时候通常有如下类型:微带线和带状 线,对于他们的区分,最简单的理解是,微带线只有1个参考地,而带状线有2个参考地,如下图 所示诫带线 带状线对照上面常用的8层主板,只有top 和bottom 走线层才是微带线类型,其他的走线层都是带状线类型在计算传输线特性阻抗的时候,主板阻抗要求基本上是:单线阻抗要求55或者600hm, 差分线阻抗要求是 70~1100hm ,厚度要求一般是1~2mm ,根据板厚要求来分层得到各厚度高度•在此假设板厚为1.6mm ,也就是63mil 左右,单端阻抗要求60Ohm ,差分阻抗要求 100Ohm ,我们假设以如下的叠层来走线。

solder mask 阻焊剂;焊锡掩膜;绿漆 PCB板各层含义在EDA软件的专门术语中,有很多不是有相同定义的。

以下就字面上可能的意义来解释。

Mechnical:一般多指板型机械加工尺寸标注层。

Keepoutlayer:定义走线、打穿孔(via或摆零件的区域。

这几个限制可以独立分开定义。

Topoverlay:顶丝印层。

Bottomoverlay:底丝印层。

Toppaste:顶层需要露出铜皮上锡膏的部分。

Bottompaste:底层需要露出铜皮上锡膏的部分。

Topsolder:应指顶层阻焊层,避免在制造过程中或将来维修时可能不小心的短路 Bottomsolder:应指底层阻焊层。

Drillguide:可能是不同孔径大小,对应的符号,个数的一个表。

Drilldrawing:指孔位图,各个不同的孔径会有一个对应的符号。

Multilayer:应该没有单独这一层,能指多层板,针对单面板和双面板而言。

Gerber文件各层对照由Protel2004产生的Gerber文件各层扩展名与PCB原来各层对应关系表: Layer : File extension ------------------------- 顶层Top (copper Layer : .GTL 底层Bottom (copper Layer : .GBL 中间信号层Mid Layer 1, 2, ... , 30 : .G1, .G2, ... , .G30 内电层Internal Plane Layer 1, 2, ... , 16 : .GP1, .GP2, ... , .GP16 顶丝印层Top Overlay : .GTO 底丝印层Bottom Overlay : .GBO 顶掩膜层Top Paste Mask : .GTP 底掩膜层Bottom Paste Mask : .GBP Top Solder Mask : .GTS Bottom Solder Mask : .GBS Keep-Out Layer : .GKO Mechanical Layer 1, 2, ... , 16 : .GM1, .GM2, ... , .GM16 Top Pad Master : .GPT Bottom Pad Master : .GPB Drill Drawing, Top Layer - Bottom Layer (Through Hole : .GD1 Drill Drawing, other Drill (Layer Pairs : .GD2, .GD3, ... Drill Guide, Top Layer - Bottom Layer (Through Hole : .GG1 Drill Guide, other Drill (Layer Pairs : .GG2, .GG3, ... 层PCB板就是在多个板层完成后再采取压制工艺将其压制成一块电路板,而且为了减少成本和过孔干扰,多层PCB板往往并不比双层板和单层板厚多少,这就使得组成多层PCB板的板层相对于普通的双层板和单层板往往厚度更小,机械强度更低,导致对加工的要求更高。

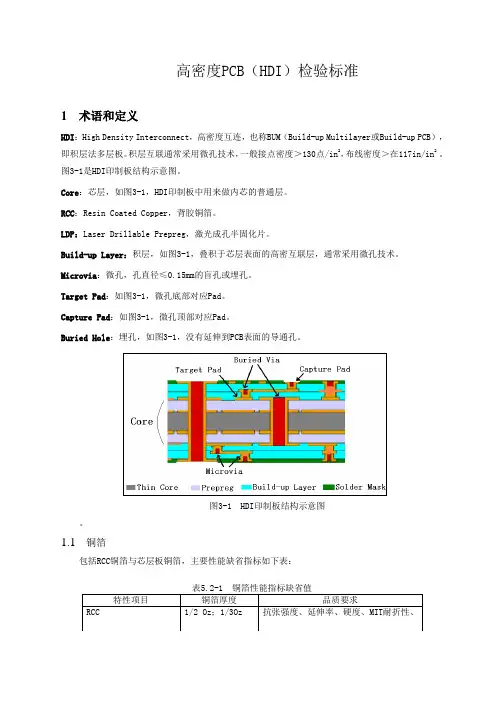

高密度PCB(HDI)检验标准1 术语和定义HDI:High Density Interconnect,高密度互连,也称BUM(Build-up Multilayer或Build-up PCB),即积层法多层板。

积层互联通常采用微孔技术,一般接点密度>130点/in2,布线密度>在117in/in2。

图3-1是HDI印制板结构示意图。

Core:芯层,如图3-1,HDI印制板中用来做内芯的普通层。

RCC:Resin Coated Copper,背胶铜箔。

LDP:Laser Drillable Prepreg,激光成孔半固化片。

Build-up Layer:积层,如图3-1,叠积于芯层表面的高密互联层,通常采用微孔技术。

Microvia:微孔,孔直径≤0.15mm的盲孔或埋孔。

Target Pad:如图3-1,微孔底部对应Pad。

Capture Pad:如图3-1,微孔顶部对应Pad。

Buried Hole:埋孔,如图3-1,没有延伸到PCB表面的导通孔。

图3-1 HDI印制板结构示意图。

1.1铜箔包括RCC铜箔与芯层板铜箔,主要性能缺省指标如下表:1.2金属镀层微孔镀铜厚度要求:表5.3-1 微孔镀层厚度要求2 尺寸要求本节描述HDI印制板的尺寸精度的特别要求,包括板材、导线、孔等。

尺度特性需用带刻度的≥30倍的放大系统作精确的测量和检验。

2.1板材厚度要求及公差2.1.1积层厚度要求及公差缺省积层介质为65~80um的RCC,压合后平均厚度≥40um,最薄处≥30um。

2.2导线公差导线宽度以线路底部宽度为准。

其公差要求如下表所示:表6.2-1 导线精度要求2.3孔径公差表6.3-1 孔径公差要求图6.3-1 微孔孔径示意图2.4微孔孔位微孔允许与Target Pad及Capture Pad相切,但不允许破盘。

图6.4-1 微孔孔位示意图3 结构完整性要求结构完整性要求需在热应力(Thermal stress)试验后进行,热应力试验方法:依据IPC-TM-650-2.6.8条件B进行。

PCB多层板每层厚度及材质(对于板层实物的理解很重要) PCB板的标准厚度有:0.70mm, 0.80mm、0.95mm、1.00mm、1.27mm、1.50mm、1.60mm、2.00mm、2.40mm、3.00mm, 3.20mm、3.50mm、4.00mm、6.40mm等。

1、其中以最多见的1.6mm嘉⽴创的PCB为例:由最上⾯的四层板层压图可知:1.6mm厚度的PCB,最上⾯是⼀层1盎司的铜,然后是(0.2mm-0.5盎司)厚度的PP⽚,然后是第⼆信号层其铜箔只有0.5盎司厚度,接着是(1.2mm-0.5OZ)厚度的core层,下⾯是0.2mm厚度的PP⽚,最后是1盎司的底层。

6层板类似。

2、PP⽚和芯板上图中的Prepreg是PCB的薄⽚绝缘材料。

Prepreg在被层压前未半固化⽚,⼜称为预浸材料,主要⽤于多层印制板的内层导电图形的粘合材料及绝缘材料。

在Prepreg被层压后,半固化的环氧树脂被挤压开来,开始流动并凝固,将多层电路板粘合在⼀起,并形成⼀层可靠的绝缘体。

上图中的core是制作印制板的基础材料。

Core⼜称之为芯板,具有⼀定的硬度及厚度,并且双⾯包铜。

所以,其实就是Core与Prepreg压合⽽成的。

他们的区别:1)、Prepreg在PCB中属于⼀种材料,前者材质半固态,类似于纸板,后者材质坚硬,类似于铜板;2)、Prepreg类似于粘合剂+绝缘体;⽽Core则是PCB的基础材料,两种是完全不同的功能作⽤;3)、Prepreg能够卷曲⽽Core⽆法弯曲;4)、Prepreg不导电,⽽Core两⾯均有铜层,是印制板的导电介质。

3、嘉⽴创PCB的具体参数:a、PP的型号:2116b、介电常数:⼤致4.2-4.7c、内层铜厚0.5盎司,外层铜厚1盎司d、沉⾦厚度:0.02-0.03UM(微⽶)左右,喷锡:平均厚度⼤于15UM(微⽶),铜箔平均厚度⼤于30UM(微⽶)孔铜平均厚度⼤于18UM(微⽶),阻焊油厚度在10-15UM(微⽶)左右,字符油厚度在5-8UM(微⽶)左右。

1、基材:base material2、层压板:laminate3、覆金属箔基材:metal-clad bade material4、覆铜箔层压板:copper-clad laminate (CCL)5、单面覆铜箔层压板:single-sided copper-clad laminate6、双面覆铜箔层压板:double-sided copper-clad laminate7、复合层压板:composite laminate8、薄层压板:thin laminate9、金属芯覆铜箔层压板:metal core copper-clad laminate10、金属基覆铜层压板:metal base copper-clad laminate11、挠性覆铜箔绝缘薄膜:flexible copper-clad dielectric film12、基体材料:basis material13、预浸材料:prepreg14、粘结片:bonding sheet15、预浸粘结片:preimpregnated bonding sheer16、环氧玻璃基板:epoxy glass substrate17、加成法用层压板:laminate for additive process18、预制内层覆箔板:mass lamination panel19、内层芯板:core material20、催化板材:catalyzed board ,coated catalyzed laminate21、涂胶催化层压板:adhesive-coated catalyzed laminate22、涂胶无催层压板:adhesive-coated uncatalyzed laminate23、粘结层:bonding layer24、粘结膜:film adhesive25、涂胶粘剂绝缘薄膜:adhesive coated dielectric film26、无支撑胶粘剂膜:unsupported adhesive film27、覆盖层:cover layer (cover lay)28、增强板材:stiffener material29、铜箔面:copper-clad surface30、去铜箔面:foil removal surface31、层压板面:unclad laminate surface32、基膜面:base film surface33、胶粘剂面:adhesive faec34、原始光洁面:plate finish35、粗面:matt finish36、纵向:length wise direction37、模向:cross wise direction38、剪切板:cut to size panel39、酚醛纸质覆铜箔板:phenolic cellulose paper copper-clad laminates (phenolic/paperCCL)40、环氧纸质覆铜箔板:epoxide cellulose paper copper-clad laminates (epoxy/paperCCL)41、环氧玻璃布基覆铜箔板:epoxide woven glass fabric copper-clad laminates42、环氧玻璃布纸复合覆铜箔板:epoxide cellulose paper core, glass cloth surfacescopper-clad laminates43、环氧玻璃布玻璃纤维复合覆铜箔板:epoxide non woven/woven glass reinforced copper-clad laminates44、聚酯玻璃布覆铜箔板:ployester woven glass fabric copper-clad laminates45、聚酰亚胺玻璃布覆铜箔板:polyimide woven glass fabric copper-clad laminates46、双马来酰亚胺三嗪环氧玻璃布覆铜箔板:bismaleimide/triazine/epoxide woven glass fabric copper-clad lamimates47、环氧合成纤维布覆铜箔板:epoxide synthetic fiber fabric copper-clad laminates48、聚四乙烯玻璃纤维覆铜箔板:teflon/fiber glass copper-clad laminates49、超薄型层压板:ultra thin laminate50、陶瓷基覆铜箔板:ceramics base copper-clad laminates51、紫外线阻挡型覆铜箔板:UV blocking copper-clad laminates<BR< p>。

Prepreg&core

Prepreg:半固化片,又称预浸材料,是用树脂浸渍并固化到中间程度(B阶)的薄片材料。

半固化片可用作多层印制板的内层导电图形的黏结材料和层间绝缘。

在层压时,半固化片的环氧树脂融化、流动、凝固,将各层电路毅合在一起,并形成可靠的绝缘层。

core:芯板,芯板是一种硬质的、有特定厚度的、两面包铜的板材,是构成印制板的基础材料。

通常我们所说的多层板是由芯板和半固化片互相层叠压合而成的。

而半固化片构成所谓的浸润层,起到粘合芯板的作用,虽然也有一定的初始厚度,但是在压制过程中其厚度会发生一些变化。

通常多层板最外面的两个介质层都是浸润层,在这两层的外面使用单独的铜箔层作为外层铜箔。

外层铜箔和内层铜箔的原始厚度规格,一般有0.5OZ、1OZ、2OZ(1OZ约为35um或1.4mil)三种,但经过一系列表面处理后,外层铜箔的最终厚度一般会增加将近1OZ左右。

内层铜箔即为芯板两面的包铜,其最终厚度与原始厚度相差很小,但由于蚀刻的原因,一般会减少几个um。

多层板的最外层是阻焊层,就是我们常说的“绿油”,当然它也可以是黄色或者其它颜色。

阻焊层的厚度一般不太容易准确确定,在表面无铜箔的区域比有铜箔的区域要稍厚一些,但因为缺少了铜箔的厚度,所以铜箔还是显得更突出,当我们用手指触摸印制板表面时就能感觉到。

当制作某一特定厚度的印制板时,一方面要求合理地选择各种材料的参数,另一方面,半固化片最终成型厚度也会比初始厚度小一些。

下面是一个典型的6层板叠层结构

(iMX255coreboard):

PCB的参数:

不同的印制板厂,PCB的参数会有细微的差异,需要与电路板厂的工程师沟通,得到该厂的一些参数数据,主要是介电常数和阻焊层厚度两个参数各个板厂会有差别。

表层铜箔:

可以使用的表层铜箔材料厚度有三种:12um、18um和35um。

加工完成后的最终厚度大约是44um、50um和67um,大致相当于铜厚1 OZ、1.5 OZ、2 OZ。

注意:在用阻抗计算软件进行阻抗控制时,外层的铜厚没有0.5 OZ的值。

芯板:我们常用的板材是S1141A,标准的FR-4,两面包铜,可选用的规格可与厂家联系确定。

半固化片:

规格(原始厚度)有7628(0.185mm/7.4mil),2116(0.105mm/4.2mil),1080(0.075mm /3mil),3313(0.095mm/4mil),实际压制完成后的厚度通常会比原始值小10-15um左右(即0.5-1mil),因此叠层设计的最小介质层厚不得小于3mil。

同一个浸润层最多可以使用3个半固化片,而且3个半固化片的厚度不能都相同,最少可以只用一个半固化片,但有的厂家要求必须至少使用两个。

如果半固化片的厚度不够,可以把芯板两面的铜箔蚀刻掉,再在两

面用半固化片粘连,这样可以实现较厚的浸润层。

半固化片的介电常数与厚度有关,下表为不同型号的半固化片厚度和介电常数参数:

型号厚度介电常数

1080 2.8mil 4.3

3313 3.8mil 4.3

2116 4.5mil 4.5

7628 6.8mil 4.7 板材的介电常数与其所用的树脂材料有关,FR4板材其介电常数为4.2—4.7,并且随着频率的增加会减小。

阻焊层:

铜箔上面的阻焊层厚度C2≈8-10um,表面无铜箔区域的阻焊层厚度C1根据表面铜厚的不同而不同,当表面铜厚为45um时C1≈13-15um,当表面铜厚为70um时C1≈17-18um,在用SI9000进行计算时,阻焊层的厚度取0.5OZ即可。

导线横截面:

由于铜箔腐蚀的关系,导线的横截面不是一个矩形,实际上是一个梯形。

以TOP层为例,当铜箔厚度为1OZ时,梯形的上底边比下底边短1MIL。

比如线宽5MIL,那么其上底边约4MIL,下底边5MIL。

上下底边的差异和铜厚有关,下表是不同情况下梯形上下底的关系。

线宽铜厚(OZ)上线宽(mil)下线宽(mil)

内层 0.5 W-0.5 W

内层 1 W-1 W

内层 2 W-1.5 W-1

外层 0.5 W-1 W

外层 1 W-0.8 W-0.5

外层 2 W-1.5 W-1

说明:上表中的W表示设计的理想线宽。

通常阻抗计算采用的模型为:

上面两个模型为基本的微带线模型和带状线模型。

在微带线模型中,还有如下几种:

无涂覆层的模型一般不采用。

上图右边的模型中的介电常数Er1和Er2根据采用的半固化片的具体型号确定,主要型号已经在上面列出。

具体的参数需要向板厂咨询。

下面解释板厂给我们的叠层图的含义:。