Verilog HDL与FPGA数字系统设计ch05_FSM

- 格式:ppt

- 大小:1.17 MB

- 文档页数:6

基于FPGA verilog HDL的FSM设计

陈晓

【期刊名称】《福建电脑》

【年(卷),期】2017(033)003

【摘要】本文主要介绍了有限状态自动机的分类与比较及状态编码,采用verilog HDL分别进行了一段式状态机、两段式状态机、三段式状态机三种设计.

【总页数】2页(P130-131)

【作者】陈晓

【作者单位】广东工商职业学院广东肇庆 526040

【正文语种】中文

【相关文献】

1.用Verilog HDL实现基于FPGA的通用分频器的设计 [J], 罗浩;许艳;仲佳嘉

2.基于FPGA的verilog HDL语言设计优化 [J], 王春旭;周晓平;王黎黎

3.基于Verilog HDL的高速可综合FSM设计 [J], 王鹏;郭忠文

4.基于Verilog HDL的FPGA数字系统设计优化 [J], 李桂林;苗长新

5.基于Verilog HDL语言的FPGA设计 [J], 彭保;范婷婷;马建国

因版权原因,仅展示原文概要,查看原文内容请购买。

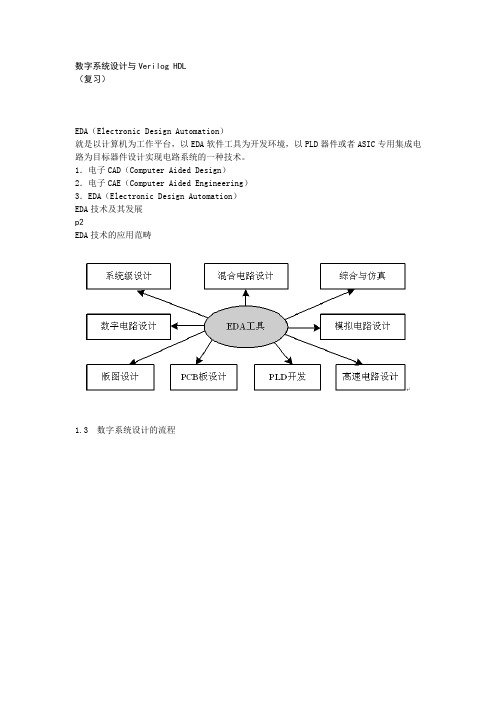

数字系统设计与Verilog HDL(复习)EDA(Electronic Design Automation)就是以计算机为工作平台,以EDA软件工具为开发环境,以PLD器件或者ASIC专用集成电路为目标器件设计实现电路系统的一种技术。

1.电子CAD(Computer Aided Design)2.电子CAE(Computer Aided Engineering)3.EDA(Electronic Design Automation)EDA技术及其发展p2EDA技术的应用范畴1.3 数字系统设计的流程基于FPGA/CPLD的数字系统设计流程1. 原理图输入(Schematic diagrams )2、硬件描述语言 (HDL文本输入)设计输入硬件描述语言与软件编程语言有本质的区别综合(Synthesis)将较高层次的设计描述自动转化为较低层次描述的过程◆行为综合:从算法表示、行为描述转换到寄存器传输级(RTL)◆逻辑综合:RTL级描述转换到逻辑门级(包括触发器)◆版图综合或结构综合:从逻辑门表示转换到版图表示,或转换到PLD器件的配置网表表示综合器是能自动实现上述转换的软件工具,是能将原理图或HDL语言描述的电路功能转化为具体电路网表的工具适配适配器也称为结构综合器,它的功能是将由综合器产生的网表文件配置于指定的目标器件中,并产生最终的可下载文件对CPLD器件而言,产生熔丝图文件,即JEDEC文件;对FPGA器件则产生Bitstream 位流数据文件p8仿真(Simulation)功能仿真(Function Simulation)时序仿真(Timing Simulation)仿真是对所设计电路的功能的验证p9编程(Program)把适配后生成的编程文件装入到PLD器件中的过程,或称为下载。

通常将对基于EEPROM工艺的非易失结构PLD器件的下载称为编程(Program),将基于SRAM 工艺结构的PLD器件的下载称为配置(Configure)。

数字系统设计与VerilogHDL课程设计一、课程设计背景数字系统设计和VerilogHDL是计算机科学与技术专业中比较重要的课程之一。

在该课程中,学生将学习到数字系统的设计和实现过程,以及VerilogHDL语言的应用和编写。

本课程设计旨在让学生通过实践,巩固并深化所学知识,提高其实际运用能力,并帮助学生更好地理解数字系统设计和VerilogHDL的重要性。

二、课程设计目标与要求1. 课程设计目标本课程设计主要目标是让学生了解数字系统设计和VerilogHDL的工作原理和实现方法,并通过实践进行巩固,提高学生的动手能力,为日后从事该领域的工作做好充分的准备。

2. 课程设计要求本课程设计要求学生能够在充分理解了数字系统设计和VerilogHDL的基本原理和方法后,进行硬件电路图、程序代码的设计和仿真。

同时,学生需要自主完成以下任务:1.学习数字系统设计和VerilogHDL的基本知识。

2.设计并仿真一个简单的多功能数字系统,包括至少一个输入和一个输出设备,以及多个存储器(SRAM、DRAM、ROM等都可以)。

3.使用VerilogHDL语言设计实现一个几位数的计算器。

4.完成个人或小组课程设计报告,包括设计过程中的心得、体会等内容。

三、课程设计流程1. 学习数字系统设计和VerilogHDL的基本知识数字系统设计和VerilogHDL的基本知识包括数字系统的基本概念、数字信号处理、电路设计和VerilogHDL的基本语法和程序设计方法等。

学生可以通过阅读相关教材和参考资料来学习这些知识。

2. 设计多功能数字系统在完成学习后,学生可以开始设计自己的多功能数字系统。

该系统应该包括输入、输出、存储器等组件,并应该考虑到系统的稳定性、处理速度、数据存储和传输等方面的问题。

设计的过程中还需注意电路连接、时序控制、设计优化等方面,确保数字系统的高效功能和性能。

3. 设计计算器在完成多功能数字系统的设计后,学生可以进一步使用VerilogHDL语言,编写程序设计一个几位数的计算器。

fpga数字电路设计与verilog hdl编程FPGA(现场可编程逻辑门阵列)数字电路设计是一种高度灵活的硬件设计方法,它允许工程师在芯片上实现复杂的数字逻辑电路。

Verilog HDL(硬件描述语言)编程是一种用于描述数字电路行为和结构的语言,它可以用于编写FPGA数字电路的设计。

FPGA数字电路设计与Verilog HDL编程的主要步骤如下:1. 设计需求分析:首先,明确设计的目标和功能需求,例如实现特定的逻辑功能、控制算法等。

2. 设计输入:将需求转换为数字电路逻辑,可以使用硬件描述语言(如Verilog或VHDL)编写。

编写过程中,需要遵循一定的编程规范,如模块化设计、良好注释等。

3. 逻辑仿真:在设计完成后,需要对电路进行逻辑仿真,以验证其功能是否正确。

仿真工具可以将Verilog代码转换为数字电路,并模拟其实际运行情况。

通过观察仿真结果,可以发现并修复设计中的问题。

4. 综合:将编写好的Verilog代码综合为具体的FPGA芯片配置文件。

综合工具会将逻辑电路优化,以便在FPGA上实现。

这一步骤会生成硬件描述文件,包括布局、布线信息等。

5. 下载与测试:将生成的FPGA配置文件下载到目标FPGA芯片上,并进行实际测试。

测试过程中,可以通过观察输出结果、与预期结果对比等方式,验证设计功能的正确性。

6. 优化与迭代:根据测试结果,对设计进行优化。

这可能包括修改Verilog代码、调整布局布线等。

经过多次迭代,直至达到满意的性能。

7. 交付与生产:完成设计验证后,可以将优化后的FPGA设计交付给生产环节,用于实际应用。

总之,FPGA数字电路设计与Verilog HDL编程是一种灵活且高效的设计方法。

通过编写Verilog代码,可以实现复杂的数字逻辑电路,并在FPGA芯片上实时运行。

在设计过程中,需要关注编程规范、逻辑仿真、综合与优化等方面,以保证电路功能的正确性和性能。