第81章低功耗设计问题-大连理工大学精品课程建设工程

- 格式:ppt

- 大小:514.50 KB

- 文档页数:14

嵌入式系统中的低功耗设计策略在嵌入式系统中,低功耗设计一直是一个重要的课题。

随着移动互联网的迅速发展和智能设备的普及,对于嵌入式系统的功耗要求也越来越高。

低功耗设计不仅可以延长嵌入式系统的使用时间,还可以降低系统的发热量,提高系统的稳定性和可靠性。

因此,如何在设计阶段合理降低系统的功耗,成为了设计工程师们必须面对的一个挑战。

首先,在嵌入式系统中实施低功耗设计策略时,可以从硬件设计和软件设计两个方面进行考虑。

在硬件设计方面,采用低功耗的微处理器和低功耗芯片是提高整体系统功耗效率的关键。

选择适合的电源管理芯片并在设计中合理布局供电线路,可以有效减少功耗的消耗。

此外,通过合理设计系统的时钟频率和使用低功耗组件也是低功耗设计的重要手段。

其次,对于软件设计而言,优化软件算法和程序结构是减少系统功耗的有效途径。

在编写程序时,尽量避免频繁的访问外设和传输数据,可以有效减少系统的功耗。

同时,合理控制系统的进程调度和休眠策略,避免程序长时间运行或者在系统空闲时进入休眠模式,也是保证系统低功耗的必备措施。

另外,在嵌入式系统中,尽量利用硬件加速器来减少系统功耗也是一个有效策略。

通过合理设计硬件加速器的功能和使用场景,可以将部分高功耗任务交给硬件加速器来完成,减轻处理器的计算压力,从而降低系统功耗。

此外,采用合适的传输协议和数据压缩技术,也可以有效减少系统在数据传输时的功耗消耗。

最后,为了实时监测系统功耗情况,可以在系统中集成功耗监测模块,随时监控系统各组件的功耗情况。

通过实时监测系统的功耗消耗情况,可以及时发现系统中存在的功耗瓶颈和问题,从而采取相应措施进行优化,保证系统的最佳功耗状态。

综上所述,嵌入式系统中的低功耗设计策略涉及多个方面,包括硬件设计、软件设计、利用硬件加速器、传输协议选择以及功耗监测等各个环节。

只有在全面考虑各个方面的因素并采取相应措施的情况下,才能够确保嵌入式系统在功耗上取得最佳性能,满足用户对于低功耗和高性能的需求。

超低功耗电子电路系统设计原则虽然超低功耗设计仍然是在CMOS集成电路(IC)基础上发展起来的,但是因为用户众多,数千种专用或通用超低功耗IC不断涌现,使设计人员不再在传统的CMOS 型IC上下功夫,转而选择新型超低功耗IC,致使近年来产生了多种超低功耗仪表。

电池供电的水表、暖气表和煤气表近几年能够发展起来就是一个证明。

目前,电池供电的单片机则是超低功耗IC的代表。

本文将对超低功耗电路设计原则进行分析,并就怎样设计成超低功耗的产品作一些论述,从而证明了这种电路在电路结构和性价比等方面对传统电路极具竞争力。

1 CMOS集成电路的功耗分析无论是低功耗还是超低功耗IC,主要还是建立在CMOS电路基础上的。

虽然超低功耗IC对单元电路进行了新形式的设计,但作为功耗分析,仍然离不开 CMOS 电路基本原理。

以74系列为代表的TTL集成电路,每门的平均功耗约为10mW;低功耗的TTL集成电路,每门平均功耗只有1mW。

74系列高速 CMOS电路,每门平均功耗约为10μW;而超低功耗CMOS通用小规模IC,整片的静态平均功耗却可低于10μW。

传统的单片机,休眠电流常在 50μA~2mA范围内;而超低功耗的单片机休眠电流可达到1μA以下。

CMOS电路的动态功耗不仅取决于负载,而且就电路内部而言,功耗与电源电压、集成度、输出电平以及工作频率都有密切联系。

因此设计超低功耗电路时不得不对全部元件的内外性质做仔细分析。

CHMOS或CMOS电路的功耗特性一般可以表示为:P=PD+PA式中, P--总功耗PD--静态功耗,PD=VDD·IDD (1)PA--动态功耗,PA=PTC+PC=VDD·ITC+f·CL·vdd2(2)PTC --瞬时导通功耗PC--输出电容充放电功耗VDD--工作电源电压IDD--静态时由电源流向电路内部的电流ITC--脉冲电流的时间平均值f--输入脉冲重复频率CL--电路输出端的负载电容式(1)为静态功耗表达式。

FPGA设计与应用_大连理工大学中国大学mooc课后章节答案期末考试题库2023年1.Xilinx FPGA芯片的核心资源不包括()。

答案:Flash2.Verilog HDL的常量不包括()。

答案:枚举型3.最适合做开关级建模的语言是()。

答案:Verilog HDL4.下列Verilog HDL标识符错误的是()。

答案:16_bitss5.关于assign语句说法不正确的是()。

答案:assign语句有可能综合成触发器。

6.关于always语句说法不正确的是()。

答案:always语句一定综合成触发器。

7.下列不符合可综合设计的描述方法()。

答案:使用阻塞赋值,使得行为描述语句内实现并行化。

8.下列哪个厂商不是FPGA的制造商()。

答案:E-ELEMENTS9.ModelSim SE进行Verilog HDL仿真验证非必须的仿真库是()。

答案:std_ver10.关于if和case语句说法不正确的是()。

答案:case比if的面积小。

11.在Verilog HDL中,错误的整数表示是()。

答案:4’200012.关于BlockRam说法正确的是()。

答案:BlockRam的深度和位宽是可以配置的。

13.下列数据类型声明错误的是()。

答案:wire data_i [2:0];14.假设向量线网a的值是4’b1001,下列表达式结果等于1的是()。

答案:~^ a15.下列哪一项不是同步电路设计的优点()。

答案:节约面积,提高集成度。

16.不属于FPGA设计流程中的仿真环节是()。

答案:结构仿真17.关于逻辑运算符说法不准确的是()。

答案:逻辑非(!)与一元非(~)用法完全相同。

18.关于端口说法正确的是()。

答案:缺省的端口类型是wire型。

19.在always和initial语句中不可以使用的语句是()。

答案:模块例化语句20.FPGA的配置模式不包括()。

答案:主从模式21.不属于ChipScope Pro工具的部分是()。

低功耗CMOS带隙基准源赵玉迎;厚娇;常金;姜久兴;赵波【摘要】本文采用了CSMC 0.18um的标准CMOS工艺,设计了一种工作在亚阈值区的低功耗CMOS带隙基准源,本设计电路是由纯MOS管组成,不包含双极型晶体管,采用工作在线性区的MOS管代替电阻,减少了芯片的面积,工作在亚阈区的MOS管也使得系统的功耗有所降低。

室温下,整个电路系统的电流(包含启动电路)为433.08nA,功耗为649.6nW,版图面积为0.0048mm2,工艺流程与标准CMOS工艺有很好的兼容性。

%This article uses CSMC 0.18µm standard CMOS process technology, a low power CMOS voltage reference was developed using 0.18µm CMOS process technology, The device consists of MOSFET circuit operated in the subthreshold region and used no resistors, the design of the circuit is composed of pure MOS transistors, does not include the transistors, using a strong-inversion of the MOS transistor instead of resistance, greatly reducing the chip area,working in sub-threshold region MOS transistors also makes the system power consumption is greatly reduced. At room temperature, the current overall circuit (including start-up circuit) is about 433.08nA, the power is 649.6nW, the layout area is 0.0048mm2, process have good compatibility with standard CMOS process.【期刊名称】《电子世界》【年(卷),期】2015(000)023【总页数】4页(P27-30)【关键词】带隙基准;低功耗;亚阈值区【作者】赵玉迎;厚娇;常金;姜久兴;赵波【作者单位】哈尔滨理工大学;哈尔滨理工大学;哈尔滨理工大学;哈尔滨理工大学;哈尔滨理工大学【正文语种】中文便携式电子产品已经成为当今消费者的重要需求,SoC技术的广泛应用已经成为当今发展的重要趋势,低功耗是SoC系统的发展目标[1]。

数字电路与系统_大连理工大学中国大学mooc课后章节答案期末考试题库2023年1.ASM图是数字系统控制过程的算法流程图,表示了所有操作的准确时间序列,精确到一个时钟周期。

参考答案:正确2.把256×2的RAM,扩展成256×4的RAM,需要2片256×2的RAM。

参考答案:正确3.设计三种图案彩灯控制系统的控制器。

三种图案彩灯依次循环亮,其中苹果形图案灯亮16 s,香蕉形图案灯亮12 s,葡萄形图案灯亮9 s。

用逻辑变量A、B、G分别表示苹果灯、香蕉灯、葡萄灯。

用逻辑变量X、Y、Z分别表示计时信号16s、12s、9s。

下列ASM图正确表示了该灯光控制系统。

【图片】参考答案:错误4.计数器不是时序逻辑电路。

参考答案:错误5.已知有DAC电路,如下图所示。

其中【图片】,【图片】=5伏,当输入二进制数为110时,输出电压是多少?【图片】参考答案:-3.75 伏6.观察下列电路,Vref=10伏,如果输入二进制数为1000000000时,输出电压多少?【图片】参考答案:0 伏7.一般来说,时序逻辑电路由组合电路和触发器两部分组成。

参考答案:正确8.74161是一款模15的计数器。

参考答案:错误9.74163是异步清零、同步置数的计数器。

参考答案:错误10.如果用卡诺图化简逻辑函数,拟得到最简或与式,应该在卡诺图上圈0。

参考答案:正确11.具有直接输入端的触发器,其直接输入端有最高优先权,可以直接决定触发器的状态。

参考答案:正确12.在用卡诺图求逻辑函数的最简与或式的时候,如果有一个圈中的1都被别的圈包含了,那么可以断定:这个圈是多余的。

参考答案:正确13.用74290实现模40的计数器,至少需要2片74290。

参考答案:正确14.把石英晶体加入多谐振荡器电路中,其目的是让频率更稳定。

参考答案:正确15.观察下图,该多路数据选择器完成的逻辑函数是【图片】【图片】参考答案:正确16.已知一个数字系统,有5个独立状态。

化工原理实验_大连理工大学中国大学mooc课后章节答案期末考试题库2023年1.燃烧必须具备可燃物、助燃物和点火源三大条件,缺一不可。

因此,可以采取尽量隔离的方式来防止实验室火灾发生。

参考答案:正确2.流体阻力实验中,必需用到的主要设备包括参考答案:离心泵、阀门、流量计、差压变送器、温度传感器3.为保证板式精馏塔具有较高的塔板效率,工业精馏塔塔板上主要的气液相接触状态为参考答案:泡沫态_喷射态4.流量计校正实验中,可以采用的流量测定方法有参考答案:待测流量计与标准流量计串联_使用置于电子称上方的容器收集液体,计量单位时间收集的液体质量_使用带刻度的容器收集液体,计量单位时间收集的液体体积5.下列流量计中,可以水平安装的流量计有参考答案:文丘里流量计_孔板流量计_涡轮流量计6.实验中如果出现了异常现象或实验数据有明显误差,正确的做法是参考答案:和指导教师一起研究异常现象发生的原因,解决问题_在数据记录中如实注明_对异常现象或有明显误差的数据做出合理的分析、解释7.在进行球阀的局部阻力测试时,可以通过管路系统中的()调整流量参考答案:管路系统中除待测球阀之外的其他阀门开度8.在实验室发生事故时,现场人员应迅速组织、指挥,切断事故源,尽量阻止事态蔓延、保护现场;及时有序的疏散学生等人员,对现场已受伤人员做好自助自救、保护人身及财产。

参考答案:正确9.为方便进出专人管理的设备房间,可自行配制钥匙。

参考答案:错误10.实验室内可以堆放个人物品。

参考答案:错误11.为了预防电击(触电),电气设备的金属外壳须接地,最好是埋设接地电阻很小专用线。

参考答案:正确12.动某些非固定安装的电气设备时(如电风扇,照明灯),可以不必切断电源。

参考答案:错误13.有易燃易爆危险品的实验室禁止使用明火。

参考答案:正确14.从事特种作业(如电工、焊工、辐射、病原微生物等)的人员,必须接受相关的专业培训通过考核并持有相应的资质证书才能上岗。

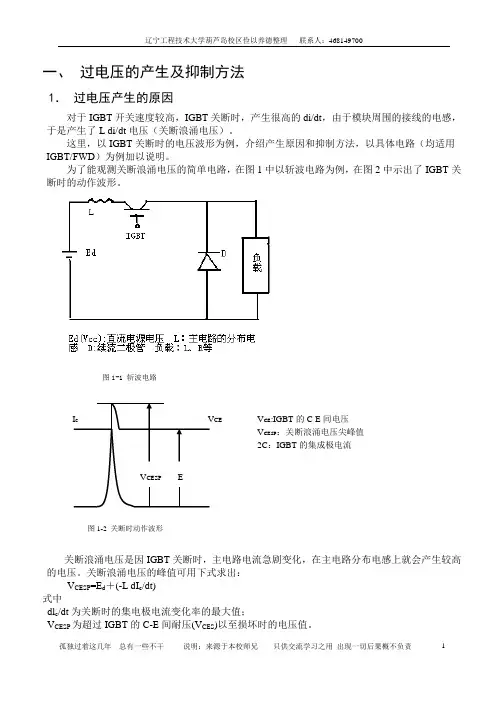

一、 过电压的产生及抑制方法1. 过电压产生的原因对于IGBT 开关速度较高,IGBT 关断时,产生很高的di/dt ,由于模块周围的接线的电感,于是产生了L di/dt 电压(关断浪涌电压)。

这里,以IGBT 关断时的电压波形为例,介绍产生原因和抑制方法,以具体电路(均适用IGBT/FWD )为例加以说明。

为了能观测关断浪涌电压的简单电路,在图1中以斩波电路为例,在图2中示出了IGBT 关断时的动作波形。

图1-1 斩波电路关断浪涌电压是因IGBT 关断时,主电路电流急剧变化,在主电路分布电感上就会产生较高的电压。

关断浪涌电压的峰值可用下式求出:V CESP =E d +(-L dI c /dt)式中dl c /dt 为关断时的集电极电流变化率的最大值;V CESP 为超过IGBT 的C-E 间耐压(V CES )以至损坏时的电压值。

V CE :IGBT 的C-E 间电压 V CESP :关断浪涌电压尖峰值 2C :IGBT 的集成极电流 图1-2 关断时动作波形2.过电压抑制方法作为过电压产生主要因素的关断浪涌电压的抑制方法有如下几种:(1)在IGBT中装有保护电路(=缓冲电路)可吸浪涌电压。

缓冲电路的电容采用薄膜电容,并靠近IGBT配置,可使高频浪涌电压旁路。

(2)调整IGBT的驱动电路的V CE或R C,使di/dt最小。

(3)尽量将电件电容靠近IGBT安装,以减小分布电感,采用低阻抗型的电容效果更佳。

(4)为降低主电路及缓冲电路的分布电感,接线越短越粗越好,用铜片作接线效果更佳。

图1-1为过电压抑制措施及配置位置。

图1-1 过电压抑制措施及配置位置F—避雷针D—变压器静电屏蔽层C—静电感应过电压抑制电容RC1—阀侧浪涌过电压抑制用RC电路RC2—阀侧浪涌过电压抑制用反向阻断式RC电路RV—压敏电阻过电压抑制器RC3—阀器件换相过电压抑制用RC电路RC4—直流侧RC抑制电路RCD—阀器件关断过电压抑制用RCD电路二、缓冲电路的种类和特点1、个别缓冲电路(1)RC缓冲电路RC缓冲电路的关断浪涌电压抑制效果好,最适合于斩波电路。

低功耗设计论文(5篇)低功耗设计论文(5篇)低功耗设计论文范文第1篇关键词:低功耗;SoC;CMOS;功耗估量;The Application of Low-Power Methods in SoC DesignAbstract: SOC design occupies an important position in IC design market. The low-power design is an important part in SoC design process. This paper firstly gives a comprehensive analysis of the composed of CMOS circuit power consumption and the related theory of power estimation, then analyzes the SoC low-power design theory of various design levels in detail.Keywords: low-power,SoC,CMOS,power estimation1引言随着工艺水平的不断进展,集成电路设计已经进入超深亚微米(Deep Sub-Micron,DSM)和纳米的SoC时代,设计规模越来越大,单一SoC芯片的集成度已经达到了上亿门。

在之前的集成电路设计中,设计者首要关怀的芯片性能往往是面积与速度,然后才是功耗。

到了深亚微米阶段,功耗设计在芯片设计中所占的比重开头上升到与面积和速度同等重要的程度,设计人员需从功耗、性能和成本三者之间取得折衷。

据统计数据分析,目前市场上的一些功能强大的微处理器芯片功耗可达100-150 W,平均功耗密度可达50-75 W/cm2。

而芯片上某些热点(hot spots)的功耗更是数倍于这一数值。

功耗问题的重要性在便携式数码产品芯片的设计中显现的尤为突出。

找工作准备set_dont_touch_network可以穿过logic,可以用于clocks, pins, 或ports。

当你对设计不十分熟悉时,这个属性可能会传到你不希望的地方去。

set_ideal_net = set_ideal_network -no_propagateclk在创建的时候,会默认为ideal net的,但当clk接入到data path的时候,D端就会考虑我clk上的负载,但并不会影响clk的ideal net的属性。

假如我的clk需要门电路做gating,gating后的时钟也有很大的扇出,那我为了忽略掉延迟,是不是需要在gating后重新给clk定义ideal net?因为ideal net不能穿过逻辑。

如果你的CG集成好的标准单元,它会自动继承ideal的属性上面这几句话中涉及到:set_dont_touch_network和set_ideal_network,而实际上我们在综合时用的是set_dont_touch_network虞希清是怎么讲的呢?P60虞希清书中给的时钟建模语句既不包含ideal network语句,也不包含dont touch network语句衍生时钟什么时候用?应该是分频的时候用?061的启示:CTS之后时序变好还是变差061的实验基于:smic65工艺下的源和后处理。

使用icc,所在目录icc_MACROsetupCTS之后,in2reg的时序如何变换?变好还是变差?CTS后,input port的capture clock由于时钟树的存在,会有延时;而input port的launch clock仍然保持不变,故input port的setup时序会变好。

左上图为Place后的时序报告,右上图的CTS后的时序报告。

虽然已经CTS过,但是其input port到达时间中的clock network delay仍然是ideal,仍然为0.input port的到达时间中的clock network delay即使一直到PnR步骤完成,仍然是ideal的,即为0.这并不符合实际情况,因为input port上的信号不可能比时钟提前到,该信号和时钟是同一时间到达的。

##理工大学电气系电路理论大纲解析一、大纲内容第一章:电路模型和电路定律1 电路根本参数:电流,电压,电功率,能量2 电路的原件约束:电阻,电感,电容,电源,受控电源3 电路的结构约束:KCL KVL重点:建立参考方向的概念,掌握元件的端口方程,掌握建立电路方程的根本依据,为以后学习奠定根底。

第二章:电阻电路的等效变换1 电阻的传联合并联2 电阻的Y形连接和三角形连接的等效变换3 实际电源的模型以与等效变换4 输入电阻定义重点:建立等效的概念,以与由复杂化简单的思想。

第三章:电阻电路的一般分析1 图论根底2 线性电阻电路方程的几种建立方法重点:理解每种方法的原理,掌握方程的列写规那么。

熟练掌握回路电流法和节点电压法,掌握其中的一些技巧。

第四章:电路定律1 叠加定律和替代定律2 电源等效定律3 特勒根定律重点:理解和掌握各个定律,运用到实际的问题中。

熟练掌握戴维宁定律和##定律,带受控源的情况以与等效电阻的的计算方法。

第五章:含有运算放大器的电阻电路1 运算放大器的电路模型2 含运算放大器的电路的分析重点:理解运算放大器虚短虚断的含义,并能运用虚短虚断来进展电路分析第六章:一阶电路1 动态电路的概念以与初始条件2 一阶电路的各种响应3 一阶电路的暂态分量和稳态分量重点:熟练列写动态电路暂态过程的微分方程,求电路响应变量的初值,求电路的暂态解。

第七章:二阶电路1 二阶电路的各种响应2列写微分方程分析二阶电路的工作状态重点:理解二阶电路各种响应的概念,能列微分方程分析电路的工作状态:过阻尼,欠阻尼,临界阻尼。

第八章:向量法1 复数和正弦量2 向量法的根底3 电路定律的向量形式重点:能够运用向量法解决具体的电路问题。

第九章:正弦稳态电路的分析1阻抗和导纳的概念2 电路的向量图3 正弦稳态电路的分析4 正弦稳态电路的功率5 电路的谐振重点:理解阻抗和导纳的概念,熟练利用向量法分析正弦稳态电路,理解正弦稳态电路的功率以与其计算与前面的相关概念,定律的比照学习。

运用能量概念的“电路”课程教学方法

陈希有;李冠林;周惠巍

【期刊名称】《电气电子教学学报》

【年(卷),期】2016(38)2

【摘要】本文的基本观点是,在某些专门场合,能量概念比功率更重要,在“电路”

课程教学的某些方面,应适当运用能量概念.为此结合如下内容,包括元件能量与功率、电感的无功功率、RLC串联正弦电路的无功功率、耦合系数相等的证明、RLC串

联电路暂态响应的能量交换关系以及均匀传输线驻波中的电磁能量分析等,阐述了

运用能量概念的教学方法,以便培养学生运用能量概念思考问题的科学视角和工程

观点.

【总页数】5页(P91-95)

【作者】陈希有;李冠林;周惠巍

【作者单位】大连理工大学电子信息与电气工程学部,辽宁大连,116023;大连理工

大学电子信息与电气工程学部,辽宁大连,116023;大连理工大学电子信息与电气工

程学部,辽宁大连,116023

【正文语种】中文

【中图分类】TM13

【相关文献】

1.《集成电路版图设计》课程设计教学方法的初探——集成电路IC人才成长规律

的研究 [J], 房小平;王铁文

2.以模型化电路建立反馈概念先行调整电子电路基础课程教学 [J], 许自图

3.加拿大多元教学方法在高职集成电路设计课程中的运用 [J], 张红;余建

4."电路"课程中谐振电路的一种教学方法 [J], 沙涛;孙建红;杭建军

5.独立学院电路原理图与电路板设计课程教学方法探索 [J], 兰英;黄宇;徐灵飞;因版权原因,仅展示原文概要,查看原文内容请购买。