38译码器实现逻辑电路ppt课件

- 格式:ppt

- 大小:1.46 MB

- 文档页数:11

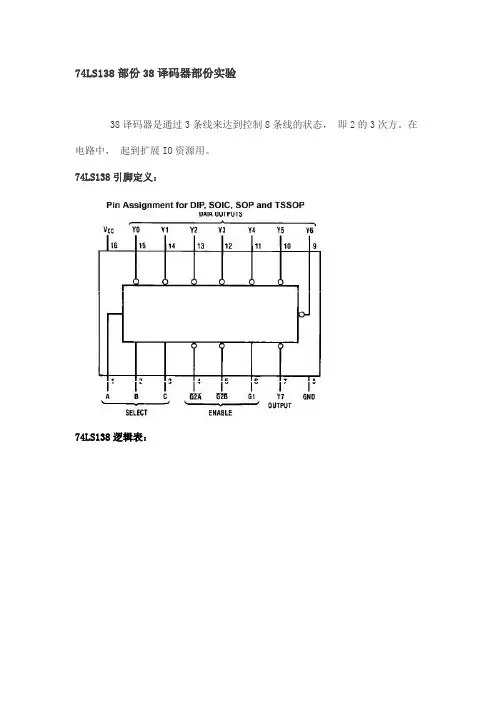

74LS138部份38译码器部份实验38译码器是通过3条线来达到控制8条线的状态,即2的3次方。

在电路中,起到扩展IO资源用。

74LS138引脚定义:74LS138逻辑表:相关原理:程序运行照片:以下实验通过P1.0,P1.1,P1.2三条数据线通过74LS138译码作一个8路跑马灯实验。

接线方法:1、用4PIN数据排线插入CPU部份的JP44的P1.0-P1.3 口.另一端插入74LS138部份的JP22作为数据输入。

2、用一条8PIN数据排线,连接78LS138的输出口JP25到 8路指示灯的JP32,运行可看到跑马灯。

程序流程图:汇编语言参考程序:org 0000hajmp mainorg 0080h ;;定义P1.0,P1.1,P1.2 分别为AA,BB,CC 以便在程序中描述AA EQU P1.0BB EQU P1.1CC EQU P1.2MAIN:CLR CC ;状态1 A,B,C为000CLR BBCLR AACALL DELAY ;调用延时CLR CC ;状态2 A,B,C 为100 CLR BBSETB AACALL DELAY ;调用延时CLR CC ;状态2 A,B,C 为010 SETB BBCLR AACALL DELAYCLR CCSETB BBSETB AACALL DELAYSETB CCCLR BBCLR AACALL DELAYSETB CCCLR BBSETB AACALL DELAYSETB CCSETB BBCLR AACALL DELAYSETB CCSETB BBSETB AACALL DELAYJMP MAIN ;重新开始DELAY: ;延时子程序MOV R5,#255D3:MOV R2,#255D4: DJNZ R2,D4 DJNZ R5,D3RETEND。

《集成电路设计实践》报告题目:3-8译码器设计院系:自动化学院电子工程系专业班级:微电学生学号:学生姓名:指导教师姓名:戴力职称:讲师起止时间:2015.12.25-2016.01.08成绩:一、设计任务1) 依据3-8译码器的真值表,给出3-8译码器的电路图,完成3-8译码器由电路图到晶体管级的转化(需提出至少2种方案);2) 绘制原理图(Sedit),完成电路特性模拟(Tspice,瞬态特性),给出电路最大延时时间;3) 遵循设计规则完成译码器晶体管级电路图的版图,流程如下:4) 版图布局规划-基本单元绘制-功能块的绘制-布线规划-总体版图);5) 版图检查与验证(DRC检查);6) 针对自己画的版图,给出实现该电路的工艺流程图。

二、电路设计方案的确定3-8译码器真值表由三个输入端A,B,C和八个输出端Y0,Y1,Y2,Y3,Y4,Y5 ,Y6,Y7组成,输入输出用二进制表示。

从真值表可看出3-8译码器的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。

如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。

可通过使用三输入与非门及反相器实现功能,三输入与非门由三个pmos和三个nmos组成。

三、电路特性及其仿真首先用S-Edit软件画出电路的模拟图,然后检查所画电路是否存在错误,将各个管子的尺寸标注出来,检查无误后点击T-Spice按钮将出现电路的网表图,然后给检测出的电路网表加上电源和输入信号,经检查,确认添加无误后进行电路模拟仿真,即可得到电路模拟仿真图像。

网表如下:仿真图如下:电路图如下:结果:据仿真结果和设计电路要求对比可以看出,所设计的电路满足设计需求,并且可以实现3-8译码器的功能,所以设计的电路是可以正常使用的。

四、版图的布局规划及基本单元设计根据前面所画的电路模拟图,可以看出3-8译码器需要30个PMOS和30个NMOS,PMOS和NOMS一部分组成反向器,一部分组成多个逻辑门,制作版图时采用L-Edit软件,制作版图时应注意版图各层的相关设计规则及对尺寸的要求,在制作版图时需注意所有光刻孔的几何尺寸都必须大于或等于最小距离。

38译码器原理38译码器是一种常见的数字逻辑电路,它在数字系统中扮演着十分重要的角色。

它能够将输入的数字信号进行解码,输出对应的控制信号,从而实现不同功能的控制。

本文将对38译码器的原理进行介绍,希望能够帮助读者更好地理解和应用这一电路。

首先,我们来看一下38译码器的基本结构。

38译码器由三个输入端和八个输出端组成,输入端共有三位,输出端共有八位。

在输入端,我们可以输入0至7的数字信号;而在输出端,每个输出端对应一个特定的数字信号。

当输入端接收到某一数字信号时,对应的输出端将会输出高电平信号,而其他输出端则输出低电平信号。

接下来,我们来详细了解38译码器的工作原理。

当输入端接收到一个数字信号时,比如输入为3,那么在输出端,对应的第3个输出端将会输出高电平信号,而其他输出端则输出低电平信号。

这样,我们就可以根据输入端的信号来控制对应的输出端,实现不同功能的控制。

在实际应用中,38译码器通常被用于数字系统中的地址译码和显示控制等方面。

在地址译码中,它可以根据输入的地址信号来选择对应的存储单元或外设,实现对存储器或外设的控制和访问。

而在显示控制中,它可以根据输入的数字信号来控制七段数码管等显示设备,实现数字信息的显示和输出。

除此之外,38译码器还可以与其他逻辑电路相结合,实现更复杂的逻辑功能。

比如,它可以与门电路、触发器等组合,构成各种数字逻辑电路,满足不同的应用需求。

因此,熟练掌握38译码器的原理和应用对于数字系统的设计和实现至关重要。

总的来说,38译码器作为一种常见的数字逻辑电路,具有解码输入信号并输出对应控制信号的功能,其原理和应用十分重要。

通过本文的介绍,相信读者对38译码器有了更深入的了解,希望能够对读者在数字系统设计和应用中起到一定的帮助。

希望本文能够帮助读者更好地理解38译码器的原理和应用,同时也希望读者能够在实际应用中灵活运用这一电路,为数字系统的设计和实现提供帮助。

班级:通信13-3班姓名:王亚飞学号:1306030318 指导教师:成绩:电子与信息工程学院信息与通信工程系摘要EDA技术是以微电子技术为物理层面,现代电子设计技术为灵魂,计算机软件技术为手段,最终形成集成电子系统或专用集成电路ASIC为目的的一门新兴技术。

而VHDL语言是硬件描述语言之一,其广泛应用性和结构的完整性使其成为硬件描述语言的代表。

随着社会经济和科技的发展,越来越多的电子产品涌如我们的日常生活当中,在日常生活中译码器起着不可忽视的作用。

本设计就是运用VHDL语言设计的3-8译码器。

3-8译码器电路的输入变量有三个即D0,D1,D2,输出变量有八个Y0-Y7,对输入变量D0,D1,D2译码,就能确定输出端Y0-Y7的输出端变为有效(低电平),从而达到译码目的。

关键词:EDA;3-8译码器1实验目的1、通过一个简单的3-8译码器的设计,让学生掌握组合逻辑电路的设计方法。

2、初步掌握VHDL语言的常用语句。

3、掌握VHDL语言的基本语句及文本输入的EDA设计方法。

2实验背景2.1 VHDL的简介VHDL语言是一种用于电路设计的高级语言。

它在80年代的后期出现。

最初是由美国国防部开发出来供美军用来提高设计的可靠性和缩减开发周期的一种使用范围较小的设计语言。

但是,由于它在一定程度上满足了当时的设计需求,于是他在1987年成为A I/IEEE的标准(IEEE STD 1076-1987)。

1993年更进一步修订,变得更加完备,成为A I/IEEE的A I/IEEE STD 1076-1993标准。

目前,大多数的CAD厂商出品的EDA软件都兼容了这种标准。

VHDL的英文全写是:VHSIC (Very High eed Integrated Circuit)Hardware Descriptiong Language.翻译成中文就是超高速集成电路硬件描述语言。

因此它的应用主要是应用在数字电路的设计中。

实验五 译码器、数据选择器及其应用一、实验目的1.掌握中规模集成译码器、数据选择器的逻辑功能和使用方法。

2.了解译码器的应用。

3.学习用数据选择器构成组合逻辑电路的方法。

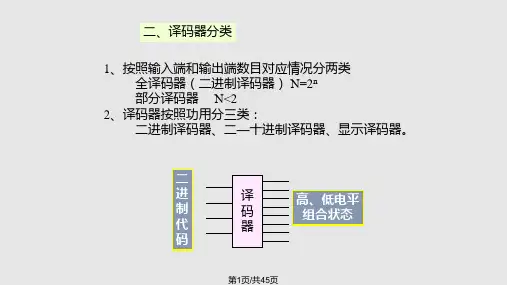

二、实验原理1.译码器是将输入的具有特定含义的二进制代码翻译成输出信号的不同组合,实现电路控制功能的逻辑电路。

译码器在数字系统中应用广泛,可用于代码的转换、终端数字的显示、数据的分配等等。

译码器可分为变量译码器和显示译码器。

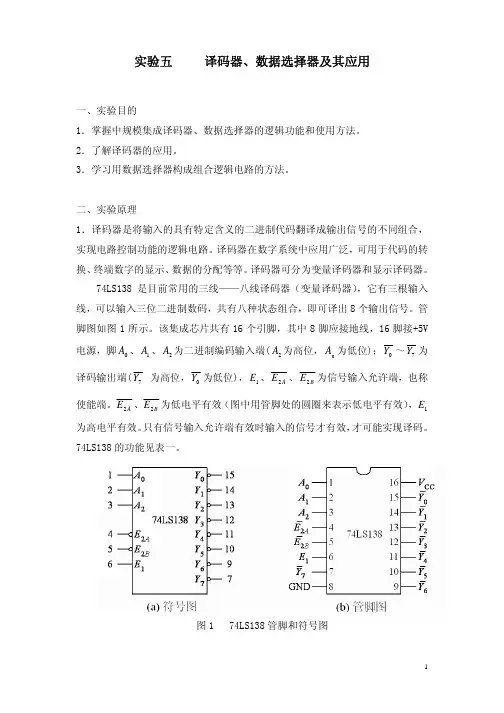

74LS138是目前常用的三线——八线译码器(变量译码器),它有三根输入线,可以输入三位二进制数码,共有八种状态组合,即可译出8个输出信号。

管脚图如图1所示。

该集成芯片共有16个引脚,其中8脚应接地线,16脚接+5V 电源,脚0A 、1A 、2A 为二进制编码输入端(2A 为高位,0A 为低位);0Y ~7Y 为译码输出端(7Y 为高位,0Y 为低位),1E 、A E 2、B E 2为信号输入允许端,也称使能端。

A E 2、B E 2为低电平有效(图中用管脚处的圆圈来表示低电平有效),1E 为高电平有效。

只有信号输入允许端有效时输入的信号才有效,才可能实现译码。

74LS138的功能见表一。

图1 74LS138管脚和符号图表一 74LS138的逻辑功能2.74LS138可用作函数信号发生器,如图2所示,实现的逻辑函数是ABC C B A C B A C B A Z +++= 图23.数据选择器又叫“多路开关”。

数据选择器在选择控制电位的控制下,从几个数据输入中选择一个并将其送到一个公共的输出端。

数据选择器的功能类似一个多掷开关,,如图3所示,图中有四路数据0D ~3D ,通过选择从控制信号1A 、0A 从四路数据中选中某一路数据送至输出端W 。

数据选择器为目前逻辑设计中应用十分广泛的逻辑部件,它有2选1、4选1、8选1、16选1等类别。

8选1数据选择器74LS151:74LS151引脚排列如图3,功能如表二。

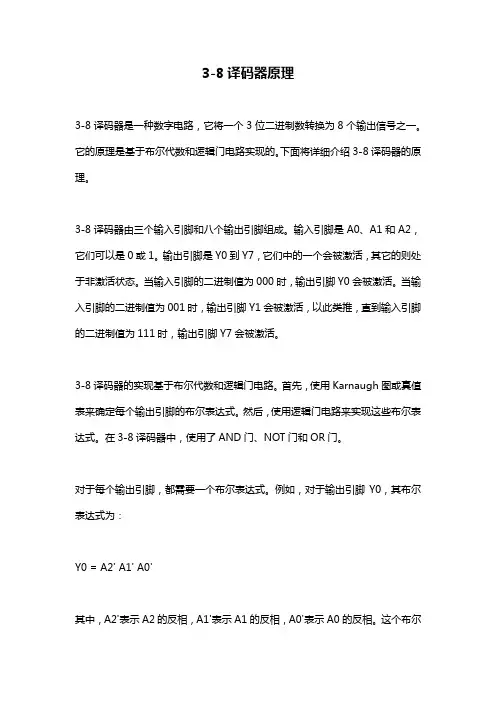

3-8译码器原理3-8译码器是一种数字电路,它将一个3位二进制数转换为8个输出信号之一。

它的原理是基于布尔代数和逻辑门电路实现的。

下面将详细介绍3-8译码器的原理。

3-8译码器由三个输入引脚和八个输出引脚组成。

输入引脚是A0、A1和A2,它们可以是0或1。

输出引脚是Y0到Y7,它们中的一个会被激活,其它的则处于非激活状态。

当输入引脚的二进制值为000时,输出引脚Y0会被激活。

当输入引脚的二进制值为001时,输出引脚Y1会被激活,以此类推,直到输入引脚的二进制值为111时,输出引脚Y7会被激活。

3-8译码器的实现基于布尔代数和逻辑门电路。

首先,使用Karnaugh图或真值表来确定每个输出引脚的布尔表达式。

然后,使用逻辑门电路来实现这些布尔表达式。

在3-8译码器中,使用了AND门、NOT门和OR门。

对于每个输出引脚,都需要一个布尔表达式。

例如,对于输出引脚Y0,其布尔表达式为:Y0 = A2' A1' A0'其中,A2'表示A2的反相,A1'表示A1的反相,A0'表示A0的反相。

这个布尔表达式表示当A2、A1和A0都为0时,Y0会被激活。

对于每个布尔表达式,都需要使用逻辑门电路来实现。

例如,对于Y0的布尔表达式,可以使用三个NOT门和一个AND门来实现。

首先,使用三个NOT门来反相A2、A1和A0,然后将它们的输出连接到一个AND门的输入引脚上。

当A2、A1和A0都为0时,三个NOT门的输出都为1,这样AND门的输出就会变为1,从而激活Y0。

3-8译码器的原理基于布尔代数和逻辑门电路实现。

它可以将一个3位二进制数转换为8个输出信号之一。

对于每个输出引脚,都需要一个布尔表达式和一个逻辑门电路来实现。

3-8译码器在数字电路中有广泛的应用,例如在计算机内存芯片中用于选择特定的存储单元。

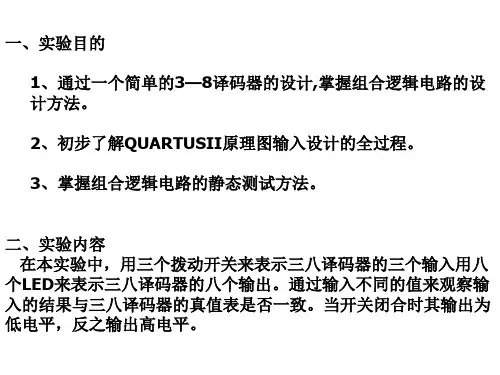

组合电路——3-8译码器的设计一、实验目的1、通过一个简单的3-8译码器的设计,让学生掌握组合逻辑电路的设计方法。

2、熟悉原理图输入及仿真步骤。

3、掌握组合逻辑电路的静态测试方法。

4、初步了解可编程器件设计的全过程。

5、理解硬件描述语言和具体电路的映射关系。

二、硬件要求主芯片Altera EPM7128SLC84-15,时钟。

三、实验内容描述一个3线-8线译码器,使能端为g1、g2a、g2b,地址选择端为a、b、c,输出端为总线y。

四、实验原理三-八译码器三输入,八输出。

当输入信号按二进制方式的表示值为N时,输入端低电平有效输出端从零到八记,标号为N输出端输出低电平表示有信号产生,而其它则为高电平表示无信号产生。

三个输入端能产生的组合状态有八种。

电路符号:3-8译码器器工作原理框图。

如图1所示。

图1五、实验源程序:decoder3_8.vhdlibrary ieee;use ieee.std_logic_1164.all;entity decoder3_8 isport(a,b,c,g1,g2a,g2b:in std_logic;y:out std_logic_vector(7 downto 0));end ;architecture rtl of decoder3_8 issignal dz:std_logic_vector(2 downto 0);begindz<=c&b&a;process(dz,g1,g2a,g2b )beginif (g1='1' and g2a='0' and g2b='0') thencase dz iswhen "000"=>y<="11111110";when "001"=>y<="11111101";when "010"=>y<="11111011";when "011"=>y<="11110111";when "100"=>y<="11101111";when "101"=>y<="11011111";when "110"=>y<="10111111";when "111"=>y<="01111111";when others=>y<="XXXXXXXX"; end case;elsey<="11111111";end if;end process;end;六、波形仿真结果。

38译码器原理38译码器是一种常用的数字电路元件,它在数字系统中扮演着重要的角色。

它的原理和工作方式对于理解数字电路和数字系统的运作原理至关重要。

本文将对38译码器的原理进行详细介绍,帮助读者更好地理解和掌握这一知识点。

首先,让我们来了解一下38译码器的基本结构。

38译码器有三个输入端,分别标记为A、B和C,以及八个输出端,分别标记为Y0到Y7。

在38译码器中,当输入信号为000时,Y0输出为高电平,其余输出为低电平;当输入信号为001时,Y1输出为高电平,其余输出为低电平;以此类推,当输入信号为111时,Y7输出为高电平,其余输出为低电平。

这种工作方式使得38译码器能够将三位二进制输入信号转换为八位输出信号,实现了信号的译码功能。

其次,我们来详细了解38译码器的工作原理。

38译码器内部采用了与门、非门和或门等逻辑门电路。

当输入信号为000时,通过38译码器内部的逻辑门电路运算,最终使得Y0输出为高电平,其余输出为低电平。

当输入信号为001时,内部逻辑门电路运算后,使得Y1输出为高电平,其余输出为低电平。

以此类推,当输入信号为111时,内部逻辑门电路运算后,使得Y7输出为高电平,其余输出为低电平。

这种逻辑门电路的设计和运算方式,实现了38译码器的译码功能。

另外,值得注意的是,38译码器还可以被用作其他数字电路元件的辅助器件。

例如,它可以被用来实现BCD码到七段数码管的转换,从而实现数字的显示功能。

此外,它还可以被用来实现各种数字系统中的地址译码功能,帮助系统实现对不同地址空间的访问和控制。

总之,38译码器是一种重要的数字电路元件,它的原理和工作方式对于理解数字电路和数字系统至关重要。

通过本文的介绍,相信读者对38译码器有了更深入的了解,能够更好地应用和掌握这一知识点。

希望本文能够帮助读者更好地理解38译码器的原理和应用,为进一步学习和研究数字电路和数字系统打下坚实的基础。

摘要EDA技术是指以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。

利用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC版图或PCB版图的整个过程的计算机上自动处理完成。

现在对EDA的概念或范畴用得很宽。

包括在机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域,都有EDA的应用。

目前EDA技术已在各大公司、企事业单位和科研教学部门广泛使用。

例如在飞机制造过程中,从设计、性能测试及特性分析直到飞行模拟,都可能涉及到EDA技术。

本文所指的EDA技术,主要针对电子电路设计、PCB设计和IC设计。

EDA设计可分为系统级、电路级和物理实现级。

关键词译码,VHDL语言,MAX+PLUSⅡAbstractEDA technology refers to the computer for working platform, shirt-sleeve application of electronic technology, computer technology and information processing and intelligent technology to the latest achievements of electronic products, the automatic design.Using EDA tools, electronic stylist can be from concept, algorithm, agreement, etc, begin to design your electronic system a lot work can be finished by computer and electronic products can be from circuit design, performance analysis to design the IC territory or PCB layout the whole process of the computer automatically complete the processing.Now on the concept of using EDA or category very wide. Included in machinery, electronics, communication, aerospace, chemical, mineral, biology, medicine, military and other fields, have EDA applications. Current EDA technology has in big companies, enterprises, institutions and teaching research departments extensive use. For example in the aircraft manufacturing process, from design, performance testing and characteristic analysis until a flight simulator, all may involve EDA technology. Globalization-the EDA technology, mainly in electronic circuit design, PCB design and IC design.EDA can be divided into system level and circuit-level and physical implementation level.Keywords cent, the VHDL language, MAX+PLUS II目录摘要 (I)ABSTRACT (II)目录 .............................................................................................................................................. I II 引言 (1)一EDA技术简介 (2)1.1EDA技术的概念 (2)1.2EDA技术的特点 (2)1.3EDA设计技术的主要内容 (2)1.4EDA设计技术的方法 (2)1.5EDA技术的发展趋势 (3)二硬件语言VHDL描述 (5)2.1VHDL概述 (5)2.2VHDL语言的特点 (5)2.3VHDL语言的基本结构 (6)2.4VHDL语言的设计方法 (6)2.5VHDL语言的设计流程 (6)三3-8译码器 (7)3.1M AX+PLUS II软件介绍 (7)3.23-8译码器的工作原理和VHDL语言程序 (7)3.2.1 3-8译码器的工作原理 (7)3.2.2 3-8译码器的VHDL语言程序 (8)3.33-8译码器的仿真和原理分析 (9)3.3.1 3-8译码器的仿真步骤 (9)3.3.2 3-8译码器的仿真波形 (13)3.3.3 3-8译码器的仿真波形分析 (13)3.3.4 3-8译码器的原理框图 (14)结论 (15)致谢 (16)参考文献 (17)附录A (18)附录B (19)附录C (20)引言随着社会的发展,科学技术也在不断的进步。

实验一 3—8译码逻辑设计(图形法)姓名:赵佳伟学号:1002100449一、实验目的l、学习并掌握MAX+PLUSⅡ10.0 Altera CPLD软件开发平台。

2、通过一个简单的3—8译码器的设计,掌握图形编程的使用方法。

3、掌握组合逻辑电路的静态测试方法。

二、实验步骤(1)进入windows操作系统,打开MAX+PLUSⅡ10.0。

1、启动File/Project Name菜单,输入设计项目的名字。

点Assign/Device菜单,选择器件(本设计全选用EPM7128) 。

见图2.1.1。

2、启动菜单File/New,选择Graphic Editor File,打开原理图编辑器,进行原理图设计输入。

图2.1.1(2)设计的输入1、编辑环境下放置一个器件①在原理图的空白处双击鼠标左键,出现图2.1.2。

②在光标处输入组件名称或用鼠标点取组件,OK即可。

③如果安放相同组件,只要按住Ctrl键,同时用鼠标拖动该组件④图2.1.3为组件安放结果.图2.1.2图2.1.32、在器件的管脚上添加连线在元件引脚附近,鼠标光标自动由箭头变为十字。

按住鼠标左键拖动,即可画出连线如图2.1.4。

图2.1.43、保存原理图单击保存按钮,对于第一次输入的新原理图,出现类似文件管理器的图框,选择合适的目录和名称保存刚才输入的原理图 2.1.4,原理图的扩展名.GDF,本实验中取名为:EDA.GDF。

(3)原理图编译启动MAX+PLUS II\COMPILER菜单,按START开始编译,生成.SOF和.POF等文件,以便硬件下载和编程时调用,同时生成.RPT文件,如图2.1.5。

图2.1.5(4)仿真1、创建波形文件:①首先,将设计指定为当前项目。

②创建一个波形文件。

选择菜单MAX+PLUSⅡ\Waveform Editor,打开仿真工具Waveform Editor,或选择新建一个Waveform Editor文件,将创建一个新的无标题波形文件,如图2.1.6所示:图2.1.6③储存波形文件。