一种新型的抽取滤波器设计

- 格式:pdf

- 大小:303.81 KB

- 文档页数:3

低功耗Delta-Sigma ADC抽取滤波器的设计与实现的开题报告一、选题背景与意义Delta-Sigma ADC是一种高精度、低功耗的模数转换器,广泛应用于信号采集和处理、电力电子、无线通信等领域。

其中,抽取滤波器是Delta-Sigma ADC的核心部件之一,用于对模数转换器输出的无穷序列进行数字滤波和抽取操作,得到有限序列的数字信号。

因此,对Delta-Sigma ADC抽取滤波器的设计和实现具有重要的理论和应用价值。

二、研究内容和研究方法本文以Delta-Sigma ADC抽取滤波器的设计和实现为研究目标,包括以下内容:1. Delta-Sigma ADC的原理和应用,介绍Delta-Sigma调制器、数字滤波器等基本原理。

2. 抽取滤波器的设计和实现,包括数字信号处理中的抽取和滤波操作、滤波器结构和参数的设计和优化等方面。

3. 模拟电路和数字电路的设计和实现,包括滤波器的模拟电路、数字电路、系统级集成等方面。

4. 系统仿真和测试验证,通过理论分析、MATLAB仿真和硬件实现等方式对抽取滤波器的性能进行分析和测试。

研究方法主要包括文献综合、数学分析、MATLAB仿真、软件编程和电路实现等技术手段。

三、研究进度目前,已经完成Delta-Sigma ADC的理论研究和抽取滤波器的设计方案,初步确定了数字电路和模拟电路的方案设计。

下一步,将进行MATLAB仿真和电路模拟验证,并进行实际系统测试。

四、预期研究成果本研究的预期成果包括:1. 抽取滤波器的设计方案和实现流程,提高Delta-Sigma ADC抽取滤波器的设计和实现水平。

2. 系统仿真和测试验证结果,提高Delta-Sigma ADC抽取滤波器的性能和应用范围。

3. 发表相关论文及优秀学术著作,提高科研水平。

五、研究难点和风险控制Delta-Sigma ADC抽取滤波器的设计和实现具有一定难度,其风险主要体现在以下方面:1. 短时间内难以完成全部设计和实现工作。

FPGA的FIR抽取滤波器设计用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器,使FPGA在数字信号处理方面有了长足的进步。

本文介绍了一种采用Xilinx公司的XC2V1000实现FIR抽取滤波器的设计方法。

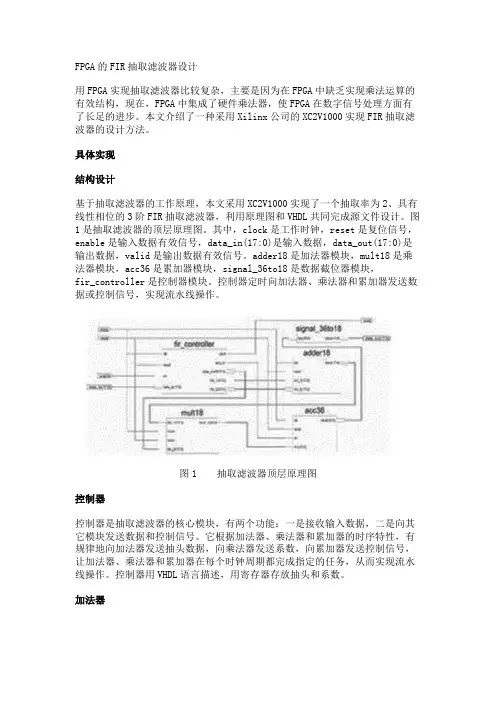

具体实现结构设计基于抽取滤波器的工作原理,本文采用XC2V1000实现了一个抽取率为2、具有线性相位的3阶FIR抽取滤波器,利用原理图和VHDL共同完成源文件设计。

图1是抽取滤波器的顶层原理图。

其中,clock是工作时钟,reset是复位信号,enable是输入数据有效信号,data_in(17:0)是输入数据,data_out(17:0)是输出数据,valid是输出数据有效信号。

adder18是加法器模块,mult18是乘法器模块,acc36是累加器模块,signal_36to18是数据截位器模块,fir_controller是控制器模块。

控制器定时向加法器、乘法器和累加器发送数据或控制信号,实现流水线操作。

图1 抽取滤波器顶层原理图控制器控制器是抽取滤波器的核心模块,有两个功能:一是接收输入数据,二是向其它模块发送数据和控制信号。

它根据加法器、乘法器和累加器的时序特性,有规律地向加法器发送抽头数据,向乘法器发送系数,向累加器发送控制信号,让加法器、乘法器和累加器在每个时钟周期都完成指定的任务,从而实现流水线操作。

控制器用VHDL语言描述,用寄存器存放抽头和系数。

加法器加法器的输入和输出都是18 bit,用VHDL语言描述实现。

它有两个工作时钟的延迟,在输入数据准备好的情况下,第一个时钟得出相加结果,第二个时钟把相加结果锁存输出。

乘法器乘法器为18 bit输入,36bit输出,用库元件MULT18X18S和36 bit锁存器实现。

MULT18X18S是XC2V1000自带的18×18bit硬件乘法器,单个时钟就可完成乘法运算。

Sigma-Delta ADC中抽取滤波器的设计与实现的开题报告一、选题背景及研究意义Sigma-Delta ADC抽取滤波器是Sigma-Delta调制器中最为关键的一个组成部分,它对ADC整个系统性能的影响非常大。

抽取滤波器的作用是减小Sigma-Delta ADC的过采样率,缩小ADC转换器的宽带,从而减小数字滤波器的计算量,提高Sigma-Delta ADC抽取率和工作效率。

抽取滤波器设计精度要求高,设计难度大,对滤波器设计者的理论水平有着很高的要求。

因此,设计一种高效、高性能的Sigma-Delta ADC抽取滤波器是当前研究热点之一。

本篇开题报告旨在探索Sigma-Delta ADC抽取滤波器的设计与实现,为其优化提供理论参考和技术支持。

二、研究内容和方法本研究的内容主要包括:1. 研究Sigma-Delta ADC抽取滤波器的主要设计原理和特点,分析其难点和瓶颈;2. 探索Sigma-Delta ADC抽取滤波器设计的各种算法和方法,比较其优缺点,实现对各种算法的评估、验证和对比;3. 设计一种符合IFI6UHPC架构的Sigma-Delta ADC抽取滤波器电路,实现其关键算法和方法功能;4. 对设计的Sigma-Delta ADC抽取滤波器电路进行实验测试,验证其设计的正确性和性能优越性;5. 最后,对设计过程和实验结果进行详细分析和总结,并提出改进和优化方案。

本研究的方法主要包括:1. 文献资料研究法:查阅与Sigma-Delta ADC抽取滤波器相关的文献资料,了解其发展历程、设计思路和实现细节;2. 算法研究法:针对Sigma-Delta ADC抽取滤波器的各种算法和方法,比较其优缺点,实现对各种算法的评估、验证和对比;3. 仿真模拟法:利用计算机软件对设计的Sigma-Delta ADC抽取滤波器电路进行仿真模拟,进行性能分析和优化调试;4. 实验验证法:采用硬件电路搭建方式对设计的Sigma-Delta ADC抽取滤波器电路进行实验验证,验证其设计的正确性和性能优越性。

改进型CIC抽取滤波器设计与FPGA实现张杰;戴宇杰;张小兴;吕英杰【摘要】为了改善级联积分梳状(CIC)滤波器通带不平和阻带衰减不足的缺点,给出一种改进型CIC滤波器.该滤波器在采用COSINE滤波器提高阻带特性的基础上,级联了一个SINE滤波器,补偿了其通带衰减.硬件实现时,采用新的多相分解方法结合非递归结构,不仅大大减少了存储单元数量,还使电路结构更加规则.经仿真和FPGA 验证,改进型CIC滤波嚣使用较少硬件,实现了阻带衰减100.3 dB,通带衰减仅为0.000 1 dB.【期刊名称】《现代电子技术》【年(卷),期】2009(032)010【总页数】3页(P22-24)【关键词】CIC抽取滤波器;COSINE滤波器;SINE滤波器;设计优化;FPGA【作者】张杰;戴宇杰;张小兴;吕英杰【作者单位】南开大学,南开大学微电子所,天津,300071;南开大学,南开大学微电子所,天津,300071;南开大学,南开大学微电子所,天津,300071;南开大学,南开大学微电子所,天津,300071【正文语种】中文【中图分类】TP368.1抽取滤波器是Σ-Δ模/数转换器中的重要组成部分,积分梳状滤波器经常作为第一级滤波器,用以实现抽取和低通滤波[1]。

其优点是实现时不需要乘法器电路,且系数为整数,不需要电路来存储系数,同时通过置换抽取可以使部分电路工作在较低频率,与相同滤波性能的其他FIR滤波器相比,节约了硬件开销[2]。

经过仿真,抽取率为32的一阶积分梳状滤波器第一旁瓣相对于主瓣的衰减最大约为15 dB,这样的阻带衰减根本达不到实用滤波器的设计要求。

为了改变滤波性能,一般采用级联积分梳状滤波器(CIC)[3]。

但经过CIC降频滤波系统降频后会产生信号混叠现象,并且主瓣曲线不平,需要用新的算法或新结构来修正改善这些特性。

1 CIC抽取滤波器原理经典的抽取滤波器为Hogenauer [3]CIC滤波器,其传输函数表达式为:(1)式中:参数M为降频因子,决定了CIC的通带大小;K为滤波器的阶数,对阻带衰减起到加深作用。

FIR抽取滤波器的工作原理FIR(有限脉冲响应)滤波器是一种数字滤波器,常用于信号处理和数字通信领域。

它的工作原理基于对输入信号的离散时间样本进行线性加权求和的方式。

FIR滤波器的工作原理可以分为三个主要步骤:采样、加权和求和。

1.采样:输入信号经过模数转换器(A/D转换器)转换为数字形式,以离散时间点的方式进行采样。

这意味着信号在时间上是离散的,并以一定的时间间隔采集样本。

2.加权:每个采样点都乘以一个系数,称为滤波器的冲激响应。

冲激响应是一个数字序列,表示了滤波器的频率响应特性。

它决定了滤波器如何对不同频率的信号进行加权。

冲激响应的长度决定了滤波器的阶数,即影响滤波器频率响应的能力。

3.求和:加权后的采样点按顺序相加,得到输出信号。

输出信号是滤波器对输入信号进行处理后得到的结果。

FIR滤波器的特点是其脉冲响应是有限长度的,因此它不具有反馈回路。

这意味着它的稳定性得到了保证,并且不会引入频率抖动或波动。

此外,FIR滤波器的相应通带和停带特性可以精确设计,其幅频响应在通带内的波动较小,同时对停带内的频率具有较高的抑制能力。

设计FIR滤波器的关键是确定滤波器的冲激响应。

常见的设计方法有窗函数法、频率采样法和最小平方误差法等。

窗函数法通过在理想传递函数和实际传递函数之间引入窗函数来设计滤波器。

频率采样法在设计过程中提前选择一组所需的频率样本点,然后通过这些样本点确定滤波器的冲激响应。

最小平方误差法是基于最小化输入信号和期望响应之间的均方误差来设计滤波器。

FIR滤波器的应用广泛,例如语音处理、图像处理、音频处理和无线通信等领域。

它可以实现低通、高通、带通和带阻等多种滤波器类型,具有较好的抗混叠性能和相位线性特性,能够有效地去除信号中的干扰和噪声。

总结起来,FIR滤波器的工作原理是将输入信号离散采样后,对每个采样点乘以滤波器的冲激响应系数,并将这些加权后的采样点求和,得到输出信号。

滤波器的冲激响应可以通过不同的设计方法获得,以满足特定的频率响应要求。