项目二一位十进制加法计算器的逻辑电路设计与制作共100页文档

- 格式:ppt

- 大小:7.06 MB

- 文档页数:50

课程设计(论文)任务书电气学院电力系统专业12(1 )班一、课程设计(论文)题目:十进制加法计算器设计二、课程设计(论文)工作自2015年1 月12 日起至2015 年1月16 日止。

三、课程设计(论文) 地点: 电气学院机房10-303四、课程设计(论文)容要求:1.课程设计的目的(1)综合运用单片机原理及应用相关课程的理论知识和实际应用知识,进行单片机应用系统电路及程序设计,从而使这些知识得到进一步的巩固,加深和发展;(2)熟悉和掌握单片机控制系统的设计方法,汇编语言程序设计及proteus 软件的使用;(3)通过查阅图书资料、以及书写课程设计报告可提高综合应用设计能力,培养独立分析问题和解决问题的能力。

2.课程设计的容及任务课程设计容:利用单片机及一些外围电路设计一个简易的十进制加法计算器,硬件电路设计大概主要包括:键盘电路,显示电路以及复位电路和晶振电路。

软件方面的设计主要包括:LED显示程序设计、数值送显示缓存程序设计、读键子程序设计、运算程序的设计。

课程设计任务:设计一个键盘显示装置,键盘上除了定义0~9共10个数字键外,还要相应的功能健,其它键不定义无响应。

利用此系统可分别输入十进制被加数和加数,实现两个数相加并将结果以十进制形式显示出来。

3.课程设计说明书编写要求(1)设计说明书用A4纸统一规格,论述清晰,字迹端正,应用资料应说明出处。

(2)说明书容应包括(装订次序):题目、目录、正文、设计总结、参考文献等。

应阐述整个设计容,要重点突出,图文并茂,文字通畅。

(3)报告容应包括方案分析;方案对比;整体设计论述;硬件设计(电路接线,元器件说明,硬件资源分配);软件设计(软件流程,编程思想,程序注释,)调试结果;收获与体会;附录(设计代码放在附录部分,必须加上合理的注释)(4)学生签名:2015年1月16 日课程设计(论文)评审意见(1)总体方案的选择是否正确;正确()、较正确()、基本正确()(2)程序仿真能满足基本要求;满足()、较满足()、基本满足()(3)设计功能是否完善;完善()、较完善()、基本完善()(4)元器件选择是否合理;合理()、较合理()、基本合理()(5)动手实践能力;强()、较强()、一般()(6)学习态度;好()、良好()、一般()(7)基础知识掌握程度;好()、良好()、一般()(8)回答问题是否正确;正确()、较正确()、基本正确()、不正确()(9)程序代码是否具有创新性;全部()、部分()、无()(10)书写整洁、条理清楚、格式规;规()、较规()、一般()总评成绩优()、良()、中()、及格()、不及格()评阅人:年月日摘要随着社会科技的发展和进步,计算器因其功能强大而早已成为人们日常生活中必不可少的工具,最简单的计算器就能实现简单的加减乘除运算,这让人们免去了复杂的计算过程,大大提高了工作效率。

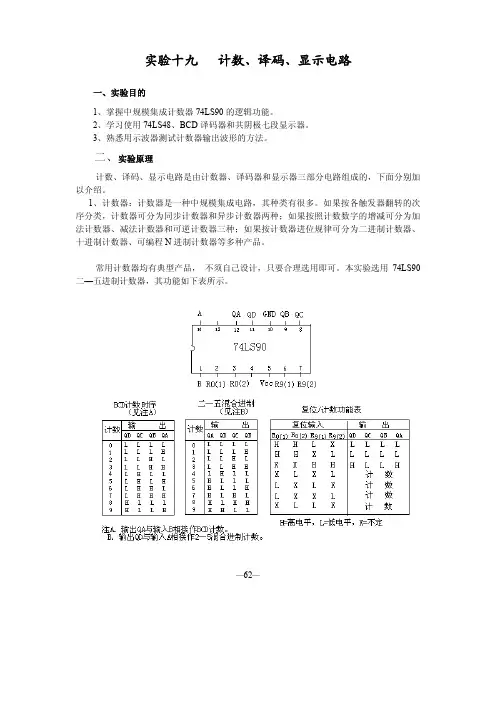

实验十九 计数、译码、显示电路一、实验目的1、掌握中规模集成计数器74LS90的逻辑功能。

2、学习使用74LS48、BCD译码器和共阴极七段显示器。

3、熟悉用示波器测试计数器输出波形的方法。

二、 实验原理计数、译码、显示电路是由计数器、译码器和显示器三部分电路组成的,下面分别加以介绍。

1、计数器:计数器是一种中规模集成电路,其种类有很多。

如果按各触发器翻转的次序分类,计数器可分为同步计数器和异步计数器两种;如果按照计数数字的增减可分为加法计数器、减法计数器和可逆计数器三种;如果按计数器进位规律可分为二进制计数器、十进制计数器、可编程N进制计数器等多种产品。

常用计数器均有典型产品,不须自己设计,只要合理选用即可。

本实验选用74LS90二—五进制计数器,其功能如下表所示。

6263(1) R 0(1)和R 0(2)为直接复位端,R 9(1)和R 9(2)为直接置位端,可以预置数字“9”(Q D = Q A = 1,Q B = Q C = 0)。

(2) A 为二分频计数器的输入,Q A 的输出频率为CP A 的1/2。

B 为五进制计数器的输入,把Q A 输出作为五进制计数器B 的输入,即构成8421BCD 码十进制计数器。

2、 译码器:这里所说的译码器是将二进制数译成十进制数的器件。

我们选用的74LS48是BCD 码七段译码器兼驱动器。

其外引线排列图和功能表如下所示。

1234567891011121314GNDVCC 74LS48B1615CLTBI/RBORBIDAgabcdef十进制数 或功能输 入LT RBI D C B A 0123H H H H H X X X L L L L L L L H L L H L L L H H BI/RBO H H H H 输 出a b c d e f g H H H H H H L L H H L L L L H H L H H L H H H H H L L H 字 型注4567H H H H X X X X L H L L L H L H L H H L L H H H H H H H L H H L L H H H L H H L H H L L H H H H H H H H L L L L H H H X X X H L L L H L L H H L H L H H H H H H H H H H H H H L L H H L L L H H L H L L H H L L H 891011H X H L H H H H H H X X X H H L L H H L H H H H L H H H L H L L L H H H L L H L H H L L L H H H H L L L L L L L 12131415H X H H H H H 1BI RBI LTX H LX XL X X X X X X X XL L L L L L HL L L L L L L L L L L L L L H H H H H H H2 34(1) 要求输出数字0~15时,“灭灯输入”(BI )必须开路或保持高电平。

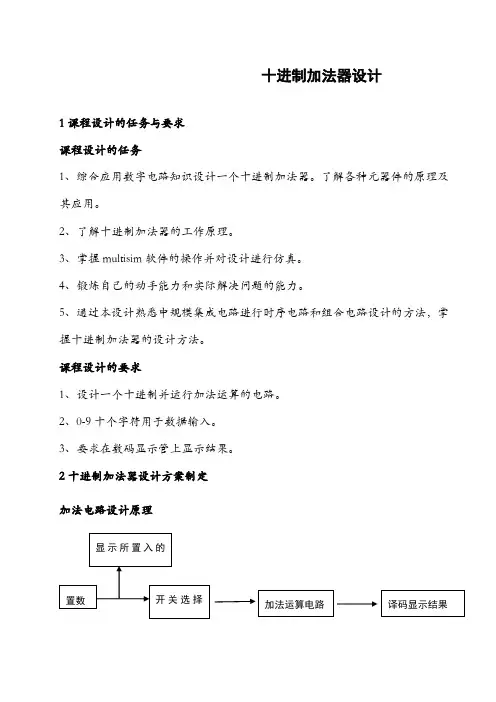

十进制加法器设计1课程设计的任务与要求 课程设计的任务1、综合应用数字电路知识设计一个十进制加法器。

了解各种元器件的原理及其应用。

2、了解十进制加法器的工作原理。

3、掌握multisim 软件的操作并对设计进行仿真。

4、锻炼自己的动手能力和实际解决问题的能力。

5、通过本设计熟悉中规模集成电路进行时序电路和组合电路设计的方法,掌握十进制加法器的设计方法。

课程设计的要求1、设计一个十进制并运行加法运算的电路。

2、0-9十个字符用于数据输入。

3、要求在数码显示管上显示结果。

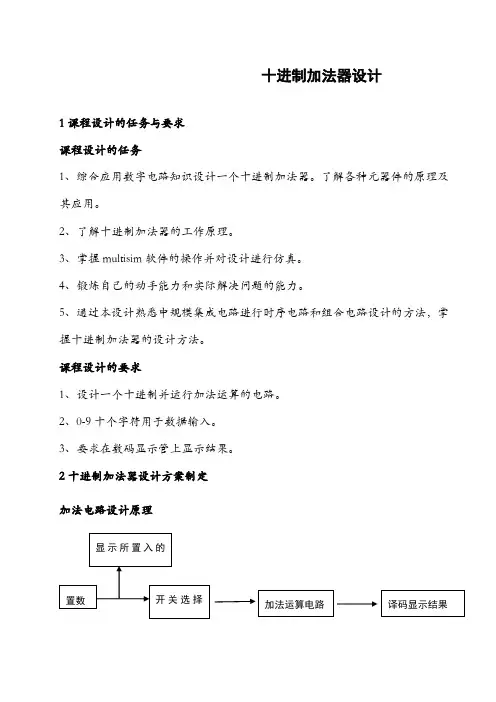

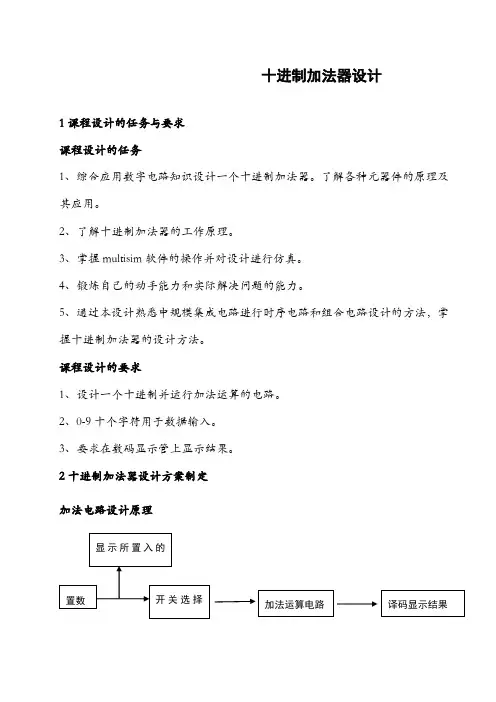

2十进制加法器设计方案制定 加法电路设计原理图1加法运算原理框图如图1所示第一步置入两个四位二进制数。

例如(1001)2,(0011)2和(0101)2,(1000),同时在两个七段译码显示器上显示出对应的十进制数9,3和5,8。

2第二步将置入的数运用加法电路进行加法运算。

第三步前面所得结果通过另外两个七段译码器显示。

即:加法运算方式,则(1000)2+(0110)2=(1110)2 十进制8+6=14 并在七段译码显示出14。

运算方案通过开关S1——S8接不同的高低电平来控制输入端所置的两个一位十进制数,译码显示器U8和U9分别显示所置入的两个数。

数A直接置入四位超前进位加法器74LS283的A4——A1端,74LS283的B4——B1端接四个2输入异或门。

四个2输入异或门的一输入端同时接到开关S1上,另一输入端分别接开关S5——S8,通过开关S5——S8控制数B的输入,通过加法器74LS283完成两个数A和B的相加。

由于译码显示器只能显示0——9,所以当A+B>9时不能显示,我们在此用另一片芯片74LS283完成二进制码与8421BCD码的转换,即S>9(1001)2时加上3(0011)2,产生的进位信号送入译码器U10来显示结果的十位,U11显示结果的个位。

3十进制加法器电路设计加法电路的实现用两片4位全加器74LS283和门电路设计一位8421BCD码加法器。

十进制加法器设计1课程设计的任务与要求 课程设计的任务1、综合应用数字电路知识设计一个十进制加法器。

了解各种元器件的原理及其应用。

2、了解十进制加法器的工作原理。

3、掌握multisim 软件的操作并对设计进行仿真。

4、锻炼自己的动手能力和实际解决问题的能力。

5、通过本设计熟悉中规模集成电路进行时序电路和组合电路设计的方法,掌握十进制加法器的设计方法。

课程设计的要求1、设计一个十进制并运行加法运算的电路。

2、0-9十个字符用于数据输入。

3、要求在数码显示管上显示结果。

2十进制加法器设计方案制定 加法电路设计原理图1加法运算原理框图如图1所示第一步置入两个四位二进制数。

例如(1001)2,(0011)2和(0101)2,(1000),同时在两个七段译码显示器上显示出对应的十进制数9,3和5,8。

2第二步将置入的数运用加法电路进行加法运算。

第三步前面所得结果通过另外两个七段译码器显示。

即:加法运算方式,则(1000)2+(0110)2=(1110)2 十进制8+6=14 并在七段译码显示出14。

运算方案通过开关S1——S8接不同的高低电平来控制输入端所置的两个一位十进制数,译码显示器U8和U9分别显示所置入的两个数。

数A直接置入四位超前进位加法器74LS283的A4——A1端,74LS283的B4——B1端接四个2输入异或门。

四个2输入异或门的一输入端同时接到开关S1上,另一输入端分别接开关S5——S8,通过开关S5——S8控制数B的输入,通过加法器74LS283完成两个数A和B的相加。

由于译码显示器只能显示0——9,所以当A+B>9时不能显示,我们在此用另一片芯片74LS283完成二进制码与8421BCD码的转换,即S>9(1001)2时加上3(0011)2,产生的进位信号送入译码器U10来显示结果的十位,U11显示结果的个位。

3十进制加法器电路设计加法电路的实现用两片4位全加器74LS283和门电路设计一位8421BCD码加法器。

十进制加法器设计1课程设计的任务与要求 课程设计的任务1、综合应用数字电路知识设计一个十进制加法器。

了解各种元器件的原理及其应用。

2、了解十进制加法器的工作原理。

3、掌握multisim 软件的操作并对设计进行仿真。

4、锻炼自己的动手能力和实际解决问题的能力。

5、通过本设计熟悉中规模集成电路进行时序电路和组合电路设计的方法,掌握十进制加法器的设计方法。

课程设计的要求1、设计一个十进制并运行加法运算的电路。

2、0-9十个字符用于数据输入。

3、要求在数码显示管上显示结果。

2十进制加法器设计方案制定 加法电路设计原理图1加法运算原理框图如图1所示第一步置入两个四位二进制数。

例如(1001)2,(0011)2和(0101)2,(1000),同时在两个七段译码显示器上显示出对应的十进制数9,3和5,8。

2第二步将置入的数运用加法电路进行加法运算。

第三步前面所得结果通过另外两个七段译码器显示。

即:加法运算方式,则(1000)2+(0110)2=(1110)2 十进制8+6=14 并在七段译码显示出14。

运算方案通过开关S1——S8接不同的高低电平来控制输入端所置的两个一位十进制数,译码显示器U8和U9分别显示所置入的两个数。

数A直接置入四位超前进位加法器74LS283的A4——A1端,74LS283的B4——B1端接四个2输入异或门。

四个2输入异或门的一输入端同时接到开关S1上,另一输入端分别接开关S5——S8,通过开关S5——S8控制数B的输入,通过加法器74LS283完成两个数A和B的相加。

由于译码显示器只能显示0——9,所以当A+B>9时不能显示,我们在此用另一片芯片74LS283完成二进制码与8421BCD码的转换,即S>9(1001)2时加上3(0011)2,产生的进位信号送入译码器U10来显示结果的十位,U11显示结果的个位。

3十进制加法器电路设计加法电路的实现用两片4位全加器74LS283和门电路设计一位8421BCD码加法器。