11-乘法器

- 格式:pdf

- 大小:485.92 KB

- 文档页数:54

一、概述利用四位二进制寄存器、全加器以及D触发器等元器件,实现四位二进制乘法器的控制部分和乘法的实现部分。

成法是加法的简便运算乘法运算只能通过加法运算以及移位运算来实现。

在控制端用四个触发器产生四个控制信号来控制实现的加法移位功能,实现端在控制端信号作用下依次执行置零、加法、移位和循环操作。

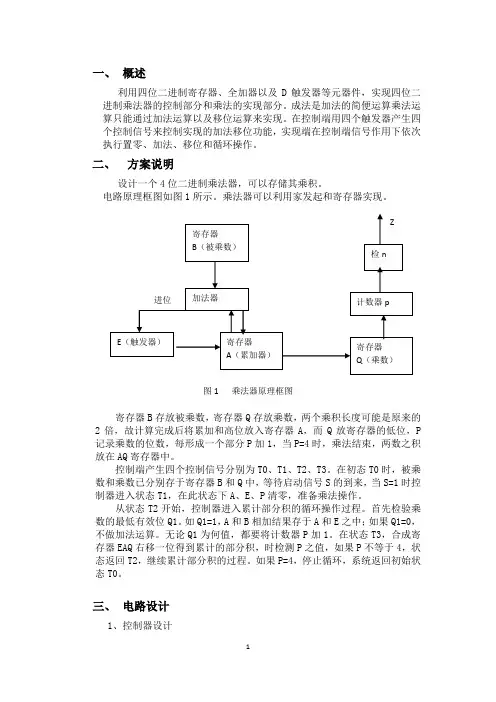

二、方案说明设计一个4位二进制乘法器,可以存储其乘积。

电路原理框图如图1所示。

乘法器可以利用家发起和寄存器实现。

图1 乘法器原理框图寄存器B存放被乘数,寄存器Q存放乘数,两个乘积长度可能是原来的2倍,故计算完成后将累加和高位放入寄存器A,而Q放寄存器的低位,P 记录乘数的位数,每形成一个部分P加1,当P=4时,乘法结束,两数之积放在AQ寄存器中。

控制端产生四个控制信号分别为T0、T1、T2、T3。

在初态T0时,被乘数和乘数已分别存于寄存器B和Q中,等待启动信号S的到来,当S=1时控制器进入状态T1,在此状态下A、E、P清零,准备乘法操作。

从状态T2开始,控制器进入累计部分积的循环操作过程。

首先检验乘数的最低有效位Q1。

如Q1=1,A和B相加结果存于A和E之中;如果Q1=0,不做加法运算。

无论Q1为何值,都要将计数器P加1。

在状态T3,合成寄存器EAQ右移一位得到累计的部分积,时检测P之值,如果P不等于4,状态返回T2,继续累计部分积的过程。

如果P=4,停止循环,系统返回初始状态T0。

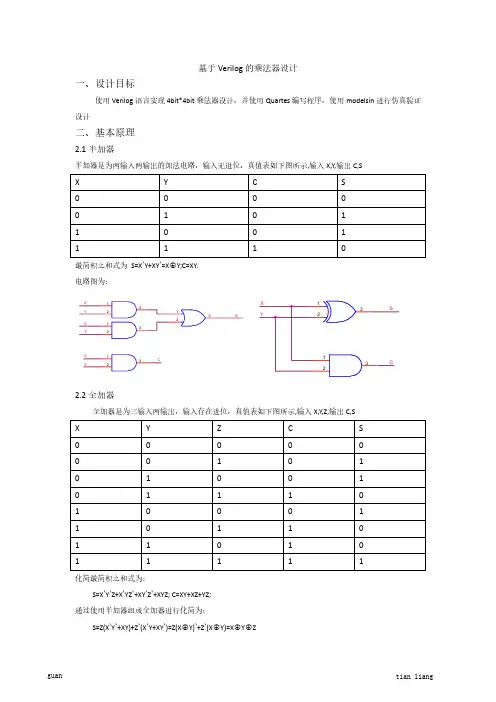

三、电路设计1、控制器设计根据图2所示的ASM图表,可以设计二进制乘法器的控制器。

图2 二进制乘法器ASM图表四个D触发器的驱动方程为:D0=T0S’+T3Z=((T0S’)’·(T3Z)’)’D1=T0S=((T0S)’)’D2=T1+T3Z’=(T1’·(T3Z’)’)’D3=T2控制器仿真电路如图2所示。

控制器中S为启动信号,高电平有效,系统开始工作时应使T0=1,T1=T2=T3=0,故图中设置了Reset信号(负脉冲)图2 二进制乘法器的控制逻辑图2. 二进制乘法器数据处理器(1) A寄存器A寄存器具有并入、移位、同步清0和保持功能。

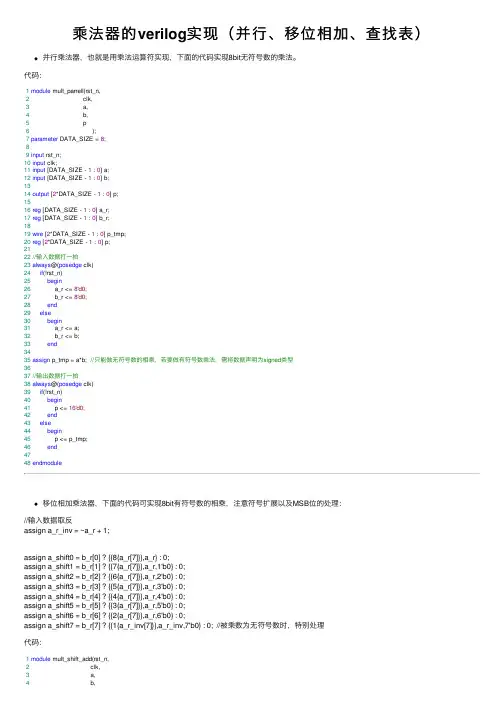

乘法器的verilog实现(并⾏、移位相加、查找表)并⾏乘法器,也就是⽤乘法运算符实现,下⾯的代码实现8bit⽆符号数的乘法。

代码:1module mult_parrell(rst_n,2 clk,3 a,4 b,5 p6 );7parameter DATA_SIZE = 8;89input rst_n;10input clk;11input [DATA_SIZE - 1 : 0] a;12input [DATA_SIZE - 1 : 0] b;1314output [2*DATA_SIZE - 1 : 0] p;1516reg [DATA_SIZE - 1 : 0] a_r;17reg [DATA_SIZE - 1 : 0] b_r;1819wire [2*DATA_SIZE - 1 : 0] p_tmp;20reg [2*DATA_SIZE - 1 : 0] p;2122//输⼊数据打⼀拍23always@(posedge clk)24if(!rst_n)25begin26 a_r <= 8'd0;27 b_r <= 8'd0;28end29else30begin31 a_r <= a;32 b_r <= b;33end3435assign p_tmp = a*b; //只能做⽆符号数的相乘,若要做有符号数乘法,需将数据声明为signed类型3637//输出数据打⼀拍38always@(posedge clk)39if(!rst_n)40begin41 p <= 16'd0;42end43else44begin45 p <= p_tmp;46end4748endmodule移位相加乘法器,下⾯的代码可实现8bit有符号数的相乘,注意符号扩展以及MSB位的处理://输⼊数据取反assign a_r_inv = ~a_r + 1;assign a_shift0 = b_r[0] ? {{8{a_r[7]}},a_r} : 0;assign a_shift1 = b_r[1] ? {{7{a_r[7]}},a_r,1'b0} : 0;assign a_shift2 = b_r[2] ? {{6{a_r[7]}},a_r,2'b0} : 0;assign a_shift3 = b_r[3] ? {{5{a_r[7]}},a_r,3'b0} : 0;assign a_shift4 = b_r[4] ? {{4{a_r[7]}},a_r,4'b0} : 0;assign a_shift5 = b_r[5] ? {{3{a_r[7]}},a_r,5'b0} : 0;assign a_shift6 = b_r[6] ? {{2{a_r[7]}},a_r,6'b0} : 0;assign a_shift7 = b_r[7] ? {{1{a_r_inv[7]}},a_r_inv,7'b0} : 0; //被乘数为⽆符号数时,特别处理代码:1module mult_shift_add(rst_n,2 clk,3 a,4 b,5 p6 );7parameter DATA_SIZE = 8;89input rst_n;10input clk;11input [DATA_SIZE - 1 : 0] a;12input [DATA_SIZE - 1 : 0] b;1314output [2*DATA_SIZE - 2 : 0] p;1516//输⼊数据打⼀个时钟节拍17reg [DATA_SIZE - 1 : 0] a_r;18reg [DATA_SIZE - 1 : 0] b_r;1920//输⼊数据取反21wire [DATA_SIZE - 1 : 0] a_r_inv;2223//输⼊数据移位24wire [2*DATA_SIZE - 1 : 0] a_shift0;25wire [2*DATA_SIZE - 1 : 0] a_shift1;26wire [2*DATA_SIZE - 1 : 0] a_shift2;27wire [2*DATA_SIZE - 1 : 0] a_shift3;28wire [2*DATA_SIZE - 1 : 0] a_shift4;29wire [2*DATA_SIZE - 1 : 0] a_shift5;30wire [2*DATA_SIZE - 1 : 0] a_shift6;31wire [2*DATA_SIZE - 1 : 0] a_shift7;3233//输出数据打⼀个时钟节拍34wire [2*DATA_SIZE - 1 : 0] p_tmp;35reg [2*DATA_SIZE - 1 : 0] p;3637//输⼊数据打⼀个时钟节拍38always@(posedge clk)39if(!rst_n)40begin41 a_r <= 8'd0;42 b_r <= 8'd0;43end44else45begin46 a_r <= a;47 b_r <= b;48end49//输⼊数据取反50assign a_r_inv = ~a_r + 1;5152//输⼊数据移位,注意符号扩展,不仅仅是最⾼位扩展53//对每⼀个bit都需扩展54assign a_shift0 = b_r[0] ? {{8{a_r[7]}},a_r} : 0;55assign a_shift1 = b_r[1] ? {{7{a_r[7]}},a_r,1'b0} : 0;56assign a_shift2 = b_r[2] ? {{6{a_r[7]}},a_r,2'b0} : 0;57assign a_shift3 = b_r[3] ? {{5{a_r[7]}},a_r,3'b0} : 0;58assign a_shift4 = b_r[4] ? {{4{a_r[7]}},a_r,4'b0} : 0;59assign a_shift5 = b_r[5] ? {{3{a_r[7]}},a_r,5'b0} : 0;60assign a_shift6 = b_r[6] ? {{2{a_r[7]}},a_r,6'b0} : 0;61assign a_shift7 = b_r[7] ? {{1{a_r_inv[7]}},a_r_inv,7'b0} : 0; //被乘数为⽆符号数时,特别处理6263assign p_tmp = a_shift0 + a_shift1 + a_shift2 + a_shift3 + a_shift464 + a_shift5 + a_shift6 + a_shift7;6566always@(posedge clk)67if(!rst_n)68begin69//p <= 16'd0;70 p <= 15'd0;71end72else73begin74//p <= p_tmp[15:0];75 p <= p_tmp[14:0];76end7778endmoduletestbench:1module mult_shift_add_tb;23// Inputs4reg rst_n;5reg clk;6reg [7:0] a;7reg [7:0] b;89// Outputs10wire [14:0] p;1112// Instantiate the Unit Under Test (UUT)13 mult_shift_add uut (14 .rst_n(rst_n),15 .clk(clk),16 .a(a),17 .b(b),18 .p(p)19 );2021parameter CLK_PERIOD = 10;2223initial begin24 rst_n = 0;25 clk = 0;2627 #100;28 rst_n = 1;29end3031always #(CLK_PERIOD/2) clk = ~clk;3233always@(posedge clk)34if(!rst_n)35begin36 a = 8'd0;37 b = 8'd0;38end39else40begin41 a = a + 1;42 b = b - 1;43end4445endmoduleISIM仿真结果:移位相加乘法器树:将assign p_tmp = a_shift0 + a_shift1 + a_shift2 + a_shift3 + a_shift4 + a_shift5 + a_shift6 + a_shift7;换为:assign sum_01 = a_shift0 + a_shift1;assign sum_23 = a_shift2 + a_shift3;assign sum_45 = a_shift4 + a_shift5;assign sum_67 = a_shift6 + a_shift7;assign sum_0123 = sum_01 + sum_23;assign sum_4567 = sum_45 + sum_67;assign p_tmp = sum_0123 + sum_4567;就成为乘法器树。

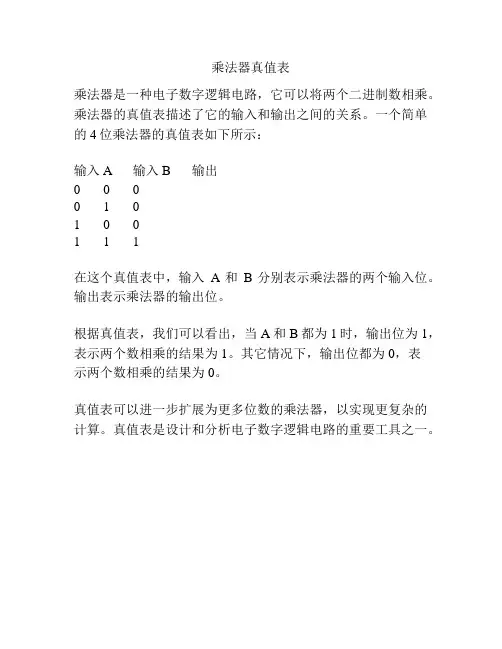

乘法器真值表

乘法器是一种电子数字逻辑电路,它可以将两个二进制数相乘。

乘法器的真值表描述了它的输入和输出之间的关系。

一个简单的4位乘法器的真值表如下所示:

输入A 输入B 输出

0 0 0

0 1 0

1 0 0

1 1 1

在这个真值表中,输入A和B分别表示乘法器的两个输入位。

输出表示乘法器的输出位。

根据真值表,我们可以看出,当A和B都为1时,输出位为1,表示两个数相乘的结果为1。

其它情况下,输出位都为0,表

示两个数相乘的结果为0。

真值表可以进一步扩展为更多位数的乘法器,以实现更复杂的计算。

真值表是设计和分析电子数字逻辑电路的重要工具之一。

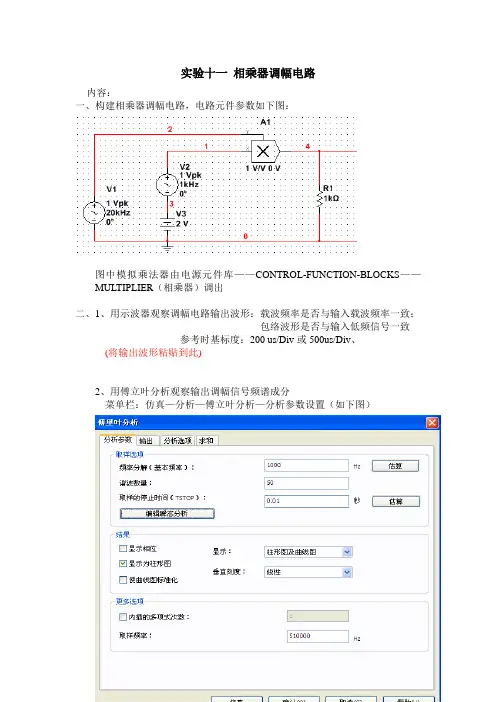

实验十一相乘器调幅电路

内容:

一、构建相乘器调幅电路,电路元件参数如下图:

图中模拟乘法器由电源元件库——CONTROL-FUNCTION-BLOCKS——MULTIPLIER(相乘器)调出

二、1、用示波器观察调幅电路输出波形:载波频率是否与输入载波频率一致;

包络波形是否与输入低频信号一致

参考时基标度:200 us/Div或500us/Div、

(将输出波形粘贴到此)

2、用傅立叶分析观察输出调幅信号频谱成分

菜单栏:仿真—分析—傅立叶分析—分析参数设置(如下图)

分析输出对象选V(4)后。

点击“仿真”。

观察其频谱。

(将频谱图粘贴到此)

对象分别选输入量V(2),观察其频谱(将频谱图粘贴到此)

对象分别选输入量V(1),观察其频谱(将频谱图粘贴到此)

三、变更参数,用示波器观察输出波形

1、将直流电压V3更改为1V(此时调幅度为1),用示波器观察输出信号波形。

(将输出波形粘贴到此)

2、将直流电压V3更改为0.6V(此时调幅度>1),用示波器观察输出信号波形。

(将输出波形粘贴到此)

3、将直流电压V3更改为0V(或短路取消V3),用傅立叶分析观察输出信号频谱(将频谱图粘贴到此)

用示波器观察输出信号波形(将输出波形粘贴到此)。

实验十一模拟乘法器调幅(AM、DSB、SSB)一、实验目的1.掌握用集成模拟乘法器实现全载波调幅、抑止载波双边带调幅和单边带调幅的方法。

2.研究已调波与调制信号以及载波信号的关系。

3.掌握调幅系数的测量与计算方法。

4.通过实验对比全载波调幅、抑止载波双边带调幅和单边带调幅的波形。

5.了解模拟乘法器(MC1496)的工作原理,掌握调整与测量其特性参数的方法。

二、实验内容1.调测模拟乘法器MC1496正常工作时的静态值。

2.实现全载波调幅,改变调幅度,观察波形变化并计算调幅度。

3.实现抑止载波的双边带调幅波。

4.实现单边带调幅。

三、实验原理及实验电路说明幅度调制就是载波的振幅(包络)随调制信号的参数变化而变化。

本实验中载波是由晶体振荡产生的465KHz高频信号,1KHz的低频信号为调制信号。

振幅调制器即为产生调幅信号的装置。

1.集成模拟乘法器的内部结构集成模拟乘法器是完成两个模拟量(电压或电流)相乘的电子器件。

在高频电子线路中,振幅调制、同步检波、混频、倍频、鉴频、鉴相等调制与解调的过程,均可视为两个信号相乘或包含相乘的过程。

采用集成模拟乘法器实现上述功能比采用分离器件如二极管和三极管要简单得多,而且性能优越。

所以目前无线通信、广播电视等方面应用较多。

集成模拟乘法器常见产品有BG314、F1595、F1596、MC1495、MC1496、LM1595、LM1596等。

(1)MC1496的内部结构在本实验中采用集成模拟乘法器MC1496来完成调幅作用。

MC1496是四象限模拟乘法器,其内部电路图和引脚图如图11-1所示。

其中V1、V2与V3、V4组成双差分放大器,以反极性方式相连接,而且两组差分对的恒流源V5与V6又组成一对差分电路,因此恒流源的控制电压可正可负,以此实现了四象限工作。

V7、V8为差分放大器V5与V6的恒流源。

图11-1 MC1496的内部电路及引脚图2)静态工作点的设定(1)静态偏置电压的设置静态偏置电压的设置应保证各个晶体管工作在放大状态,即晶体管的集-基极间的电压应大于或等于2V,小于或等于最大允许工作电压。

摘要Multisim是美国国家仪器(NI)有限公司推出的以Windows为基础的仿真工具,适用于初级的模拟/数字电路板的设计工作,包含电路原理图图形及电路硬件描述语言的输入方式,具有丰富的仿真分析能力。

模拟乘法器是一种完成两个模拟信号(电压或电流)相乘作用的电子器件。

它具有两个输入端对和一个输出端对,是三端对有源器件。

主要内容为基于Multisim的模拟乘法器应用设计与仿真。

阐述了双边带调幅及普通调幅、同步检波、混频、乘积型鉴相电路的原理,并在电路设计与仿真平台Multisim11仿真环境中创建集成模拟乘法器MC1496电路模块,利用模拟乘法器MC1496完成各项电路的设计与仿真,并结合LabVIEW虚拟仪器实现对语音信号的普通调幅及解调。

关键词:Multisim;模拟乘法器;MC1496AbstractMultisim introduced by United States National Instruments(NI) Limited company is a Windows-based simulation tool, suitable for design elementary analog / digital circuit, contains a circuit theory of diagram and the circuit hardware description language input methods, with extensive simulation analysis.Analog multiplier is a complete two analog signals (voltage or current) multiplied by the role of electronic devices. It has two inputs and one output on the right, yes three-terminal on the active device.The main content is that analog multiplier multisim-based application design and simulation. Describe some circuit’s theory, such as Double Side Band amplitude modulation and common amplitude modulation、synchronous detection、mixing、product type phase. Create the integrated circuit analog multiplier MC1496 module in simulation platform Multisim11 simulation environment, make use of the analog multiplier MC1496 module complete circuit design and simulation, combined with labVIEW fictitious instrument to complete the speech signal amplitude modulation and demodulation.Keywords: Multisim;Analog Multiplier;MC1496目录第1章概述 (1)1.1 Multisim简介 (1)1.2 Multisim发展 (1)第2章总体设计思想 (3)2.1 模拟乘法器MC1496的工作原理 (3)2.2 幅度调制 (5)2.3 同步检波 (7)2.4 混频 (8)2.5 乘积型鉴相 (9)2.6 语音信号调制解调 (10)2.7 本章小结 (11)第3章电路调试与仿真 (12)3.1 模拟乘法器MC1496的创建 (12)3.2 调幅设计 (15)3.3 同步检波设计 (17)3.4 混频设计 (19)3.5 乘积型鉴相设计 (21)3.6 语音信号调制 (24)3.7 本章小结 (25)结论 (26)参考文献 (27)致谢 (28)第1章概述1.1 Multisim简介Multisim是加拿大图像交互技术公司(Interactive Image Technoligics简称IIT 公司)推出的以Windows为基础的仿真工具,适用于初级的模拟/数字电路板的设计工作。

计算机运算原理技术 2007-08-21 20:41:18 阅读1312 评论4 字号:大中小订阅第三节定点数运算定点数运算包括移位、加、减、乘、除几种。

一、移位运算1.移位的意义移位运算在日常生活中常见。

例如15米可写作1500厘米,单就数字而言,1500相当于小数点左移了两位,并在小数点前面添了两个0;同样15也相当于1500相对于小数点右移了两位,并删去了小数点后面的两个0。

可见,当某个十进制数相对于小数点左移n位时,相当于该数乘以10n;右移n位时,相当于该数除以10n。

计算机中小数点的位置是事先约定的,因此,二进制表示的机器数在相对于小数点作n 位左移或右移时,其实质就便该数乘以或除以2n(n=1,2...n)。

移位运算又叫移位操作,对计算机来说,有很大的实用价值,例如,当计算机没有乘(除)运算线路时,可以采用移位和加法相结合,实现乘(除)运算。

计算机中机器数的字长往往是固定的,当机器数左移n位或右移n位时,必然会使其n 位低位或n位高位出现空位。

那么,对空出的空位应该添补0还是1呢?这与机器数采用有符号数还是无符号数有关,对有符号的移位叫算术移位。

2.算术移位规则对于正数,由于[x]原=[x]补=[x]反=真值,故移位后出现的空位均以0添之。

对于负数,由于原码、补码和反码的表示形式不同,故当机器数移位时,对其空位的添补规则也不同。

下表列出了三种不同码制的机器数(整数或小数均可),分别对应正数或负数,移位后的添补规则。

必须注意的是:不论是正数还是负数,移位后其符号位均不变,这是算术移位的重要特点。

不同码制机器数移位后的空位添补规则码制添补代码正数原码、补码、反码0原码0负数补码左移添0右移添1反码 1由上表可得出如下结论:(1)机器数为正时,不论左移或右移,添补代码均为0。

(2)由于负数的原码其数值部分与真值相同,故在移位时只要使符号位不变,其空位均添0。

(3)由于负数的反码其各位除符号位外与负数的原码正好相反,故移位后所添的代码应与原码相反,即全部添1。

课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:定点原码二位乘法器的设计院(系):专业:班级:学号:姓名:指导教师:说明:结论(优秀、良好、中等、及格、不及格)作为相关教环节考核必要依据;格式不符合要求;数据不实,不予通过。

报告和电子数据必须作为实验现象重复的关键依据。

学术诚信声明本人声明:所呈交的报告(含电子版及数据文件)是我个人在导师指导下独立进行设计工作及取得的研究结果。

尽我所知,除了文中特别加以标注或致谢中所罗列的内容以外,报告中不包含其他人己经发表或撰写过的研究结果,也不包含其它教育机构使用过的材料。

与我一同工作的同学对本研究所做的任何贡献均己在报告中做了明确的说明并表示了谢意。

报告资料及实验数据若有不实之处,本人愿意接受本教学环节“不及格”和“重修或重做”的评分结论并承担相关一切后果。

本人签名: 日期:年月日课程设计任务书目录第1章总体设计方案 (1)1.1设计原理 (1)1.2设计思路 (3)1.3设计环境 (3)第2章详细设计方案 (5)2.1顶层方案图的设计与实现 (5)2.2创建顶层图形设计文件 (5)2.3器件的选择与引脚锁定 (6)第3章功能模块的设计与实现 (7)3.1控制器模块的设计与实现 (7)3.2选择器模块的设计与实现 (7)3.3乘数模块的设计与实现 (8)3.4部分积模块的设计与实现 (9)3.5原码两位乘法器模块的设计与实现 (10)第4章编程下载与硬件测试 (12)3.1编程下载 (12)3.2硬件测试及结果分析 (12)参考文献 (13)第1章 总体设计方案1.1设计原理原码两位乘的乘数和被乘数用原码表示,根据乘数最后两位的取值情况,依次求出被乘数对应的4种选择值,然后与上次部分积相加之后,再对本次得出的部分值右移两位,循环执行,直至乘数的高两位运算完成为止。

两位乘数共有四种状态,对应的四种状态可得表1.表中2倍的被乘数可通过乘数将X 左移1位得到2X ,在机器内通常采用左斜送一位来实现。

目录摘要........................................................................................................................................................................- 3 -第一章概述........................................................................................................................................................- 4 -1.1加法器概述及应用 (4)1.2乘法器概述及应用 (4)第二章加法器电路的研究 .............................................................................................................................- 5 -2.1一位全加器简介 (5)2.1.1 一位全加器符号.............................................................................................................................- 5 -2.1.2 一位全加器真值表.........................................................................................................................- 6 -2.2静态CMOS一位全加器电路 (6)2.3镜像CMOS全加器 (7)2.3.1镜像CMOS全加器原理图...........................................................................................................- 7 -2.3.2镜像CMOS全加器工作原理 ....................................................................................................- 8 -2.3.3镜像CMOS全加器棍棒图.........................................................................................................- 8 -2.4基于传输门的全加器 (8)2.5曼彻斯特进位链全加器 (9)2.5.1 曼彻斯特进位链的静态实现.......................................................................................................- 9 -2.5.2 曼彻斯特进位链的动态实现.................................................................................................... - 10 -第三章乘法器电路的研究 .......................................................................................................................... - 10 -3.1四位乘法器原理 (10)3.2阵列乘法器 (11)3.2.1 阵列乘法器原理...........................................................................................................................- 11 -3.2.2 阵列乘法器延时分析 ................................................................................................................. - 12 -3.3进位保留乘法器 (13)3.3.1进位保留乘法器原理 .................................................................................................................. - 13 -3.3.2进位保留乘法器延时分析 ......................................................................................................... - 14 -3.4树状乘法器 (14)第四章乘法器基本单元设计...................................................................................................................... - 15 -4.1两输入与门设计 (15)4.1.1 两输入与门原理图...................................................................................................................... - 15 -4.1.2 两输入与门版图.......................................................................................................................... - 16 -4.2基于传输门的全加器设计 (16)4.2.1 全加器逻辑功能测试 ................................................................................................................. - 17 -4.2.2 全加器延时分析.......................................................................................................................... - 18 -4.2.3 Cout与Sum延时比较................................................................................................................ - 21 -4.2.4 全加器版图设计及LVS............................................................................................................. - 22 -4.2.5 全加器功耗................................................................................................................................... - 24 -第五章四位无符号阵列乘法器设计与仿真........................................................................................... - 24 -5.1四位无符号阵列乘法器设计 (24)5.1.1四位无符号阵列乘法器原理图................................................................................................. - 24 -5.1.2 四位无符号阵列乘法器逻辑功能测试.................................................................................. - 25 -5.1.3 乘法器延时参数测量 ................................................................................................................. - 27 -5.2四位无符号阵列乘法器版图设计 (38)5.2.1 四位无符号阵列乘法器版图.................................................................................................... - 38 -5.2.2 原理图与版图对查比较(LVS).................................................................................................. - 39 -5.3四位无符号阵列乘法器版图仿真 (40)第六章总结与改进........................................................................................................................................ - 45 -参考文献............................................................................................................................................................ - 45 -摘要乘法运算非常耗费硬件面积并且速度很慢,许多计算问题解决的快慢受乘法器电路工作速度的约束,因此,在大多数先进的数字系统为实现高速算术运算都集成了硬件乘法单元,例如许多高速单片机微控制器中的算逻运算都使用了硬件并行乘法器。