6.3 STM32F207ZG的时钟深入剖析(32M,40M,72M灵活切换)

- 格式:pdf

- 大小:753.83 KB

- 文档页数:15

ST代理-深圳恒信宇电子请给文档评分谢谢!主要特点与中文描述STM32F205STM32F207描 述 该stm32f20x是基于高性能的32位精简指令集的核心运行频率高达120兆赫。

该系列采用高速嵌入式存储器(快闪记忆体可达1字节,多达128个字节的系统存储器),多达4个字节的备份存储器,和一个范围广泛的增强我/操作系统和外设连接到建业巴士,三巴士和一个32 - multi-ahb总线矩阵。

该设备还具有一个自适应的实时内存加速器(艺术加速器?),允许实现一个性能相当于0个等待状态的程序执行从快闪记忆体在频率高达120兆赫。

这一业绩已被证实使用coremark基准。

所有设备提供三的12位模数转换器,数模转换器,低功耗的时钟,十二个通用的16位定时器包括脉宽调制定时器的电机控制,2通用32位定时器。

一个真正的数字随机发生器(测距)。

它们还具有标准和先进的通信接口。

新的先进的设备包括一个输出,增强柔性静态存储器控制(设计)接口(设备提供软件包100引脚和更多),和一个摄像头界面传感器。

该装置还采用标准外设。

相关型号:STM32F051,STM32F2系列,STM32F4系列,STM32F100,STM32F101,STM32F102,STM32F103, STM32F105,STM32F107,STM32L151,STM32L152,STM32F050 ST代理-深圳恒信宇电子请给文档评分谢谢!主要特点与中文描述STM32F205STM32F207主要特点* 核心:32位- 3处理器(120兆赫最大)的自适应实时加速器(加速器?)允许0-wait国家 执行性能快闪存储器,微处理器,能力高达150 / 1.25 /兆赫(dhrystone能力高达2.1)* 记忆:多达1字节的闪存* 512字节的存储器* 高达128 + 4个字节的存储器* 灵活的静态内存控制器,支持小型闪存,静态存储器,psram,也和记忆* 液晶并行接口,8080 / 6800模式* 计算单元* 时钟,复位和供应管理* 从1.8到3.6伏的供电+我/操作系统* 4至26兆赫的晶体振荡器* 内部16兆赫* 32千赫振荡器时钟的校准* 内部32千赫* 低功率* 睡眠,停止和待机模式* vbatsupply为时钟,20×32位备份寄存器,和可选的4备份存储器* 3×12位,0.5μ的ADC多达24通道和6吨三交错模式* ×12位模数转换器2* 通用存储器控制器:16-stream集中FIFO和突发支持* 96位独特的身份证* 高达17定时器* 多达十二个16位和32位定时器,高达120兆赫,每到4集成电路/业主立案 法团/脉宽调制或脉冲计数器和正交(增量)编码器输入* 调试模式:串行线调试(社署),系统,和cortex-m3嵌入式追踪宏?* 多达140个输入/输出端口中断能力:* 多达136个快速输入/输出高达60兆赫* 高达138 5 v-tolerant我/操作系统* 多达15个通信接口* 高达3×串行接口(兼容pmbus)* 高达4和2 uarts USART(7.5兆位/秒,7816接口,林,红外通信,调制解调器控制)* 多达3个接口(30兆位/秒),2混合接口实现音频类精度通过音频锁相环或外部锁相环2×可以* 接口(网主动)* 接口* 先进连接* 2全速设备/主机/控制芯片与芯片的物理层* 2高速全速设备/主机/控制芯片专用,片上全速物理层和低引脚数接口* 10 / 100以太网专用存储器:支持国际1588v2硬件,信息产业部/简化媒体独立接口* 8 - 14位并行接口(48字节/秒最大)* 模拟真随机数发生器。

stm32系统时钟配置问题系统从上电复位到72mz 配置好之前,提供时钟的是内如高速rc 振荡器提供8MZ 的频率,这个由下面void SystemInit (void)函数的前面的一部分代码来完成的和保证的:RCC->CR |= (uint32_t)0x00000001;#ifndef STM32F10X_CLRCC->CFGR &= (uint32_t)0xF8FF0000;#elseRCC- >CFGR &= (uint32_t)0xF0FF0000;#endif RCC->CR &= (uint32_t)0xFEF6FFFF; RCC->CR &= (uint32_t)0xFFFBFFFF;RCC->CFGR &= (uint32_t)0xFF80FFFF;#ifdef STM32F10X_CLRCC->CR &= (uint32_t)0xEBFFFFFF;RCC->CIR = 0x00FF0000;RCC->CFGR2 = 0x00000000;#elif defined (STM32F10X_LD_VL) || defined (STM32F10X_MD_VL) || (defined STM32F10X_HD_VL)RCC->CIR =0x009F0000;RCC->CFGR2 = 0x00000000;#elseRCC->CIR = 0x009F0000;#endif#if defined (STM32F10X_HD) || (defined STM32F10X_XL) || (defined STM32F10X_HD_VL)#ifdefDATA_IN_ExtSRAMSystemInit_ExtMemCtl();#endif#endif接着void SystemInit (void)调用SetSysClock();函数,将系统时钟配置到72m,将AHB,APB1,APB2 等外设之前的时钟都配置好,然后切换到72mz 下运行。

STM32 系统时钟配置一、STM32的时钟系统时钟是什么?时钟通常是振荡器(如晶振)产生的特定频率的方波信号,时钟周期是时钟频率的倒数,时钟频率1MHz时钟周期为1/1000000=1us。

时钟周期是MCU处理指令的最小时间单元,每个程序指令都需要若干个时钟周期,MCU的时钟频率越快,完成一个指令的时间就越短,速度就越快。

时钟是MCU运行的基础,好比MCU的脉搏,是MCU性能的重要参数。

每个MCU 都是在某个特定的时钟频率下进行工作的,如C51单片机时钟频率为12MHz,而STM32F103 的系统时钟频率是72MHz。

STM32的时钟系统STM32时钟频率较高,时钟越快功耗越大,同时抗电磁干扰能力也会越弱。

而且STM32外设非常多,而通常外设是不需要像系统时钟那么高的频率的,比如看门狗和RTC 只需要几十K的时钟即可。

另外实际使用的时候通常只会用到有限的几个外设,STM32可以只给需要启动的外设分配时钟,以此来降低功耗。

由此可看出STM32 的时钟系统较为复杂,它采用了多个时钟源的方法来解决这些问题。

STM32 有4个独立时钟源:HSI、HSE、LSI、LSE。

①、HSI是高速内部时钟,RC振荡器,频率为8MHz,精度不高。

②、HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

③、LSI是低速内部时钟,RC振荡器,频率为40kHz,提供低功耗时钟。

④、LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

其中LSI是作为IWDGCLK(独立看门狗)时钟源和RTC时钟源而独立使用,HSI高速内部时钟 HSE高速外部时钟 PLL锁相环时钟这三个经过分频或者倍频作为系统时钟来使用基本时钟源(图中绿色箭头指出):(1)HSI高速内部时钟,RC振荡器,8MHz。

(2)HSE高速外部时钟,石英/陶瓷谐振器,8MHz。

(3)LSI低速内部时钟,RC振荡器,40kHz。

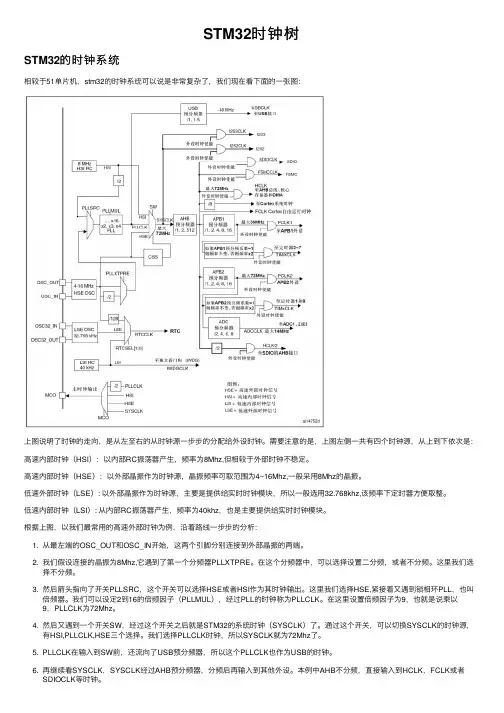

STM32时钟树STM32的时钟系统相较于51单⽚机,stm32的时钟系统可以说是⾮常复杂了,我们现在看下⾯的⼀张图:上图说明了时钟的⾛向,是从左⾄右的从时钟源⼀步步的分配给外设时钟。

需要注意的是,上图左侧⼀共有四个时钟源,从上到下依次是:⾼速内部时钟(HSI):以内部RC振荡器产⽣,频率为8Mhz,但相较于外部时钟不稳定。

⾼速内部时钟(HSE):以外部晶振作为时钟源,晶振频率可取范围为4~16Mhz,⼀般采⽤8Mhz的晶振。

低速外部时钟(LSE): 以外部晶振作为时钟源,主要是提供给实时时钟模块,所以⼀般选⽤32.768khz,该频率下定时器⽅便取整。

低速内部时钟(LSI): 从内部RC振荡器产⽣,频率为40khz,也是主要提供给实时时钟模块。

根据上图,以我们最常⽤的⾼速外部时钟为例,沿着路线⼀步步的分析:1. 从最左端的OSC_OUT和OSC_IN开始,这两个引脚分别连接到外部晶振的两端。

2. 我们假设连接的晶振为8Mhz,它遇到了第⼀个分频器PLLXTPRE。

在这个分频器中,可以选择设置⼆分频,或者不分频。

这⾥我们选择不分频。

3. 然后箭头指向了开关PLLSRC,这个开关可以选择HSE或者HSI作为其时钟输出。

这⾥我们选择HSE,紧接着⼜遇到锁相环PLL,也叫倍频器。

我们可以设定2到16的倍频因⼦(PLLMUL),经过PLL的时钟称为PLLCLK。

在这⾥设置倍频因⼦为9,也就是说乘以9,PLLCLK为72Mhz。

4. 然后⼜遇到⼀个开关SW,经过这个开关之后就是STM32的系统时钟(SYSCLK)了。

通过这个开关,可以切换SYSCLK的时钟源,有HSI,PLLCLK,HSE三个选择。

我们选择PLLCLK时钟,所以SYSCLK就为72Mhz了。

5. PLLCLK在输⼊到SW前,还流向了USB预分频器,所以这个PLLCLK也作为USB的时钟。

6. 再继续看SYSCLK,SYSCLK经过AHB预分频器,分频后再输⼊到其他外设。

《嵌入式技术》期末考试题1一、填空题(20分)1.ARM 这个缩写包含两个意思: 一是指___________;二是指______________。

2.常用的AT89C52单片机为_____位单片机, 而STM32单片机为____位单片机。

常用的STM32F103~107系列单片机是基于_________内核, 此内核采用的是___________结构。

STM32单片机共有8种输入输出模式, 其中输入模式有____种, 输出模式有_____种。

在编写按键检测程序时, 加一个延时判断的目的是为了__________, 这种方法叫________。

二、判断题(20分)学习嵌入式技术不需要硬件基础, 只需要会编写软件即可。

()2.STM32F103~107系列单片机的最大系统时钟频率为72MHz。

()3.STM32F103~107系列单片机的工作电压为5.0V。

()4.STM32的软件开发环境有Keil u5、IAR等。

()5.STM32的开发模式只有基于固件库函数方式一种。

()三、名词解释(20分)1.GPIO1、TIMER2、USART3、OS四、简答题(40分)1.请举例说明, 在你身边有哪些是单片机应用系统(至少举3例)?2.与常用的AT89C52单片机比较, STM32单片机有哪些方面的优点?3.STM32单片机常见的基本功能部件(外设)有哪些?4.编写一个函数, 函数描述: 控制LED每隔1S闪烁一次, 控制LED的引脚为PC8, 只写出具体的控制函数即可, 整体程序不用编写。

《嵌入式技术》期末考试题1 参考答案一、填空题1.ARM 公司ARM 公司设计的CPU及其架构2.8 322、3.Cortex-M3 哈佛3、4 44、延时消抖软件消抖法二、判断题1、✖2、✔3、✖4、✔5、✖三、名词解释1、输入/输出接口2、定时器3、通用串行通信接口4、操作系统四、简答题1、略2、(1)stm32 单片机的运算速度比AT89C52单片机的快;(2)stm32 单片机能移植操作系统,这样能处理多任务;(3)stm32 单片机外围接口功能比AT89C52单片机强大。

STM32时钟总结一、时钟基本概念 (2)二、时钟树 (7)三、STM32上电后时钟的过程. (7)3.1 执行SystemInit ()函数 (7)3.2 执行SetSysClock()函数. (8)3.3 执行SetSysClockTo72()函数 (8)3.3.2 判断外部高速时钟源是否稳定 (8)3.3.4 FLASH 配置. (9)3.3.5 系统时钟配置是HCLK,PCLK2为HCLK,PCLK1为HCLK的一半93.3.6 配置PLL 在这里修改倍频值。

RCC_CFGR_PLLMUL9L 93.3.7 失能PLL;判断PLL是否Readay;选择PLL 为系统时钟,一直等到时钟稳定 (9)四、时钟源的选择 (10)4.1 系统默认配置时钟8*9=72M (10)4.2 配置HSI(高速内部时钟)为系统主时钟(永远不变8M)104.3 配置HSE为系统主时钟。

8M(和外部晶振有关)114.4 配置PLLCLK为系统主时钟. (11)4.5 程序 (11)五、配置HCLK,PCLK,1 PCLK2. (11)、时钟基本概念钟。

当时钟源被直接或通过PLL间接作为系统时钟时,它将不能被停止。

稳定阶段的延迟或PLL 稳定),从一个时钟源到另一个时钟源的切换才会发生。

在被选择时钟源没有就绪时,系统时钟的切换不会发生。

直至目标时钟源就绪,才发生切换。

时钟安全系统(CSS)时钟安全系统可以通过软件被激活。

一旦其被激活,时钟监测器将在HSE振荡器启动延迟后被使能,并在HSE时钟关闭后关闭。

如果HSE时钟发生故障,HSE 振荡器被自动关闭,时钟失效事件将被送到高级定时器TIM1的刹车输入端,并产生时钟安全中断CSSI,允许软件完成营救操作。

此CSSI中断连接到Cortex ?M3的NMI中断。

一旦CSS被激活,并且HSE时钟出现故障,CSS中断就产生,并且NMI 也自动产生。

NMI 将被不断执行,直到CSS中断挂起位被清除。

Page 1基于ARM内核的32位MCU,150DMIPs,高达1MB Flash/128+4KB RAM,USB On-The-Go Full-speed/High-speed,以太网,17 TIMs,3 ADCs,15个通信&摄像头接口主要特性:内核:使用ARM 32位Cortex™-M3 CPU,自适应实时加速器(ART加速器™)可以让程序在Flash中以最高120MHz频率执行时,能够实现零等待状态的运行性能,内置存储器保护单元,能够实现高达150DMIPS/1.25DMIPS/MHz(Dhrystone 2.1)性能。

存储器:高达1M字节的Flash存储器512字节的动态口令存储器高达128+4K字节的SRAM灵活的静态存储控制器,支持CF卡、SRAM、PSRAM、NOR和NAND存储器并行LCD接口,兼容8080/6800模式时钟、复位和电源管理:1.65~3.6V用于供电和I/O管脚上电复位、掉电复位、可编程电压监测器和欠压复位4~26MHz晶体振荡器内嵌经出厂调校的16MHz RC振荡器(25 °C下精度为1%)带校准功能的32kHz RTC振荡器内嵌带校准功能的32kHz的RC振荡器低功耗:睡眠、停机和待机模式VBAT为RTC,20×32位后备寄存器,以及可选的4KB后备SRAM供电3×12位A/D转换器,0.5μs转换时间:多达24个输入通道在三倍间插模式下转换速率高达6MSPS2×12位D/A转换器通用DMA:16组带集中式FIFO和支持分页的DMA控制器多达17个定时器:多达12个16位和2个32位的定时器,频率可达120MHz,每个定时器有多达4个用于输入捕获/输出比较/PWM或脉冲计数的通道和增量编码器输入调试模式:串行单线调试(SWD)和JTAG接口Cortex-M3内嵌跟踪模块(ETM)多达140个具有中断功能的I/O端口:多达136个快速I/O端口,其频率可达60MHz多达138个耐5V的I/O端口多达15个通信接口:多达3个I2C接口(支持SMBus/PMBus)多达4个USART接口和2个UART接口(传输速率7.5 Mbit/s,支持ISO7816,LIN,IrDA接口和调制解调控制)多达3个SPI接口(传输速度可达30 Mbit/s),其中2个可复用为I2S接口,通过音频PLL或外部PLL来实现音频类精度2个CAN接口(2.0B 版本)SDIO接口高级互连功能:带有片上物理层的USB 2.0全速设备/主机/On-The-Go控制器带有专用DMA,片上全速PHY和ULPI的USB 2.0高速/全速设备/主机/On-The-Go 控制器带有专用DMA的10/100 以太网MAC.,支持硬件IEEE 1588v2(MII/RMII)8到14bit并行摄像头接口,最高达48Mbyte/sCRC计算单元96位唯一ID模拟真正的随机数发生器Page 2目录略Page 3目录略Page 4目录略Page 5表格目录略Page 6表格目录略Page 7插图目录略Page 8插图目录略Page 9插图目录略Page 101 简介这个数据手册给出了STM32F205xx和STM32F207xx系列微控制器的说明书。

STM32片上时钟分析一、结论1、f107应当使用25MHz晶振。

若采用8MHz的晶振,搭配3.0.0版固件库,则将f107当做f103使用,不能驱动通信线产品所有功能(以太网)。

2、以太网的时钟可以参考f107数据手册,附录A2.二、stm32f107的片上时钟系统f107与f103时钟系统略有不同,以下讨论除非特别说明,全都针对f107,采用25MHz 晶振,时钟树见附录。

1、系统时钟:SYSCLK系统复位后,HSI振荡器被选为系统时钟(8MHz),通过软件(SystemInit()函数)将系统时钟源切换到PLLCLK。

PLLCLK的来源是外部晶振HSE,由HSE信号经过5分频、8倍频、5分频、9倍频得到,为72MHz。

(若在f107上采用8MHz晶振,则将HSE信号9倍频得到PLLCLK(72MHz),即系统时钟)2、RTC时钟源来自32.768kHZ晶振。

3、金牛版上另外有一个25MHz的晶振,供给以太网PHY。

三、时钟系统初始化(SystemInit()函数)此函数在3.0.0与3.1.2版本固件库中是不同的。

相较于f103,f107在硬件上多了两个锁相环和一个CFGR2寄存器,并且定义了CR寄存器的26~29位。

3.0.0版本固件库升级为3.1.2版本,正是为了配合这种变化,并实现新增的功能。

调用3.0.0库中的SystemInit()函数,结果如下:寄存器值CR 0101 0083CFGR 001D 0402CFGR2 函数未涉及此寄存器CIR 0000 0000对此不作过多讨论,这样的方式会使以太网无法使用。

调用3.1.2库中的SystemInit()函数,结果如下:寄存器值CR 0501 0083CFGR 001D 0402CFGR2 0001 0644CIR 009F 0000前三个寄存器配置了系统时钟,CIR是对中断的设置。

这样,系统时钟的来源如下图。

蓝色为复位后的时钟系统,红色为软件设置的时钟。

STM32学习----时钟(转载)在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。

①、HSI是高速内部时钟,RC振荡器,频率为8MHz。

②、HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

HSE/LSE时钟源③、LSI是低速内部时钟,RC振荡器,频率为40kHz。

④、LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

⑤、PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。

倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

其中40kHz的LSI供独立看门狗IWDG使用,另外它还可以被选择为实时时钟RTC的时钟源。

另外,实时时钟RTC的时钟源还可以选择LSE,或者是HSE的128分频。

RTC的时钟源通过RTCSEL[1:0]来选择。

STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz 的时钟源。

该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1分频,也就是,当需要使用USB模块时,PLL必须使能,并且时钟频率配置为48MHz或72MHz。

另外,STM32还可以选择一个时钟信号输出到MCO脚(PA8)上,可以选择为PLL 输出的2分频、HSI、HSE、或者系统时钟。

系统时钟SYSCLK,它是供STM32中绝大部分部件工作的时钟源。

系统时钟可选择为PLL输出、HSI或者HSE。

系统时钟最大频率为72MHz,它通过AHB分频器分频后送给各模块使用,AHB分频器可选择1、2、4、8、16、64、128、256、512分频。

其中AHB分频器输出的时钟送给5大模块使用:①、送给AHB总线、内核、内存和DMA使用的HCLK时钟。

②、通过8分频后送给Cortex的系统定时器时钟。

③、直接送给Cortex的空闲运行时钟FCLK。

④、送给APB1分频器。

APB1分频器可选择1、2、4、8、16分频,其输出一路供APB1外设使用(PCLK1,最大频率36MHz),另一路送给定时器(Timer)2、3、4倍频器使用。

STM32F207的时钟说明请尽可能参阅英文原文件STM32F207有三个可选的时钟源,具体如下:(1)HIS时钟源(内部集成的时钟源)(2)HSE时钟源(外部高速晶体振荡器提供的时钟源或来自其他设备的时钟源)(3)PLL(PLL的时钟输入可以是HIS或者HSE时钟源)时钟控制器在选择内核及外设的时钟时具有高度的灵活性,以使他们都可以工作在最高频率上,并且能够保证给那些需要特殊频率的外设提供合适的频率,如Ethernet, USB OTG FS 和HS,I2S和SDIO。

三个可选的时钟源都可以独立地打开或关闭,以降低系统的功耗。

设备还有两个次要的时钟源,具体如下:(1)32KHz低速内部RC,可以驱动独立的看门狗和可以选择性使用的RTC(可用于在停止或待机状态下自动唤醒设备)(2)32.768KHz的低速外部晶体,可以作为RTC的时钟源。

几个预分频器用于配置AHB总线的频率,高速APB总线(APB2)和低速APB总线(APB1)所控制的区域的频率。

AHB总线的最高频率是120MHz,APB2总线的最高频率是60MHz,APB1总线的最高频率是30MHz。

所有的外设时钟都来源于系统时钟(SYSCLK),以下的几个除外:(1)USB OTG FS时钟(48MHz),随机模拟产生器(RNG)时钟(<=48MHz),SDIO时钟(<=48MHz),这些时钟来源于一个特殊的PLL(PLL2)的输出(PLL48CLK)。

(2)I2S时钟:为了达到高品质的音频效果,I2S时钟可能从特殊的PLL(PLLI2S)或外部接在I2S_CKIN引脚上的时钟得到。

(3)USB OTG HS(60MHz)时钟,由外部硬件提供。

(4)Ethernet MAC时钟(TX,RX和RMII)可以从外部硬件得到。

Ethernet使用时,AHB总线时钟不得低于25MHz。

RCC模块将AHB时钟8分频后提供给了Cortex系统定时器System Timer。

STM32时钟概述:

HSE:high speed external clock signal,高速外部时钟,最常用8M无源晶振,可以2分频或不分频,一般不分频,为8M。

HS I:high speed internal clock signal,高速内部时钟,8M,有温漂。

PLL时钟源:来源于HSE或者HSI/2,一般选HSE为时钟源。

PLLCLK时钟:通过设置PLL的倍频因子,对PLL时钟源进行倍频,倍频因子为:2-16。

一般设为9,则PLLCLK为72M。

(72M为官方推荐的稳定时钟源)。

SYSCLK:系统时钟,可来源于HSE、HSI、PLLCLK,一般设置SYSCLK=PLLCLK=72Mhz。

HCLK:AHB总线时钟(也有的说APB总线时钟),可分频,一般不分频,即HCLK=SYSCLK=72M。

PCLK2:APB2总线时钟,由HCLK经过APB2预分频器得到,一般1分频,PCLK2=HCLK=72M。

PCLK1:APB1总线时钟,由HCLK经过APB1预分频器得到,一般2分频,PCLK1=HCLK/2=36M。

RTC时钟:来源于HSE/128、LSE、LSI(一般40KHZ),独立的看门狗时钟由LSI提供。

MCO时钟输出:由PA8复用所得,可以对外提供时钟,可以检查所配置好的时钟(结合示波器使用),可来源于PLLCLK/2 SYSCLK HSE HSI。

stm32几种时钟控制介绍,含原理图本文提到的有以下内容:• 时钟系统与总线矩阵• SysTick系统定时器• RTC实时时钟• 看门狗定时器• 通用定时器一、时钟系统与总线矩阵stm32F4的时钟树如下图所示:在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。

HSI是高速内部时钟,RC振荡器,频率为8MHz。

HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

LSI是低速内部时钟,RC振荡器,频率为40kHz。

LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。

倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

我们在学习51单片机的时候,其内部是没有晶振的,而stm32是有的。

stm32可以通过RCC(时钟控制寄存器)对时钟进行参数配置以及使能。

我们还可以通过修改system_stm32f4xx.c文件,来配置上述时钟树上的一些分频、倍频参数,得到理想的频率。

在单片机系统中,CPU和总线以及外设的时钟设置是非常重要的,因为没有时钟就没有时序,组合电路需要好好理解清楚。

我们先来看一下总线矩阵。

片上总线标准种类繁多,而由ARM公司推出的AMBA片上总线受到了广大IP开发商和SoC系统集成者的青睐,已成为一种流行的工业标准片上结构。

AMBA规范主要包括了AHB(Advanced High performance Bus)系统总线和APB(Advanced Peripheral Bus)外围总线。

二者分别适用于高速与相对低速设备的连接。

一般性的时钟设置需要先考虑系统时钟的来源,是内部RC还是外部晶振还是外部的振荡器,是否需要PLL。

然后考虑内部总线和外部总线,最后考虑外设的时钟信号。

遵从先倍频作为CPU时钟,然后在由内向外分频,下级迁就上级的原则。