双端口存储器原理实验

- 格式:docx

- 大小:250.32 KB

- 文档页数:10

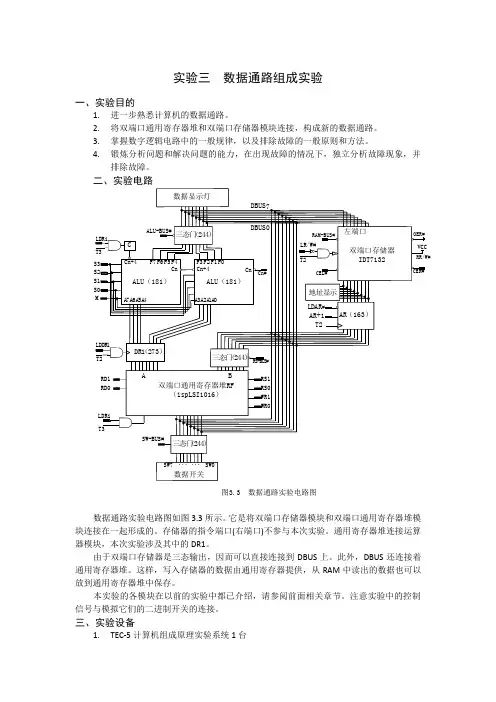

实验三数据通路组成实验一、实验目的1.进一步熟悉计算机的数据通路。

2.将双端口通用寄存器堆和双端口存储器模块连接,构成新的数据通路。

3.掌握数字逻辑电路中的一般规律,以及排除故障的一般原则和方法。

4.锻炼分析问题和解决问题的能力,在出现故障的情况下,独立分析故障现象,并排除故障。

二、实验电路图3.3 数据通路实验电路图数据通路实验电路图如图3.3所示。

它是将双端口存储器模块和双端口通用寄存器堆模块连接在一起形成的。

存储器的指令端口(右端口)不参与本次实验。

通用寄存器堆连接运算器模块,本次实验涉及其中的DR1。

由于双端口存储器是三态输出,因而可以直接连接到DBUS上。

此外,DBUS还连接着通用寄存器堆。

这样,写入存储器的数据由通用寄存器提供,从RAM中读出的数据也可以放到通用寄存器堆中保存。

本实验的各模块在以前的实验中都已介绍,请参阅前面相关章节。

注意实验中的控制信号与模拟它们的二进制开关的连接。

三、实验设备1.TEC-5计算机组成原理实验系统1台2.逻辑测试笔一支(在TEC-5实验台上)3.双踪示波器一台(公用)4.万用表一只(公用)四、故障的分析与排除数字电路中难免要出现这样或那样的故障。

有了故障迅速加以诊断并排除,使电路能正常运行,这是实际工作中经常遇到的事。

因此,学会分析电路故障,提高排除故障的能力,是很有必要的。

就数字电路的故障性质而言,大体有两大类:一类是设计中的错误或不当造成的故障;另一类是元件损坏或性能不良造成的。

1.设计错误造成的故障常见的设计错误有逻辑设计错误和布线错误。

对于布线错误,只要能仔细的进行检查就可以排除。

要较快的判断出布线错误的位置,可以通过对某个预知特性点的观察检测出来。

例如,该点的信号不是预期的特性,则可以往前一级查找。

常见的布线错误是漏线和布错线。

漏线的情况往往是输入端未连线或浮空。

浮空输入可用三状态逻辑测试笔或电压表检测出来。

对于设计错误,需要在设计中加以留心和克服。

计算机组成原理实验五《存储器设计》实验报告姓名:吴速碘黄紫微学号:班级:计算机二班日期2015、5、25实验五存储器设计一、实验目的1、掌握RAM和ROM的Verilog语言描述方法;2、学习用宏模块的方法定制RAM和ROM。

二、实验任务1、设计并实现一个128*16 的单端口的RAM;2、设计并实现一个128*16的ROM;3、设计并实现一个双端口的128*16的RAM4、设计并实现一个16*32的FIFO。

5、设计并实现正弦信号发生器,见“正弦信号发生器实验指南”。

三、实验步骤1 编写Verilog代码(见附页)2功能仿真进行分析与综合,排除语法上的错误建立波形仿真文件,输入激励生成功能仿真网表进行功能仿真,观察输出结果3选择器件DE2_70开发板的使用者请选择EP2C70F896C64绑定管脚5 下载验证DE2_70开发板的下载:使用USB-Blaster进行下载四、实验内容五、实验思考题1、分析存储器采用三态输出的原因是什么?存储器的输出端是连接在数据总线上的。

数据总线相当于一条车流频繁的大马路,必须在绿灯条件下,车辆才能进入这条大马路,否则要撞车发生交通事故。

同理,存储器中的数据是不能随意传送到数据总线上的。

例如,若数据总线上的数据是“1”(高电平5V),存储器中的数据是“0”(低电平0V),两种数据若碰到一起就会发生短路而损坏单片机。

因此,存储器输出端口不仅能呈现“l”和“0”两种状态,还应具有第三种状态“高阻"态。

呈“高阻"态时,输出端口相当于断开,对数据总线不起作用,此时数据总线可被其他器件占用。

当其他器件呈“高阻”态时,存储器在片选允许和输出允许的条件下,才能将自己的数据输出到数据总线上。

2、单端口和双端口的区别是什么?单端口ram是ram的读写只有一个端口,同时只能读或者只能写。

双端口ram是ram读端口和写端口分开,一个端口能读,另一个端口可以同时写。

3、什么情况下考虑采用双端口存储器?(1)为了使不致因为等待存储器读写操作的完成而无事可做,可以采取一些加速CPU 和存储器之间有效传输的特殊措施:●采用更高速的,或加长存储器的;●采用并行操作的双端口存储器;●在CPU和之间插入一个(Cache),以缩短读出时间;●在每个存储器周期中存取几个字.(采用交叉存储器)(2)双端口存储器是指同一个存储器具有两组相互独立的读写控制线路,由于进行并行的独立操作,是一种高速工作的存储器。

双口RAM1.模块功能:双口RAM模块主要采用IDT7132等器件,它是一种特殊的数据存储芯片,它既可以用于单片机存储大容量的数据,也可以以双口RAM为共享存储器来实现两个处理器之间的通信和数据传输。

双口RAM的优点是提供了两条完全独立的端口,每个端口都有完整的地址、数据和控制总线,允许两个CPU对双端口存储器的同一单元进行同时存取;具有两套完全独立的终端逻辑来实现两个CPU 之间的握手控制信号;具有两套独立的“忙”逻辑,保证两个CPU同时对同一单元进行读/写操作的正确性。

对于单个CPU而言,双口RAM同普通RAM没有什么明显的区别。

本模块原理图见图1。

图13.主要器件:(1)IDT7132:(a)器件功能:IDT7132是高速2k*8端口静态RAM,可提供图2.1.3 IDT7132引脚图两个拥有独立的控制总线、地址总线和I/O总线端口,允许CPU独立访问内部的任何存储单元。

当/CE 引脚出现下降沿时,选中DPRAM即可通过控制OE 或R/W来访问内部存储单元。

(b) 器件引脚:IDT7132的引脚图如图2所示。

/CE、/CER:(左、右)片选控制信号。

R/WL、R/WR:(左、右)读写控制信号。

/OEL、/OER:(左、右)使能控制信号。

/BUSYL、/BUSYR:(左、右)繁忙查询控制信号。

A0L—A9L、A0R—A9R:(左、右)地址总线。

I/O0L—I/O7L、I/O0R—I/O7R:(左、右)输入/输出总线。

VCC:电源。

(c) 工作原理:IDT7132的工作时序如图3所示。

它与RAM的读写时序非常类似。

当CPU选中DPRAM时/CE引脚出现下降沿,当控制线/OE为高且R/W为低时,CPU对内部存储单元进行写操作;而当控制线OE为低且R/W为高时,CPU对内部存储单元进行读操作。

当外部CPU通过两个端口对双口RAM内部的同一个存储单元进行操作时,系统将出现竞图 2争。

这种竞争一般有如下两种模式:(1)如果两个端口的总线访问地址相同,并先于片选信号/CE有效,则片内逻辑将在CEL与CER之间发生竞争。

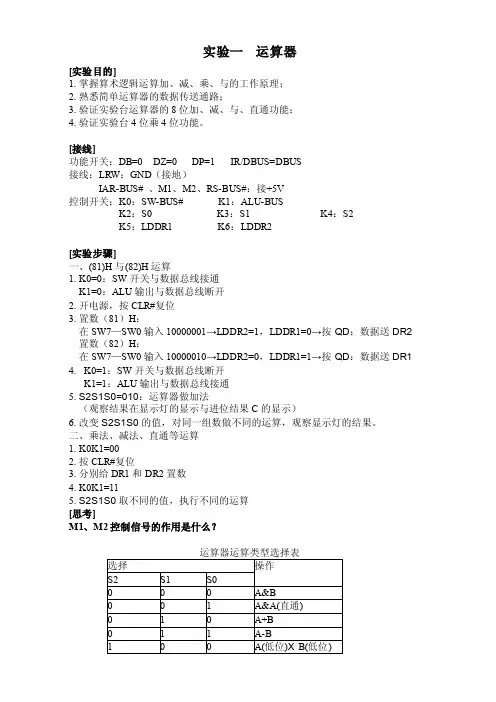

实验一运算器[实验目的]1.掌握算术逻辑运算加、减、乘、与的工作原理;2.熟悉简单运算器的数据传送通路;3.验证实验台运算器的8位加、减、与、直通功能;4.验证实验台4位乘4位功能。

[接线]功能开关:DB=0 DZ=0 DP=1 IR/DBUS=DBUS接线:LRW:GND(接地)IAR-BUS# 、M1、M2、RS-BUS#:接+5V控制开关:K0:SW-BUS# K1:ALU-BUSK2:S0 K3:S1 K4:S2K5:LDDR1 K6:LDDR2[实验步骤]一、(81)H与(82)H运算1.K0=0:SW开关与数据总线接通K1=0:ALU输出与数据总线断开2.开电源,按CLR#复位3.置数(81)H:在SW7—SW0输入10000001→LDDR2=1,LDDR1=0→按QD:数据送DR2置数(82)H:在SW7—SW0输入10000010→LDDR2=0,LDDR1=1→按QD:数据送DR1 4.K0=1:SW开关与数据总线断开K1=1:ALU输出与数据总线接通5. S2S1S0=010:运算器做加法(观察结果在显示灯的显示与进位结果C的显示)6.改变S2S1S0的值,对同一组数做不同的运算,观察显示灯的结果。

二、乘法、减法、直通等运算1.K0K1=002.按CLR#复位3.分别给DR1和DR2置数4.K0K1=115. S2S1S0取不同的值,执行不同的运算[思考]M1、M2控制信号的作用是什么?运算器运算类型选择表选择操作S2 S1 S00 0 0 A&B0 0 1 A&A(直通)0 1 0 A+B0 1 1 A-B1 0 0 A(低位)ΧB(低位)完成以下表格ALU-BUS SW-BUS# 存储器内容S2S1S0 DBUS C输入时:计算时:DR1:01100011DR2:10110100(与)DR1:10110100DR2:01100011(直通)DR1:01100011DR2:01100011(加)DR1:01001100DR2:10110011(减)DR1:11111111DR2:11111111(乘)实验二双端口存储器[实验目的]1.了解双端口存储器的读写;2.了解双端口存储器的读写并行读写及产生冲突的情况。

实验五存储器设计实验地点:EDA实验室901 实验时间:2014年5月23日实验人员:1240041 冯雅轩1240048 刘洁然实验五存储器设计一、实验目的1、掌握RAM和ROM的Verilog语言描述方法;2、学习用宏模块的方法定制RAM和ROM。

二、实验任务1、设计并实现一个128*16 的单端口的RAM;2、设计并实现一个128*16的ROM;3、设计并实现一个双端口的128*16的RAM4、设计并实现一个16*32的FIFO。

5、设计并实现正弦信号发生器,见“正弦信号发生器实验指南”。

三、实验步骤1 编写Verilog代码2功能仿真进行分析与综合,排除语法上的错误建立波形仿真文件,输入激励生成功能仿真网表进行功能仿真,观察输出结果3选择器件DE2_70开发板的使用者请选择EP2C70F896C64绑定管脚5 下载验证DE2_70开发板的下载:使用USB-Blaster进行下载四、实验内容五、实验思考题1.分析存储器采用三态输出的原因是什么?在第一个实验中,读出数据的改变是在数据地址readaddress或者存储器中存储数据发生变化时。

这是数据改变的条件,设置成三态门更高效,更合理。

2.单端口和双端口的区别是什么?单端口存储器就是:存储器接受数据和输出数据,只能在同一时刻只能执行一项操作,这样一来数据的写和传输就无法同时进行。

双端口存储器是指同一个存储器具有两组相互独立的读写控制线路,由于进行并行的独立操作,是一种高速工作的存储器。

简单说来,就是增加了一个端口,可以同时读数据和写数据,提高了机器运行速度和带宽,可以实现无冲突的读写控制。

3.什么情况下考虑采用双端口存储器?主存的存取速度是影响计算机速度的关键,才用双端口存储器可是明显提高机器的利用率和效率。

如果在对速度要求特别高的情况下,可以考虑采用双端口存储器。

4.FIFO的工作特点是什么?为什么常用于实现程序中的子程序调用、递归等?特点:FIFO(First In First Out)全称是先进先出的存储器。

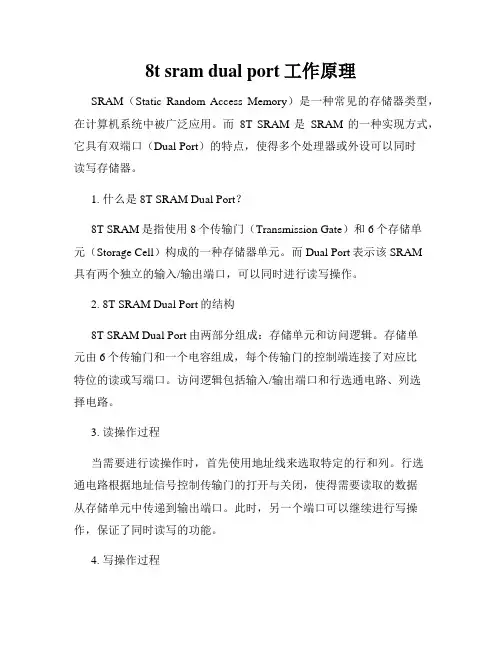

8t sram dual port工作原理SRAM(Static Random Access Memory)是一种常见的存储器类型,在计算机系统中被广泛应用。

而8T SRAM是SRAM的一种实现方式,它具有双端口(Dual Port)的特点,使得多个处理器或外设可以同时读写存储器。

1. 什么是8T SRAM Dual Port?8T SRAM是指使用8个传输门(Transmission Gate)和6个存储单元(Storage Cell)构成的一种存储器单元。

而Dual Port表示该SRAM具有两个独立的输入/输出端口,可以同时进行读写操作。

2. 8T SRAM Dual Port的结构8T SRAM Dual Port由两部分组成:存储单元和访问逻辑。

存储单元由6个传输门和一个电容组成,每个传输门的控制端连接了对应比特位的读或写端口。

访问逻辑包括输入/输出端口和行选通电路、列选择电路。

3. 读操作过程当需要进行读操作时,首先使用地址线来选取特定的行和列。

行选通电路根据地址信号控制传输门的打开与关闭,使得需要读取的数据从存储单元中传递到输出端口。

此时,另一个端口可以继续进行写操作,保证了同时读写的功能。

4. 写操作过程在进行写操作时,首先通过地址线选择具体的行和列。

接着输入端口将要写入的数据传递到输入端的传输门,通过列选择电路将数据写入到相应的存储单元。

与此同时,另一个端口可以持续进行读取操作。

5. 时序控制为了保证读写的正确性和稳定性,8T SRAM Dual Port需要进行一定的时序控制。

具体来说,读操作需要保证选通信号在读取过程中始终有效,而写操作需要保证传输门在进行写入时打开,传输完毕后关闭。

时序控制的设计需要考虑到信号延迟和操作间的冲突。

6. 数据一致性由于8T SRAM Dual Port具有双端口的特性,同时读写可能导致数据一致性的问题。

为了解决这个问题,需要在系统设计中引入其他的同步机制或者使用特定的读写协议,如互锁(handshaking)协议,保证多个端口之间的操作按照先后顺序执行。

毕业设计(论文)题目名称:基于FPGA的双口RAM在双CPU通信中的应用及设计学院:电气信息工程学院专业/班级:电子信息工程摘要基于现代通信系统的要求,本次设计详细研究了利用双端口RAM实现高速并行双CPU之间的数据通信,指出了设计中需要解决的几个关键性问题,并给出了相应的解决方案。

随着电子技术的迅速发展,大量的高速数据采集和现代工业测控系统和在线测试仪器的功能和性能提出了更高的要求,双CPU并行工作双单片机系统广泛应用。

为了使两个单片机可以快捷有效地交换信息,充分利用系统资源,共享内存实现通过使用双端口RAM现在更受欢迎的方法。

大容量高速FPGA器件具有较高的集成,体积小,灵活配置和实验风险小的优势。

在复杂数字系统越来越广泛的应用,数字电路设计采用1块FPGA设备存储设备和一些电气接口匹配电路解决方案已经成为一个主流的选择。

使用FPGA实现函数的双端口RAM是一个很好的方法来解决这个问题的并行性和速度,以及其灵活的可配置特性使基于FPGA双端口RAM容易修改测试和系统升级可以降低设计成本,缩短开发周期。

在嵌入式多CPU系统中,CPU之间的通信可以使用串行、并行和系统总线方式的双端口RAM,等等。

在三种沟通方式存在的共同传输速度慢的特点,在大量数据的情况下可能会导致数据处理时间的延长,实时性能,甚至出现数据拥堵现象。

所以与方法之间的双端口RAM数据交换系统是一个简单而有效的方法。

关键词: FPGA;双端口RAM;双CPU;并行数据通信AbstractBased on the demand of modern communication system, the design was studied by using dual port RAM to implement the parallel data communication between the double CPU, pointed out the need to be solved in the design of several key problems, and gives the corresponding solutions.With the rapid development of electronic technology, a large number of high-speed data acquisition and modern industry measurement and control system and the function of the online test instrument and performance put forward higher request, double CPU parallel work double single chip microcomputer system is widely used. Is becoming more and more widely used in complex number system, the digital circuit design of one piece of FPGA device storage equipment and some of the electrical interface matching circuit solution has become a mainstream choice. Using FPGA to realize function of dual port RAM is a very good method to solve the problem of parallelism and speed, and its flexible configurable properties based on FPGA dual port RAM is easier to modify test and system upgrade can reduce the design cost, shorten the development cycle.Key words: FPGA; Dual port RAM; Double CPU; The parallel data communication目录摘要 (I)Abstract (II)1绪论 (1)1.1研究发展趋势 (1)1.2研究现状 (1)1.3研究重点方向 (2)2 RAM与CPU之间通信的基本原理 (3)2.1 双口RAM 结构及工作原理 (3)2.1.1双口RAM的结构 (3)图2,1双口RAM存储结构图 (3)2.1.2双口RAM工作原理 (4)2.2 双CPU工作原理及应用 (5)2.2.1双CPU的结构 (5)2.2.2双CPU的工作原理 (6)2.2.3基于双CPU通信的设计及应用 (6)2.3 FPGA的基本结构及工作原理 (7)2.4本章小结 (8)3 双口RAM在双CPU通信中的设计及仿真 (9)3.1双端口RAM并行通信设计 (9)3.2系统关键性问题的解决 (10)3.2.1 系统故障冗余设计 (10)3.2.2 交叉事物处理设计 (10)3.3双CPU系统设计及关键技术问题 (11)3.3.1确保双CPU的协同可靠 (11)3.3.2合理设计交叉事物的实时处理软硬件 (11)3.3.3 双口RAM存储空间的组成及访问 (11)3.3.4可靠性的保障 (12)3.4仿真结果及性能分析 (13)3.5本章小结 (14)4总结及展望 (15)4.1课题研究所面临的问题 (15)4.2未来研究方向 (15)参考文献 (16)致谢 (17)附录 (18)1绪论1.1研究发展趋势随着现代智能系统的升级和更新,在双向通信和信息传输过程中,对信息量的增加和实时性的要求更加精准高效。

课程名称:计算机组成原理开课实验室: 2018年3月26日实验一、存储器存储实验一、实验目的掌握静态随机存储器RAM工作特性及数据的读/写方法;二、实验原理及基本技术路线图(方框原理图)1.在此实验中,半导体静态存储器的芯片规格为6116(2KX8),有三根控制线,分别是片选线CE、读线OE、写线WE。

其数据线接至数据总线,地址锁存器(74LS273)给出地址线。

2.数据开关经过三态门,并且到达总线。

地址灯AD7…AD0与地址线相连,可以通过观察地址灯来观察存储的地址。

3.当进行读写操作时,必须设置控制端CE=0,WE=0(WE=1),同时在T3传递脉冲过来。

当片选有效(CE=0)时,OE=0则进行读操作,WE=0则进行写操作。

4.实验时,需要将T3脉冲连接至实验板上时序电路模块的TS3相应插孔中。

脉冲宽度调到中层。

SW-B(三态门)为低有效电频, LDAR为高有效电频。

三、所用仪器、材料(设备名称、型号、规格等)(1)、TDN-CM+或 TDN-CM++教学实验设备一套。

(2)、PC机(或示波器)一台。

四、实验方法、步骤(1) 形成时钟脉冲信号T3。

具体接线方法和操作步骤如下:①接通电源,用示波器接入方波信号源的输出插孔H23,调节电位器W1及W2 ,使H23 端输出实验所期望的频率及占空比的方波。

②将时序电路模块(STATE UNIT)单元中的ф和信号源单元(SIGNALUNIT)中的H23 排针相连。

③在时序电路模块中有两个二进制开关“STOP”和“STEP”。

将“STOP”开关置为“RUN”状态、“STEP”开关置为“EXEC”状态时,按动微动开关START,则TS3端即输出为连续的方波信号,此时调节电位器W1,用示波器观察,使T3 输出实验要求的脉冲信号。

当“STOP”开关置为“RUN”状态、“STEP”开关置为“STEP”状态时,每按动一次微动开关START,则T3 输出一个单脉冲,其脉冲宽度与连续方式相同。

第1篇一、实验目的1. 理解存储器的基本概念、分类及工作原理;2. 掌握静态随机存储器(RAM)和只读存储器(ROM)的读写操作;3. 熟悉存储器在计算机系统中的作用及重要性;4. 提高动手能力,培养实验操作技能。

二、实验环境与仪器1. 实验环境:计算机组成原理实验室2. 实验仪器:- 计算机- 2Kx8 静态随机存储器 6116- 8 位数据锁存器 74LS273- 三态输出的 8 组总线收发器 74LS245- 非门、与门、开关、指示灯等三、实验原理1. 存储器分类存储器按存储介质可分为:磁存储器、半导体存储器、光存储器等;按存储功能可分为:只读存储器(ROM)、随机存储器(RAM)、闪存等。

2. 静态随机存储器(RAM)RAM是一种易失性存储器,断电后信息会丢失。

RAM具有读写速度快、存储容量大等特点,广泛应用于计算机系统中。

本实验使用2Kx8位静态随机存储器6116,其容量为2K字节,即2048字节,每个字节8位。

3. 只读存储器(ROM)ROM是一种非易失性存储器,断电后信息不会丢失。

ROM用于存储程序、数据等,如计算机的BIOS、固件等。

本实验使用只读存储器,具体型号未给出。

4. 存储器读写操作存储器读写操作主要包括:地址译码、数据传输、控制信号等。

本实验通过连接74LS273、74LS245等芯片,实现存储器的读写操作。

四、实验内容与步骤1. 连接电路根据实验电路图,连接2Kx8位静态随机存储器6116、8位数据锁存器74LS273、三态输出的8组总线收发器74LS245等芯片。

连接控制信号,如CE、OE、WE、P1、LDAR等。

2. 测试电路打开计算机,运行实验软件,对连接的电路进行测试。

观察存储器读写操作是否正常,如读写操作是否成功、数据是否正确等。

3. 数据初始化利用文本编辑器编辑mif文件,对只读存储器进行初始化。

将初始化后的mif文件加载到只读存储器中。

4. 读写操作在实验软件中,编写程序对存储器进行读写操作。

第18卷第1期 2008年2月 茂名学院学报

JO1 IRNAI.OF MAOMD G UN眦RSⅡY V01.18 N0.1

Eeb.20o8

一种双端口猝发式高速存储器模型 柯文德,刘晶 (茂名学院计算机与电子信息学院,广东茂名525000)

摘要:为解决高速CPU与低速主存储器两者速度的平衡和匹配问题,提出了一种双端口猝发式高速存储器模型,并通过仿 真实验验证了其正确性和可行性。该模型具备一般的猝发式存储器和双端口存储器的数据读取特点,可以高速读取成组 连续数据,较大幅度地提高微处理器系统的整体性能。 关键词:存储器;端口;猝发式;数据读取 中图分类号:TP333.1 文献标识码:A 文章编号:1671—6590(2008)01—0045—04

在现有计算机系统中,主存储器一般采用Dm (动态随机存储器)制造,其容量提高较快,但读取速 度和CPU相比,仍存在着数量级的差距[1-3】。为解决高速CPU与低速内存之间的速度差异,改善数据读 取的“瓶颈”问题,提高整机系统性能,本文提出了一种双端口猝发式存储器模型,以实现高速读取成组连 续数据。

1存储器基本模型 如图1所示,对DRAM阵列的访问有两组相互对称并各自独立的读写控制电路(图中L表示左端口信 号,R表示右端口信号),主要由以下几个部分组成: DRAM阵列:用于暂存数据。假设模型中的存储器容量为1 024 ̄512 ̄2位,即1024行,每行512列, 每列包含2位。 行地址和刷新控制:提供行地址选通信号RAS和DRAM阵列刷新信号Refo 行地址锁存器:在行地址和刷新控制信号有效时保存地址总线传送过来的地址 一 。 最后读出行地址锁存器:保存地址总线上一周期传送过来的行地址 一 。 1O位比较器:当新的地址 传送过来后,和最后读出行地址锁存器中的地址进行比较,判断是 否相同。 列地址锁存器:在列选通信号CAS有效时接收列地址。 512 ̄2位SRAM(cache):小容量高速缓冲存储器cache,用于接收DRAM中被选中的某一行。 I/0控制和数据锁存器:向数据总线D0一D。输出数据,或者接收来自数据总线D0一D。的数据。 读出放大和列写选择:当DRAM阵列中某一行被选中,该行512 ̄2位数据被选通到该读出放大单元, 每个逻辑电平被鉴别而且锁存和重写,并被送到SRAM(cache)阵列。 行译码器:接收行地址并进行译码,对1 024×512×2位DRAM阵列进行行选择。 列译码器:接收列地址并进行译码,对512×2位SRAM阵列进行行选择。 判别逻辑:判断左右地址到来的先后顺序,并决定首先执行左地址还是右地址操作。

双端口存储器原理实验 Document serial number【UU89WT-UU98YT-UU8CB-UUUT-UUT108】 华中科技大学实验报告 实验名称 双端口存储器原理实验 成绩 实验日期 第 2 次试验 指导老师 陈国平 专业 计科 班号 组别 学生姓名 同组学生 一、实验目的 1. 了解双端口静态存储器IDT7132的工作特性及其使用方法 2. 了解半导体存储器怎样存储和读取数据。 3. 了解双端口存储器怎样并行读写,并分析冲突产生的情况。 二、实验电路 图示出了双端口存储器的实验电路图。这里使用一片IDT7132(2048×8位),两个端口的地址输入A8-A10引脚接地,因此实际使用的存储容量为256字节。左端口的数据输出接数据总线DBUS,右端口的数据输出端接指令总线IBUS。 IDT7132有六个控制引脚:CEL#、LR/W#、OEL#、CER#、RR/W#、OER#。CEL#、LR/W#、OEL#控制左端口读、写操作;CER#、RR/W#、OER#控制右端口的读写操作。CEL#为左端口选择引脚,低电平有效;当CEL#=1时,禁止对左端口的读、写操作。LR/W#控制对左端口的读写。当LR/W#=1时,左端口进行读操作;LR/W#=0时,左端口进行写操作。OEL#的作用等同于三态门,当OEL#=0时,允许左端口读出的数据送到数据总线DBUS上;当OEL#=1时,禁止左端口的数据放到DBUS。因此,为便于理解,在以后的实验中,我们将OEL#引脚称为 RAM_BUS#。控制右端口的三个引脚与左端口的三个完全类似,这里不再赘述。有两点需要说明: (1) 右端口读出的数据(更确切的说法是指令)放到指令总线IBUS上而不是数据总线DBUS,然后送到指令寄存器IR。 (2) 所有数据/指令的写入都使用左端口,右端口作为指令端口,不需要进行数据的写入,因此我们将右端口处理成一个只读端口,已将RR/W#固定接高电平,OER#固定接地。这两点请同学好好理解。 存储器左端口的地址寄存器AR和右端口的地址寄存器PC都使用2片74LS163,具有地址递增的功能。同时,PC在以后的实验当中也起到程序计数器的作用。左右端口的数据和左右端口的地址都有特定的显示灯显示。存储器地址和写入数据都由实验台操作板上的二进制开关分时给出。 当LDAR#=0时,AR在T2时从DBUS接收来自SW7-SW0的地址;当AR+1=1时,在T2存储器地址加1。LDAR#和AR+1不能同时有效。在下一个时钟周期,令CEL#=0,LR/W#=0,则在T2的上升沿开始进行写操作,将SW7-SW07设置的数据经DBUS写入存储器。 三、实验任务 1. 按图所示,将有关控制信号和二进制开关对应接好,仔细复查一遍,然后接通电源。 2. 将二进制数码开关SW7-SW0(SW0为最低位)设置为00H,将其作为存储器地址置入AR;然后将二进制开关的00H作为数据写入RAM中。用这个方法,向存储器的10H、20H、30H、40H单元依次写入10H、20H、30H和40H。 3. 使用存储器的左端口,依次将第2步存入的5个数据读出,观察各单元中存入的数据是否正确。记录数据。注意:禁止两个或两个以上的数据源同时向数据总线上发送数据!在本实验中,当存储器进行读出操作时,务必将SW_BUS#的三态门关闭。而当向AR送入数据时,双端口存储器也不能被选中。 4. 通过存储器的右端口,将第2步存入的5个数据读出,观察结果是否与第3步结果相同。记录数据。 5. 双端口存储器的并行读写和访问冲突。 将CEL#、CER#同时置为0,使存储器的左右端口同时被选中。当AR和PC的地址不相同时,没有访问冲突;地址相同时,由于都是读操作,也不会冲突。如果左右端口地址相同,且一个进行读操作,一个进行写操作,就会发生冲突。检测冲突的方法:观察两个端口的“忙”信号输出指示灯BUSYL#和BUSYR#。BUSYL#/BUSYR#灯亮(为0)时,不一定发生冲突,但发生冲突时,BUSYL#/BUSYR#必定亮。 四、实验要求 1. 做好实验预习,掌握IDT7132双端口存储器的功能特性和使用方法。 2. 写出实验报告,内容是: (1) 实验目的。 (2) 实验任务3的数据表格。 (3) 实验任务4的数据表格。 (4) 实验任务5的检测结果。 五、实验步骤 1. 置DP=1,DB=0,编程开关拨到正常位置。 按电路图要求,将有关控制信号和二进制开关对应接好,反复检查后,接通电源。 数据通路 LDAR# LDPC# CEL# LR/W# RAM_BUS# CER# SW_BUS# 电平开关 K0 K1 K2 K3 K4 K5 K6

AR+1 和 PC+1 两个信号接地. 3. 将二进制数码开关SW7-SW0(SW0为最低位)设置为00H,将其作为存储器地址置入AR;然后将二进制开关的00H作为数据写入RAM中.用这个方法,向存储器的10H,20H,30H,40H单元依次写入10H,20H,30H,40H.

任务:将00H,10H,20H,30H,40H分别写入存储器单元00H,10H,20H,30H,40H. (1) 令K0(LDAR#)=0, K2(CEL#)=1, K4(RAM_BUS#)=1, K5(CER#)=1, K6(SW_BUS#)=0.

数据通路 LDAR# LDPC# CEL# LR/W# RAM_BUS# CER# SW_BUS# 电平开关 K0 K1 K2 K3 K4 K5 K6 状态 0 × 1 × 1 1 0

置SW7-SW0=00H, SW7 SW6 SW5 SW4 SW3 SW2 SW1 SW0 0 0 0 0 0 0 0 0

按QD按钮,将00H打入地址寄存器AR. (2) 令K0(LDAR#)=1, K2(CEL#)=0, K3(LR/W#)=0, K4(RAM_BUS#)=1, K5(CER#)=1, K6(SW_BUS#)=0. 数据通路 LDAR# LDPC# CEL# LR/W# RAM_BUS# CER# SW_BUS# 电平开关 K0 K1 K2 K3 K4 K5 K6 状态 1 × 0 0 1 1 0

置SW7-SW0=00H, SW7 SW6 SW5 SW4 SW3 SW2 SW1 SW0 0 0 0 0 0 0 0 0

按QD按钮,将00H写入存储器00H单元. (3) 重复1和2,只是改变SW7-SW0分别为10H,20H,30H,40H,分别将10H,20H,30H,40H

写入存储器单元10H,20H,30H,40H. 实验数据记录表: 存储单元地址 存储单元数据/指令 00H 00H 10H 10H 20H 20H 30H 30H 40H 40H

3.使用存储器的左端口,依次将第2步存入的5个数据读出,观察各单元中存入的数据是否正确.记录数据。(注意:禁止两个或两个以上的数据源同时向数据总线上发送数据!在本实验中,当存储器进行读出操作时,务必将SW_BUS#的三态门关闭.而当向AR送入数据时,双端口存储器也不能被选中.)

任务:从左端口读出存储器00H,10H,20H,30H,40H的内容. (1) 令K0(LDAR#)=0, K2(CEL#)=1, K4(RAM_BUS#)=1, K5(CER#)=1, K6(SW_BUS#)=0.

数据通路 LDAR# LDPC# CEL# LR/W# RAM_BUS# CER# SW_BUS# 电平开关 K0 K1 K2 K3 K4 K5 K6 状态 0 × 1 × 1 1 0

置SW7-SW0=00H, SW7 SW6 SW5 SW4 SW3 SW2 SW1 SW0 0 0 0 0 0 0 0 0

按QD按钮,将00H打入地址寄存器AR. (2) 先令 K6(SW_BUS#)=1,再令 K2(CEL#)=0, K3(LR/W#)=1, K4(RAM_BUS#)=0, K5(CER#)=1,则在数据总线DBUS上显示出存储器单元00H的内容00H。 (3) 重复1和2的方法,只是改变1中SW7-SW0的值分别为10H,20H,30H,40H,则可在数据总线DBUS上观察到存储器单元10H,20H,30H,40H的内容分别为10H,20H,30H,40H.

实验结果记录表1: 存储单元地址 存储单元数据/指令 DBUS显示结果

00H 00H 0 0 0 0 0 0 0 0 10H 10H 0 0 0 1 0 0 0 0 20H 20H 0 0 1 0 0 0 0 0 30H 30H 0 0 1 1 0 0 0 0 40H 40H 0 1 0 0 0 0 0 0

4.通过存储器的右端口,将第2步存入的5个数据读出,观察结果是否与第3步结果相同.记录数据。 任务:从右端口读出存储器00H,10H,20H,30H,40H的内容. (1) 令K1(LDPC#)=0, K2(CEL#)=1, K4(RAM_BUS#)=1, K5(CER#)=1, K6(SW_BUS#)=0.

数据通路 LDAR# LDPC# CEL# LR/W# RAM_BUS# CER# SW_BUS# 电平开关 K0 K1 K2 K3 K4 K5 K6 状态 × 0 1 × 1 1 0

置SW7-SW0=00H, SW7 SW6 SW5 SW4 SW3 SW2 SW1 SW0 0 0 0 0 0 0 0 0

按QD按钮,将00H打入PC.

(2) 令 K6(SW_BUS#)=1, K2(CEL#)=1, K5(CER#)=1,则在指令总线IBUS上显示出存储器单元00H的内容00H.

(3) 重复1和2的方法,只是改变1中SW7-SW0的值分别为10H,20H,30H,40H,则可在指令总线IBUS上观察到存储器单元10H,20H,30H,40H的内容分别为10H,20H,30H,40H.

实验结果记录表2: 存储单元地址 存储单元数据/指令 IBUS显示结果

00H 00H 0 0 0 0 0 0 0 0 10H 10H 0 0 0 1 0 0 0 0 20H 20H 0 0 1 0 0 0 0 0 30H 30H 0 0 1 1 0 0 0 0 40H 40H 0 1 0 0 0 0 0 0

5.双端口存储器的并行读写和访问冲突。