2-2内部存储器结构全解

- 格式:ppt

- 大小:1.35 MB

- 文档页数:36

计算机学科专业基础综合组成原理-存储器层次结构(二)(总分:100.00,做题时间:90分钟)一、{{B}}单项选择题{{/B}}(总题数:63,分数:100.00)1.主存储器主要性能指标有______。

Ⅰ.存储周期Ⅱ.存储容量Ⅲ.存取时间Ⅳ.存储器带宽∙ A.Ⅰ、Ⅱ∙ B.Ⅰ、Ⅱ、Ⅳ∙ C.Ⅰ、Ⅲ、Ⅳ∙ D.全部都是(分数:2.00)A.B.C.D. √解析:[解析] 主存储器的主要性能指标包括存储容量、存取时间、存储周期和存储器带宽。

存储容量是指某计算机实际配置的容量,通常来说,它小于最大可配置容量(主存地址空间大小)。

存取时间是指执行一次读操作或写操作的时间,分读出时间和写入时间两种。

存储周期是指存储器进行连续两次独立的读或写操作所需要的最小时间间隔,它通常大于存取时间。

存储器带宽是指单位时间内从存储器读出或写入存储器的最大信息量。

2.下面存储器中,已经被淘汰的是______。

∙ A.半导体存储器∙ B.磁表面存储器∙ C.磁芯存储器∙ D.光盘存储器(分数:2.00)A.B.C. √D.解析:[解析] 早期的计算机最常见的存储器是用各种磁芯制成的。

这种磁芯存储器已被微型集成电路块上的半导体存储器所取代。

3.主存储器速度的表示中,存取时间(Ta)和存取周期(Tc)的关系表述正确的是______。

∙ A.Ta>Tc∙ B.Ta<Tc∙ C.Ta=Tc∙ D.二者没有大小关系(分数:2.00)A.B. √C.D.解析:[解析] 存取时间是指执行一次读操作或写操作的时间,分读出时间和写入时间两种。

存储周期是指存储器进行连续两次独立的读或写操作所需要的最小时间间隔,它通常大于存取时间,故本题选B。

4.某32位微型机地址码为32位,若使用32K×8位的RAM芯片进行字扩展成存储器,则该机所允许的最大主存容量是______。

∙ A.32KB∙ B.16MB∙ C.512MB∙ D.4GB(分数:2.00)A.B.C.D. √解析:[解析] 要知道最大主存容量,只需要知道存储单元大小和存储单元个数即可。

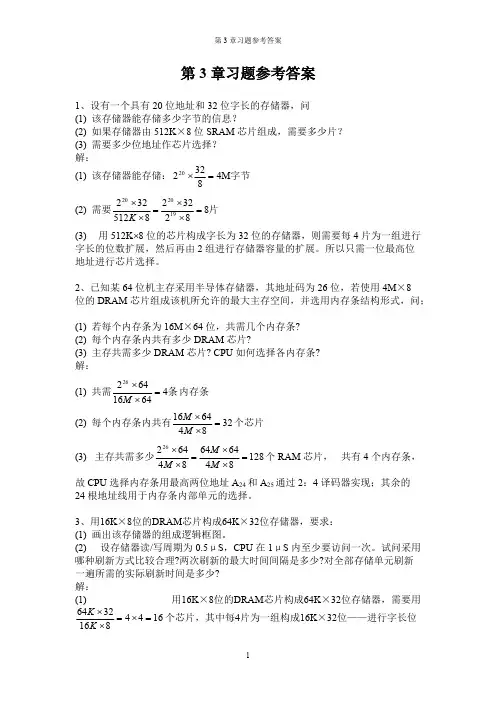

第3章习题参考答案1、设有一个具有20位地址和32位字长的存储器,问(1) 该存储器能存储多少字节的信息?(2) 如果存储器由512K ×8位SRAM 芯片组成,需要多少片?(3) 需要多少位地址作芯片选择?解:(1) 该存储器能存储:字节4M 832220=⨯(2) 需要片8823228512322192020=⨯⨯=⨯⨯K (3) 用512K ⨯8位的芯片构成字长为32位的存储器,则需要每4片为一组进行字长的位数扩展,然后再由2组进行存储器容量的扩展。

所以只需一位最高位地址进行芯片选择。

2、已知某64位机主存采用半导体存储器,其地址码为26位,若使用4M ×8位的DRAM 芯片组成该机所允许的最大主存空间,并选用内存条结构形式,问;(1) 若每个内存条为16M ×64位,共需几个内存条?(2) 每个内存条内共有多少DRAM 芯片?(3) 主存共需多少DRAM 芯片? CPU 如何选择各内存条?解:(1) 共需内存条条4641664226=⨯⨯M (2) 每个内存条内共有个芯片32846416=⨯⨯M M (3) 主存共需多少个RAM 芯片, 共有4个内存条,1288464648464226=⨯⨯=⨯⨯M M M 故CPU 选择内存条用最高两位地址A 24和A 25通过2:4译码器实现;其余的24根地址线用于内存条内部单元的选择。

3、用16K ×8位的DRAM 芯片构成64K ×32位存储器,要求:(1) 画出该存储器的组成逻辑框图。

(2) 设存储器读/写周期为0.5μS ,CPU 在1μS 内至少要访问一次。

试问采用哪种刷新方式比较合理?两次刷新的最大时间间隔是多少?对全部存储单元刷新一遍所需的实际刷新时间是多少?解:(1) 用16K ×8位的DRAM 芯片构成64K ×32位存储器,需要用个芯片,其中每4片为一组构成16K ×32位——进行字长位16448163264=⨯=⨯⨯K K数扩展(一组内的4个芯片只有数据信号线不互连——分别接D0~D 7、D 8~D 15、D 16~D 23和D 24~D 31,其余同名引脚互连),需要低14位地址(A 0~A 13)作为模块内各个芯片的内部单元地址——分成行、列地址两次由A 0~A 6引脚输入;然后再由4组进行存储器容量扩展,用高两位地址A 14、A 15通过2:4译码器实现4组中选择一组。

ROM存储器内涵EPROM2716存储器的介绍 课 堂 教 学 实 施 方 案 授 课 时 间: 课 题:只读存储器ROM、主存储器的设计

5.3 只读存储器ROM

指在微机系统的在线运行过程中,只能对其进行读操作,而不能进行写操作的一类存储器,在不断发展变化的过程中,ROM

器件也产生了掩模ROM、PROM、EPROM、EEPROM等各种不同类型。

一、掩模ROM 如图4-11所示,是一个简单的4×4位的MOS ROM存储阵列,采用单译码方式。这时,有两位地址输入,经译码后,输出四条字选择线,每条字选择线选中一个字,此时位线的输出即为这个字的每一位。 此时,若有管子与其相连(如位线1和位线4),则相应的MOS管就导通,这些位线的输出就是低电表平,表示逻辑“0”;而没有管子与其相连的位线(如位线2和位线3),则输出就是高电平,表示逻辑“1”。 二、可编程的ROM

掩模ROM的存储单元在生产完成之后,其所保存的信息就已经固定下来了,这给使用者带来了不便。为了解决这个矛盾,设计制造了一种可由用户通过简易设备写入信息的ROM器件,即可编程的ROM,又称为PROM。 PROM 的类型有多种,我们以二极管破坏型PROM为例来说明其存储原理。 这种PROM存储器在出厂时,存储体中每条字线和位线的交叉处都是两个反向串联的二极管的PN结,字线与位线之间不导通,此时,意味着该存储器中所有的存储内容均为“1”。如果用户需要写入程序,则要通过专门的PROM写入电路,产生足够大的电流把要写入“1”的那个存储位上的二极管击穿,造成这个PN结短路,只剩下顺向的二极管跨连字线和位线,这时,此位就意味着写入了“1”。读出的操作同掩模ROM。 除此之外,还有一种熔丝式PROM,用户编程时,靠专用写入电路产生脉冲电流,来烧断

P+P

+

AlSiO2

SD浮空多

晶硅栅

N基体

字线

EPROM(a)(b)

位线 A1

A2A3A4A5A6A7O1O2O0A0地VCCA8A9VPPOEA10

存储当前运行的程序指令和数据,并通过高速的系统总线直接供CPU进行处理的内部存储器简称内存或主存。

内存的容量、速度和可靠性等指标直接关系到系统的性能。

内存由半导体集成电路存储器组成,因此存取速度快、容量较小、单位存储容量价格高。

1.内存储器的作用2.3 内存概述2.3.1 内存简介1、存储器的类型DRAM:DDR2/DRR3内存SRAM:CPU内部Cache存储器半导体:闪存(SSD/U盘)外存磁介质:HDD光介质:CD-RAM/DVD/BD传统内存定义:直接与CPU进行数据交换的存储器称为内存,不能直接与CPU进行数据交换的存储器称为外存。

外存材料和原理更加多样化。

外存要求:容量大,价格便宜,断电后数据不会丢失。

外存类型:半导体材料,如SSD、U盘、CF卡等;磁介质材料,如硬盘、软盘、磁带机等;光介质材料,如CD-ROM、DVD-ROM、BD-ROM等2.内存与处理器的关系3. 内存的外观一般以三种形式出现:计算机主存(RAM):主要由DRAM 动态随机存储器构成常见的有DDR、DDR2、DDR3只读存储器(ROM):一般都用于保存微机的BIOS系统通常由EPROM、EEPROM、FlashMemory 等构成高速缓存(Cache):高速缓存的作用主要是用于在CPU和主存之间建立一个中间速度的缓冲区间,加快数据的读写速度。

高速缓冲存储器,一般含在CPU中。

“内存”:一般是指的微机中的主存部分。

4、内存的分类内存是计算机的另一个主要部件之一,是沟通CPU与其他设备的桥梁。

59.21mm61.86mm53.88mmDDR、DDR2、DDR3插口比较不同规格的DDR内存,断口位置不同。

内存条接口形式168针SDRAM DIMM内存插槽金手指每面为84Pin,金手指上有两个卡口,用来避免插入插槽时,错误将内存反向插入而导致烧毁184针DDR DIMM内存插槽金手指每面有92Pin,金手指上只有一个卡口。